Posted CAS for DDRII SDRAM Bill Gervasi Technology

Posted CAS for DDR-II SDRAM Bill Gervasi Technology Analyst October, 2002

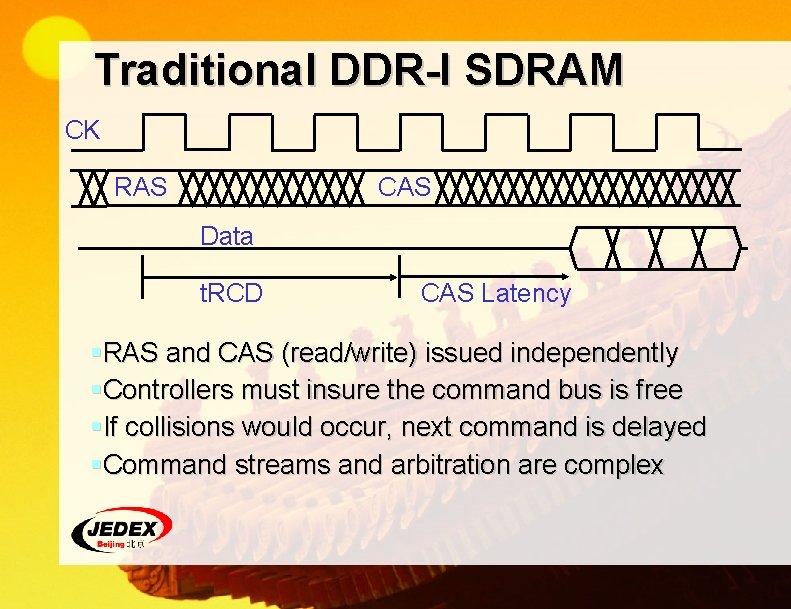

Traditional DDR-I SDRAM CK RAS CAS Data t. RCD CAS Latency §RAS and CAS (read/write) issued independently §Controllers must insure the command bus is free §If collisions would occur, next command is delayed §Command streams and arbitration are complex

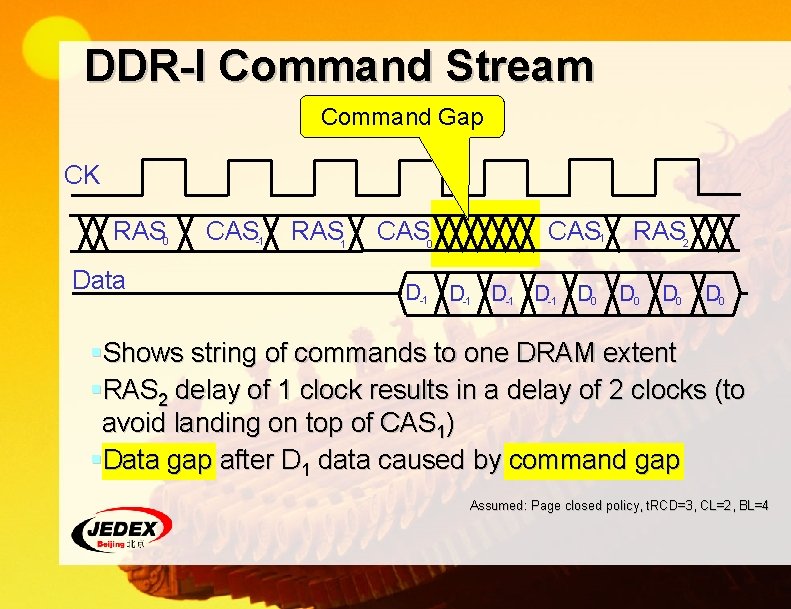

DDR-I Command Stream Command Gap CK RAS 0 Data CAS-1 RAS 1 CAS 0 CAS 1 D-1 D-1 D 0 RAS 2 D 0 D 0 §Shows string of commands to one DRAM extent §RAS 2 delay of 1 clock results in a delay of 2 clocks (to avoid landing on top of CAS 1) §Data gap after D 1 data caused by command gap Assumed: Page closed policy, t. RCD=3, CL=2, BL=4

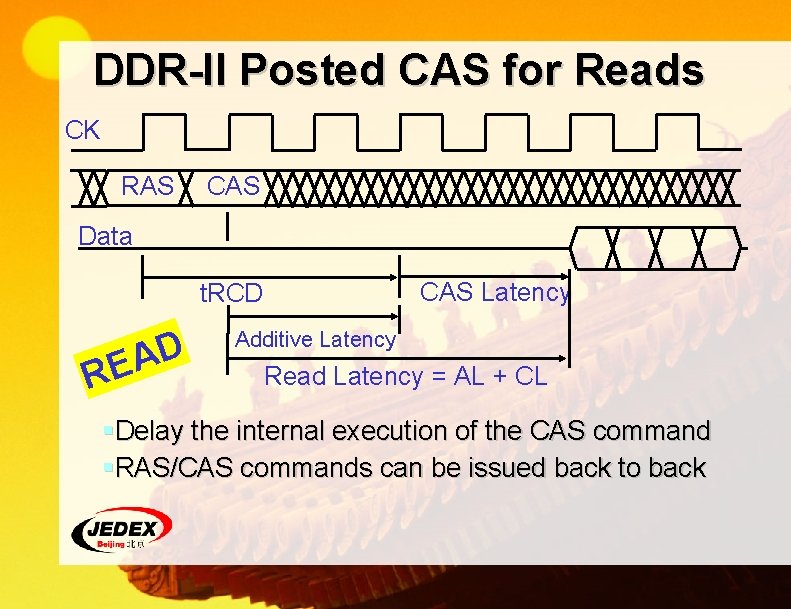

DDR-II Posted CAS for Reads CK RAS CAS Data CAS Latency t. RCD D A RE Additive Latency Read Latency = AL + CL §Delay the internal execution of the CAS command §RAS/CAS commands can be issued back to back

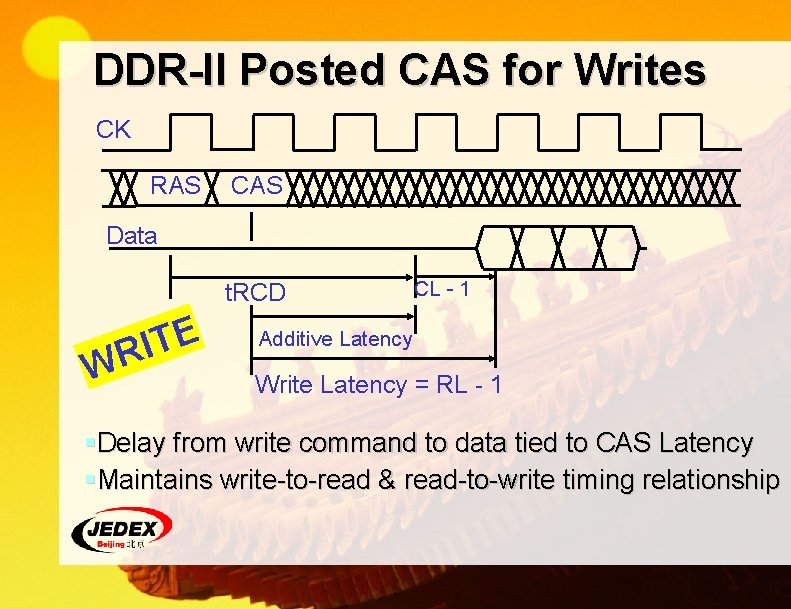

DDR-II Posted CAS for Writes CK RAS CAS Data t. RCD W E T I R CL - 1 Additive Latency Write Latency = RL - 1 §Delay from write command to data tied to CAS Latency §Maintains write-to-read & read-to-write timing relationship

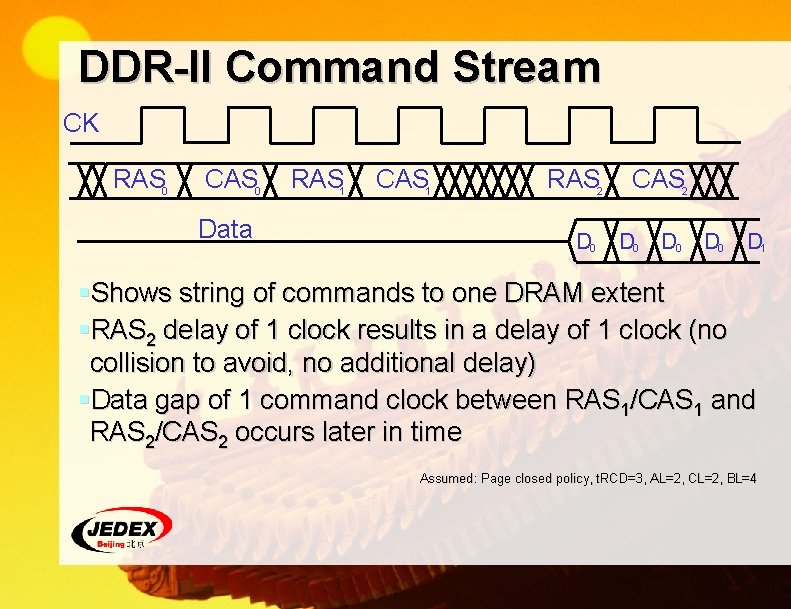

DDR-II Command Stream CK RAS 0 CAS 0 Data RAS 1 CAS 1 RAS 2 D 0 CAS 2 D 0 D 0 D 1 §Shows string of commands to one DRAM extent §RAS 2 delay of 1 clock results in a delay of 1 clock (no collision to avoid, no additional delay) §Data gap of 1 command clock between RAS 1/CAS 1 and RAS 2/CAS 2 occurs later in time Assumed: Page closed policy, t. RCD=3, AL=2, CL=2, BL=4

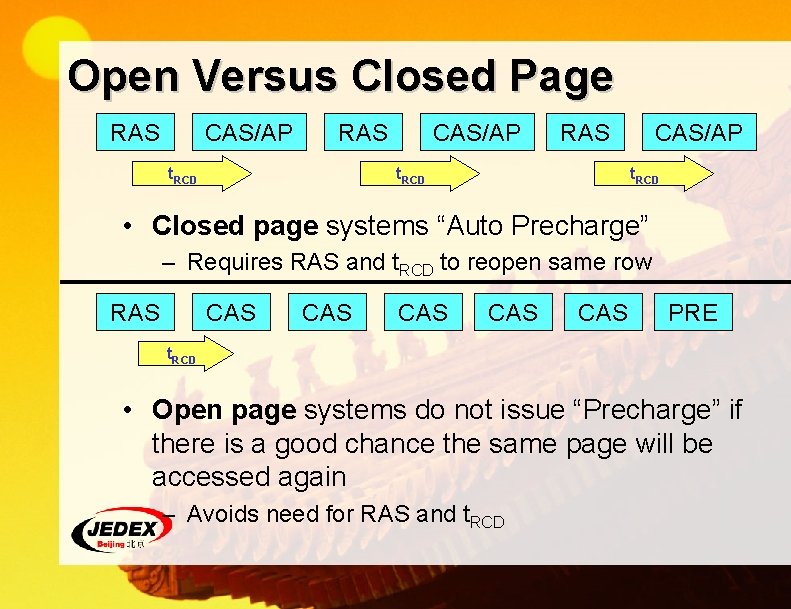

Open Versus Closed Page RAS CAS/AP RAS t. RCD CAS/AP t. RCD • Closed page systems “Auto Precharge” – Requires RAS and t. RCD to reopen same row RAS CAS CAS CAS PRE t. RCD • Open page systems do not issue “Precharge” if there is a good chance the same page will be accessed again – Avoids need for RAS and t. RCD

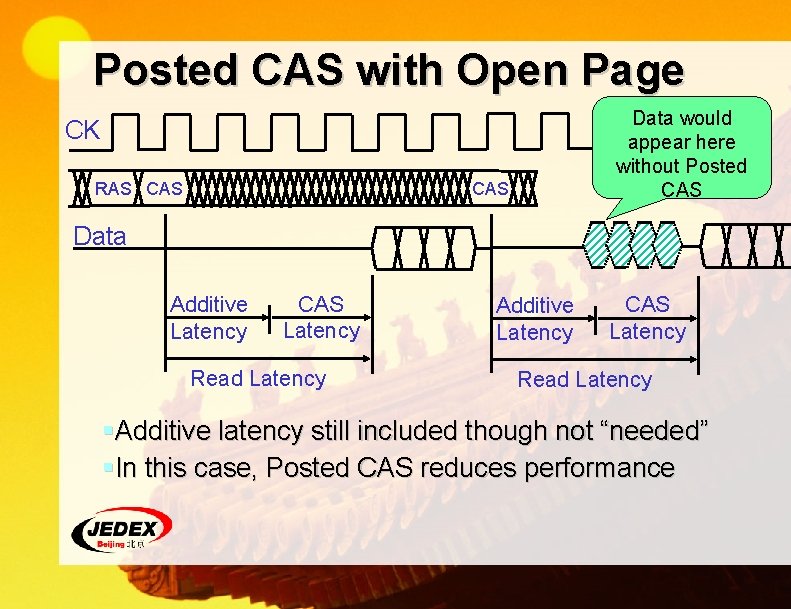

Posted CAS with Open Page Data would appear here without Posted CAS CK RAS CAS Data Additive Latency CAS Latency Read Latency §Additive latency still included though not “needed” §In this case, Posted CAS reduces performance

Posted CAS Summary Ø Closed Page Policy w. Allows RAS & CAS to be issued back to back w. No impacts to latency (from RAS) w. No command collisions w. Longer write recovery Ø Open Page Policy w. Not likely to be used due to increased latency (from CAS) w. Disable Posted CAS via programming register

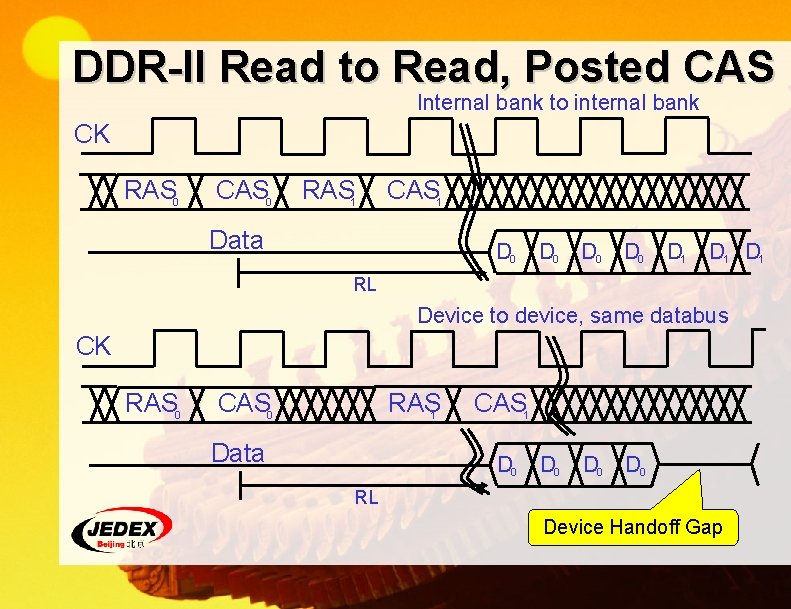

DDR-II Read to Read, Posted CAS Internal bank to internal bank CK RAS 0 CAS 0 RAS 1 CAS 1 Data D 0 D 0 D 1 D 1 RL Device to device, same databus CK RAS 0 CAS 0 RAS 1 Data CAS 1 D 0 D 0 RL Device Handoff Gap

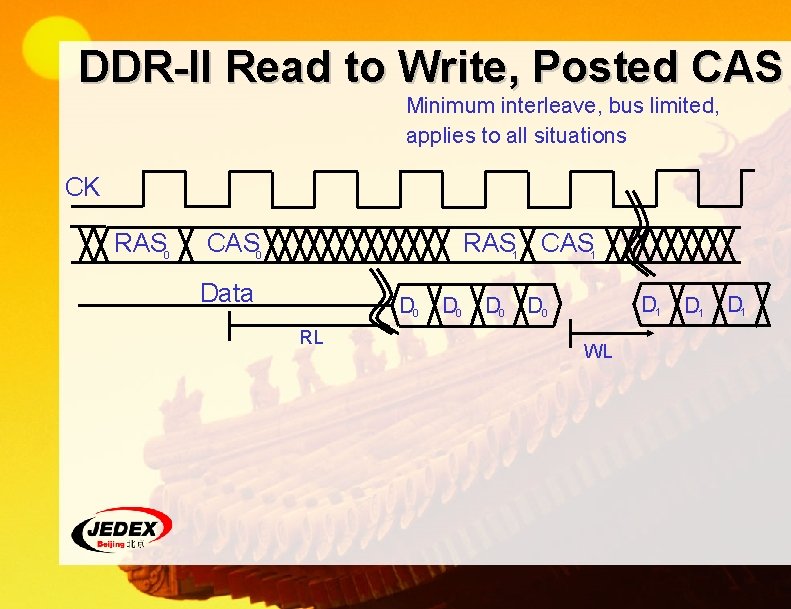

DDR-II Read to Write, Posted CAS Minimum interleave, bus limited, applies to all situations CK RAS 0 CAS 0 RAS 1 CAS 1 Data D 0 RL D 0 D 1 D 0 WL D 1

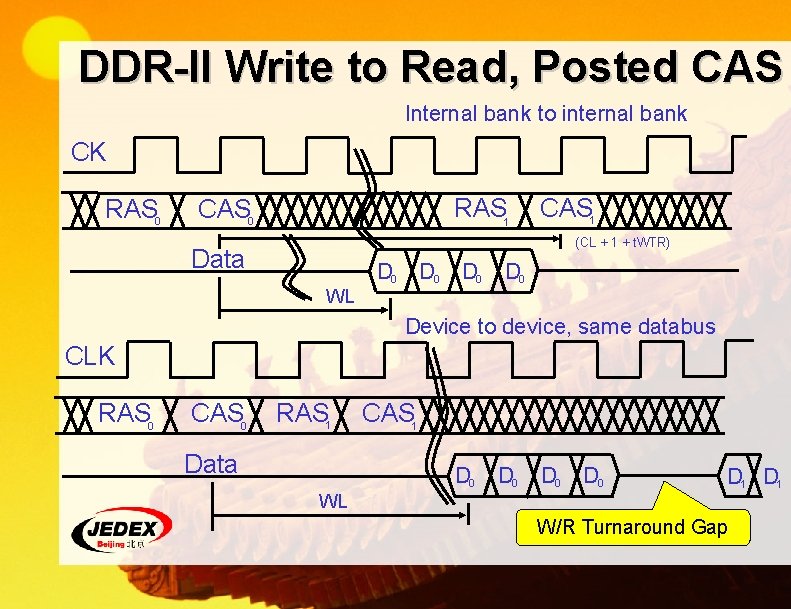

DDR-II Write to Read, Posted CAS Internal bank to internal bank CK RAS 0 RAS 1 CAS 0 CAS 1 (CL + 1 + t. WTR) Data D 0 D 0 WL Device to device, same databus CLK RAS 0 CAS 0 RAS 1 Data CAS 1 D 0 D 0 D 1 WL W/R Turnaround Gap

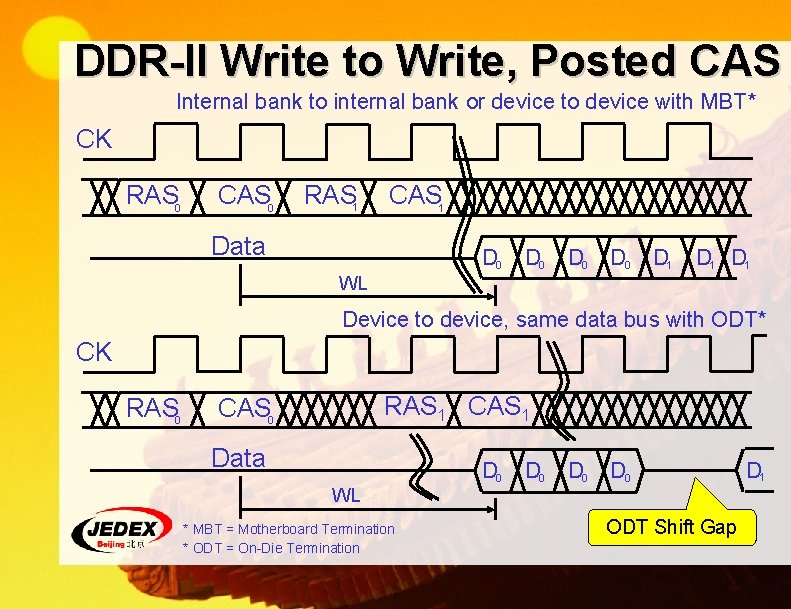

DDR-II Write to Write, Posted CAS Internal bank to internal bank or device to device with MBT* CK RAS 0 CAS 0 RAS 1 CAS 1 Data D 0 D 0 D 1 D 1 WL Device to device, same data bus with ODT* CK RAS 0 RAS 1 CAS 0 Data D 0 D 0 WL * MBT = Motherboard Termination * ODT = On-Die Termination ODT Shift Gap D 1

Conclusions: § Posted CAS reduces command bus collisions § Results in higher data throughput § Optimized with WL = RL - 1 for maximum data bus utilization § Can be disabled for open page systems § Simple concept, easy control, great benefit

- Slides: 14