Pontifcia Universidade Catlica do Rio Grande do Sul

- Slides: 48

Pontifícia Universidade Católica do Rio Grande do Sul Escola Politécnica LABORG Prof. Ney Calazans Última alteração: 27/05/2021 v Baseado em materiais originais dos Profs. Fernando Moraes, Ney Calazans e Rafael Garibotti

AULA SOBRE INTRODUÇÃO A TECNOLOGIA DE FPGAs E PROTOTIPAÇÃO DE HARDWARE

TEORIA, HISTÓRICO E ESTRUTURA DE FPGAs

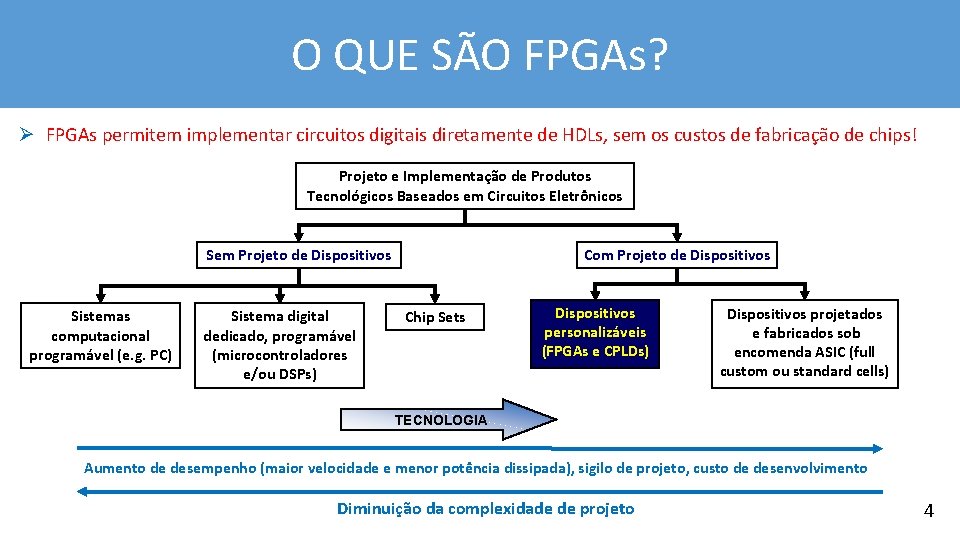

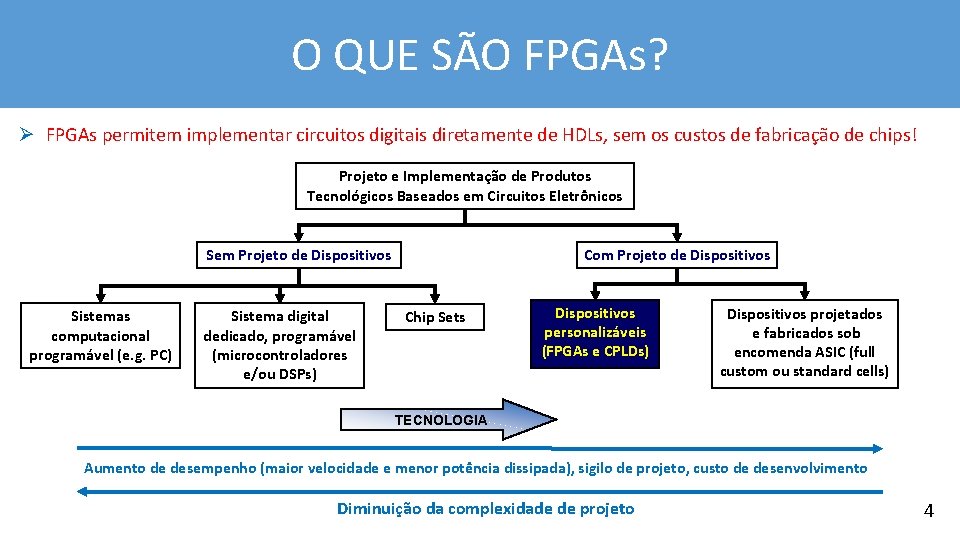

O QUE SÃO FPGAs? Ø FPGAs permitem implementar circuitos digitais diretamente de HDLs, sem os custos de fabricação de chips! Projeto e Implementação de Produtos Tecnológicos Baseados em Circuitos Eletrônicos Sem Projeto de Dispositivos Sistemas computacional programável (e. g. PC) Sistema digital dedicado, programável (microcontroladores e/ou DSPs) Com Projeto de Dispositivos Chip Sets Dispositivos personalizáveis (FPGAs e CPLDs) Dispositivos projetados e fabricados sob encomenda ASIC (full custom ou standard cells) TECNOLOGIA Aumento de desempenho (maior velocidade e menor potência dissipada), sigilo de projeto, custo de desenvolvimento Diminuição da complexidade de projeto 4

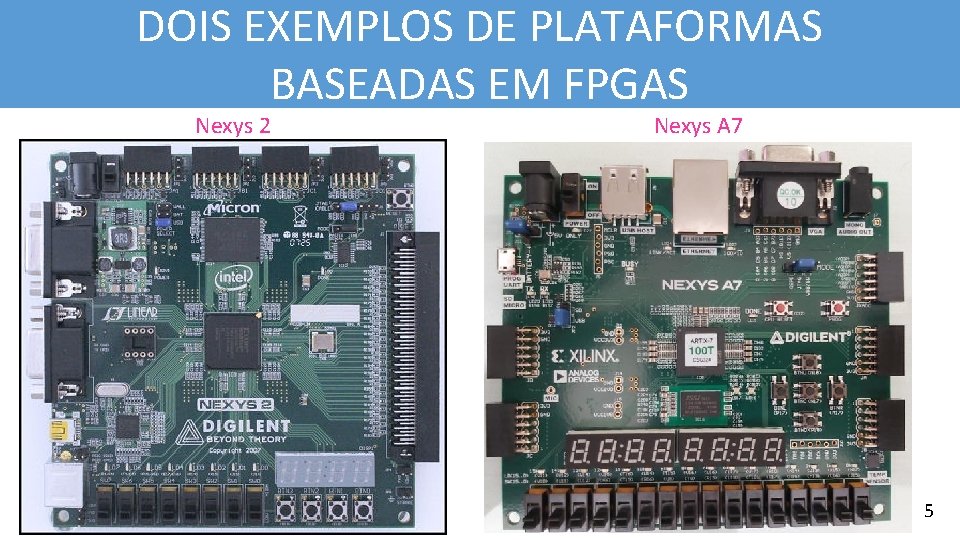

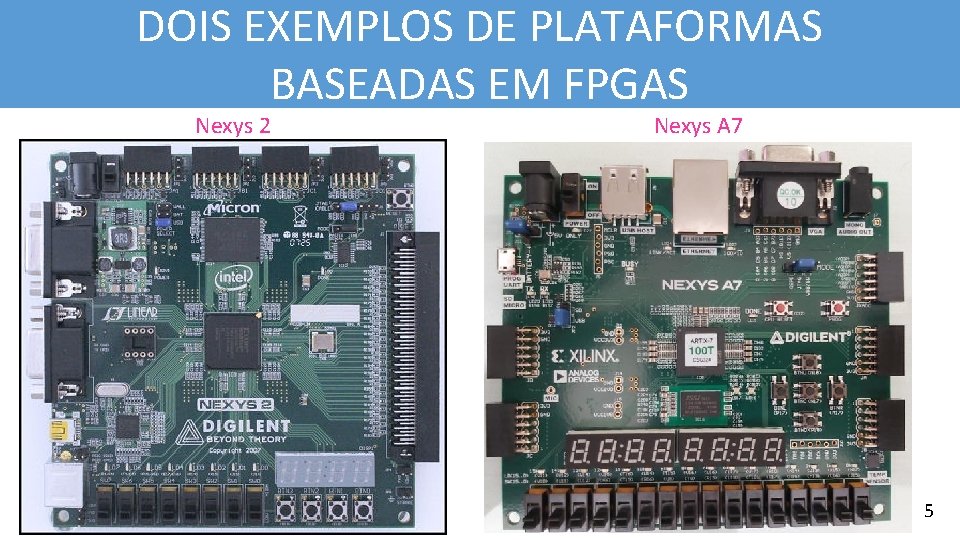

DOIS EXEMPLOS DE PLATAFORMAS BASEADAS EM FPGAS Nexys 2 Nexys A 7 5

UM POUCO DA HISTÓRIA DE FPGAs Ø Primeiro vieram PROMs e PLDs (Programmable logic devices), matrizes de portas (re -) configuráveis Ø Algumas patentes de coisas parecidas com FPGAs (field programmable gate array) surgiram no final dos anos 80 e início dos anos 90 (Casselman, Page, Peterson) Ø Os fundadores da Xilinx, Ross Freeman e Bernard Vonderschmitt, inventaram o primeiro FPGA comercial em 1985 – o XC 2064 Ø O XC 2064 tinha 64 blocos lógicos configuráveis e interconexões configuráveis entre os blocos lógicos Ø O XC 2064 só tinha blocos lógicos configuráveis (CLBs), cada um com duas LUTs de 3 entradas 6

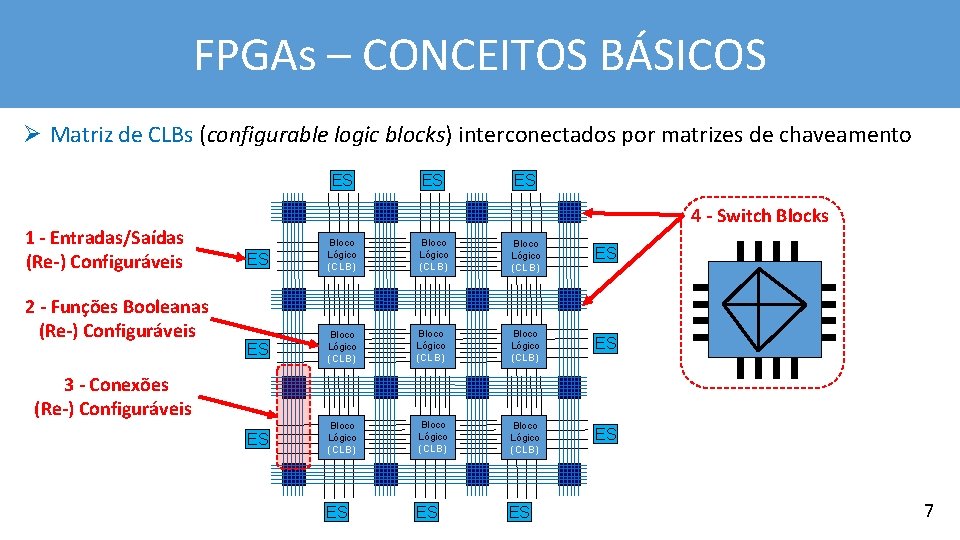

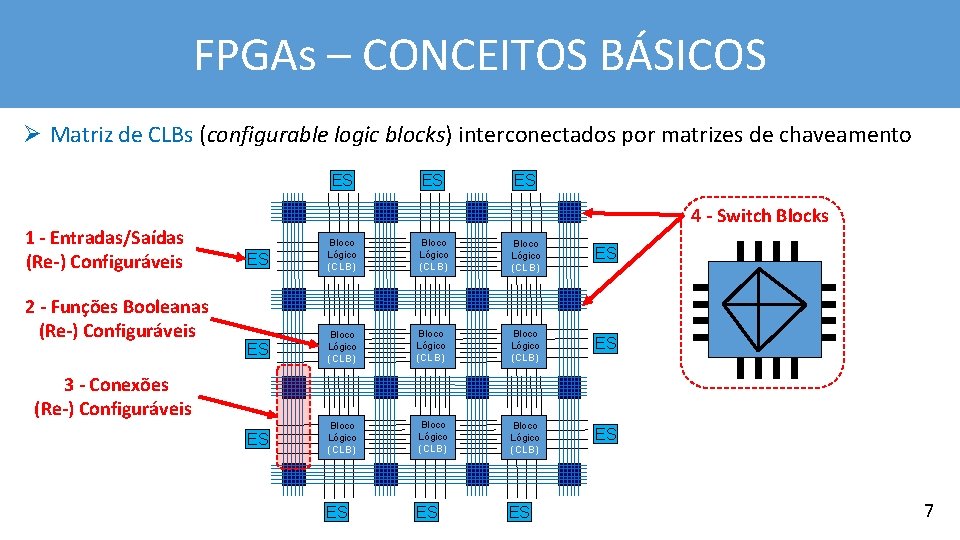

FPGAs – CONCEITOS BÁSICOS Ø Matriz de CLBs (configurable logic blocks) interconectados por matrizes de chaveamento ES 1 - Entradas/Saídas (Re-) Configuráveis 2 - Funções Booleanas (Re-) Configuráveis ES ES 4 - Switch Blocks ES Bloco Lógico (CLB) Bloco Lógico (CLB) ES ES Bloco Lógico (CLB) ES ES 3 - Conexões (Re-) Configuráveis 7

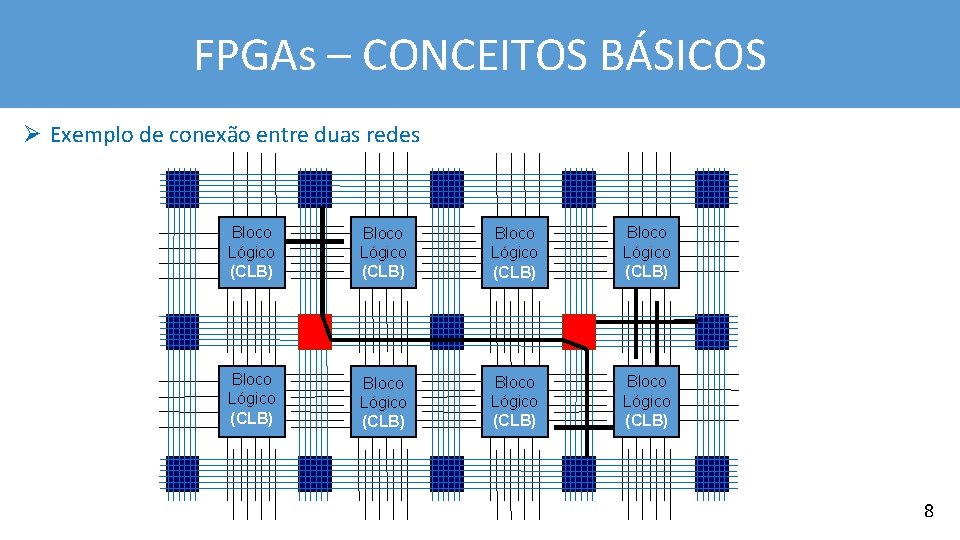

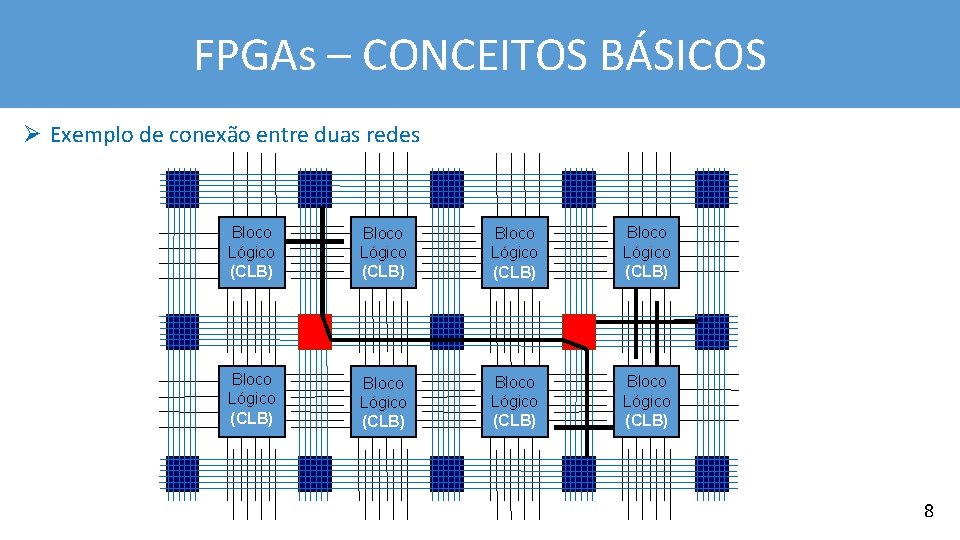

FPGAs – CONCEITOS BÁSICOS Ø Exemplo de conexão entre duas redes Bloco Lógico (CLB) Bloco Lógico (CLB) 8

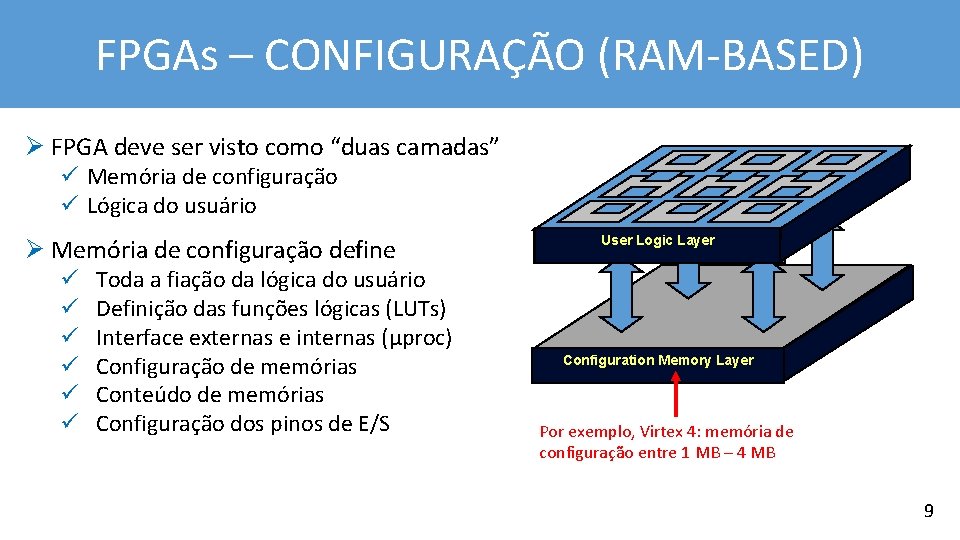

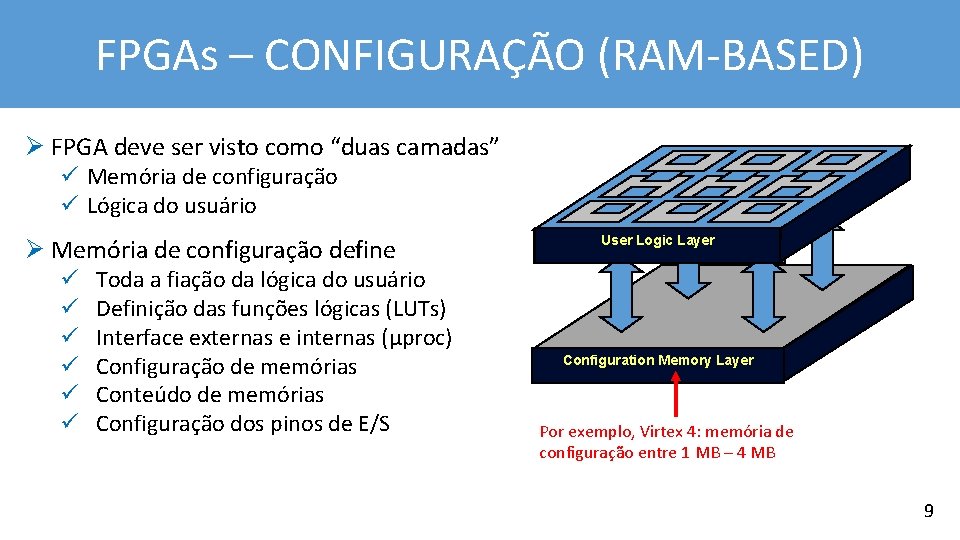

FPGAs – CONFIGURAÇÃO (RAM-BASED) Ø FPGA deve ser visto como “duas camadas” ü Memória de configuração ü Lógica do usuário Ø Memória de configuração define ü ü ü Toda a fiação da lógica do usuário Definição das funções lógicas (LUTs) Interface externas e internas (μproc) Configuração de memórias Conteúdo de memórias Configuração dos pinos de E/S User Logic Layer Configuration Memory Layer Por exemplo, Virtex 4: memória de configuração entre 1 MB – 4 MB 9

TECNOLOGIAS DE CONFIGURAÇÃO Ø Algumas diferentes tecnologias usadas para definir o comportamento de um FPGA ü Antifusível: Configuração uma única vez ü (E)EPROM: Configuração um número limitado de vezes, mantida com o chip desconectado da alimentação ü SRAM: Configuração deve ser realizada cada vez que o FPGA for alimentado 10

LUT – O GERADOR UNIVERSAL DE FUNÇÕES Ø LUT (Look-Up Table) – Um exemplo de Bloco com Função Booleana Reconfigurável ü Uma porção de hardware configurável/reconfigurável capaz de implementar qualquer tabela verdade de n entradas ü Para n=4 (2)4 2 = 65. 536 funções implementáveis • Altamente flexível • Método mais utilizado (Xilinx, Altera e outros) 11

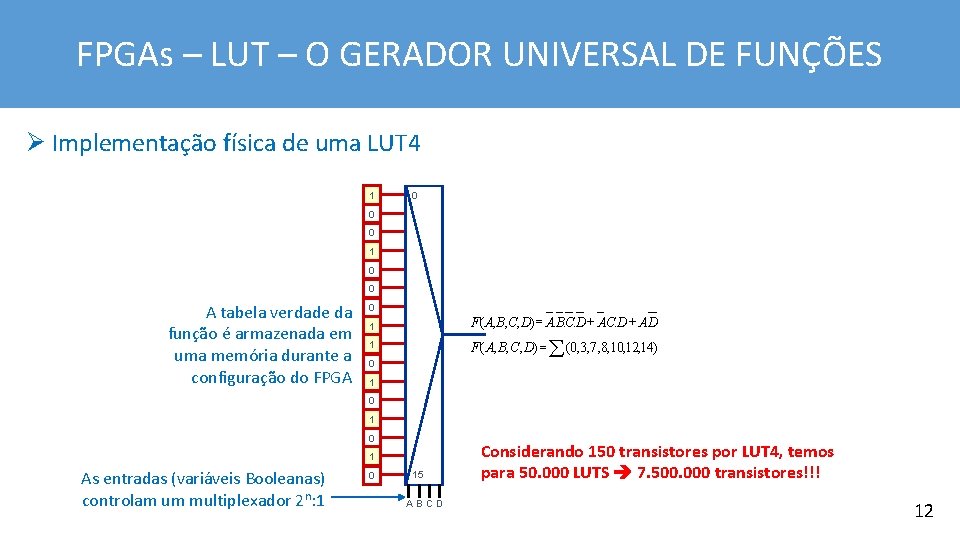

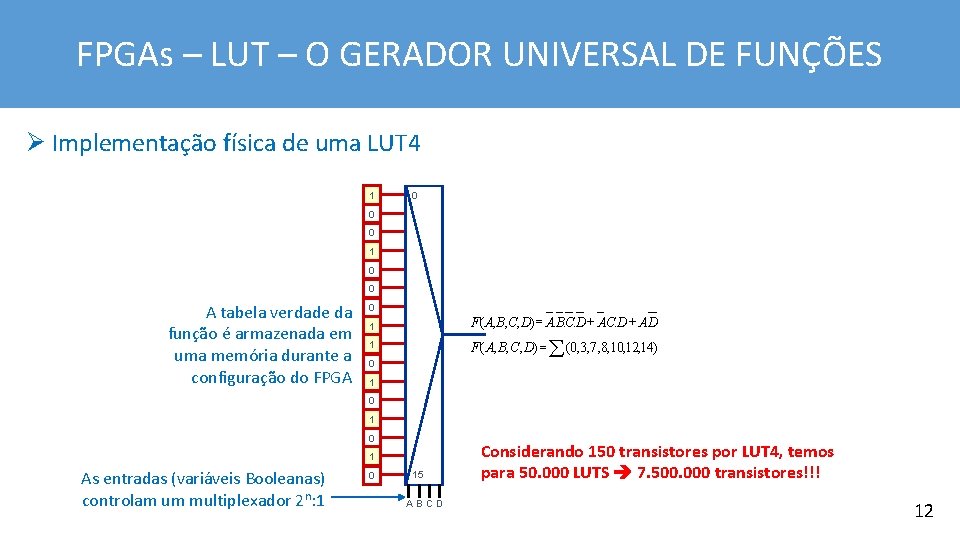

FPGAs – LUT – O GERADOR UNIVERSAL DE FUNÇÕES Ø Implementação física de uma LUT 4 1 0 0 0 1 0 0 A tabela verdade da função é armazenada em uma memória durante a configuração do FPGA 0 F( A, B, C, D) = A. B. C. D + A. D 1 F( A, B, C, D) = å (0, 3, 7, 8, 10, 12, 14) 1 0 1 0 1 As entradas (variáveis Booleanas) controlam um multiplexador 2 n: 1 0 15 ABCD Considerando 150 transistores por LUT 4, temos para 50. 000 LUTS 7. 500. 000 transistores!!! 12

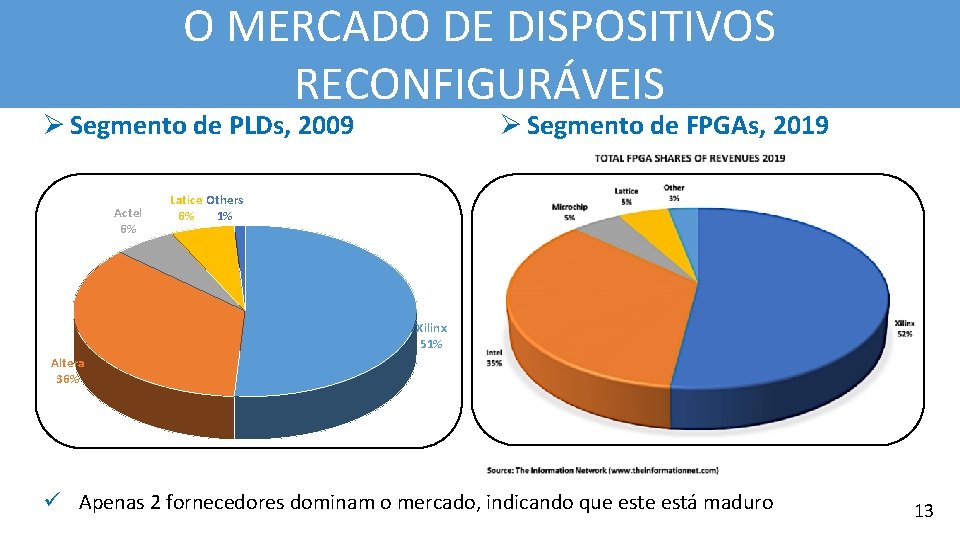

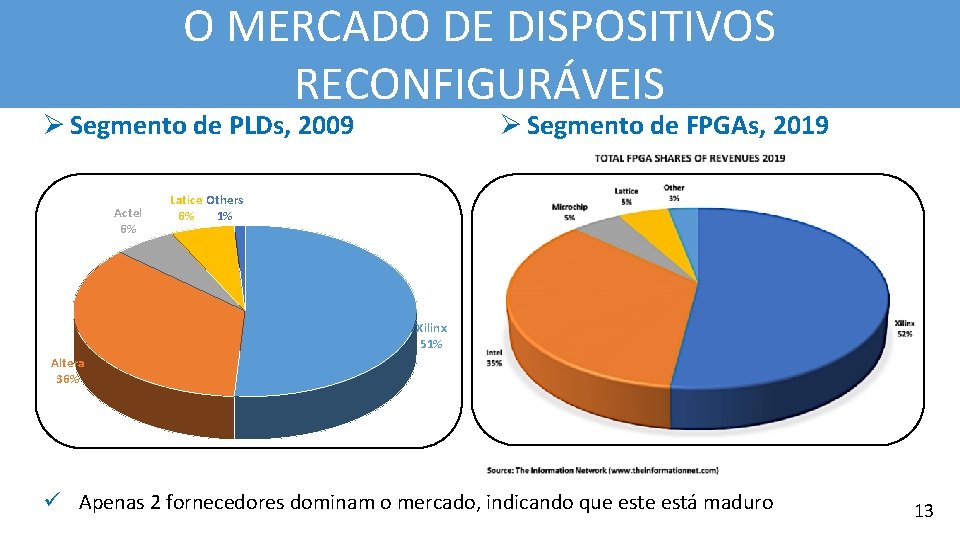

O MERCADO DE DISPOSITIVOS RECONFIGURÁVEIS Ø Segmento de PLDs, 2009 Actel 6% Ø Segmento de FPGAs, 2019 Latice Others 6% 1% Xilinx 51% Altera 36% ü Apenas 2 fornecedores dominam o mercado, indicando que está maduro 13

DISPOSITIVOS XILINX E ALTERA ATUAIS Ø Xilinx ü Baixo/Médio Custo-Desempenho • Famílias Spartan 6, Spartan 7, Artix 7, Kintex 7 ü Alto desempenho • Virtex 7 (28 nm), Virtex-Kintex Ultra. SCALE (20 nm), Virtex-Kintex Ultra. SCALE+ (16 nm) Ø Intel (até 2015 era a empresa Altera, então adquirida pela Intel, por 16, 7 GUS$) ü Baixo Custo e Mid-Range • Famílias Cyclone, Arria ü Alto desempenho • Stratix, Agilex (10 nm) 14

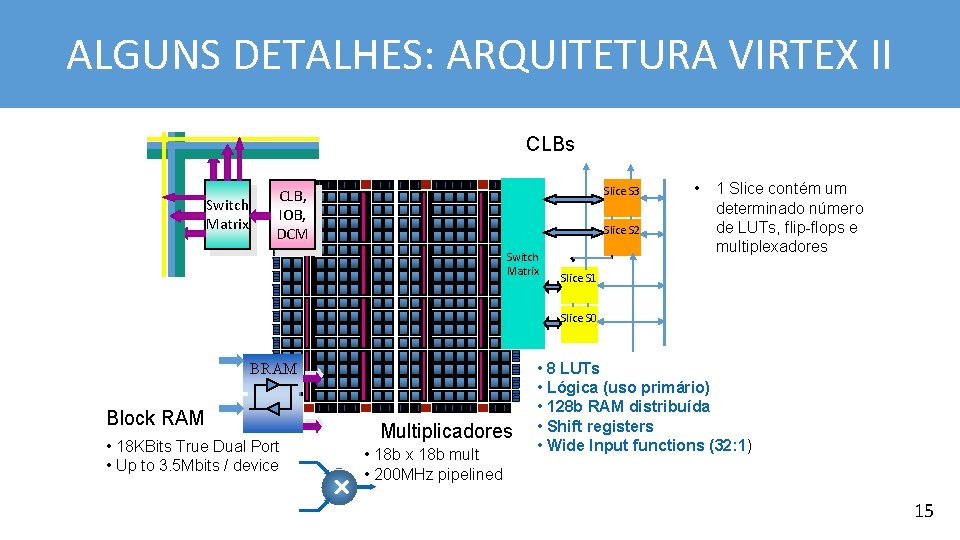

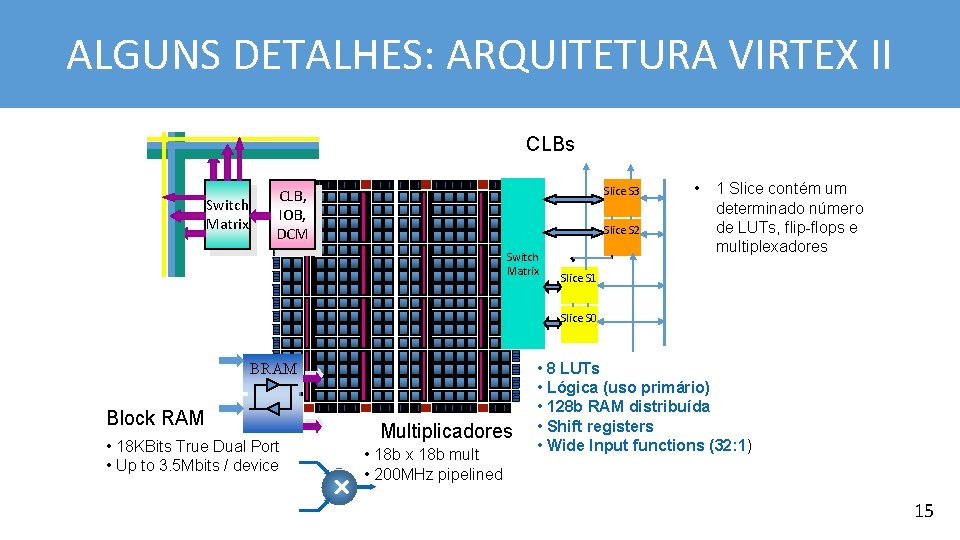

ALGUNS DETALHES: ARQUITETURA VIRTEX II CLBs Switch Matrix Slice S 3 CLB, IOB, DCM Slice S 2 Switch Matrix • 1 Slice contém um determinado número de LUTs, flip-flops e multiplexadores Slice S 1 Slice S 0 BRAM Block RAM • 18 KBits True Dual Port • Up to 3. 5 Mbits / device Multiplicadores • 18 b x 18 b mult • 200 MHz pipelined • 8 LUTs • Lógica (uso primário) • 128 b RAM distribuída • Shift registers • Wide Input functions (32: 1) 15

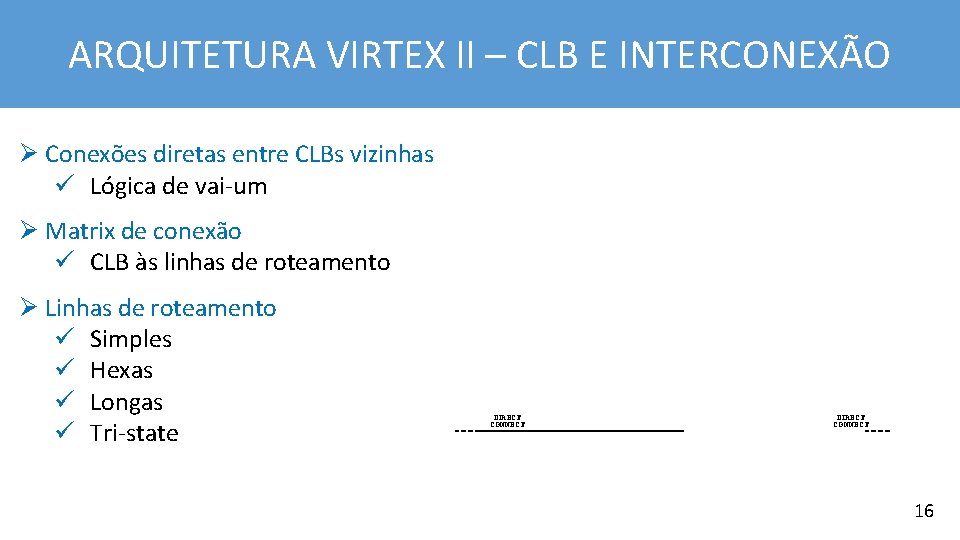

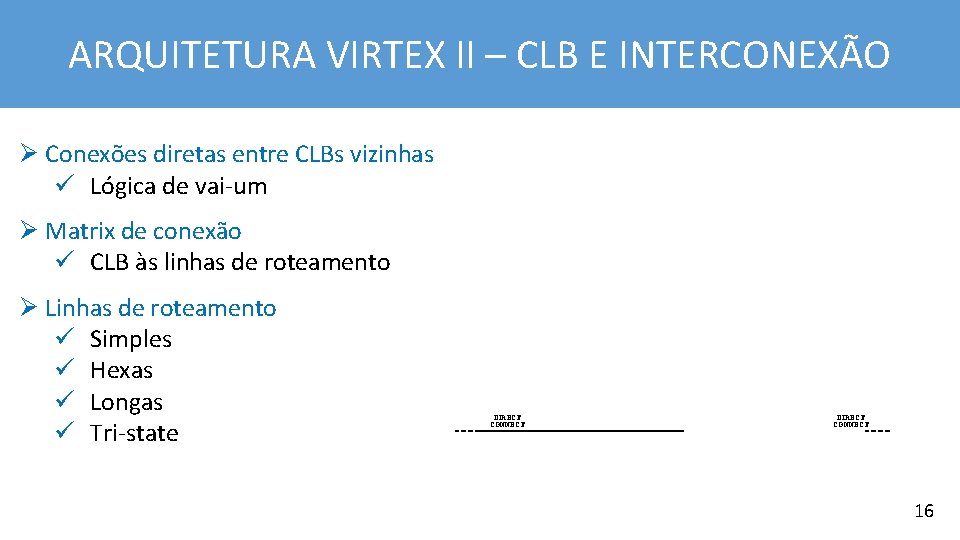

ARQUITETURA VIRTEX II – CLB E INTERCONEXÃO Ø Conexões diretas entre CLBs vizinhas ü Lógica de vai-um Ø Matrix de conexão ü CLB às linhas de roteamento Ø Linhas de roteamento ü Simples ü Hexas ü Longas ü Tri-state DIRECT CONNECT 16

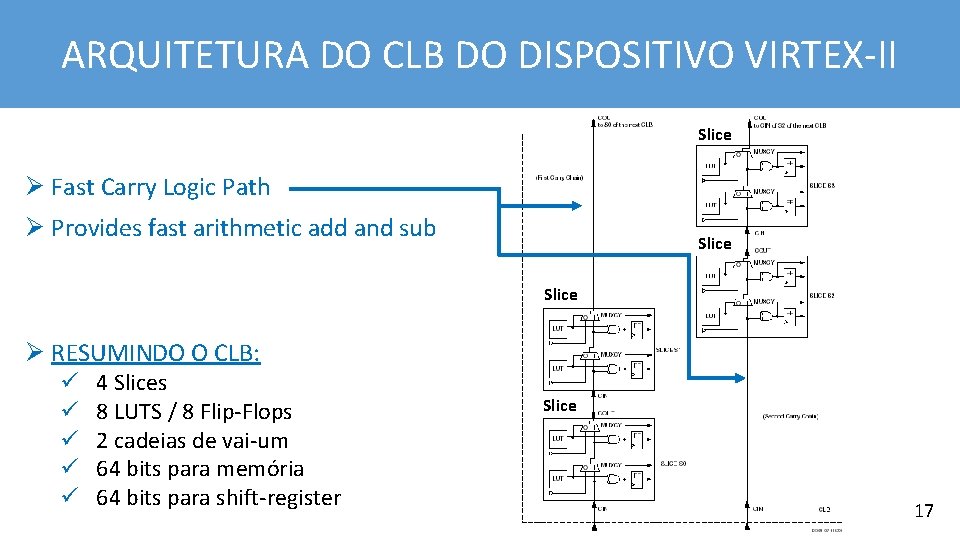

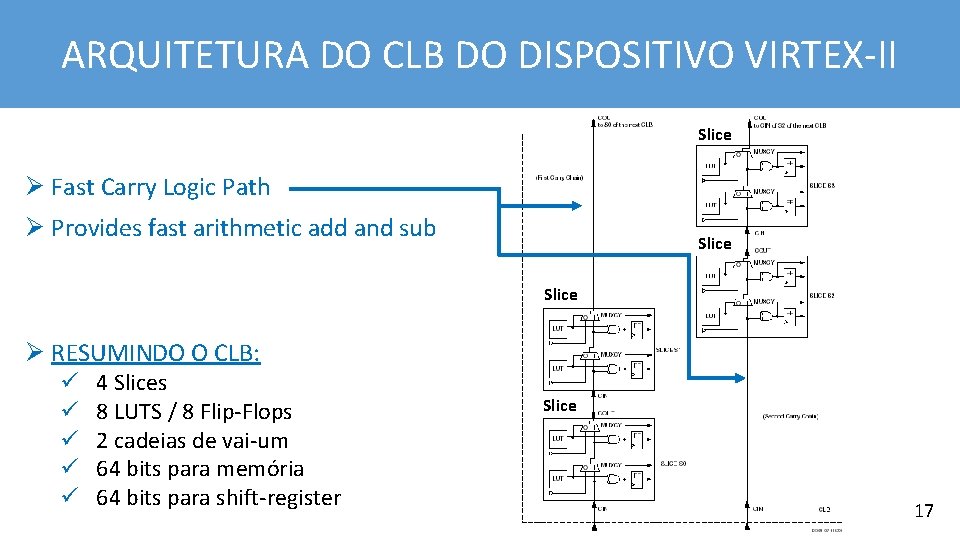

ARQUITETURA DO CLB DO DISPOSITIVO VIRTEX-II Slice Ø Fast Carry Logic Path Ø Provides fast arithmetic add and sub Slice Ø RESUMINDO O CLB: ü ü ü 4 Slices 8 LUTS / 8 Flip-Flops 2 cadeias de vai-um 64 bits para memória 64 bits para shift-register Slice 17

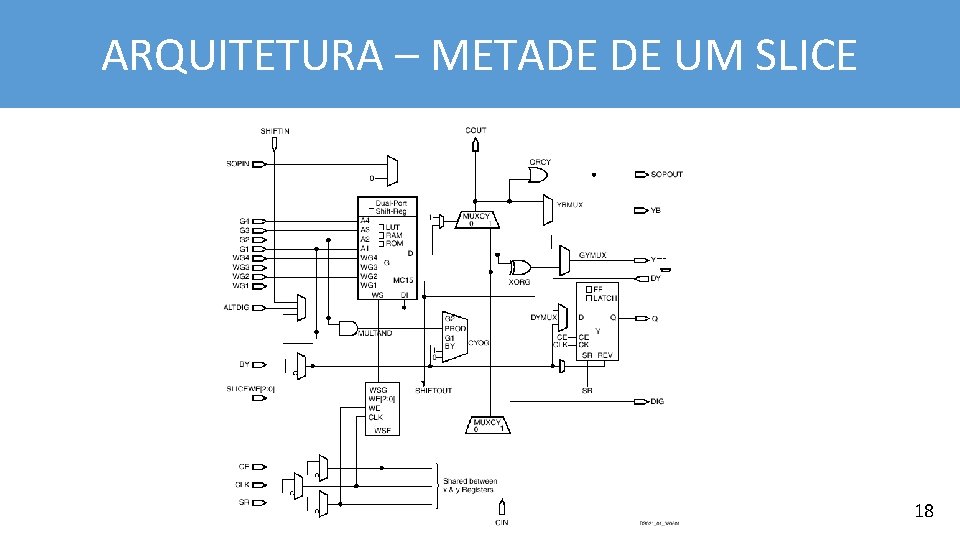

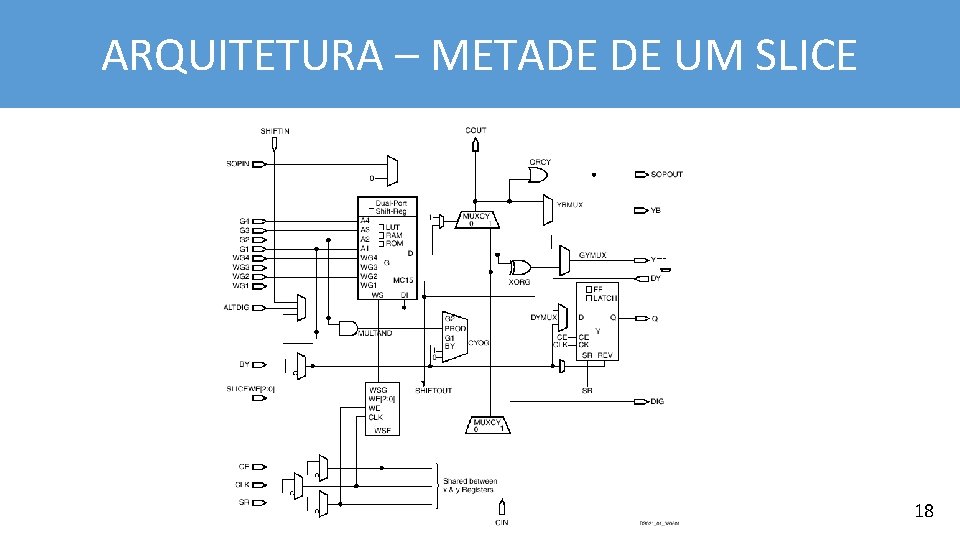

ARQUITETURA – METADE DE UM SLICE 18

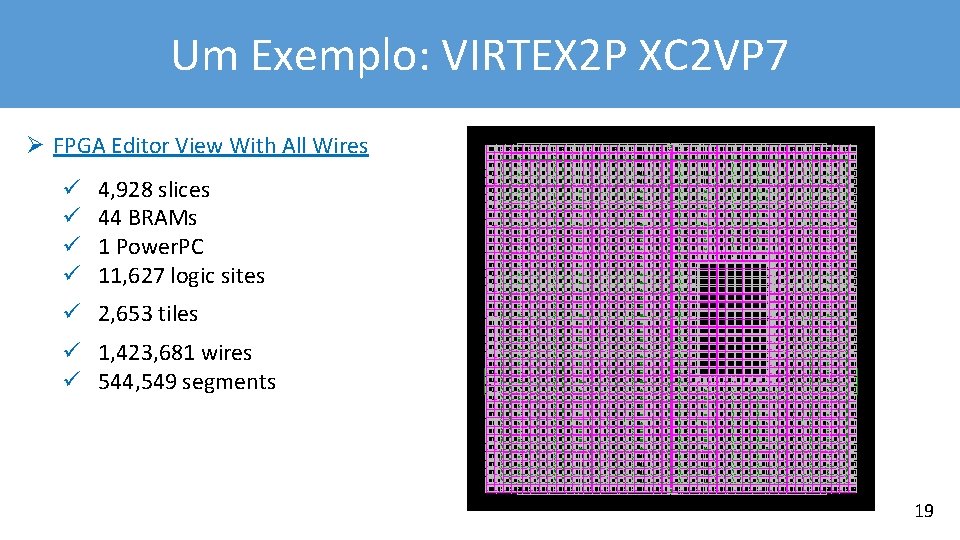

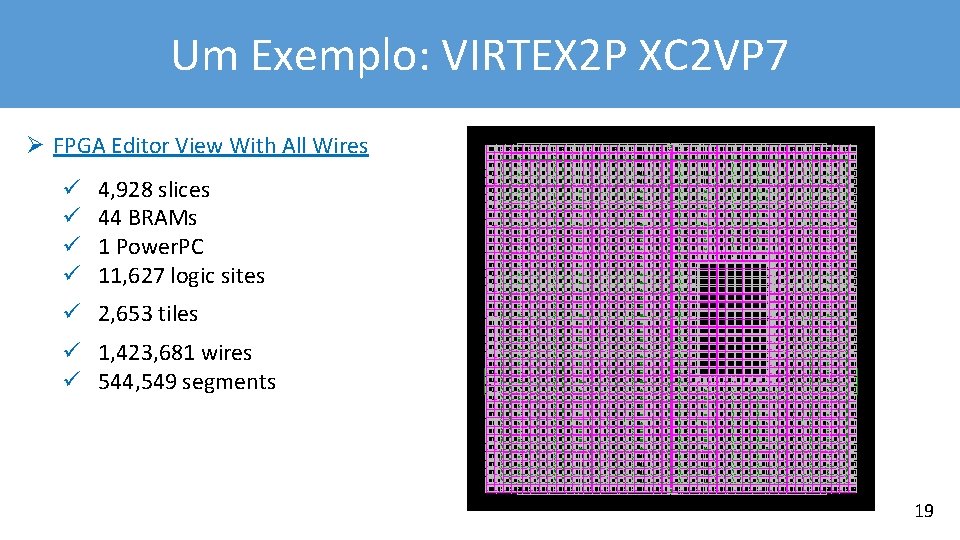

Um Exemplo: VIRTEX 2 P XC 2 VP 7 Ø FPGA Editor View With All Wires ü ü 4, 928 slices 44 BRAMs 1 Power. PC 11, 627 logic sites ü 2, 653 tiles ü 1, 423, 681 wires ü 544, 549 segments 19

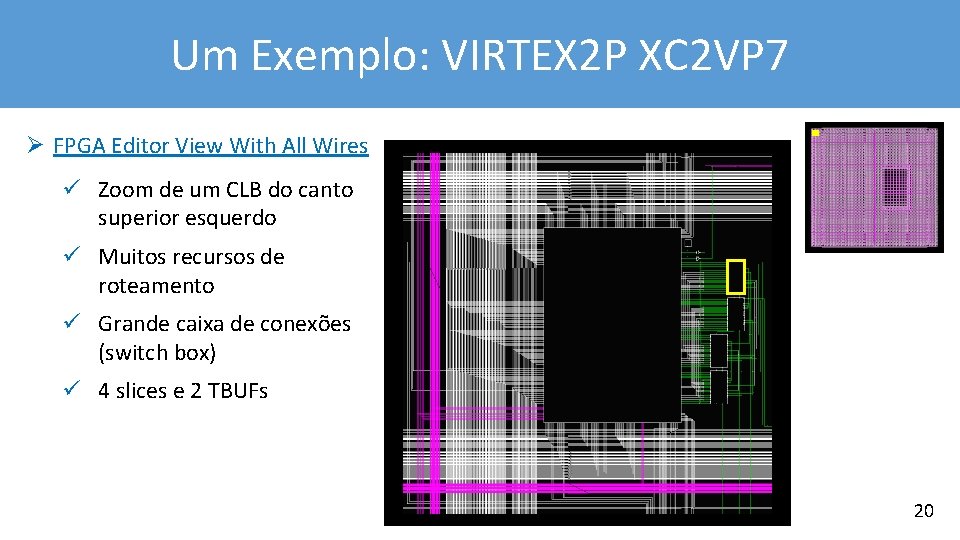

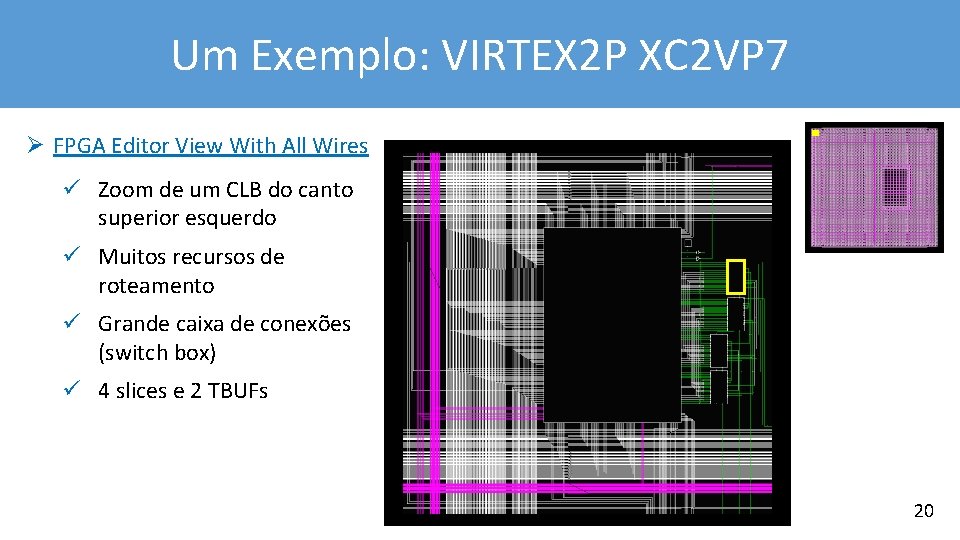

Um Exemplo: VIRTEX 2 P XC 2 VP 7 Ø FPGA Editor View With All Wires ü Zoom de um CLB do canto superior esquerdo ü Muitos recursos de roteamento ü Grande caixa de conexões (switch box) ü 4 slices e 2 TBUFs 20

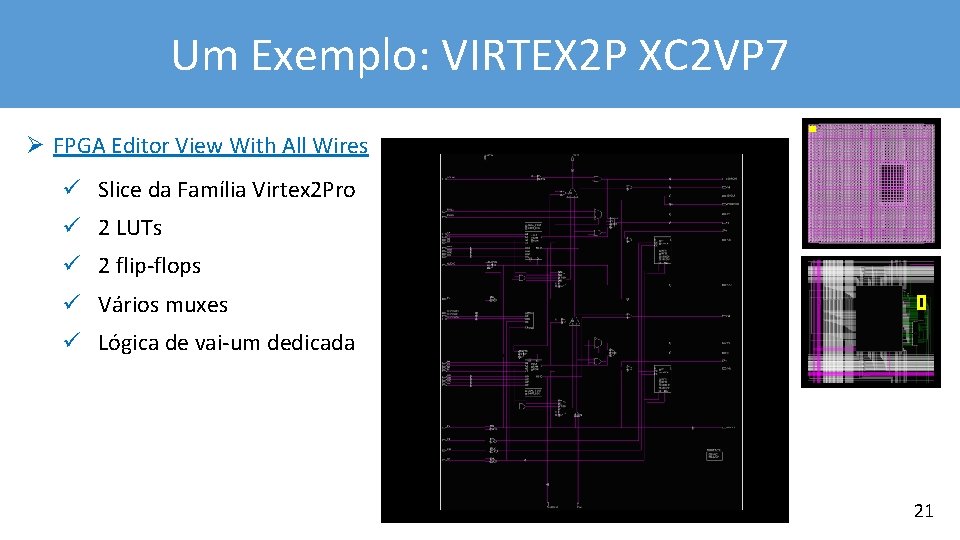

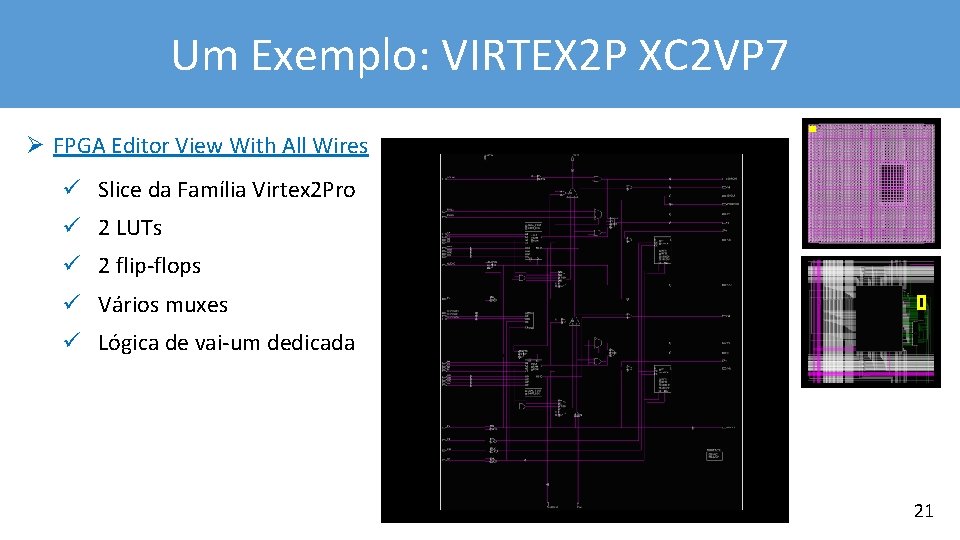

Um Exemplo: VIRTEX 2 P XC 2 VP 7 Ø FPGA Editor View With All Wires ü Slice da Família Virtex 2 Pro ü 2 LUTs ü 2 flip-flops ü Vários muxes ü Lógica de vai-um dedicada 21

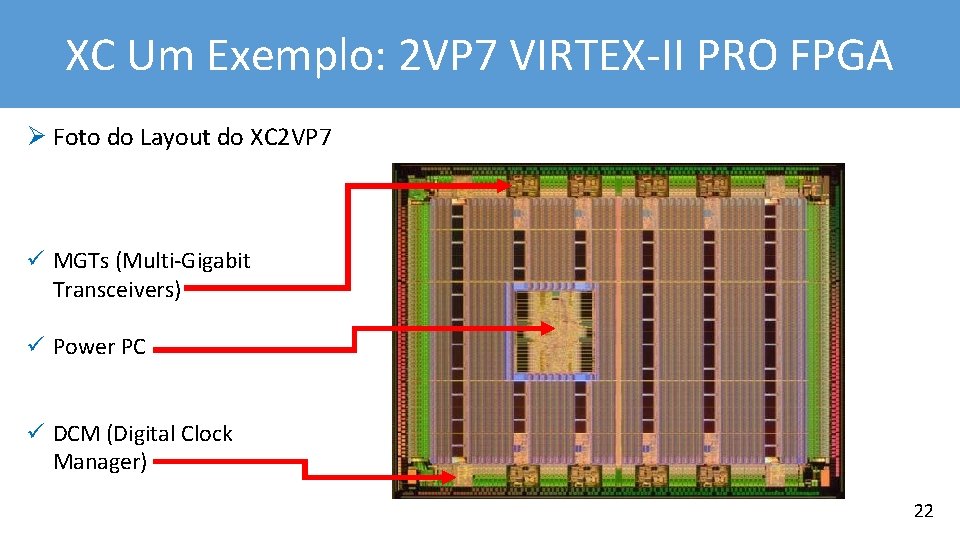

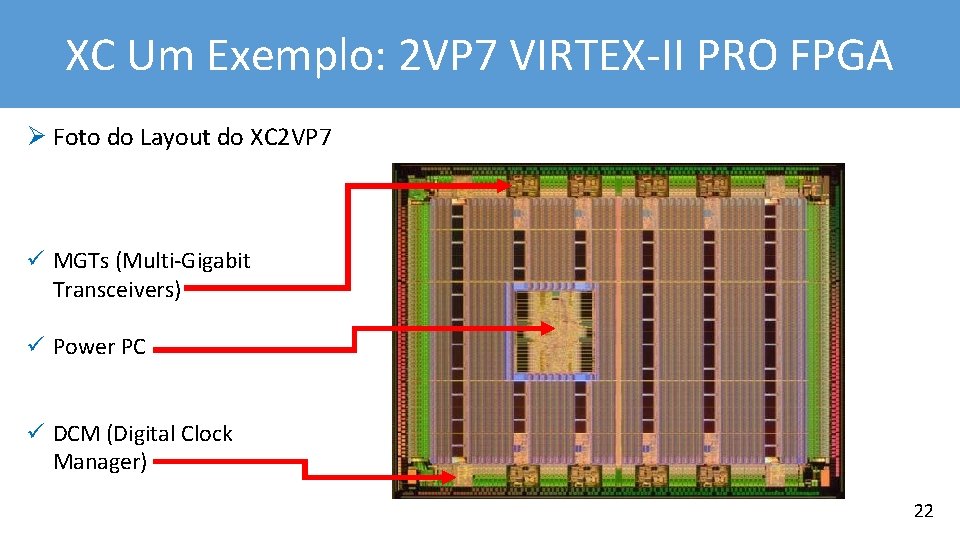

XC Um Exemplo: 2 VP 7 VIRTEX-II PRO FPGA Ø Foto do Layout do XC 2 VP 7 ü MGTs (Multi-Gigabit Transceivers) ü Power PC ü DCM (Digital Clock Manager) 22

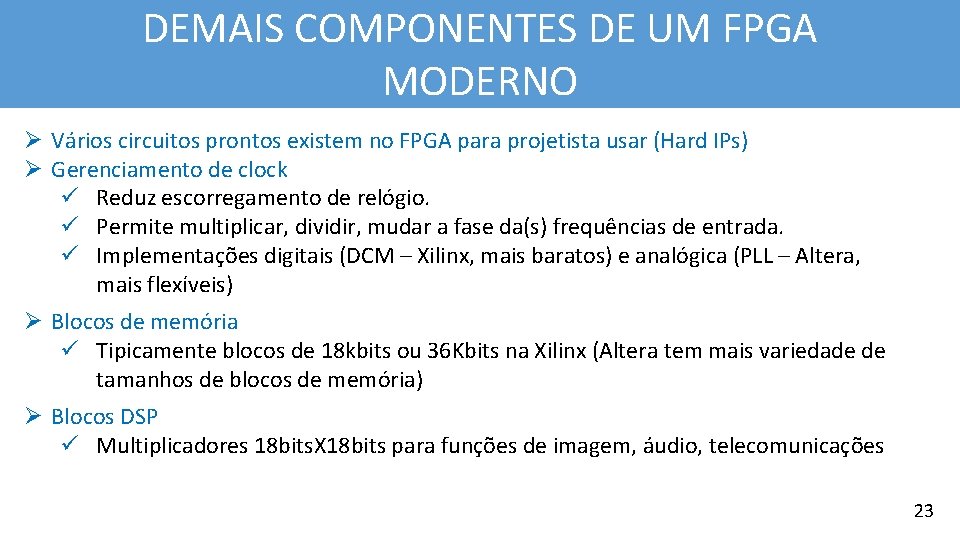

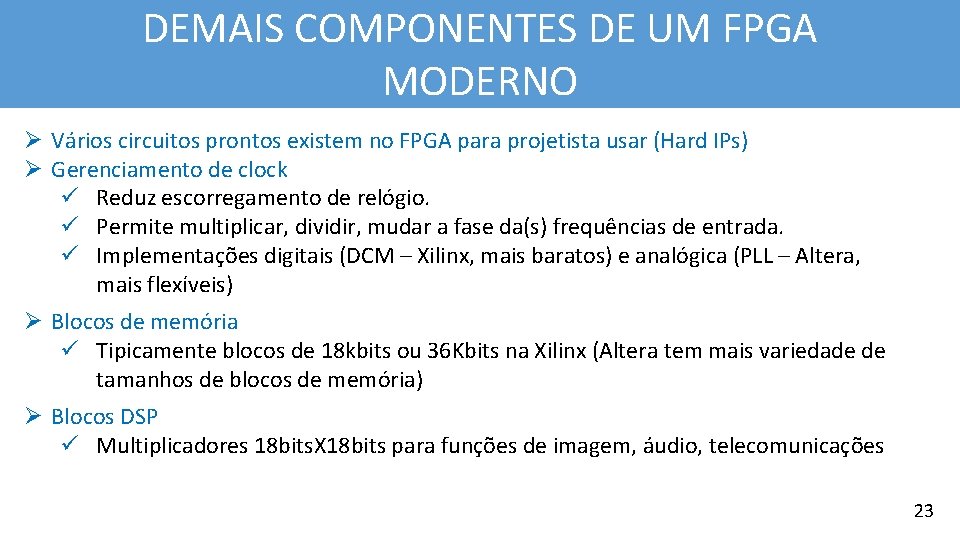

DEMAIS COMPONENTES DE UM FPGA MODERNO Ø Vários circuitos prontos existem no FPGA para projetista usar (Hard IPs) Ø Gerenciamento de clock ü Reduz escorregamento de relógio. ü Permite multiplicar, dividir, mudar a fase da(s) frequências de entrada. ü Implementações digitais (DCM – Xilinx, mais baratos) e analógica (PLL – Altera, mais flexíveis) Ø Blocos de memória ü Tipicamente blocos de 18 kbits ou 36 Kbits na Xilinx (Altera tem mais variedade de tamanhos de blocos de memória) Ø Blocos DSP ü Multiplicadores 18 bits. X 18 bits para funções de imagem, áudio, telecomunicações 23

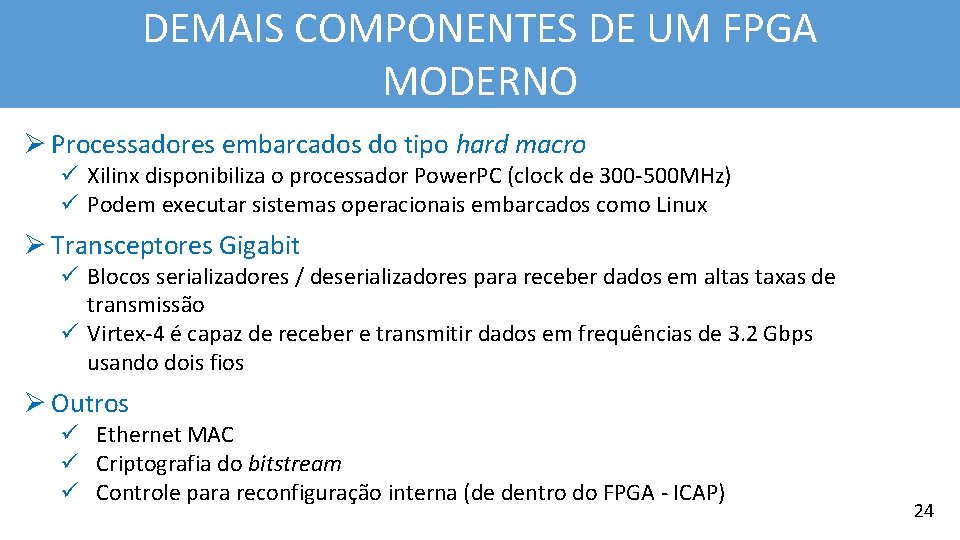

DEMAIS COMPONENTES DE UM FPGA MODERNO Ø Processadores embarcados do tipo hard macro ü Xilinx disponibiliza o processador Power. PC (clock de 300 -500 MHz) ü Podem executar sistemas operacionais embarcados como Linux Ø Transceptores Gigabit ü Blocos serializadores / deserializadores para receber dados em altas taxas de transmissão ü Virtex-4 é capaz de receber e transmitir dados em frequências de 3. 2 Gbps usando dois fios Ø Outros ü Ethernet MAC ü Criptografia do bitstream ü Controle para reconfiguração interna (de dentro do FPGA - ICAP) 24

Um Tutorial de PROTOTIPAÇÃO EM FPGAs Usando a Plataforma Nexys A 7 e o Software Xilinx VIVADO

UTILIZANDO FPGAs PARA PROTOTIPAÇÃO • 1. Inicialmente, garanta que Vivado está instalado e que a placa Nexys A 7 esteja conectada ao seu computador pelo cabo USB desde antes o computador ter sido ligado (por garantia. . . ). Garanta também que a placa está configurada para ser alimentada pela USB (JP 3), configurada para receber bitstreams via JTAG (JP 1) e ligada Abaixo aparece um circuito somador, um dos usados no trabalho T 1, que será prototipado nesta aula (compare com a sua implementação do Projeto 2 daquele trabalho). Abra o Vivado e crie um projeto de nome somador 4 com este arquivo como único fonte sintetizável, conforme visto no tutorial do T 1, sem incluir um testbench library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; --Para permitir soma de std_logic entity somador is port (A, B: in std_logic_vector(3 downto 0); Soma: out std_logic_vector(3 downto 0)); end somador; architecture somador of somador is begin Soma <= A + B; --Soma de dois vetores de 4 bits end somador; 26

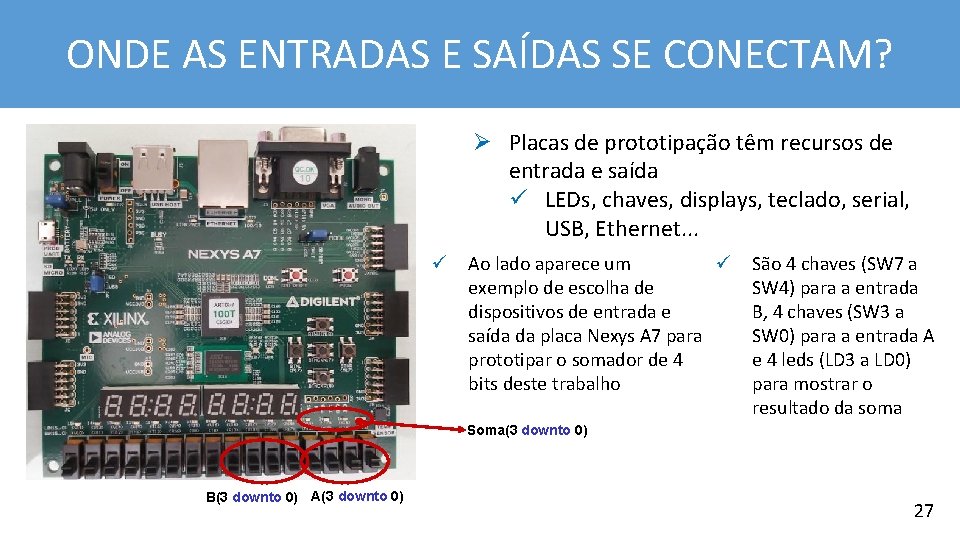

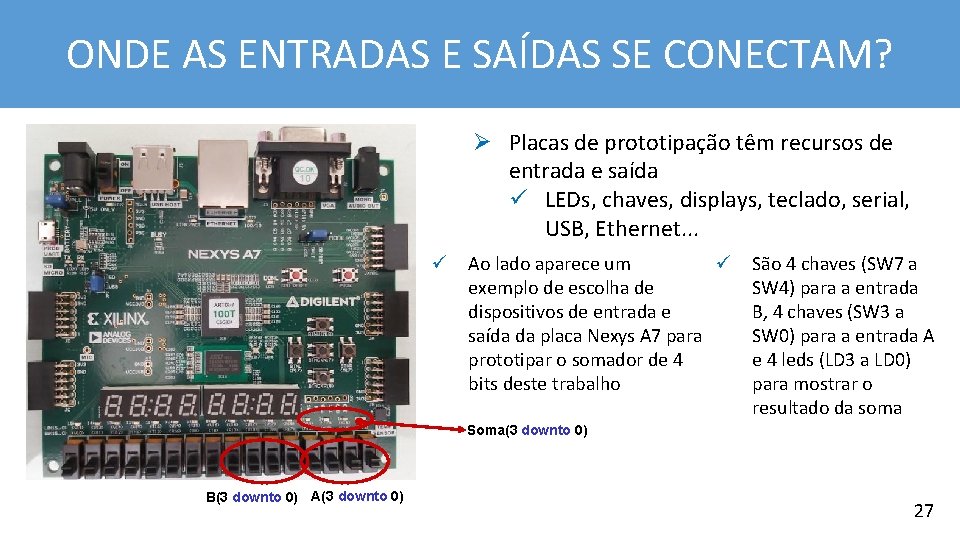

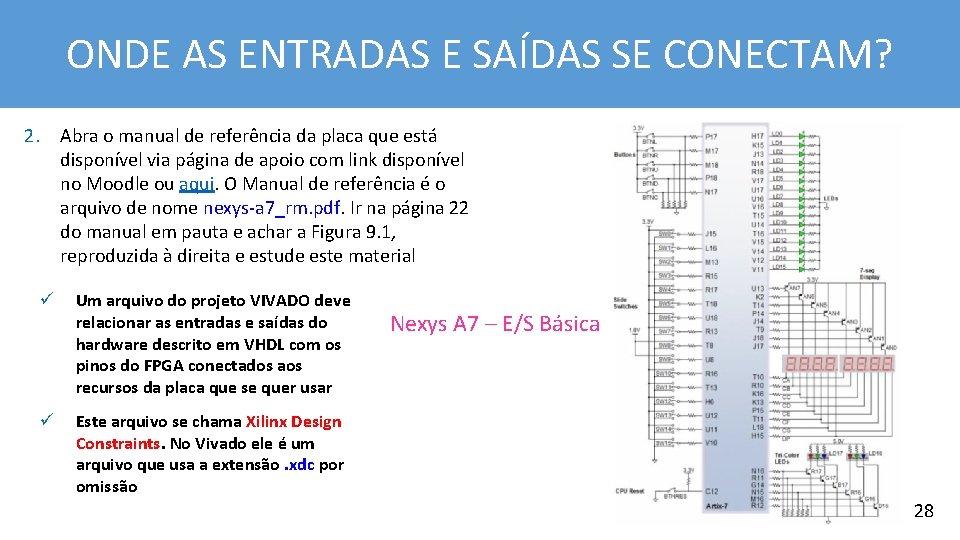

ONDE AS ENTRADAS E SAÍDAS SE CONECTAM? Ø Placas de prototipação têm recursos de entrada e saída ü LEDs, chaves, displays, teclado, serial, USB, Ethernet. . . ü Ao lado aparece um ü São 4 chaves (SW 7 a exemplo de escolha de SW 4) para a entrada dispositivos de entrada e B, 4 chaves (SW 3 a saída da placa Nexys A 7 para SW 0) para a entrada A prototipar o somador de 4 leds (LD 3 a LD 0) bits deste trabalho para mostrar o resultado da soma Soma(3 downto 0) B(3 downto 0) A(3 downto 0) 27

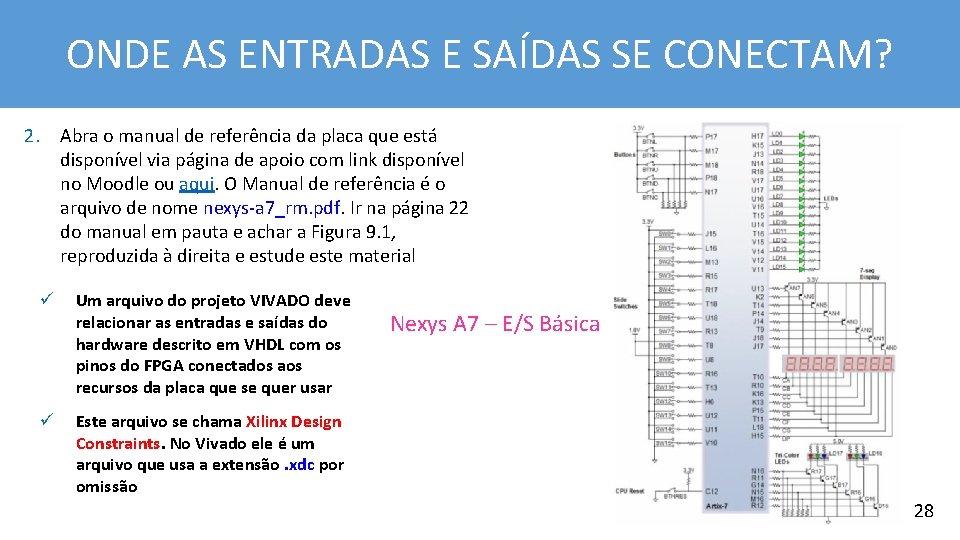

ONDE AS ENTRADAS E SAÍDAS SE CONECTAM? 2. Abra o manual de referência da placa que está disponível via página de apoio com link disponível no Moodle ou aqui. O Manual de referência é o arquivo de nome nexys-a 7_rm. pdf. Ir na página 22 do manual em pauta e achar a Figura 9. 1, reproduzida à direita e estude este material ü Um arquivo do projeto VIVADO deve relacionar as entradas e saídas do hardware descrito em VHDL com os pinos do FPGA conectados aos recursos da placa que se quer usar ü Este arquivo se chama Xilinx Design Constraints. No Vivado ele é um arquivo que usa a extensão. xdc por omissão Nexys A 7 – E/S Básica 28

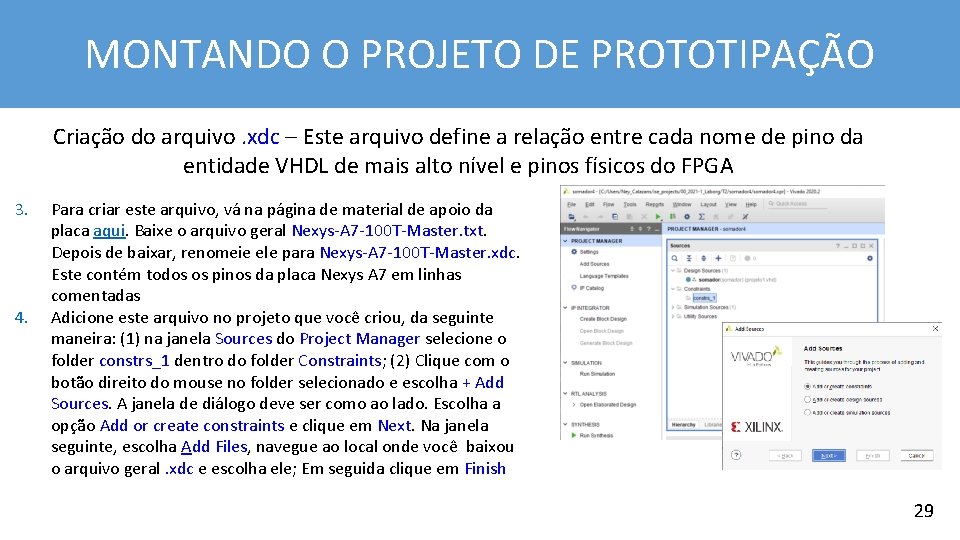

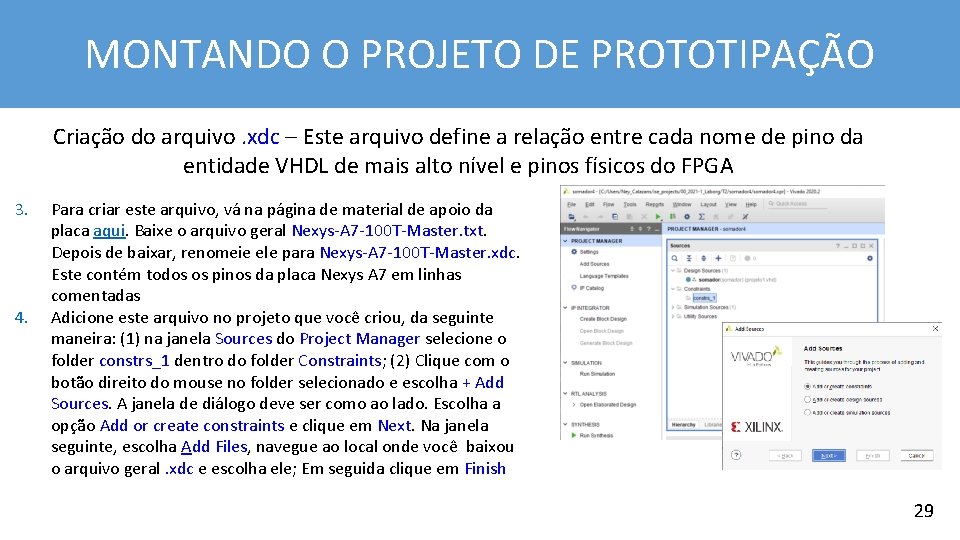

MONTANDO O PROJETO DE PROTOTIPAÇÃO Criação do arquivo. xdc – Este arquivo define a relação entre cada nome de pino da entidade VHDL de mais alto nível e pinos físicos do FPGA 3. 4. Para criar este arquivo, vá na página de material de apoio da placa aqui. Baixe o arquivo geral Nexys-A 7 -100 T-Master. txt. Depois de baixar, renomeie ele para Nexys-A 7 -100 T-Master. xdc. Este contém todos os pinos da placa Nexys A 7 em linhas comentadas Adicione este arquivo no projeto que você criou, da seguinte maneira: (1) na janela Sources do Project Manager selecione o folder constrs_1 dentro do folder Constraints; (2) Clique com o botão direito do mouse no folder selecionado e escolha + Add Sources. A janela de diálogo deve ser como ao lado. Escolha a opção Add or create constraints e clique em Next. Na janela seguinte, escolha Add Files, navegue ao local onde você baixou o arquivo geral. xdc e escolha ele; Em seguida clique em Finish 29

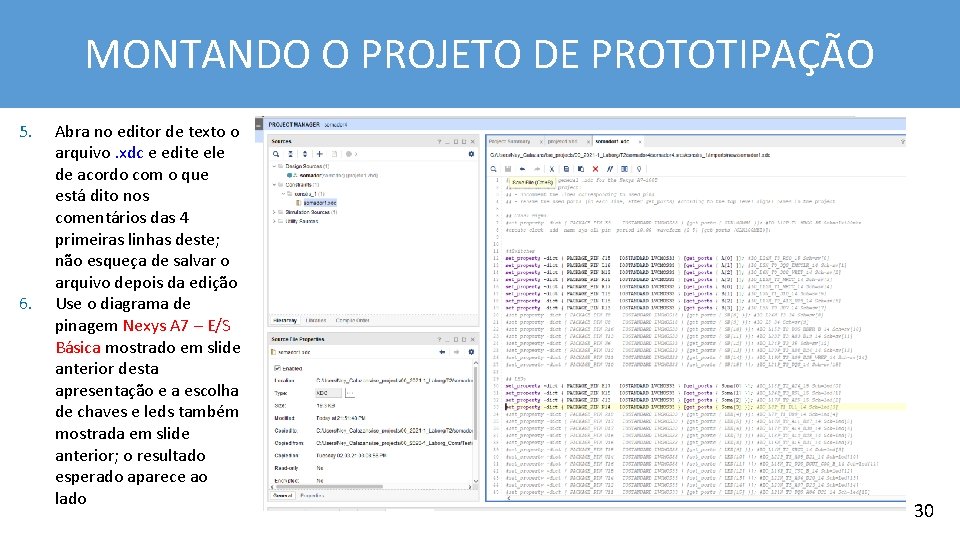

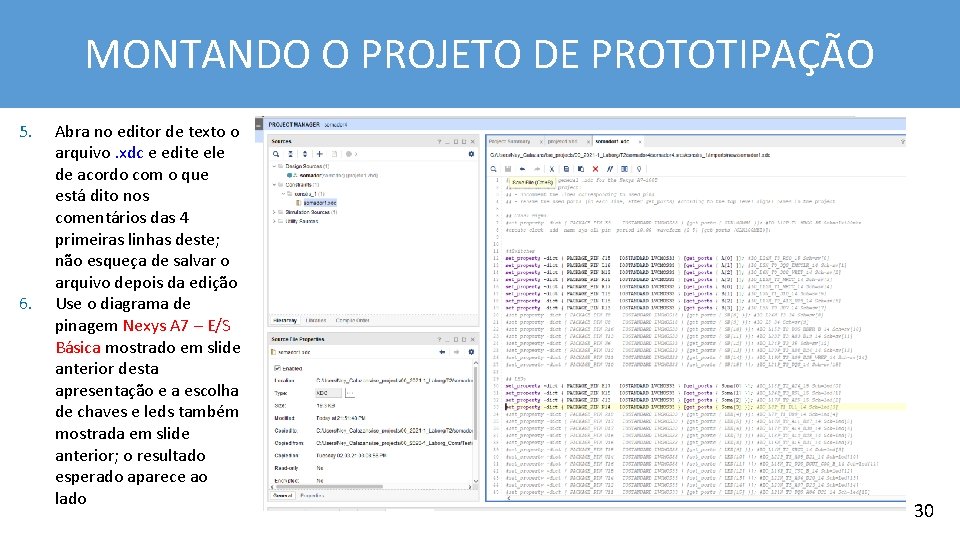

MONTANDO O PROJETO DE PROTOTIPAÇÃO 5. 6. Abra no editor de texto o arquivo. xdc e edite ele de acordo com o que está dito nos comentários das 4 primeiras linhas deste; não esqueça de salvar o arquivo depois da edição Use o diagrama de pinagem Nexys A 7 – E/S Básica mostrado em slide anterior desta apresentação e a escolha de chaves e leds também mostrada em slide anterior; o resultado esperado aparece ao lado 30

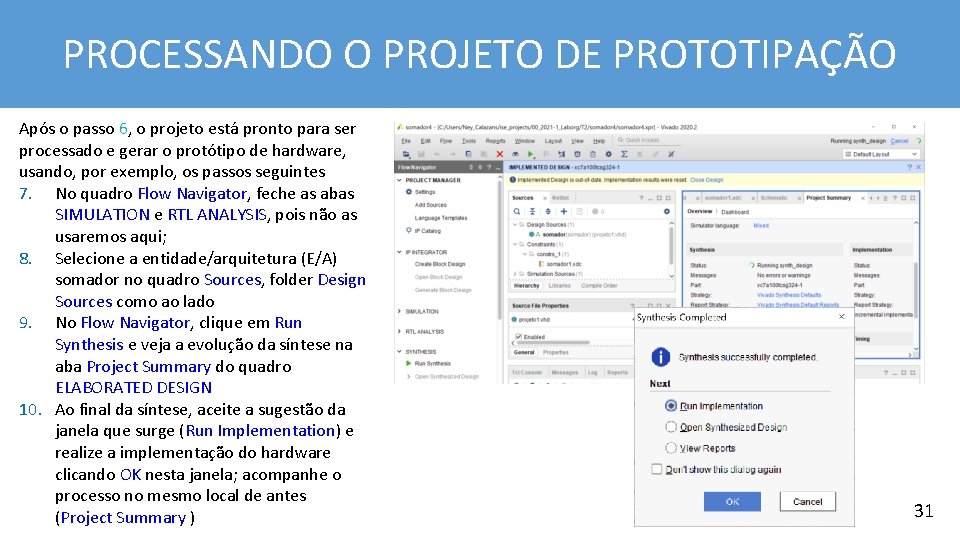

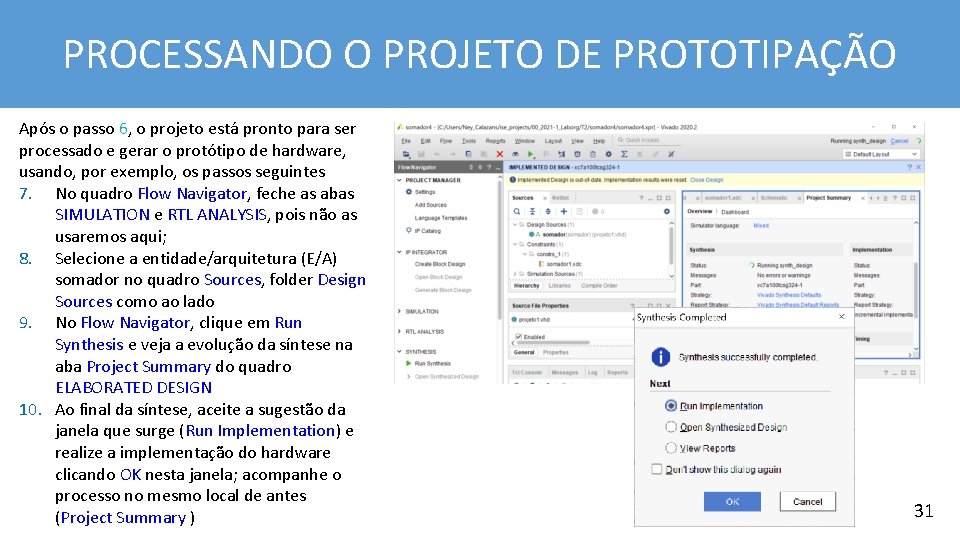

PROCESSANDO O PROJETO DE PROTOTIPAÇÃO Após o passo 6, o projeto está pronto para ser processado e gerar o protótipo de hardware, usando, por exemplo, os passos seguintes 7. No quadro Flow Navigator, feche as abas SIMULATION e RTL ANALYSIS, pois não as usaremos aqui; 8. Selecione a entidade/arquitetura (E/A) somador no quadro Sources, folder Design Sources como ao lado 9. No Flow Navigator, clique em Run Synthesis e veja a evolução da síntese na aba Project Summary do quadro ELABORATED DESIGN 10. Ao final da síntese, aceite a sugestão da janela que surge (Run Implementation) e realize a implementação do hardware clicando OK nesta janela; acompanhe o processo no mesmo local de antes (Project Summary ) 31

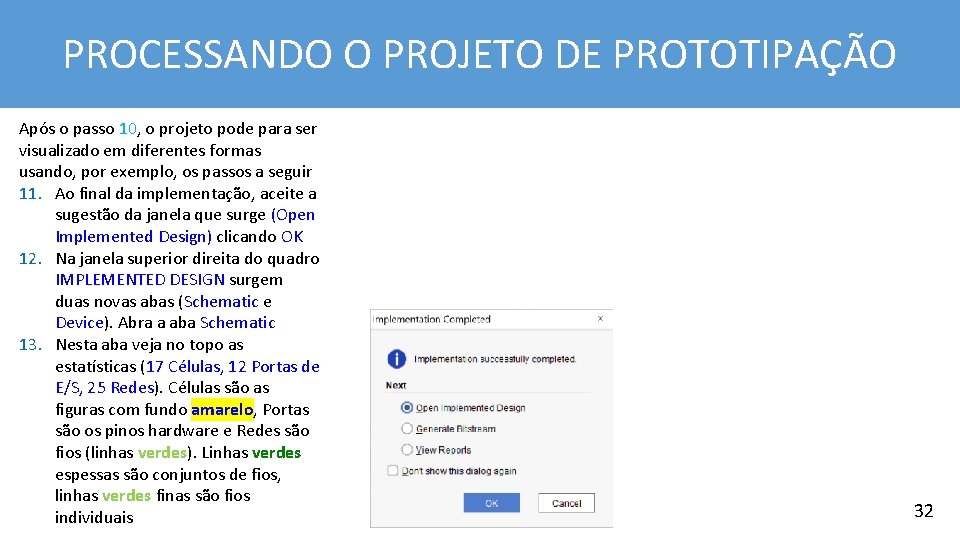

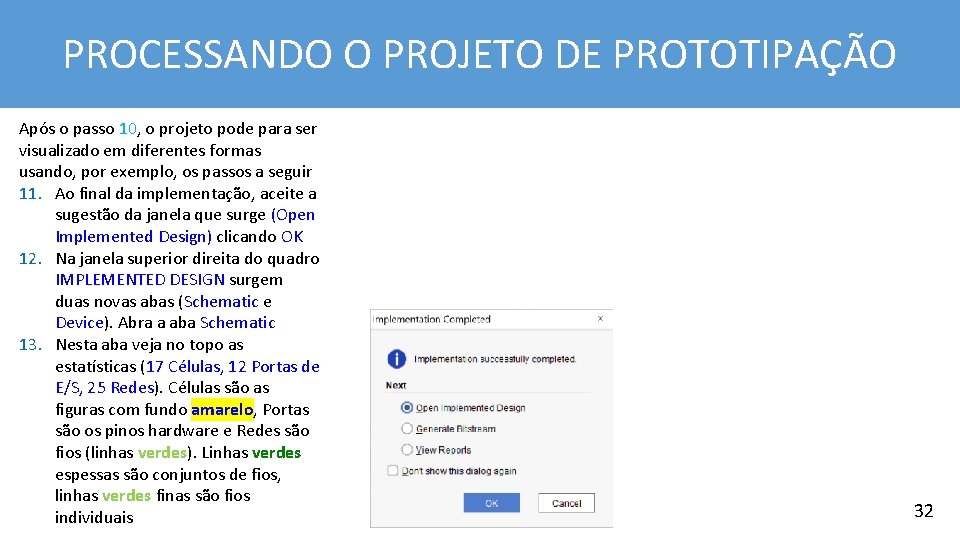

PROCESSANDO O PROJETO DE PROTOTIPAÇÃO Após o passo 10, o projeto pode para ser visualizado em diferentes formas usando, por exemplo, os passos a seguir 11. Ao final da implementação, aceite a sugestão da janela que surge (Open Implemented Design) clicando OK 12. Na janela superior direita do quadro IMPLEMENTED DESIGN surgem duas novas abas (Schematic e Device). Abra a aba Schematic 13. Nesta aba veja no topo as estatísticas (17 Células, 12 Portas de E/S, 25 Redes). Células são as figuras com fundo amarelo, Portas são os pinos hardware e Redes são fios (linhas verdes). Linhas verdes espessas são conjuntos de fios, linhas verdes finas são fios individuais 32

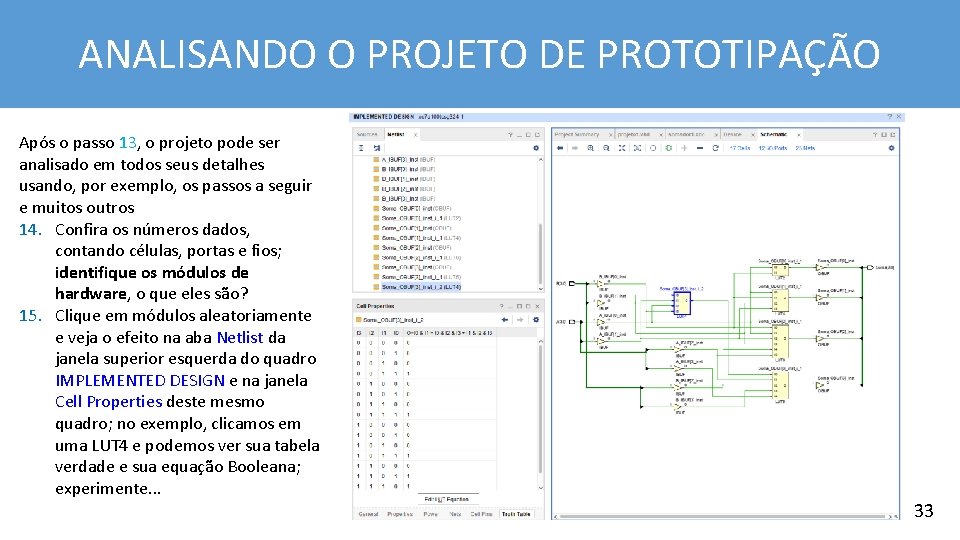

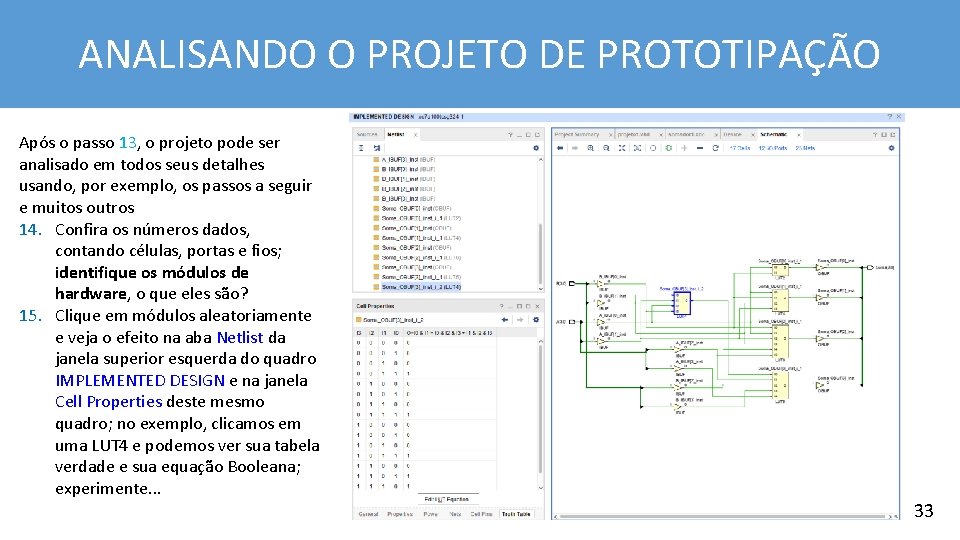

ANALISANDO O PROJETO DE PROTOTIPAÇÃO Após o passo 13, o projeto pode ser analisado em todos seus detalhes usando, por exemplo, os passos a seguir e muitos outros 14. Confira os números dados, contando células, portas e fios; identifique os módulos de hardware, o que eles são? 15. Clique em módulos aleatoriamente e veja o efeito na aba Netlist da janela superior esquerda do quadro IMPLEMENTED DESIGN e na janela Cell Properties deste mesmo quadro; no exemplo, clicamos em uma LUT 4 e podemos ver sua tabela verdade e sua equação Booleana; experimente. . . 33

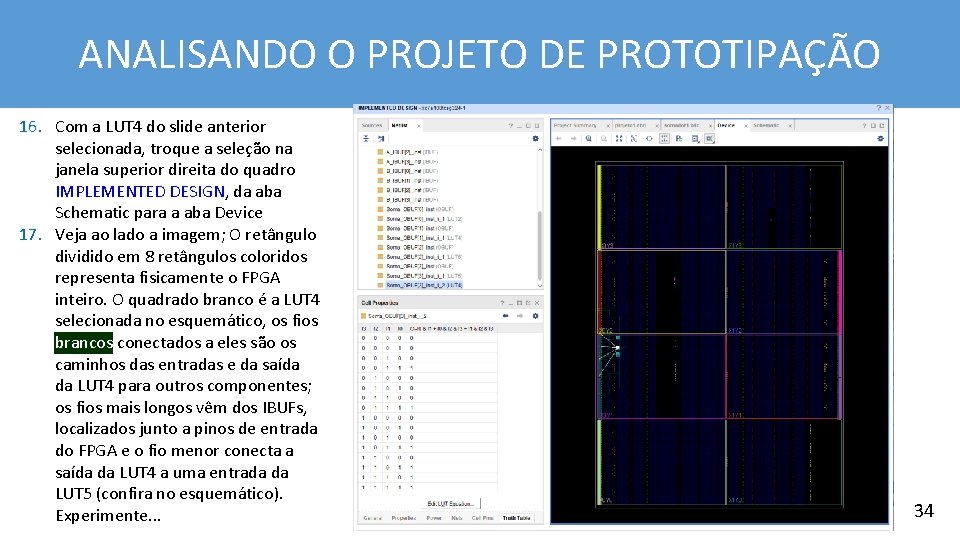

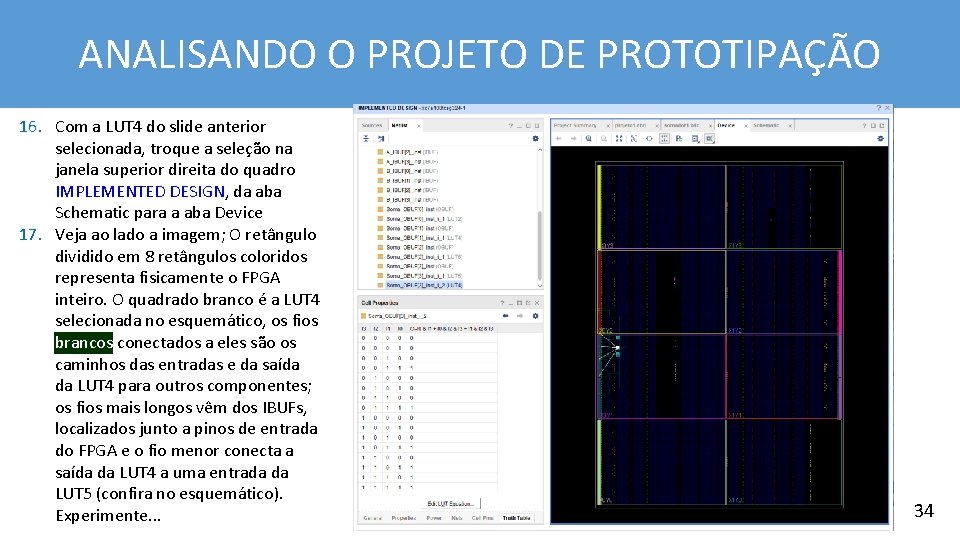

ANALISANDO O PROJETO DE PROTOTIPAÇÃO 16. Com a LUT 4 do slide anterior selecionada, troque a seleção na janela superior direita do quadro IMPLEMENTED DESIGN, da aba Schematic para a aba Device 17. Veja ao lado a imagem; O retângulo dividido em 8 retângulos coloridos representa fisicamente o FPGA inteiro. O quadrado branco é a LUT 4 selecionada no esquemático, os fios brancos conectados a eles são os caminhos das entradas e da saída da LUT 4 para outros componentes; os fios mais longos vêm dos IBUFs, localizados junto a pinos de entrada do FPGA e o fio menor conecta a saída da LUT 4 a uma entrada da LUT 5 (confira no esquemático). Experimente. . . 34

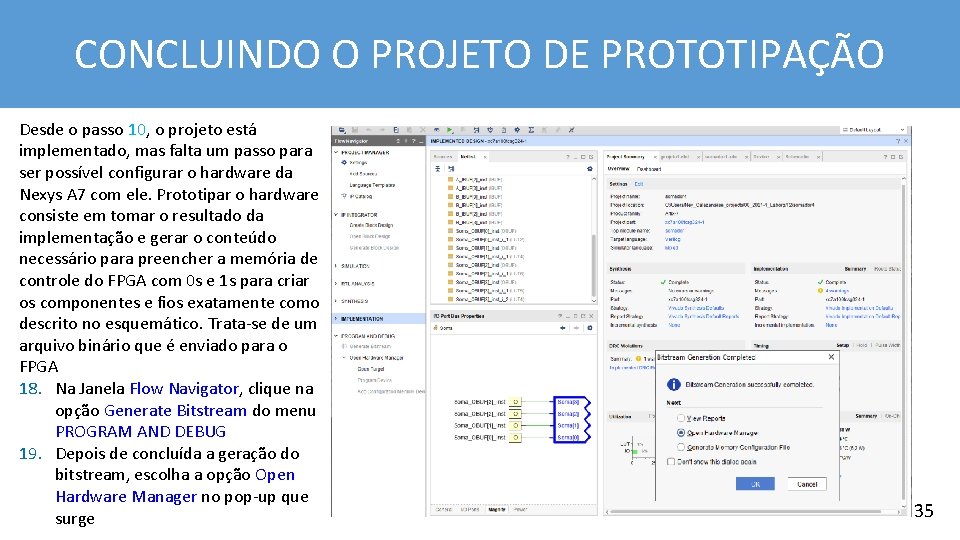

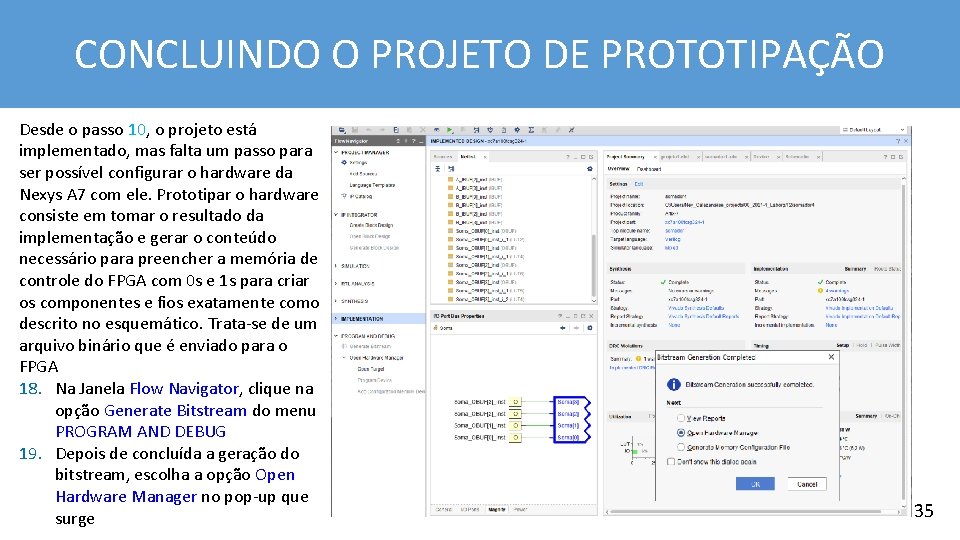

CONCLUINDO O PROJETO DE PROTOTIPAÇÃO Desde o passo 10, o projeto está implementado, mas falta um passo para ser possível configurar o hardware da Nexys A 7 com ele. Prototipar o hardware consiste em tomar o resultado da implementação e gerar o conteúdo necessário para preencher a memória de controle do FPGA com 0 s e 1 s para criar os componentes e fios exatamente como descrito no esquemático. Trata-se de um arquivo binário que é enviado para o FPGA 18. Na Janela Flow Navigator, clique na opção Generate Bitstream do menu PROGRAM AND DEBUG 19. Depois de concluída a geração do bitstream, escolha a opção Open Hardware Manager no pop-up que surge 35

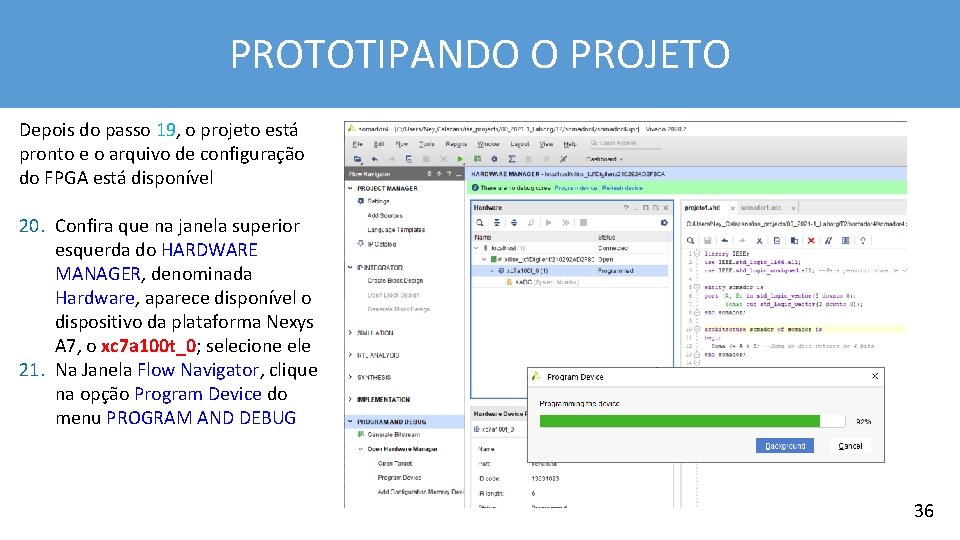

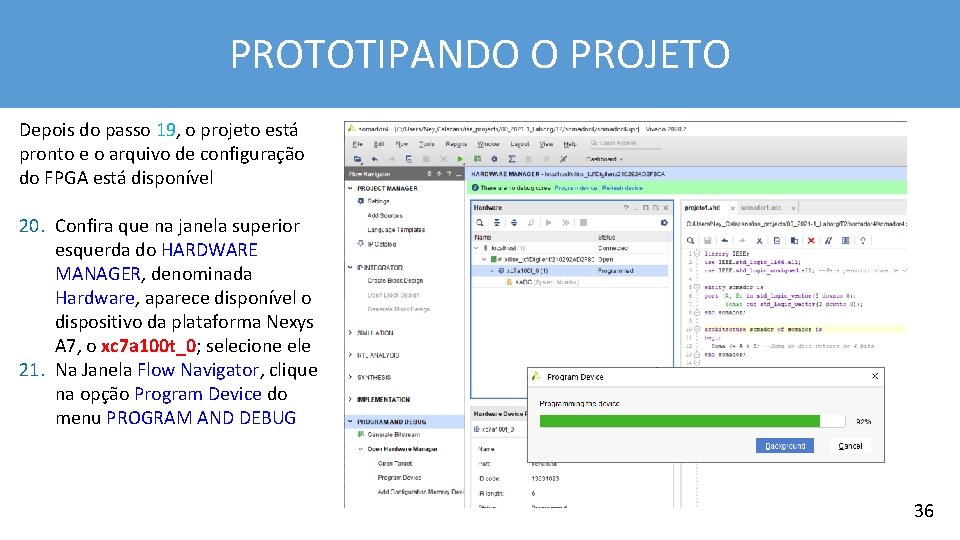

PROTOTIPANDO O PROJETO Depois do passo 19, o projeto está pronto e o arquivo de configuração do FPGA está disponível 20. Confira que na janela superior esquerda do HARDWARE MANAGER, denominada Hardware, aparece disponível o dispositivo da plataforma Nexys A 7, o xc 7 a 100 t_0; selecione ele 21. Na Janela Flow Navigator, clique na opção Program Device do menu PROGRAM AND DEBUG 36

TESTANDO O PROJETO Depois do passo 21, o projeto está pronto para ser testado na placa 22. Confira que seu projeto funciona. Cuidados: revise que foram respeitados os cuidados prévios previsto no primeiro slide deste tutorial (item antes do passo 1) 23. Veja ao lado um exemplo de operação correta do hardware somador de 4 bits: A(0010) + B(0011) = SOMA (0101). Em decimal, 2+3=5. A corresponde às 4 chaves SW 3 a SW 0, B às 4 chaves SW 7 a SW 4 e SOMA aos leds LD 3 a LD 0. As convenções são: Chave para baixo é 0 e chave para cima é 1. Led desligado é 0 e led ligado é 1 37

TRABALHO T 2

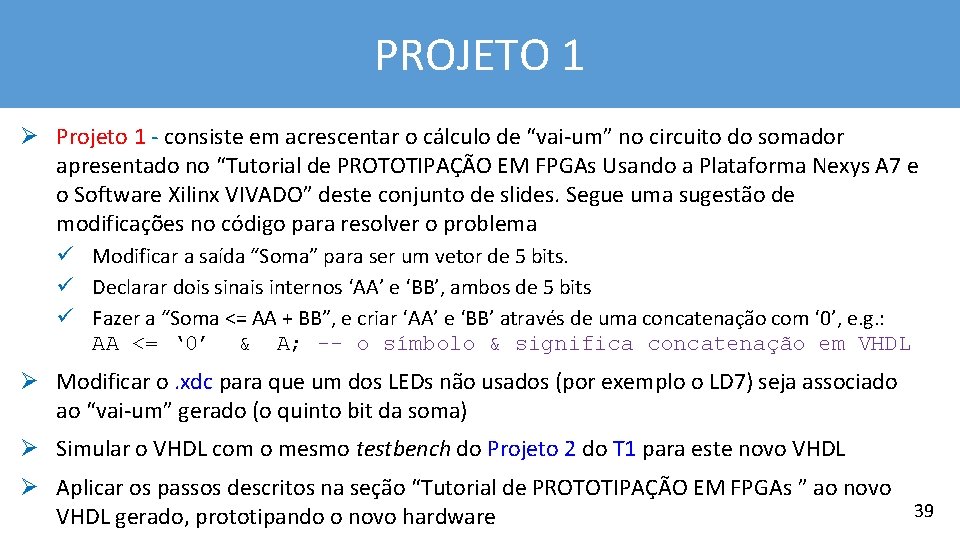

PROJETO 1 Ø Projeto 1 - consiste em acrescentar o cálculo de “vai-um” no circuito do somador apresentado no “Tutorial de PROTOTIPAÇÃO EM FPGAs Usando a Plataforma Nexys A 7 e o Software Xilinx VIVADO” deste conjunto de slides. Segue uma sugestão de modificações no código para resolver o problema ü Modificar a saída “Soma” para ser um vetor de 5 bits. ü Declarar dois sinais internos ‘AA’ e ‘BB’, ambos de 5 bits ü Fazer a “Soma <= AA + BB”, e criar ‘AA’ e ‘BB’ através de uma concatenação com ‘ 0’, e. g. : AA <= ‘ 0’ & A; -- o símbolo & significa concatenação em VHDL Ø Modificar o. xdc para que um dos LEDs não usados (por exemplo o LD 7) seja associado ao “vai-um” gerado (o quinto bit da soma) Ø Simular o VHDL com o mesmo testbench do Projeto 2 do T 1 para este novo VHDL Ø Aplicar os passos descritos na seção “Tutorial de PROTOTIPAÇÃO EM FPGAs ” ao novo 39 VHDL gerado, prototipando o novo hardware

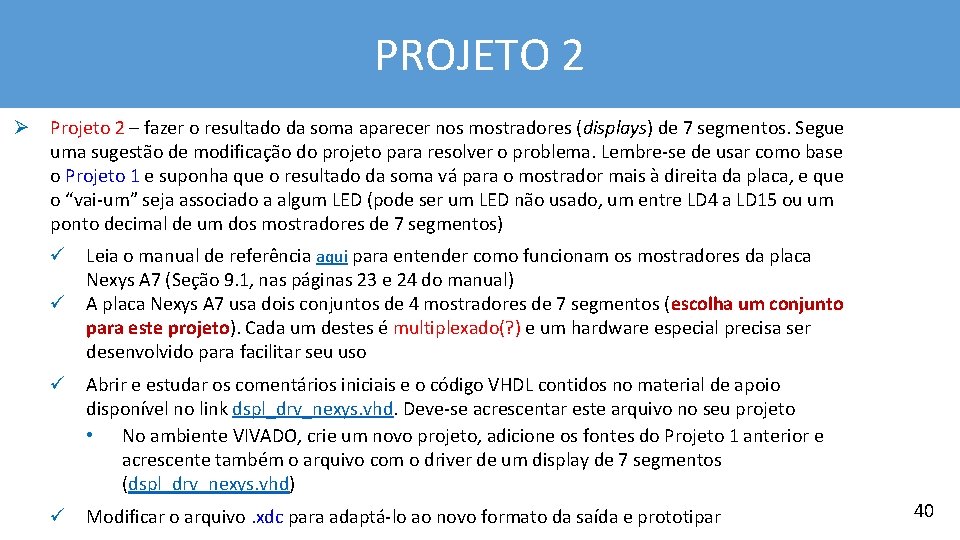

PROJETO 2 Ø Projeto 2 – fazer o resultado da soma aparecer nos mostradores (displays) de 7 segmentos. Segue uma sugestão de modificação do projeto para resolver o problema. Lembre-se de usar como base o Projeto 1 e suponha que o resultado da soma vá para o mostrador mais à direita da placa, e que o “vai-um” seja associado a algum LED (pode ser um LED não usado, um entre LD 4 a LD 15 ou um ponto decimal de um dos mostradores de 7 segmentos) ü Leia o manual de referência aqui para entender como funcionam os mostradores da placa Nexys A 7 (Seção 9. 1, nas páginas 23 e 24 do manual) ü A placa Nexys A 7 usa dois conjuntos de 4 mostradores de 7 segmentos (escolha um conjunto para este projeto). Cada um destes é multiplexado(? ) e um hardware especial precisa ser desenvolvido para facilitar seu uso ü Abrir e estudar os comentários iniciais e o código VHDL contidos no material de apoio disponível no link dspl_drv_nexys. vhd. Deve-se acrescentar este arquivo no seu projeto • No ambiente VIVADO, crie um novo projeto, adicione os fontes do Projeto 1 anterior e acrescente também o arquivo com o driver de um display de 7 segmentos (dspl_drv_nexys. vhd) ü Modificar o arquivo. xdc para adaptá-lo ao novo formato da saída e prototipar 40

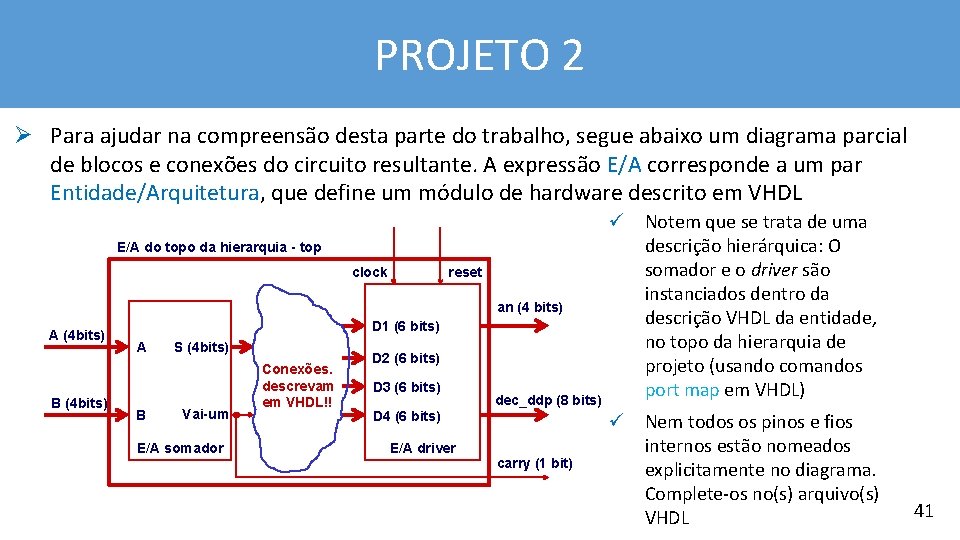

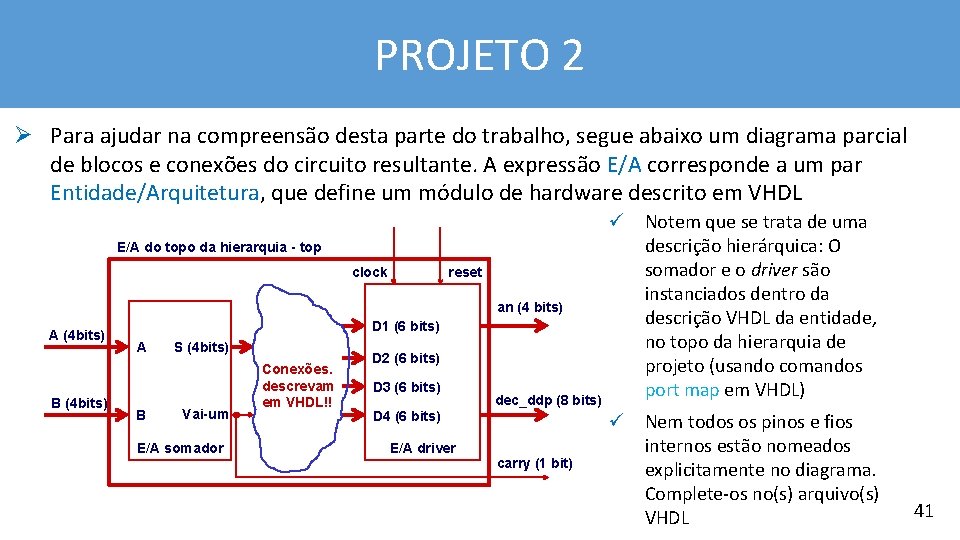

PROJETO 2 Ø Para ajudar na compreensão desta parte do trabalho, segue abaixo um diagrama parcial de blocos e conexões do circuito resultante. A expressão E/A corresponde a um par Entidade/Arquitetura, que define um módulo de hardware descrito em VHDL E/A do topo da hierarquia - top clock reset an (4 bits) A (4 bits) B (4 bits) D 1 (6 bits) A B S (4 bits) Vai-um E/A somador Conexões. descrevam em VHDL!! D 2 (6 bits) D 3 (6 bits) dec_ddp (8 bits) D 4 (6 bits) E/A driver carry (1 bit) ü Notem que se trata de uma descrição hierárquica: O somador e o driver são instanciados dentro da descrição VHDL da entidade, no topo da hierarquia de projeto (usando comandos port map em VHDL) ü Nem todos os pinos e fios internos estão nomeados explicitamente no diagrama. Complete-os no(s) arquivo(s) VHDL 41

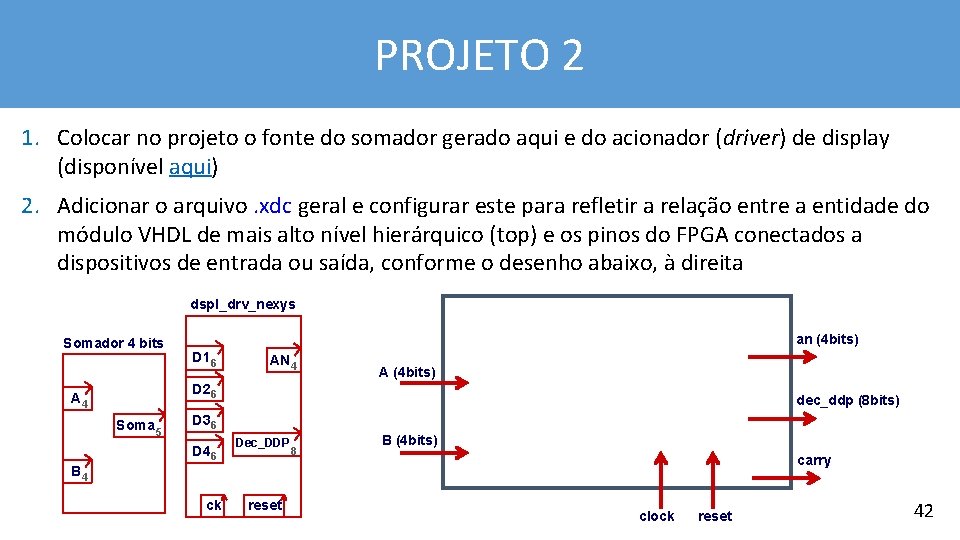

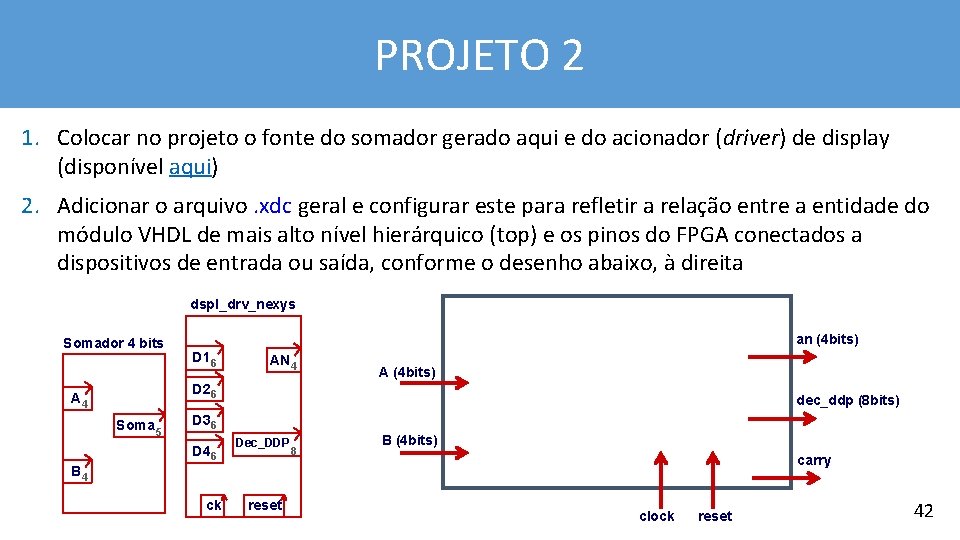

PROJETO 2 1. Colocar no projeto o fonte do somador gerado aqui e do acionador (driver) de display (disponível aqui) 2. Adicionar o arquivo. xdc geral e configurar este para refletir a relação entre a entidade do módulo VHDL de mais alto nível hierárquico (top) e os pinos do FPGA conectados a dispositivos de entrada ou saída, conforme o desenho abaixo, à direita dspl_drv_nexys Somador 4 bits an (4 bits) D 16 AN 4 A (4 bits) D 26 A 4 Soma 5 dec_ddp (8 bits) D 36 D 46 Dec_DDP 8 B (4 bits) carry B 4 ck reset clock reset 42

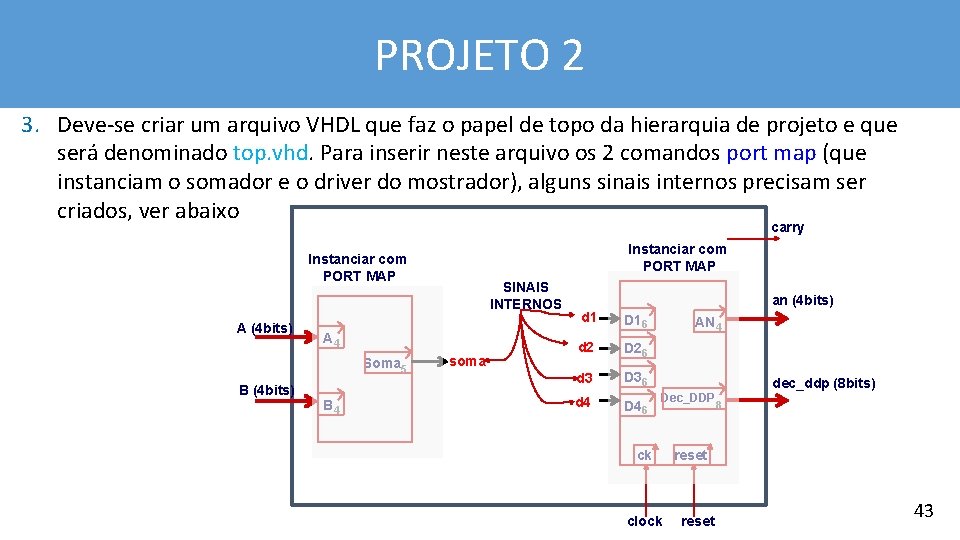

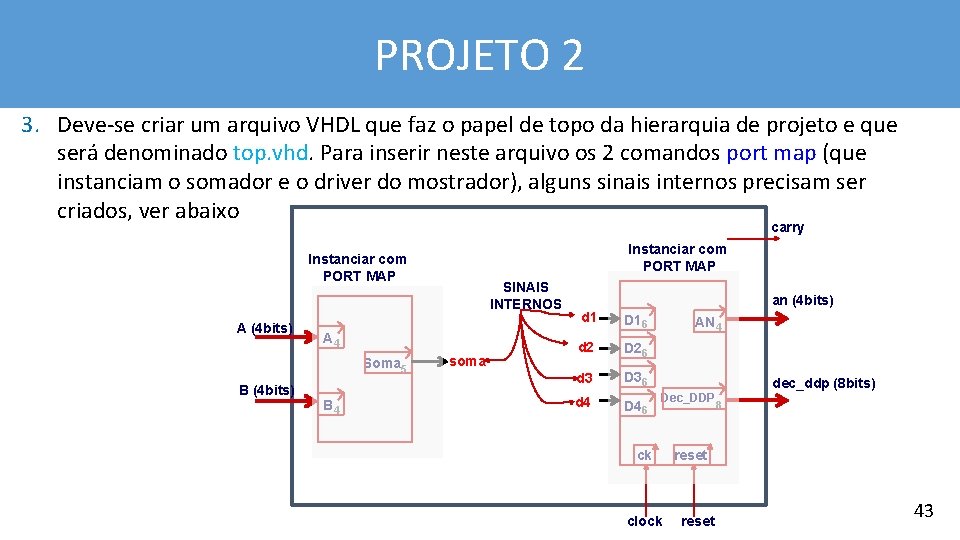

PROJETO 2 3. Deve-se criar um arquivo VHDL que faz o papel de topo da hierarquia de projeto e que será denominado top. vhd. Para inserir neste arquivo os 2 comandos port map (que instanciam o somador e o driver do mostrador), alguns sinais internos precisam ser criados, ver abaixo carry Instanciar com PORT MAP A (4 bits) A 4 Soma 5 B (4 bits) SINAIS INTERNOS B 4 soma an (4 bits) d 1 D 16 d 2 D 26 d 3 D 36 d 4 D 46 AN 4 dec_ddp (8 bits) Dec_DDP ck clock 8 reset 43

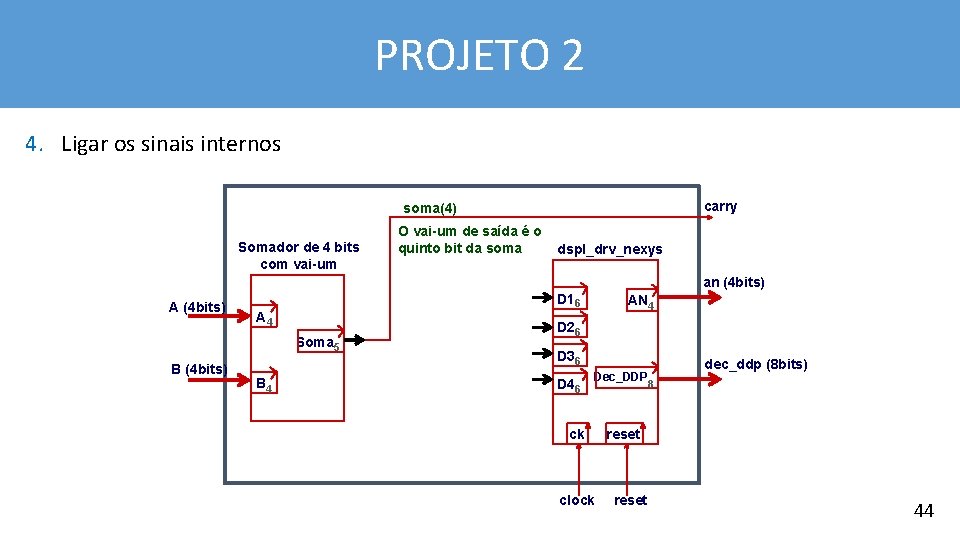

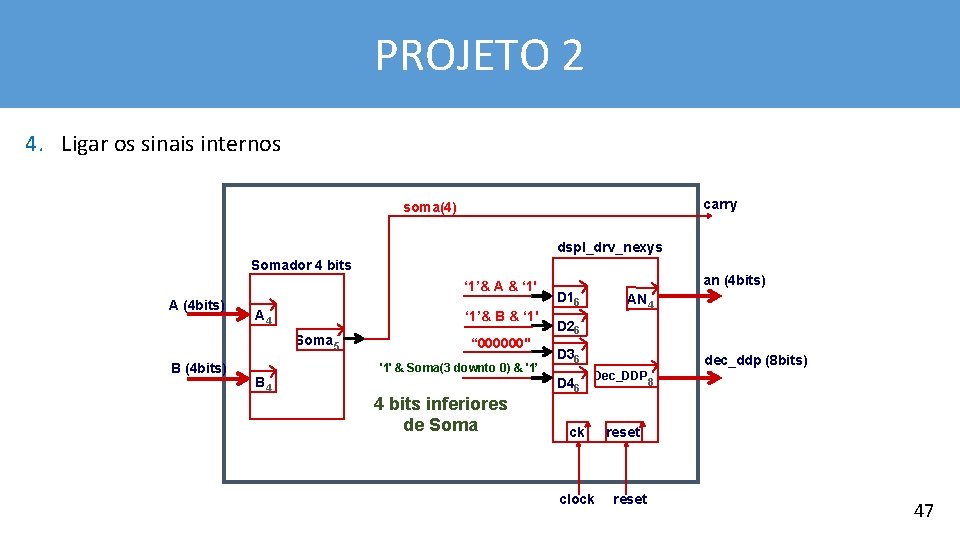

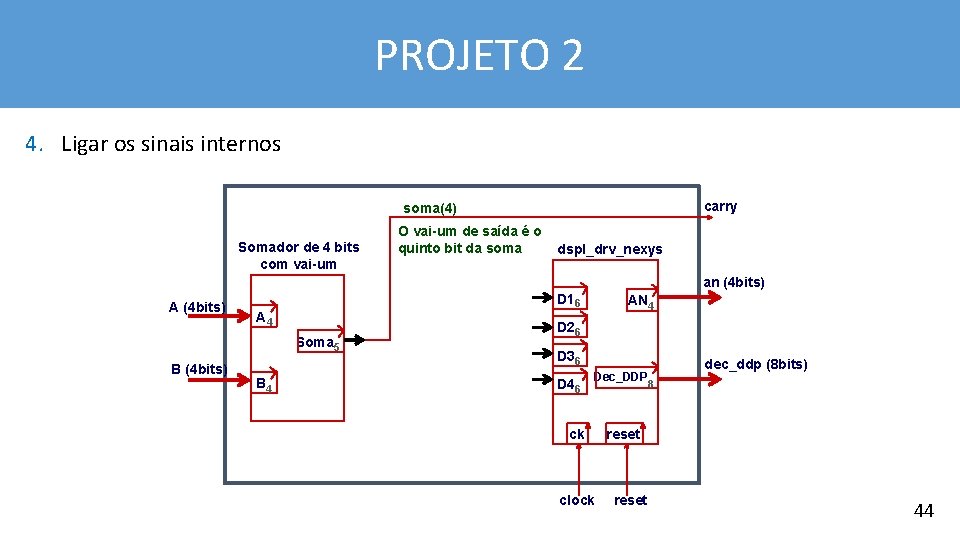

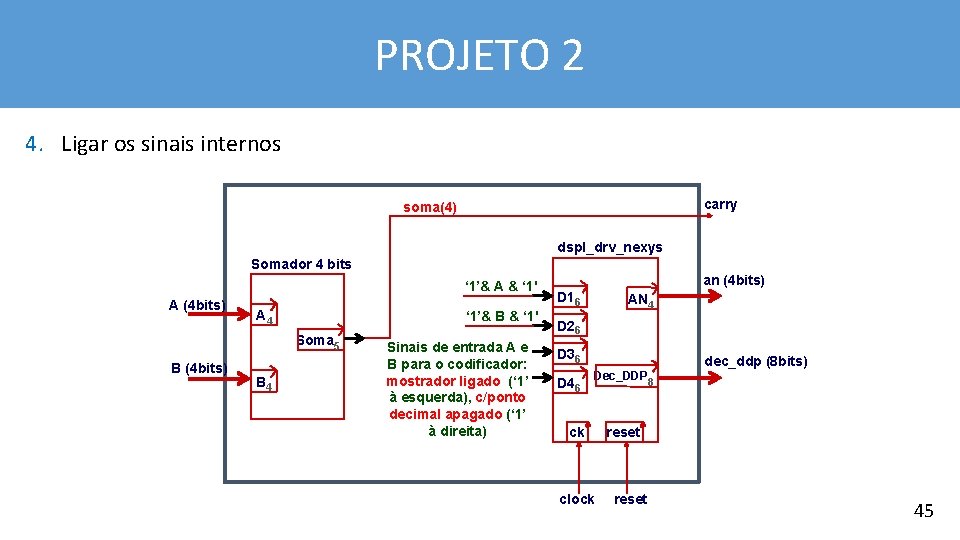

PROJETO 2 4. Ligar os sinais internos carry soma(4) Somador de 4 bits com vai-um O vai-um de saída é o quinto bit da soma dspl_drv_nexys an (4 bits) A (4 bits) D 16 A 4 Soma 5 B (4 bits) B 4 AN 4 D 26 D 36 D 46 Dec_DDP ck clock dec_ddp (8 bits) 8 reset 44

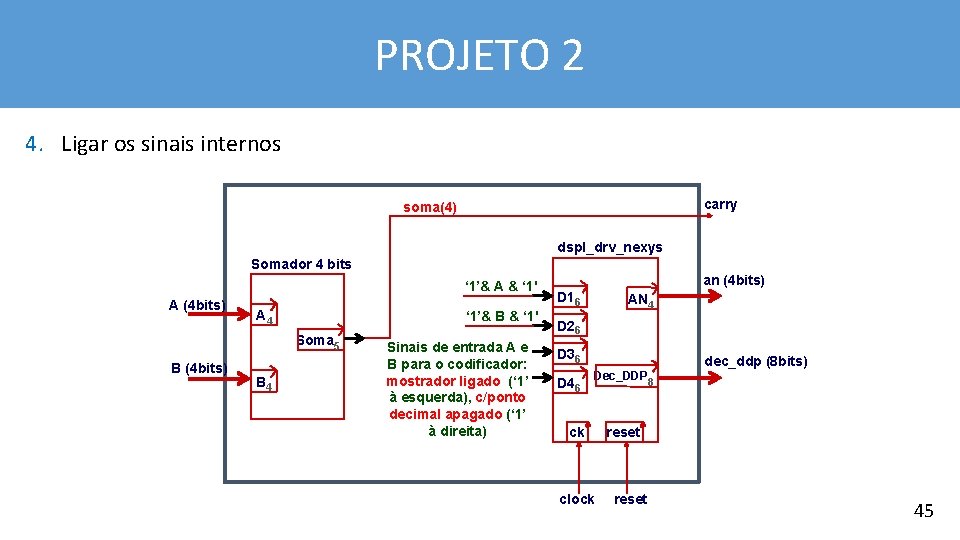

PROJETO 2 4. Ligar os sinais internos carry soma(4) dspl_drv_nexys Somador 4 bits ‘ 1’& A & ‘ 1' A (4 bits) A 4 ‘ 1’& B & ‘ 1' Soma 5 B (4 bits) B 4 Sinais de entrada A e B para o codificador: mostrador ligado (‘ 1’ à esquerda), c/ponto decimal apagado (‘ 1’ à direita) an (4 bits) D 16 AN 4 D 26 D 36 D 46 Dec_DDP ck clock dec_ddp (8 bits) 8 reset 45

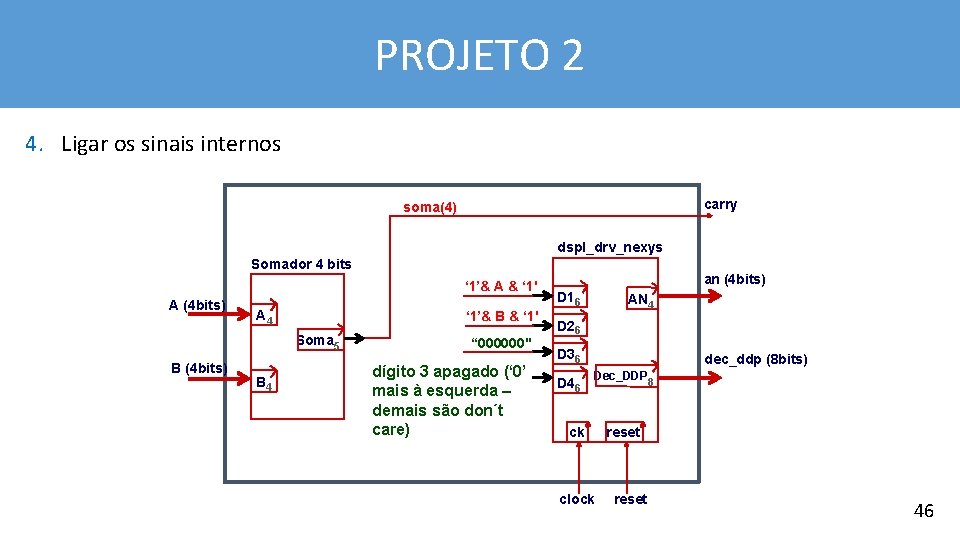

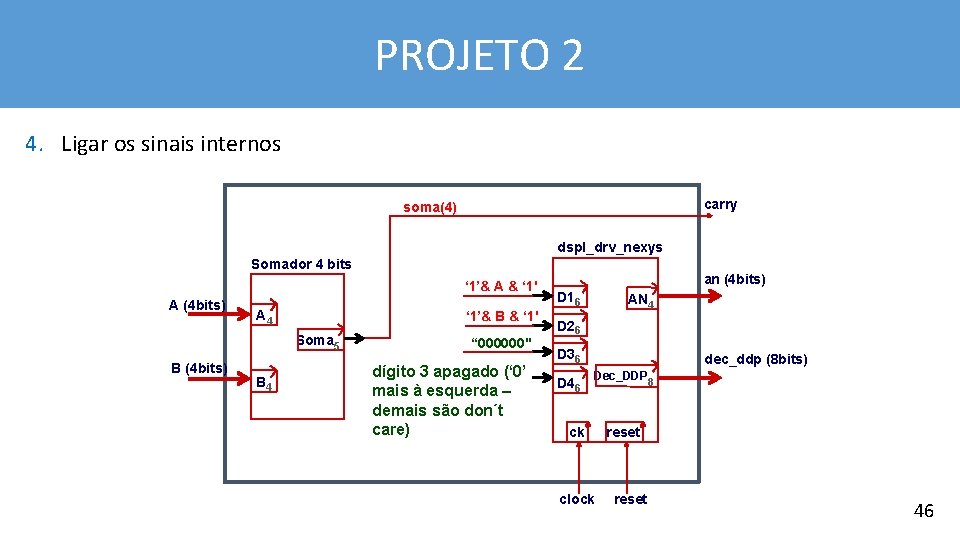

PROJETO 2 4. Ligar os sinais internos carry soma(4) dspl_drv_nexys Somador 4 bits ‘ 1’& A & ‘ 1' A (4 bits) A 4 ‘ 1’& B & ‘ 1' Soma 5 B (4 bits) B 4 “ 000000" dígito 3 apagado (‘ 0’ mais à esquerda – demais são don´t care) an (4 bits) D 16 AN 4 D 26 D 36 D 46 dec_ddp (8 bits) Dec_DDP ck clock 8 reset 46

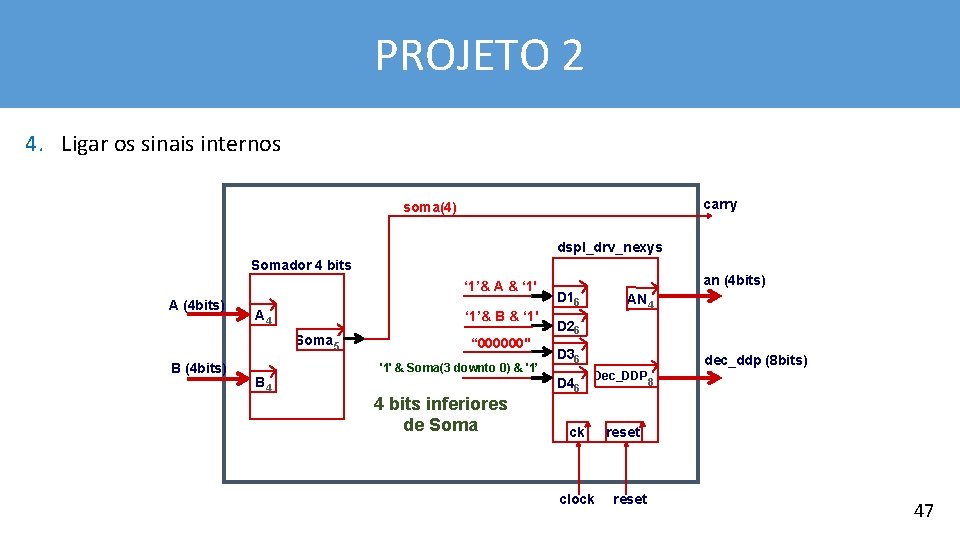

PROJETO 2 4. Ligar os sinais internos carry soma(4) dspl_drv_nexys Somador 4 bits ‘ 1’& A & ‘ 1' A (4 bits) A 4 ‘ 1’& B & ‘ 1' Soma 5 B (4 bits) B 4 “ 000000" '1' & Soma(3 downto 0) & '1’ 4 bits inferiores de Soma an (4 bits) D 16 AN 4 D 26 D 36 D 46 dec_ddp (8 bits) Dec_DDP ck clock 8 reset 47

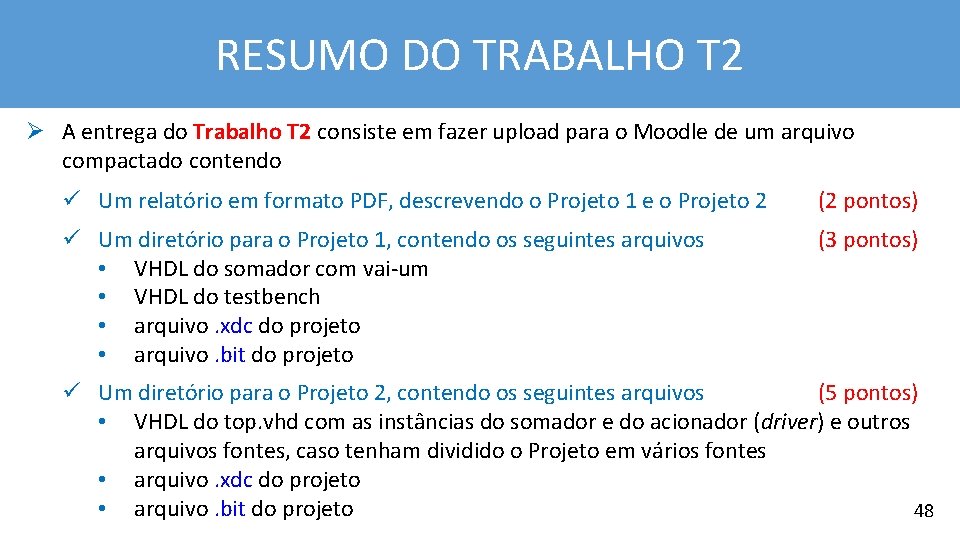

RESUMO DO TRABALHO T 2 Ø A entrega do Trabalho T 2 consiste em fazer upload para o Moodle de um arquivo compactado contendo ü Um relatório em formato PDF, descrevendo o Projeto 1 e o Projeto 2 (2 pontos) ü Um diretório para o Projeto 1, contendo os seguintes arquivos • VHDL do somador com vai-um • VHDL do testbench • arquivo. xdc do projeto • arquivo. bit do projeto (3 pontos) ü Um diretório para o Projeto 2, contendo os seguintes arquivos (5 pontos) • VHDL do top. vhd com as instâncias do somador e do acionador (driver) e outros arquivos fontes, caso tenham dividido o Projeto em vários fontes • arquivo. xdc do projeto • arquivo. bit do projeto 48