Politecnico di Milano Implementazione di un Architettura Sicura

- Slides: 16

Politecnico di Milano Implementazione di un Architettura Sicura per l’AES Relatore: Luca Breveglieri 27 Luglio 2006 Milano Motta Francesco 653571 Nazzari Davide 652171

Sommario Obiettivi AES Architettura Rilevazione D’Attacco Occupazione FPGA Risultati Conclusioni e Sviluppi Futuri 2

Obiettivi Proporre l’implementazione di un’architettura per l’AES capace di riconfigurasi in caso di attacco esterno, riscontrato tramite l’utilizzo della rilevazione d’errore. 3

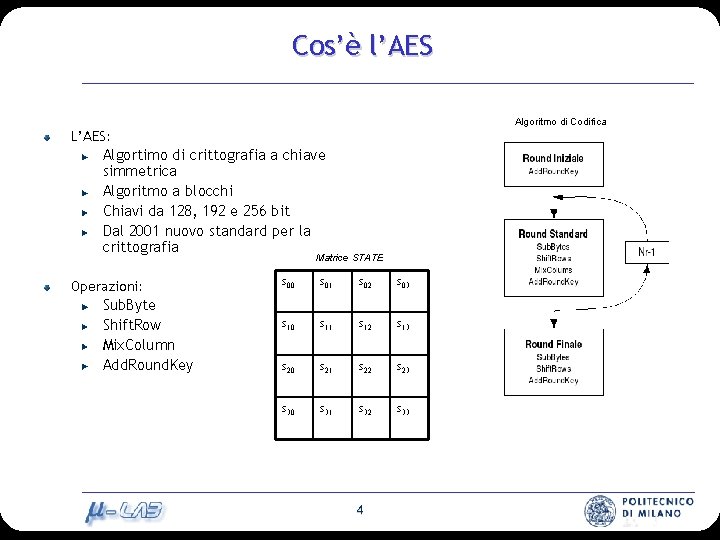

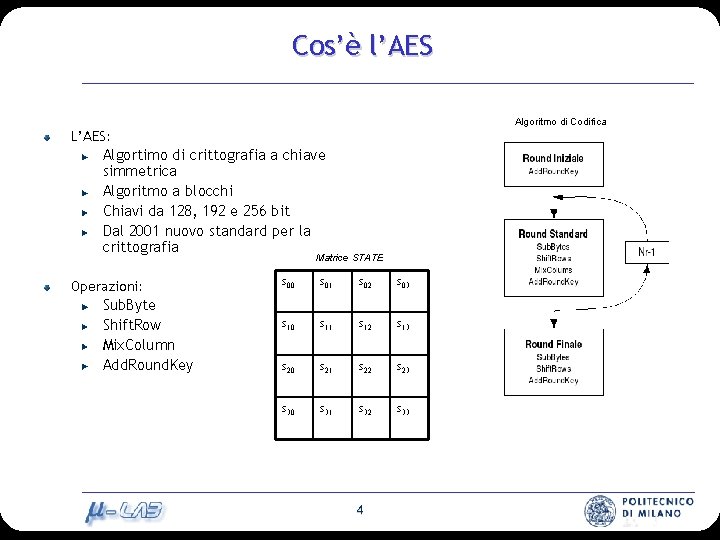

Cos’è l’AES Algoritmo di Codifica L’AES: Algortimo di crittografia a chiave simmetrica Algoritmo a blocchi Chiavi da 128, 192 e 256 bit Dal 2001 nuovo standard per la crittografia Matrice STATE Operazioni: Sub. Byte Shift. Row Mix. Column Add. Round. Key s 00 s 01 s 02 s 03 s 10 s 11 s 12 s 13 s 20 s 21 s 22 s 23 s 30 s 31 s 32 s 33 4

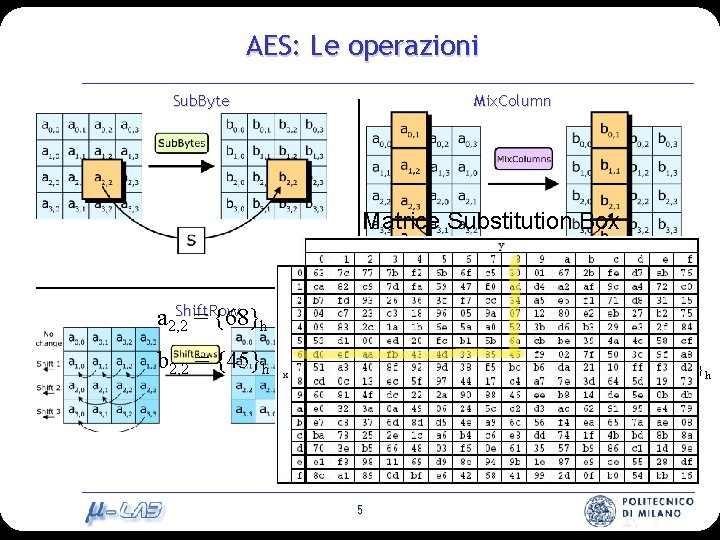

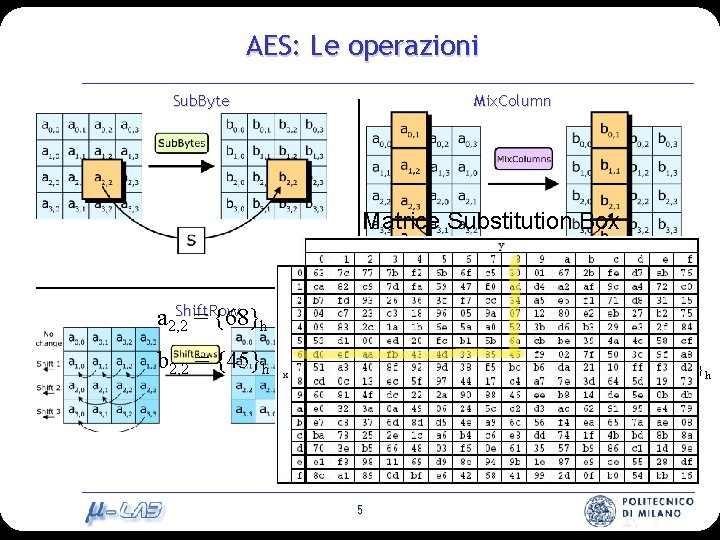

AES: Le operazioni Sub. Byte Mix. Column Matrice Substitution Box Shift. Row a 2, 2 = {68}h Add. Round. Key ac(x) = (ac, r) · x 3 + (ac, r) · x 2 + (ac, r) · x + (ac, r) b 2, 2 = {45}h c(x) = {03}h · x 3 + {01}h · x 2 + {01}h · x + {02}h b(x) = [ac(x) · c(x)] mod (x 4 -1) 5

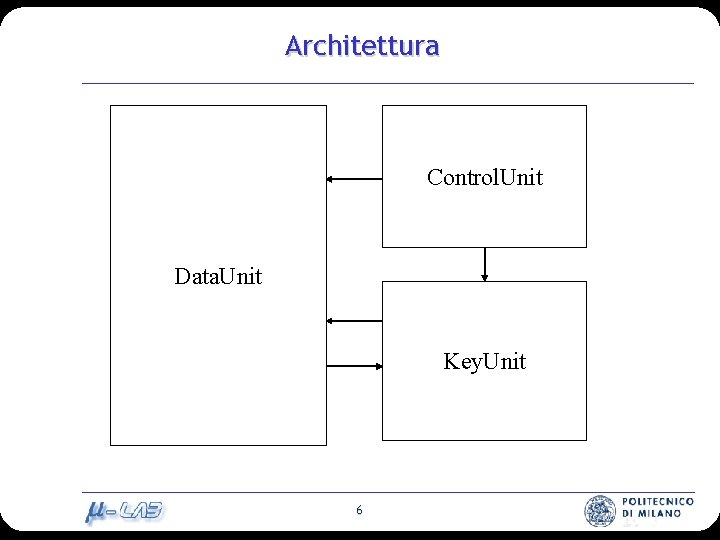

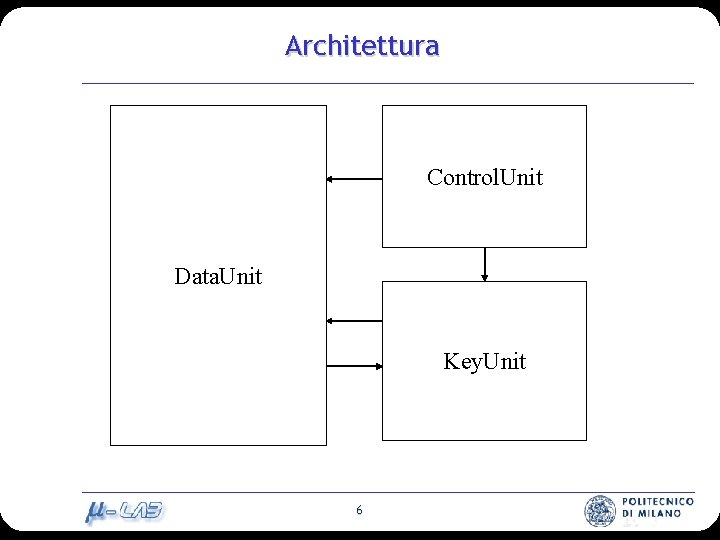

Architettura Control. Unit Data. Unit Key. Unit 6

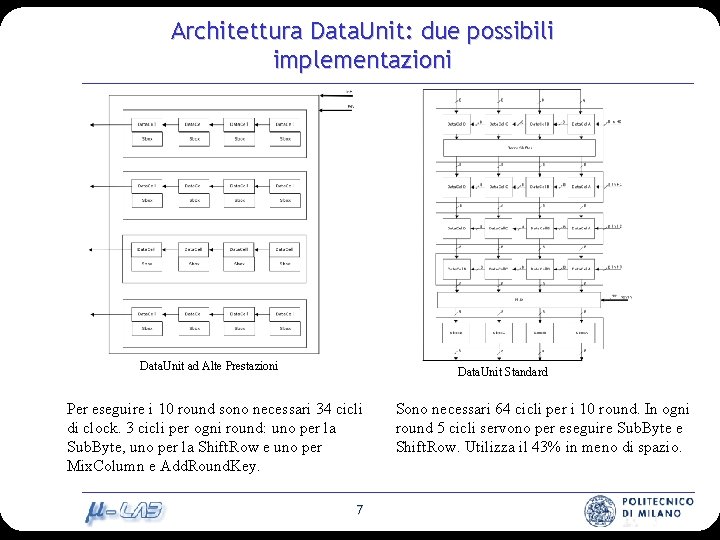

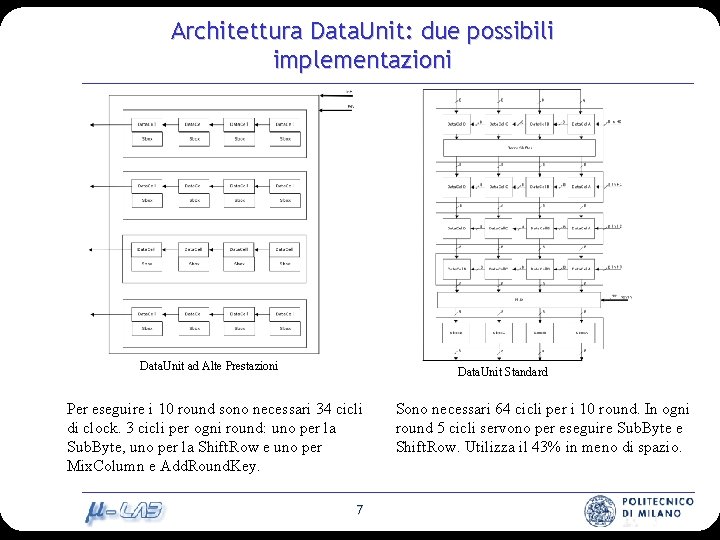

Architettura Data. Unit: due possibili implementazioni Data. Unit ad Alte Prestazioni Data. Unit Standard Per eseguire i 10 round sono necessari 34 cicli di clock. 3 cicli per ogni round: uno per la Sub. Byte, uno per la Shift. Row e uno per Mix. Column e Add. Round. Key. 7 Sono necessari 64 cicli per i 10 round. In ogni round 5 cicli servono per eseguire Sub. Byte e Shift. Row. Utilizza il 43% in meno di spazio.

Attacchi Ad oggi non è stato ancora violato Esistono nuovi tipi di attacco potenzialmente pericolosi ESISTONO NUOVI TIPI DI ATTACCHI POTENZIALMENTE PERICOLOSI Optical Attack 8

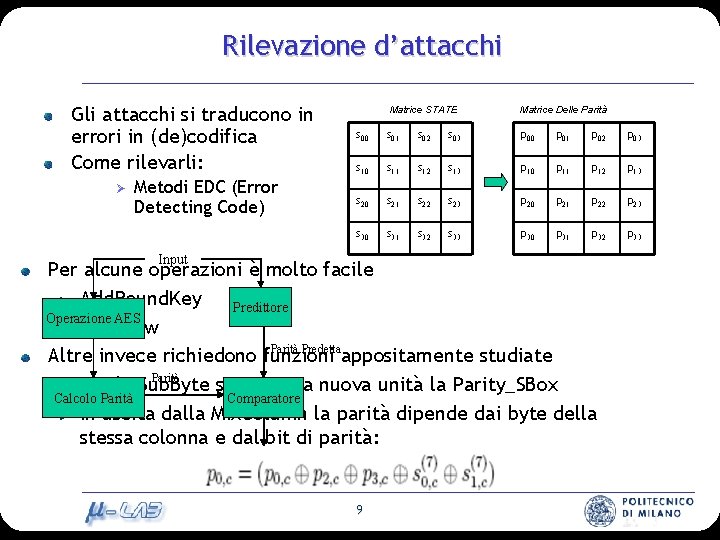

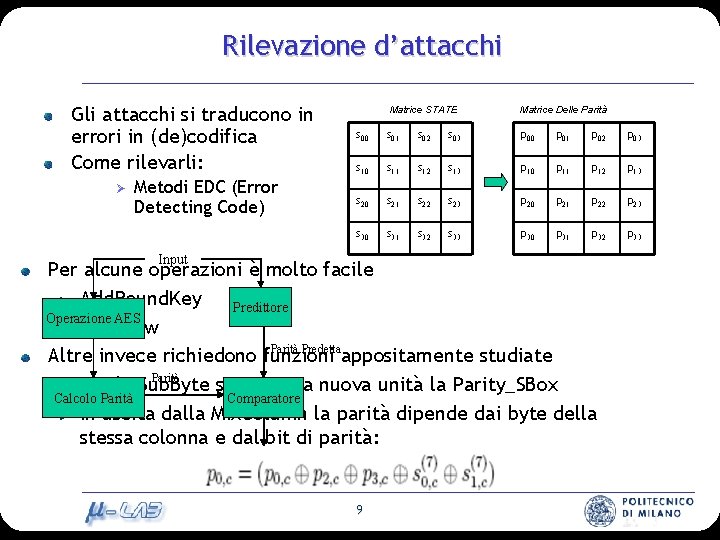

Rilevazione d’attacchi Gli attacchi si traducono in errori in (de)codifica Come rilevarli: Ø Metodi EDC (Error Detecting Code) Matrice STATE Matrice Delle Parità s 00 s 01 s 02 s 03 p 00 p 01 p 02 p 03 s 10 s 11 s 12 s 13 p 10 p 11 p 12 p 13 s 20 s 21 s 22 s 23 p 20 p 21 p 22 p 23 s 30 s 31 s 32 s 33 p 30 p 31 p 32 p 33 Input Per alcune operazioni è molto facile Add. Round. Key Predittore Operazione AES Shift. Row Parità Predetta Altre invece richiedono funzioni appositamente studiate Parità Per la Sub. Byte si crea una nuova unità la Parity_SBox Calcolo Parità Comparatore In uscita dalla Mix. Column la parità dipende dai byte della stessa colonna e dal bit di parità: 9

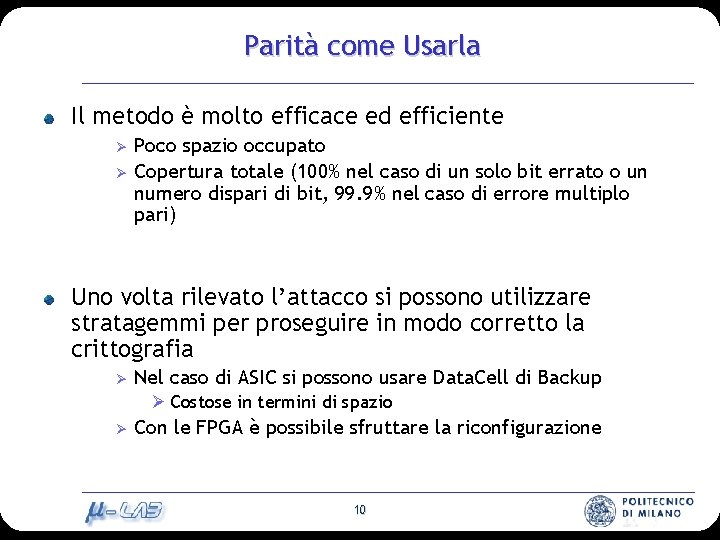

Parità come Usarla Il metodo è molto efficace ed efficiente Ø Ø Poco spazio occupato Copertura totale (100% nel caso di un solo bit errato o un numero dispari di bit, 99. 9% nel caso di errore multiplo pari) Uno volta rilevato l’attacco si possono utilizzare stratagemmi per proseguire in modo corretto la crittografia Ø Nel caso di ASIC si possono usare Data. Cell di Backup Ø Costose in termini di spazio Ø Con le FPGA è possibile sfruttare la riconfigurazione 10

Riconfigurazione Totale Equivale a “resettare” il dispositivo e riprogrammarlo Riconfigurazione Parziale Riconfiguro il solo componente soggetto all’attacco (la Dataunit) 11

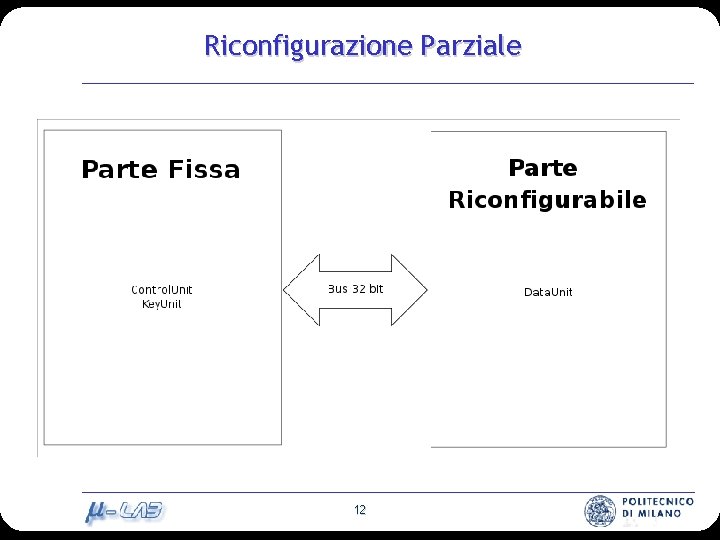

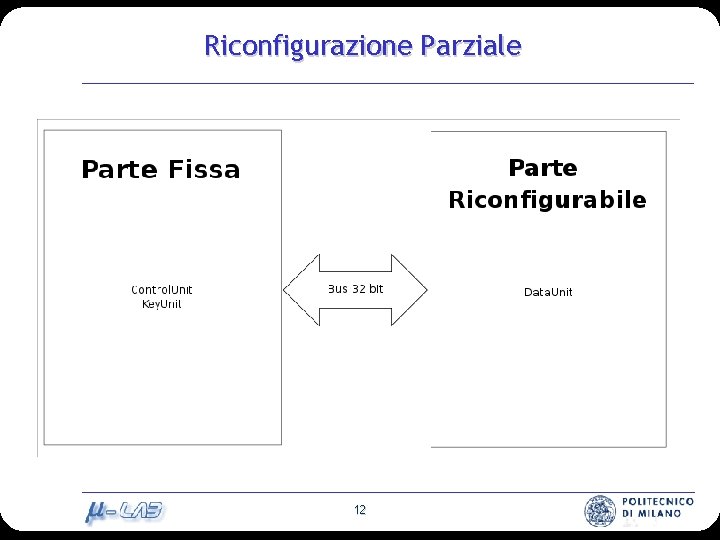

Riconfigurazione Parziale 12

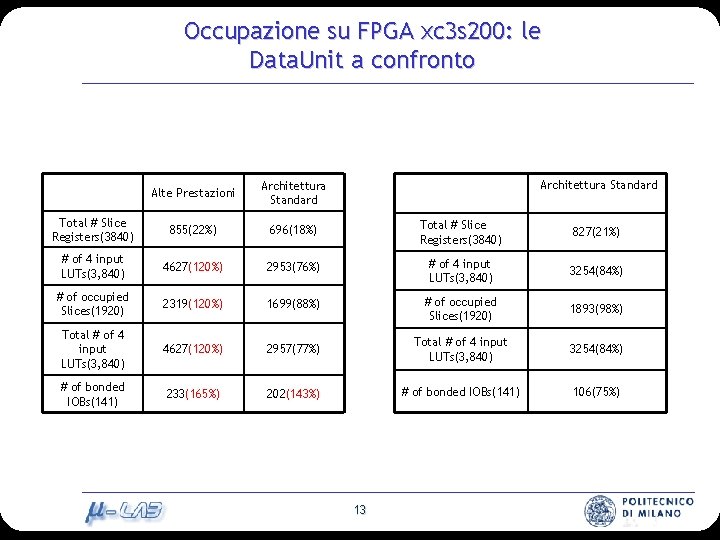

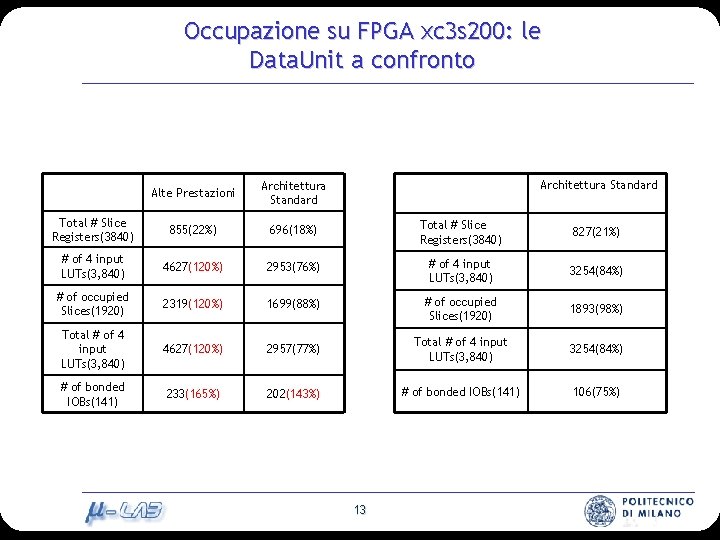

Occupazione su FPGA xc 3 s 200: le Data. Unit a confronto Architettura Standard Alte Prestazioni Architettura Standard Total # Slice Registers(3840) 855(22%) 696(18%) Total # Slice Registers(3840) 827(21%) # of 4 input LUTs(3, 840) 4627(120%) 2953(76%) # of 4 input LUTs(3, 840) 3254(84%) # of occupied Slices(1920) 2319(120%) 1699(88%) # of occupied Slices(1920) 1893(98%) Total # of 4 input LUTs(3, 840) 4627(120%) 2957(77%) Total # of 4 input LUTs(3, 840) 3254(84%) # of bonded IOBs(141) 233(165%) 202(143%) # of bonded IOBs(141) 106(75%) 13

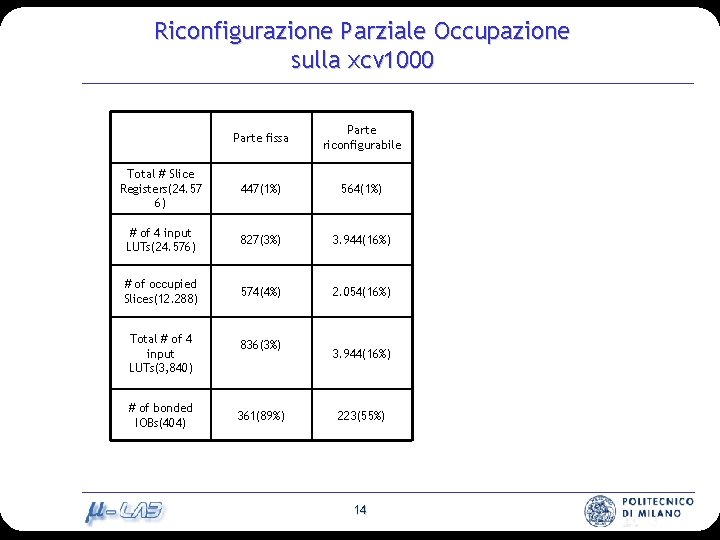

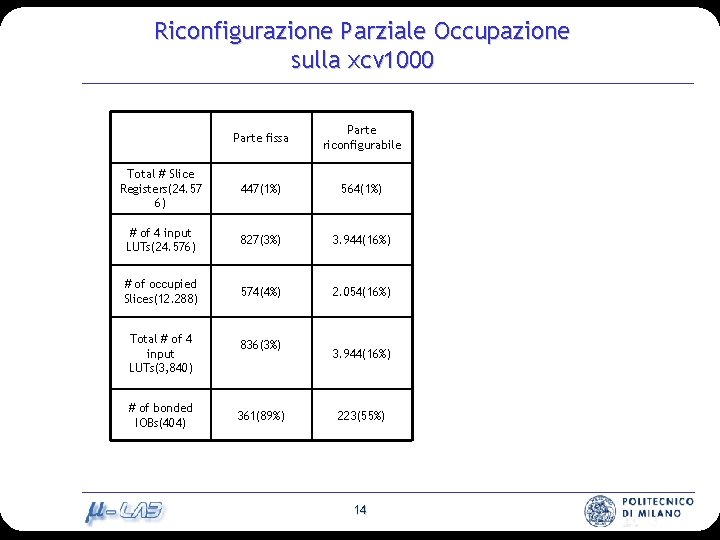

Riconfigurazione Parziale Occupazione sulla xcv 1000 Parte fissa Parte riconfigurabile Total # Slice Registers(24. 57 6) 447(1%) 564(1%) # of 4 input LUTs(24. 576) 827(3%) 3. 944(16%) # of occupied Slices(12. 288) 574(4%) 2. 054(16%) Total # of 4 input LUTs(3, 840) # of bonded IOBs(404) 836(3%) 361(89%) 3. 944(16%) 223(55%) 14

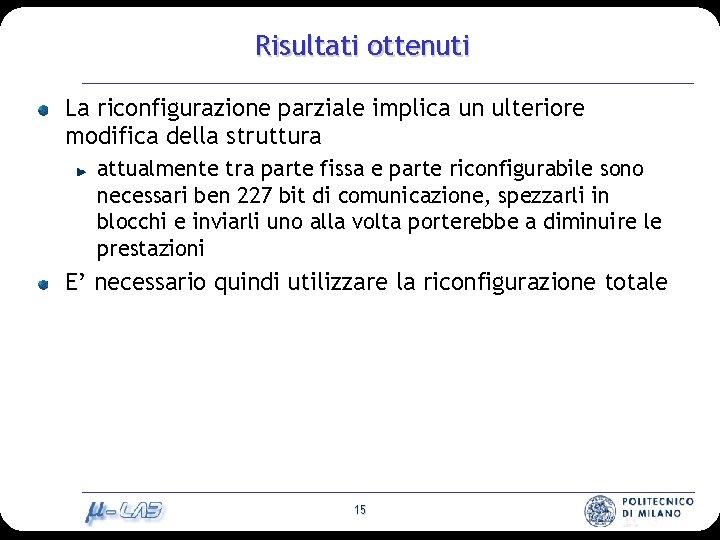

Risultati ottenuti La riconfigurazione parziale implica un ulteriore modifica della struttura attualmente tra parte fissa e parte riconfigurabile sono necessari ben 227 bit di comunicazione, spezzarli in blocchi e inviarli uno alla volta porterebbe a diminuire le prestazioni E’ necessario quindi utilizzare la riconfigurazione totale 15

Futuri sviluppi L’utilizzo delle FPGA per la realizzazione di architetture sicure è comunque conveniente perché farlo su ASIC o circuiti dedicati comporta un notevole costo in termini di spazio occupato Implementare una nuova Data. Unit da 192 e 256 bit Studiare una nuova Architettura che permetta di ridurre il numero di segnali 16