Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica STATUS OF THE HPD-PET READ-OUT ELECTRONICS A. Argentieri 1 , F. Corsi 2, C. Marzocca 2 , P. Del Vecchio 2 , E. Chesi 3, E. Nappi 1 1 Istituto 2 Dipartimento 15/01/2007 Nazionale di Fisica Nucleare - Bari di Ingegneria Elettrotecnica ed Elettronica - Politecnico di Bari 3 PH Department, CERN, Geneva HPD-PET Meeting - Bari 1

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Outline • HPD-PET Scanner Architecture (Main Features) • HPD-PET Data Acquisition System (Main Features) • HPD-PET Read-out Card • Stand-alone Read-out Card • The Implemented System - Hardware components - FPGA Firmware - Software Application and using mode • Conclusions and future tasks 15/01/2007 HPD-PET Meeting - Bari 2

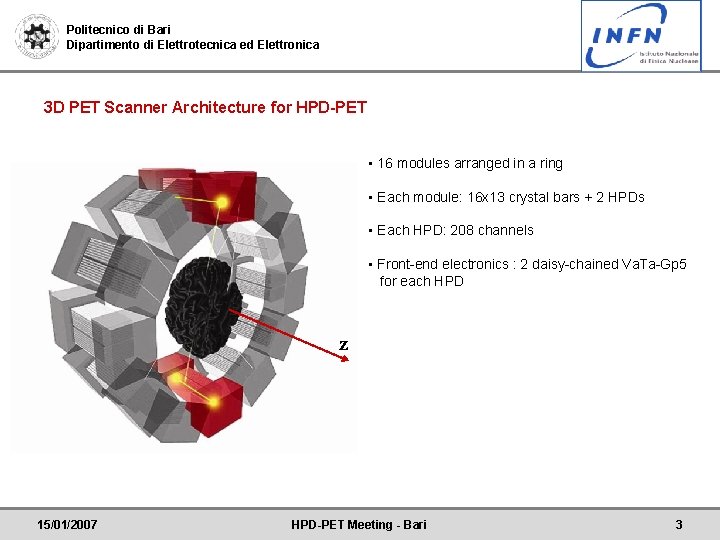

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica 3 D PET Scanner Architecture for HPD-PET • 16 modules arranged in a ring • Each module: 16 x 13 crystal bars + 2 HPDs • Each HPD: 208 channels • Front-end electronics : 2 daisy-chained Va. Ta-Gp 5 for each HPD z 15/01/2007 HPD-PET Meeting - Bari 3

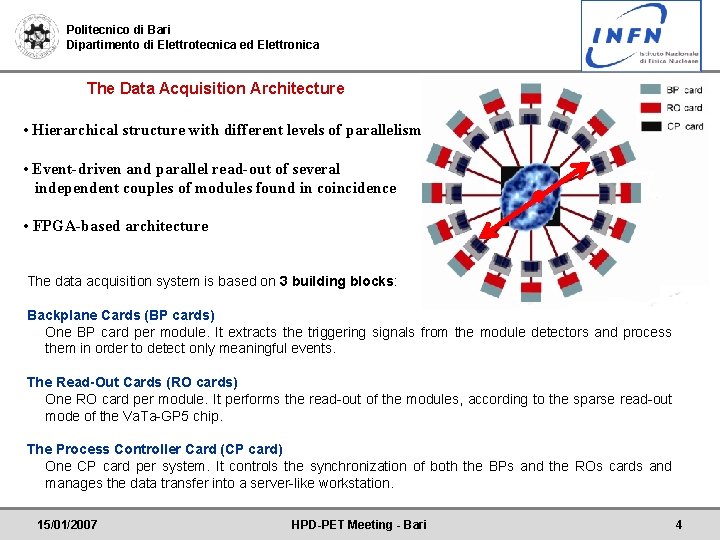

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica The Data Acquisition Architecture • Hierarchical structure with different levels of parallelism • Event-driven and parallel read-out of several independent couples of modules found in coincidence • FPGA-based architecture The data acquisition system is based on 3 building blocks: Backplane Cards (BP cards) One BP card per module. It extracts the triggering signals from the module detectors and process them in order to detect only meaningful events. The Read-Out Cards (RO cards) One RO card per module. It performs the read-out of the modules, according to the sparse read-out mode of the Va. Ta-GP 5 chip. The Process Controller Card (CP card) One CP card per system. It controls the synchronization of both the BPs and the ROs cards and manages the data transfer into a server-like workstation. 15/01/2007 HPD-PET Meeting - Bari 4

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica READ-OUT CARD: Main features • HPD-PET oriented but also useful as a standalone read-out system for the Va. Ta chip • Requirements for the PET application: • setting of the configuration registers of the four Va. Ta chips in the module, with data from USB 2. 0 bus • serial read-out for pedestal evaluation and threshold setting of the Va. Ta chips • during normal acquisition, sparse read-out of the chips, enabled by the CP card • coincidence analysis between the two HPDs and data validation • data transmission to workstation, via the USB 2. 0 bus 15/01/2007 HPD-PET Meeting - Bari 5

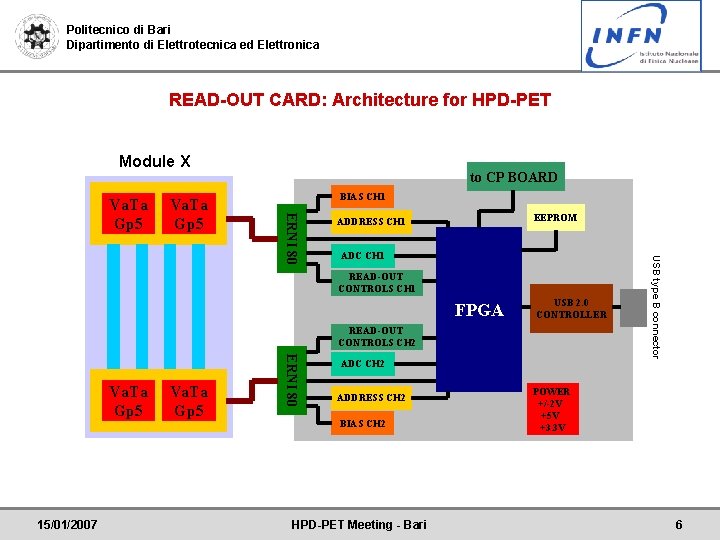

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica READ-OUT CARD: Architecture for HPD-PET Module X Va. Ta Gp 5 BIAS CH 1 EEPROM ADDRESS CH 1 ADC CH 1 READ-OUT CONTROLS CH 1 FPGA USB 2. 0 CONTROLLER READ-OUT CONTROLS CH 2 15/01/2007 Va. Ta Gp 5 ERNI 80 Va. Ta Gp 5 ADC CH 2 ADDRESS CH 2 BIAS CH 2 HPD-PET Meeting - Bari USB type B connector ERNI 80 Va. Ta Gp 5 to CP BOARD POWER +/-2 V +5 V +3. 3 V 6

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Implementation of a read-out system for standalone applications • Main hardware and firmware requirements: • oriented to the test of the Va. Ta chip • upload of the configuration registers of max 16 Va. Ta chips in daisy-chain, with data from USB 2. 0 bus • monitoring of the analog output of the Va. Ta chips • sparse and serial read-out of the chips • data transmission, via the USB 2. 0 bus • Main software requirements : • set-up of the desired configuration and upload via USB 2. 0 • selection of a single channel for monitoring its analog output • download via USB 2. 0 and data storage on local disk • postprocessing for data validation, pedestal calculation and possible extraction of data coming from one selected channel 15/01/2007 HPD-PET Meeting - Bari 7

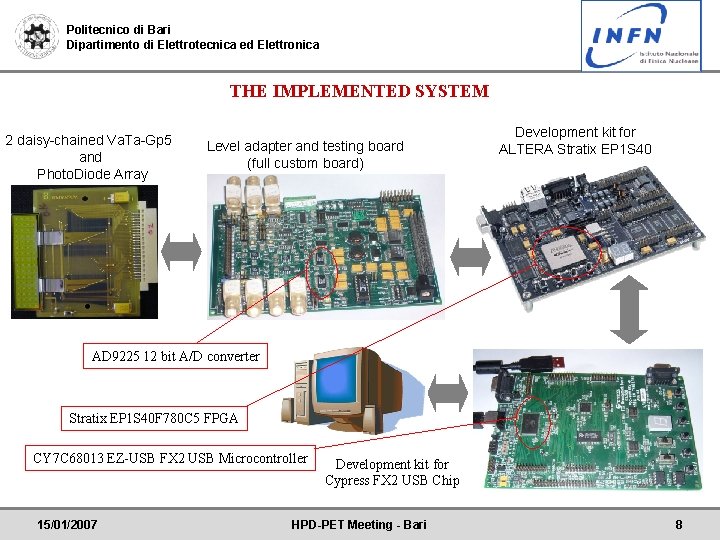

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica THE IMPLEMENTED SYSTEM 2 daisy-chained Va. Ta-Gp 5 and Photo. Diode Array Level adapter and testing board (full custom board) Development kit for ALTERA Stratix EP 1 S 40 AD 9225 12 bit A/D converter Stratix EP 1 S 40 F 780 C 5 FPGA CY 7 C 68013 EZ-USB FX 2 USB Microcontroller 15/01/2007 Development kit for Cypress FX 2 USB Chip HPD-PET Meeting - Bari 8

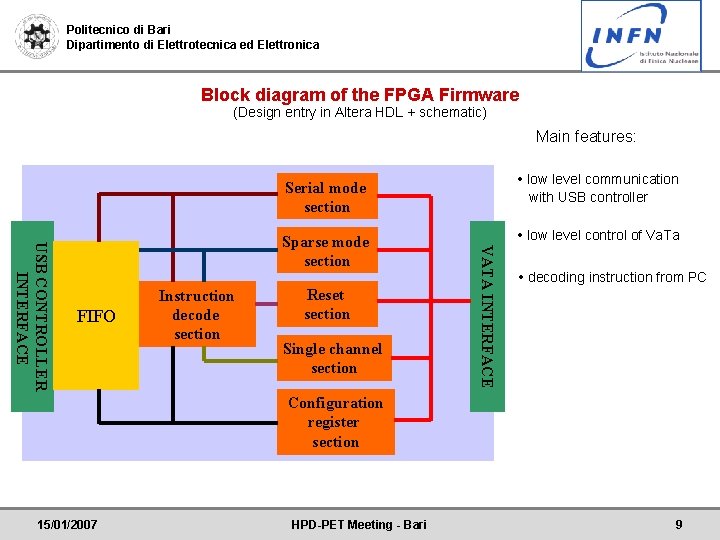

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Block diagram of the FPGA Firmware (Design entry in Altera HDL + schematic) Main features: • low level communication Serial mode section FIFO Instruction decode section Reset section Single channel section • low level control of Va. Ta VATA INTERFACE USB CONTROLLER INTERFACE Sparse mode section with USB controller • decoding instruction from PC Configuration register section 15/01/2007 HPD-PET Meeting - Bari 9

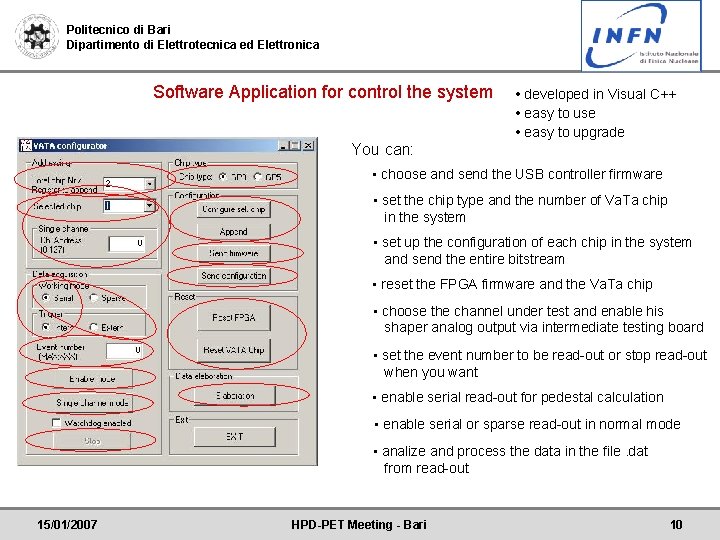

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Software Application for control the system You can: • developed in Visual C++ • easy to use • easy to upgrade • choose and send the USB controller firmware • set the chip type and the number of Va. Ta chip in the system • set up the configuration of each chip in the system and send the entire bitstream • reset the FPGA firmware and the Va. Ta chip • choose the channel under test and enable his shaper analog output via intermediate testing board • set the event number to be read-out or stop read-out when you want • enable serial read-out for pedestal calculation • enable serial or sparse read-out in normal mode • analize and process the data in the file. dat from read-out 15/01/2007 HPD-PET Meeting - Bari 10

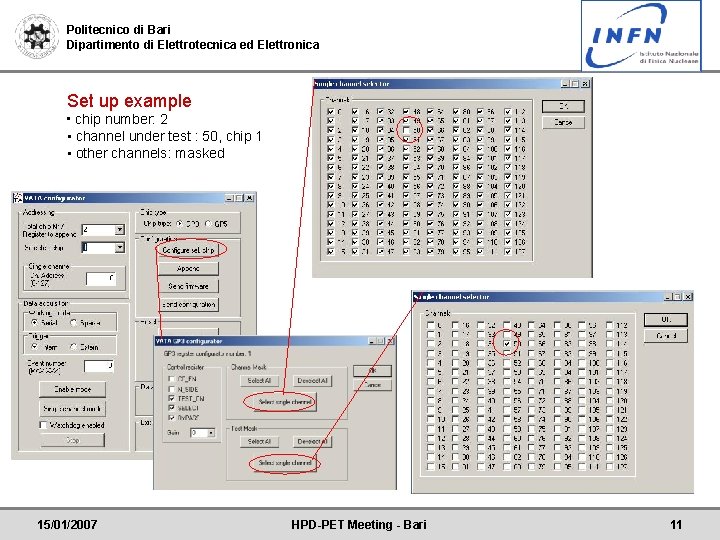

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Set up example • chip number: 2 • channel under test : 50, chip 1 • other channels: masked 15/01/2007 HPD-PET Meeting - Bari 11

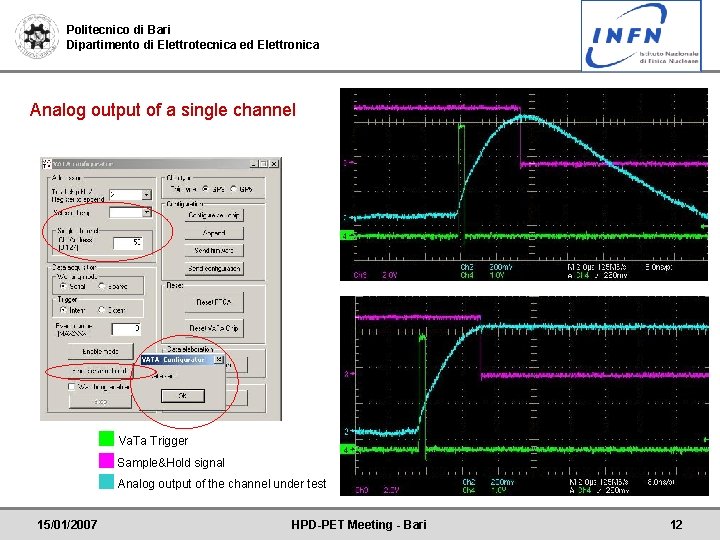

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Analog output of a single channel Va. Ta Trigger Sample&Hold signal Analog output of the channel under test 15/01/2007 HPD-PET Meeting - Bari 12

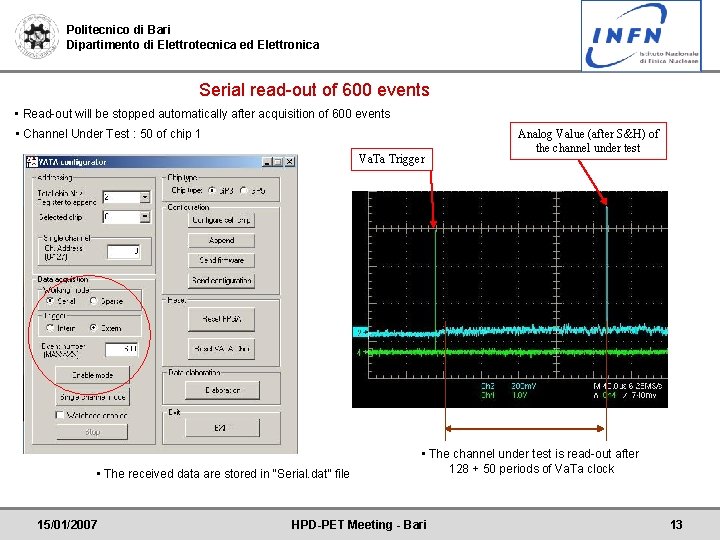

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Serial read-out of 600 events • Read-out will be stopped automatically after acquisition of 600 events • Channel Under Test : 50 of chip 1 Va. Ta Trigger • The received data are stored in “Serial. dat” file 15/01/2007 Analog Value (after S&H) of the channel under test • The channel under test is read-out after 128 + 50 periods of Va. Ta clock HPD-PET Meeting - Bari 13

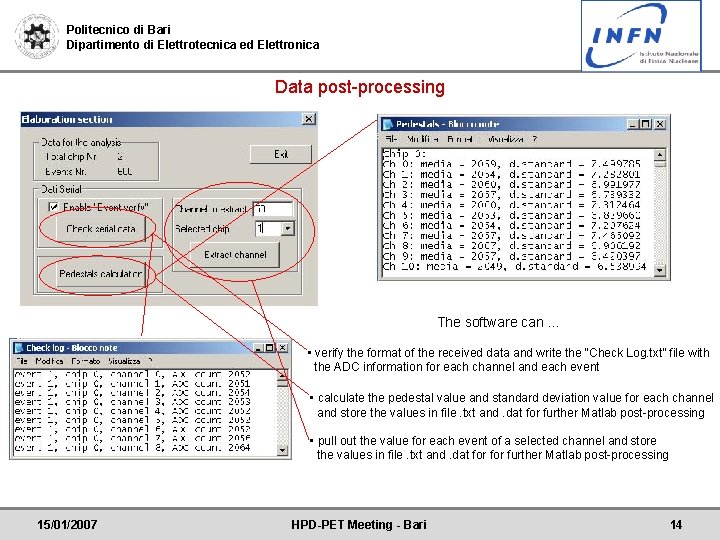

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Data post-processing The software can … • verify the format of the received data and write the “Check Log. txt” file with the ADC information for each channel and each event • calculate the pedestal value and standard deviation value for each channel and store the values in file. txt and. dat for further Matlab post-processing • pull out the value for each event of a selected channel and store the values in file. txt and. dat for further Matlab post-processing 15/01/2007 HPD-PET Meeting - Bari 14

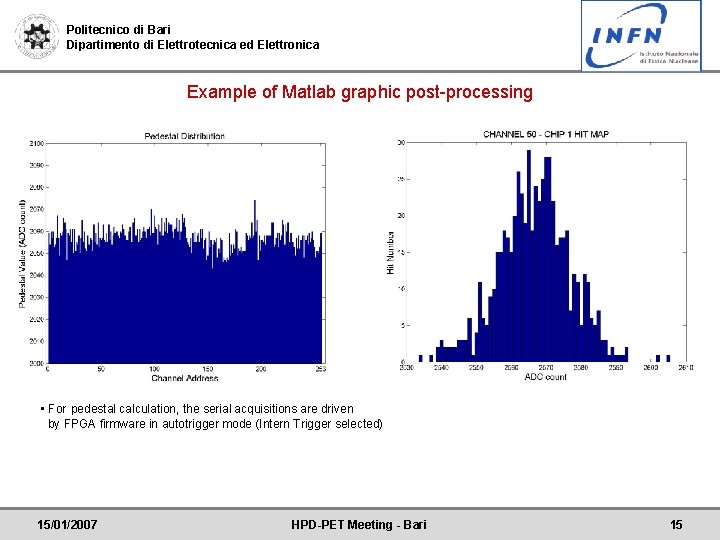

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Example of Matlab graphic post-processing • For pedestal calculation, the serial acquisitions are driven by FPGA firmware in autotrigger mode (Intern Trigger selected) 15/01/2007 HPD-PET Meeting - Bari 15

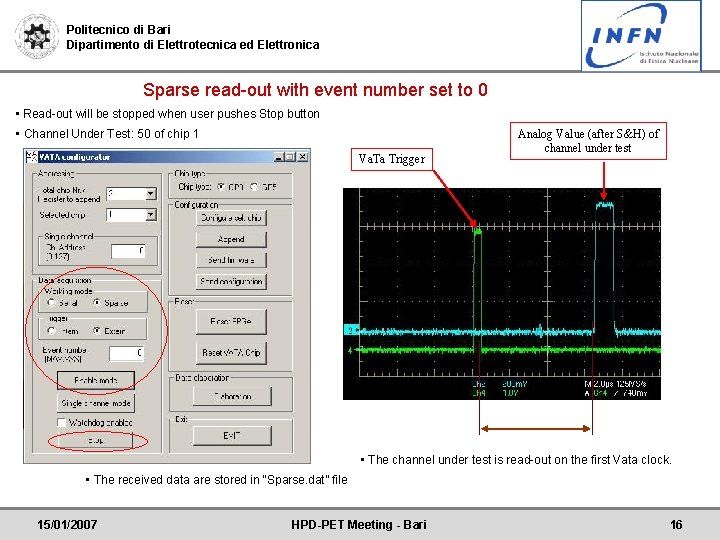

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Sparse read-out with event number set to 0 • Read-out will be stopped when user pushes Stop button • Channel Under Test: 50 of chip 1 Va. Ta Trigger Analog Value (after S&H) of channel under test • The channel under test is read-out on the first Vata clock. • The received data are stored in “Sparse. dat” file 15/01/2007 HPD-PET Meeting - Bari 16

Politecnico di Bari Dipartimento di Elettrotecnica ed Elettronica Conclusions • The implemented system is oriented to test and verify the functionality of Va. Ta chip or to read-out a simple chain of chips. • The system is easy to use. • The system can be easily upgraded thanks to the FPGA implementation. • The USB communication beetween system and PC is very fast and flexible. • The system is a good preliminary version of Read-Out Card for HPD-PET. • We have developed the required knowledge and tools to face the future challenges of the HPD-PET electronics. Future Tasks • Design and produce just one “full implemented” board with hardware for two chip chains. • Develope the FPGA firmware for coincidence analysis and control of the two chains. 15/01/2007 HPD-PET Meeting - Bari 17

- Slides: 17