PN Junction Diode Biasing diode equations diode capacitances

P-N Junction Diode Biasing diode equations diode capacitances breakdown of diodes spice model schottky diodes 1

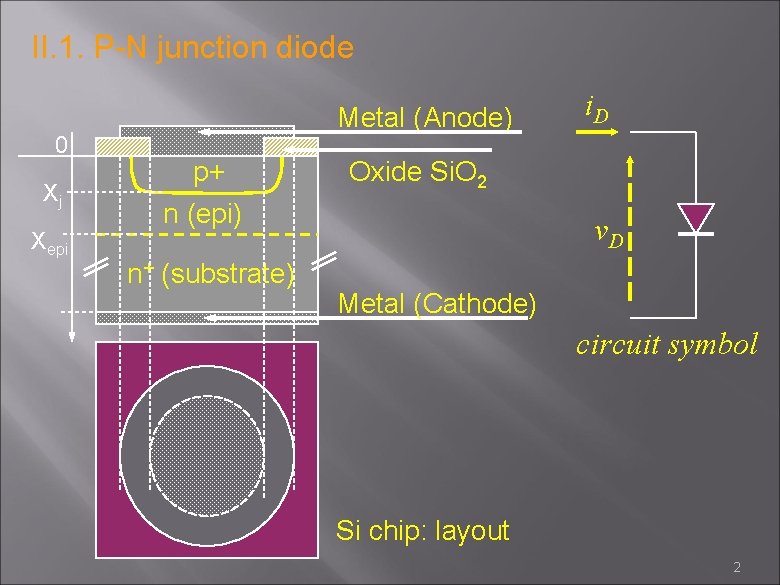

II. 1. P-N junction diode 0 Xj Xepi Metal (Anode) p+ n (epi) n+ (substrate) i. D Oxide Si. O 2 v. D Metal (Cathode) circuit symbol Si chip: layout 2

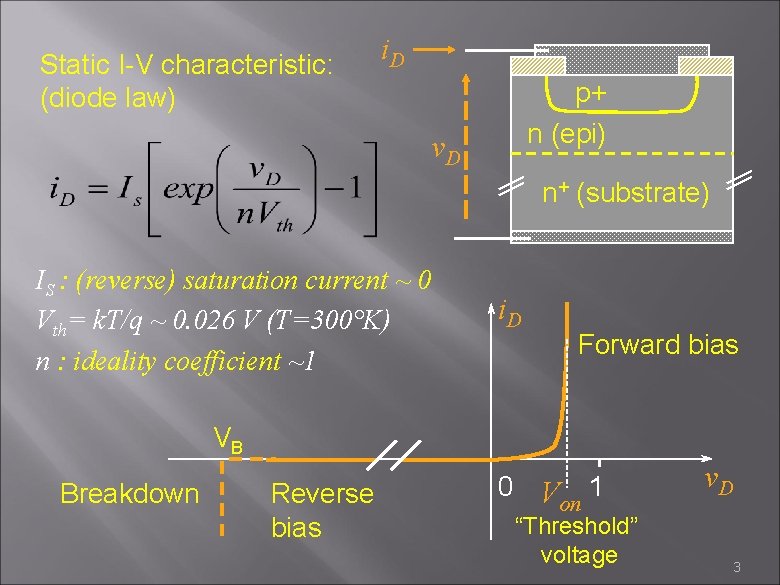

Static I-V characteristic: (diode law) i. D p+ n (epi) v. D n+ (substrate) [ A] IS : (reverse) saturation current ~ 0 Vth= k. T/q ~ 0. 026 V (T=300°K) n : ideality coefficient ~1 i. D Forward bias VB Breakdown Reverse bias 0 V 1 on “Threshold” voltage v. D 3

![P-N junction diode Abrupt junction (step junction) N[at/cm 3] p+ n ND Abrupt p-n P-N junction diode Abrupt junction (step junction) N[at/cm 3] p+ n ND Abrupt p-n](http://slidetodoc.com/presentation_image_h/2c32bb9adfb25a2a042aa0318e86d635/image-4.jpg)

P-N junction diode Abrupt junction (step junction) N[at/cm 3] p+ n ND Abrupt p-n junction ND p+ n (epi) n+ (substrate) Diffused p-n junction x[ m] a) Uniform doping in p+ and n regions b) Infinitely extended planar junction (one dimensional) 0 4

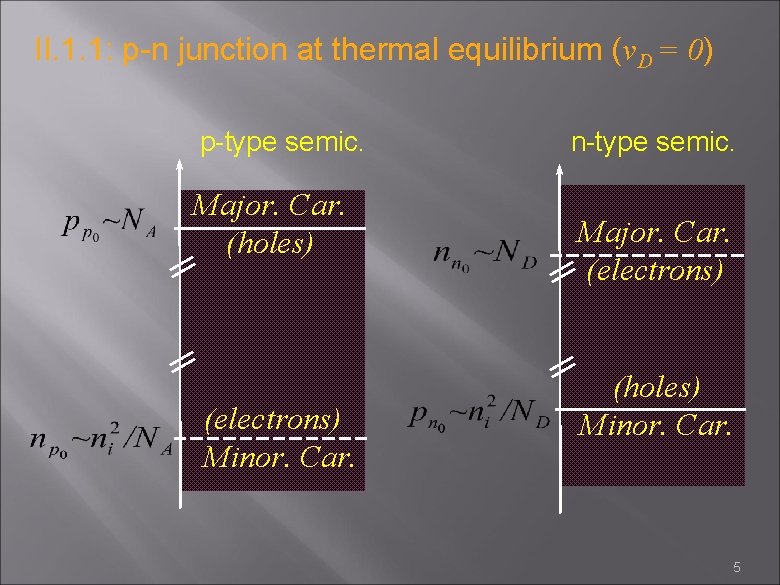

II. 1. 1: p-n junction at thermal equilibrium (v. D = 0) p-type semic. Major. Car. (holes) (electrons) Minor. Car. n-type semic. Major. Car. (electrons) (holes) Minor. Car. 5

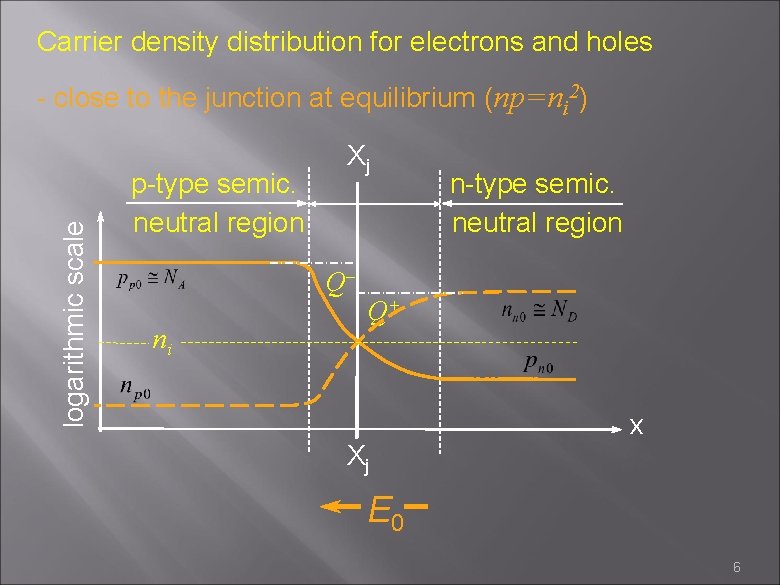

Carrier density distribution for electrons and holes logarithmic scale - close to the junction at equilibrium (np=ni 2) p-type semic. neutral region Xj Q– ni n-type semic. neutral region Q+ Xj x E 0 6

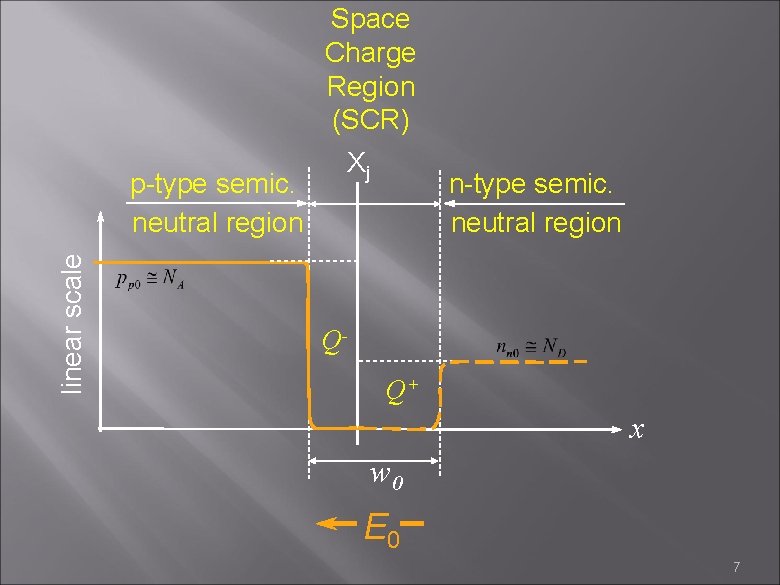

Space Charge Region (SCR) linear scale p-type semic. neutral region Xj n-type semic. neutral region QQ+ x w 0 E 0 7

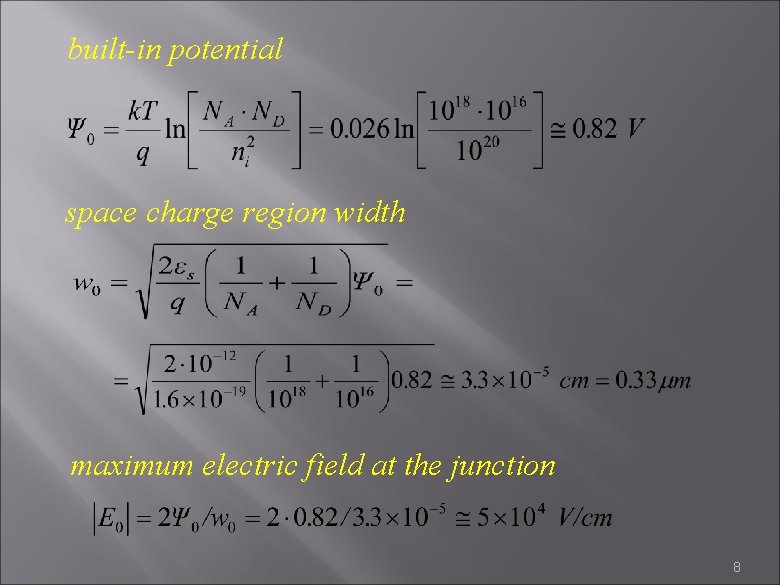

built-in potential space charge region width maximum electric field at the junction 8

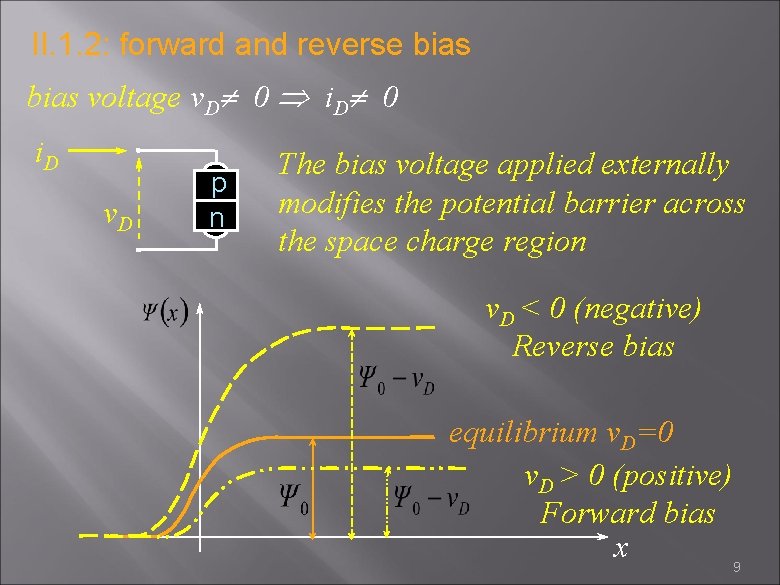

II. 1. 2: forward and reverse bias voltage v. D 0 i. D 0 i. D v. D p n The bias voltage applied externally modifies the potential barrier across the space charge region v. D < 0 (negative) Reverse bias equilibrium v. D=0 v. D > 0 (positive) Forward bias x 9

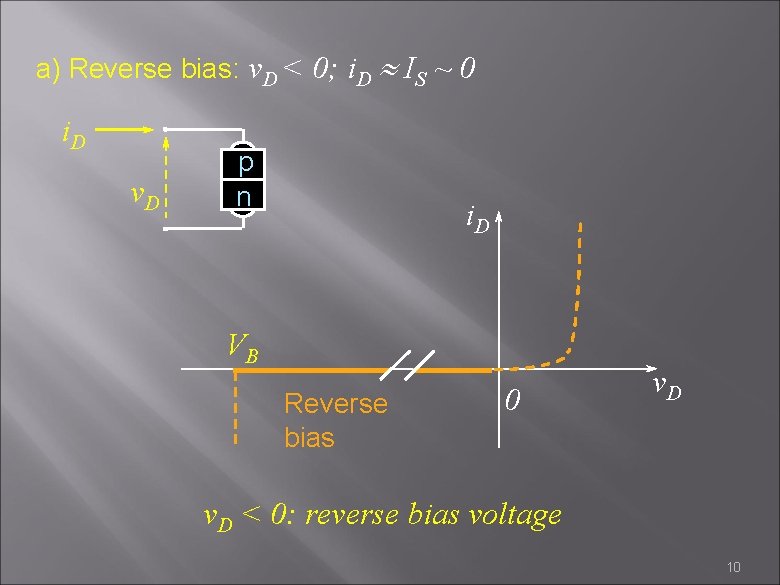

a) Reverse bias: v. D < 0; i. D IS ~ 0 i. D v. D p n i. D VB Reverse bias 0 v. D < 0: reverse bias voltage 10

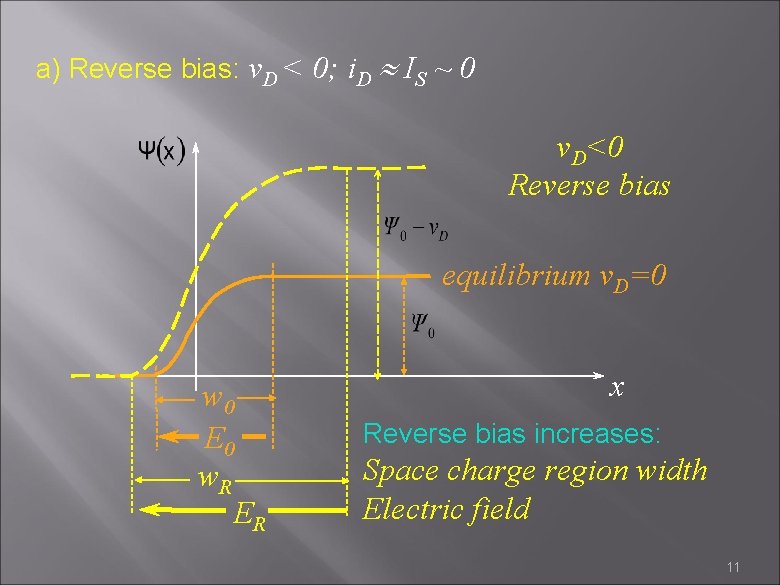

a) Reverse bias: v. D < 0; i. D IS ~ 0 v. D<0 Reverse bias equilibrium v. D=0 w 0 E 0 w. R ER x Reverse bias increases: Space charge region width Electric field 11

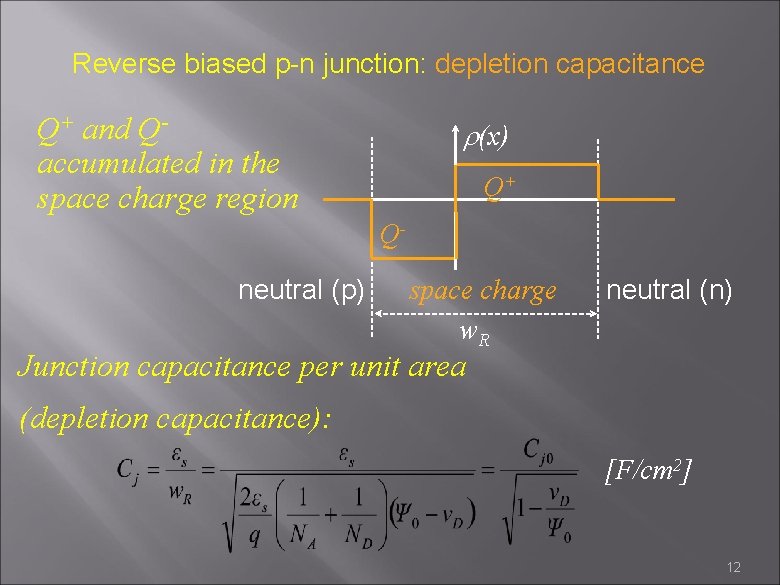

Reverse biased p-n junction: depletion capacitance Q+ and Qaccumulated in the space charge region (x) Q+ Q- neutral (p) space charge w. R neutral (n) Junction capacitance per unit area (depletion capacitance): [F/cm 2] 12

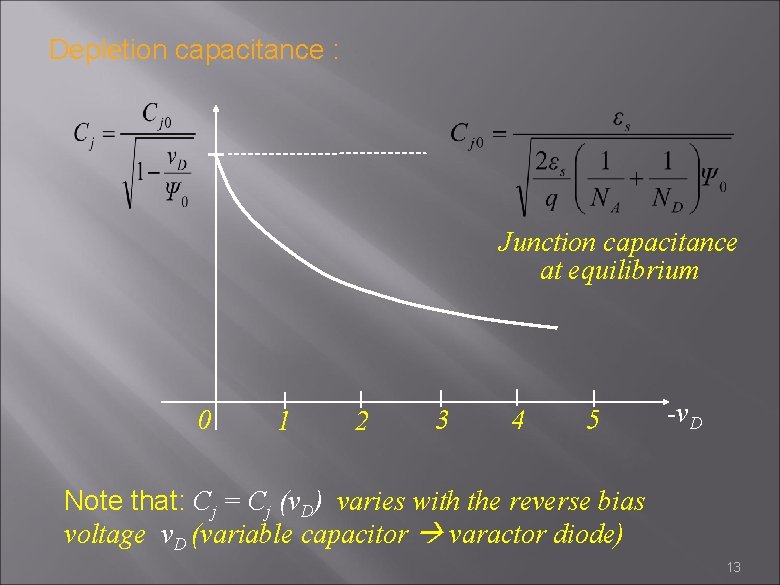

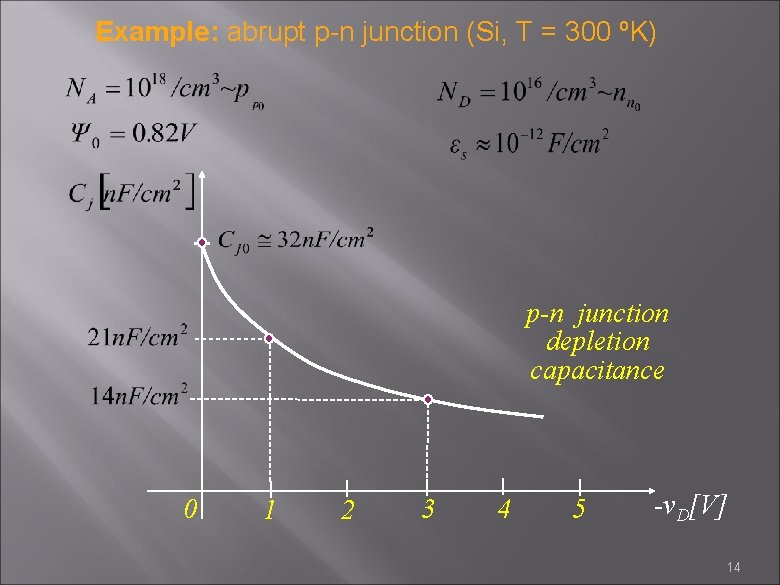

Depletion capacitance : Junction capacitance at equilibrium 0 1 2 3 4 5 -v. D Note that: Cj = Cj (v. D) varies with the reverse bias voltage v. D (variable capacitor varactor diode) 13

Example: abrupt p-n junction (Si, T = 300 ºK) p-n junction depletion capacitance 0 1 2 3 4 5 -v. D[V] 14

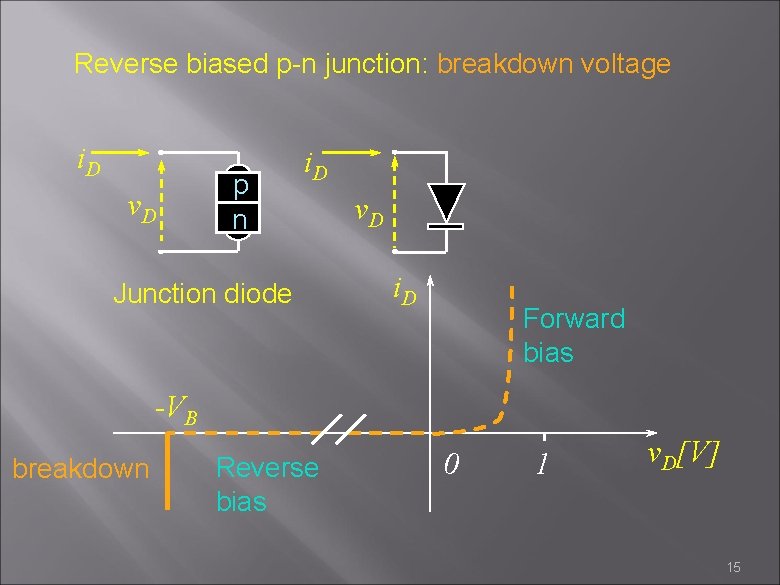

Reverse biased p-n junction: breakdown voltage i. D v. D p n i. D Junction diode v. D i. D Forward bias -VB breakdown Reverse bias 0 1 v. D[V] 15

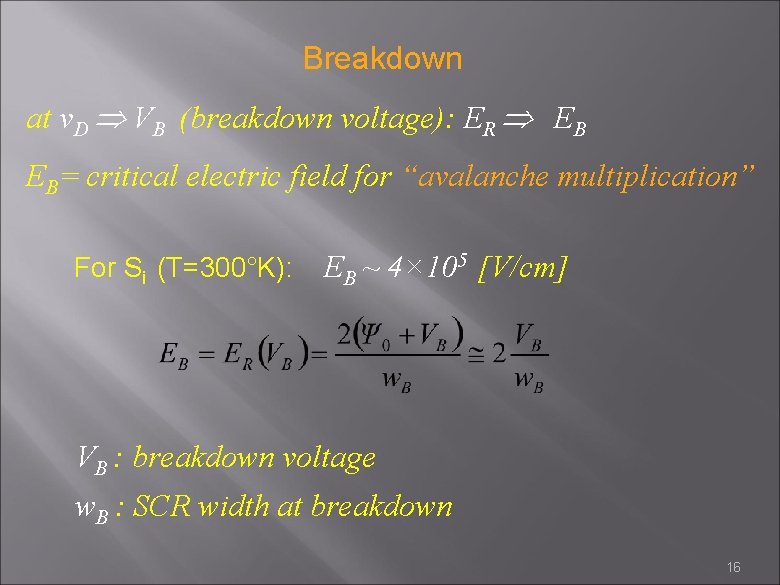

Breakdown at v. D VB (breakdown voltage): ER EB EB= critical electric field for “avalanche multiplication” For Si (T=300°K): EB ~ 4× 105 [V/cm] VB : breakdown voltage w. B : SCR width at breakdown 16

Avalanche generation Electron 1, that is thermally generated, is accelerated by the electric field ER, and colliding with the lattice generates by impact ionization the e-h pair 2 -2, and so on (for holes the same mechanism works) 2 17

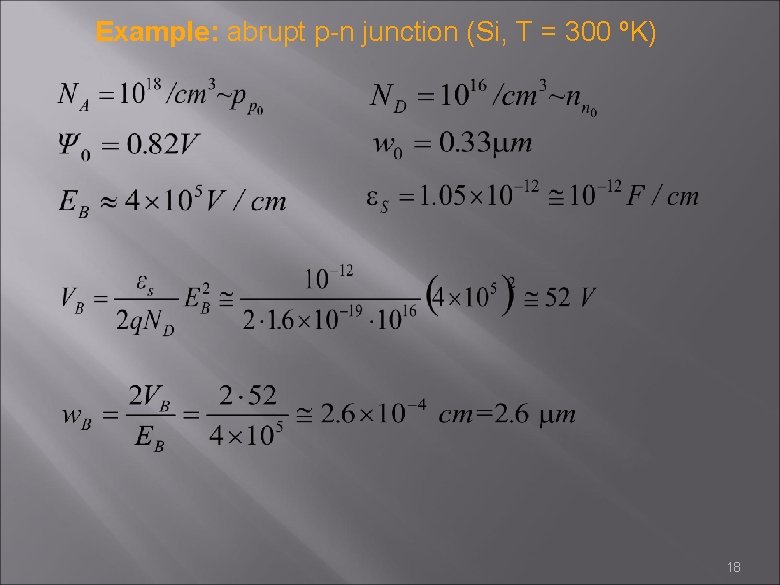

Example: abrupt p-n junction (Si, T = 300 ºK) 18

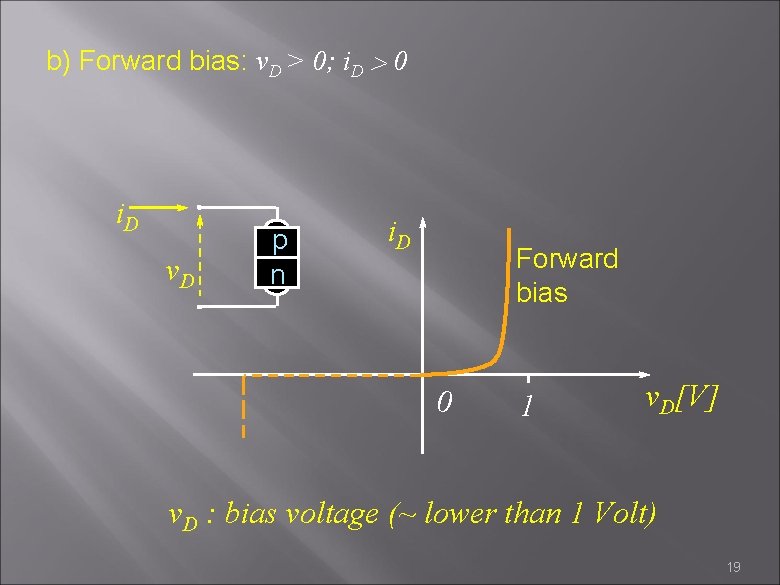

b) Forward bias: v. D > 0; i. D 0 i. D v. D p n i. D Forward bias 0 1 v. D[V] v. D : bias voltage (~ lower than 1 Volt) 19

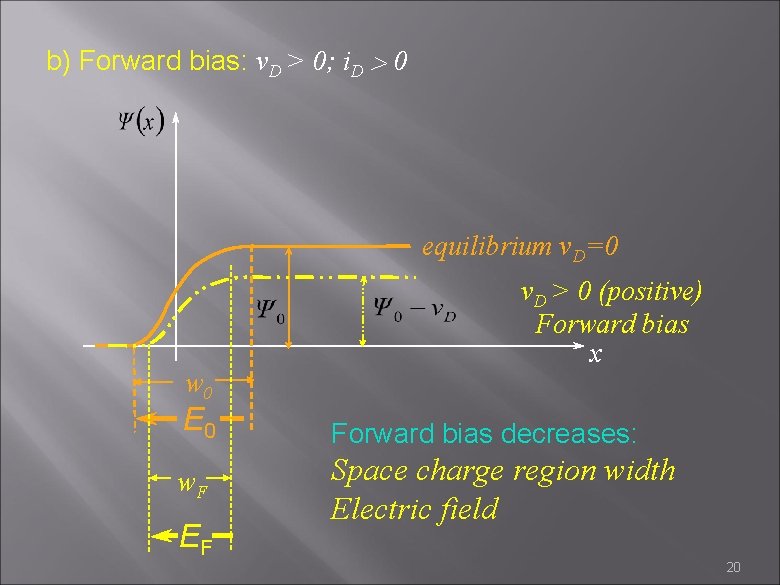

b) Forward bias: v. D > 0; i. D 0 equilibrium v. D=0 w 0 v. D > 0 (positive) Forward bias x E 0 Forward bias decreases: w. F Space charge region width Electric field EF 20

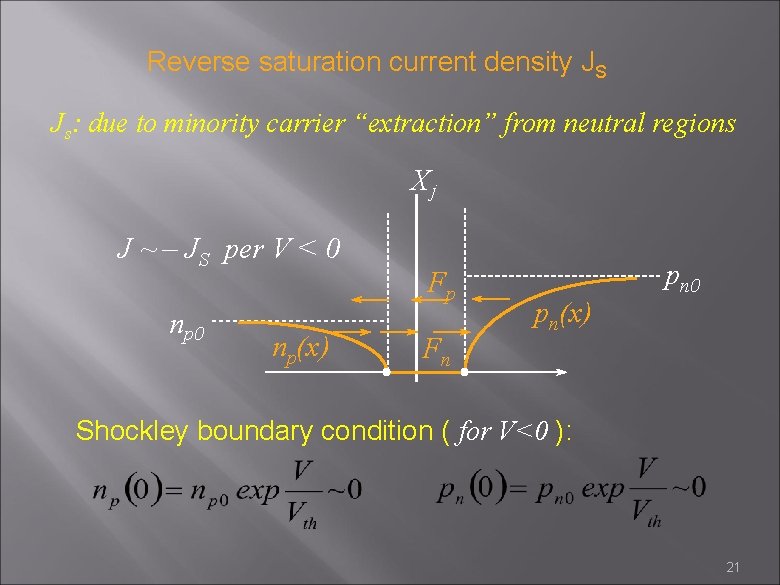

Reverse saturation current density JS Js: due to minority carrier “extraction” from neutral regions Xj J ~ – JS per V < 0 np(x) Fp Fn pn(x) pn 0 Shockley boundary condition ( for V<0 ): 21

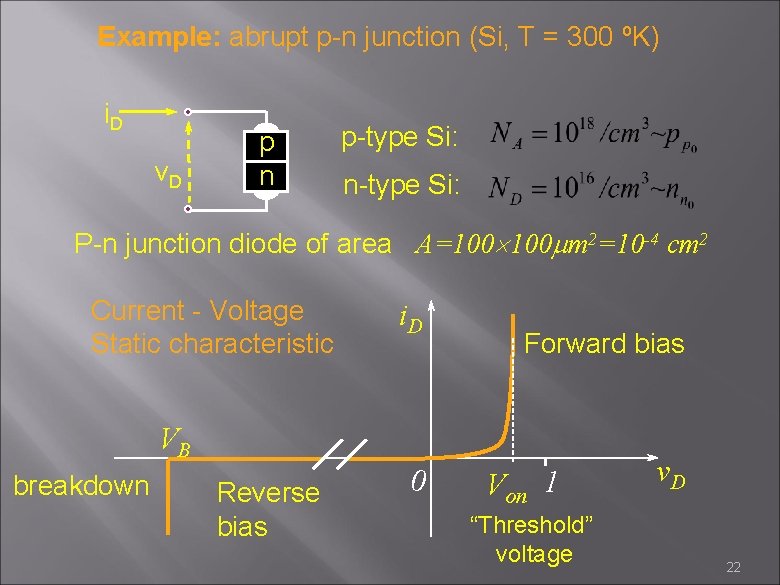

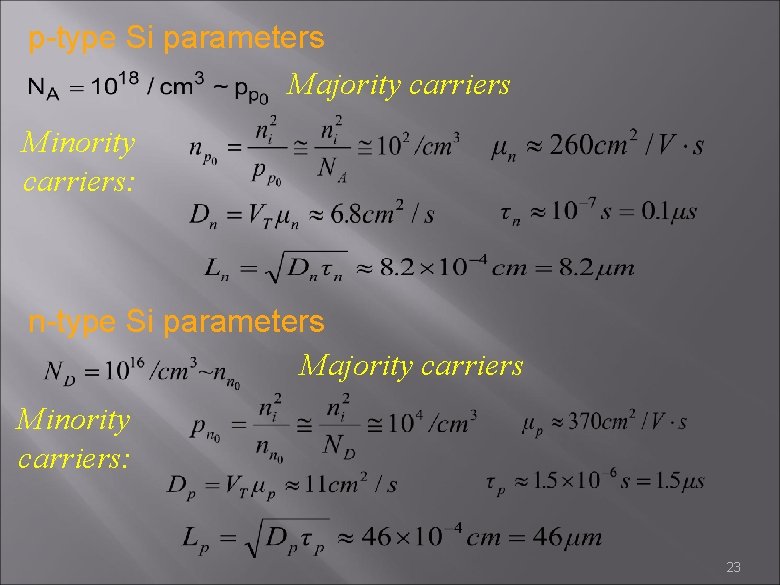

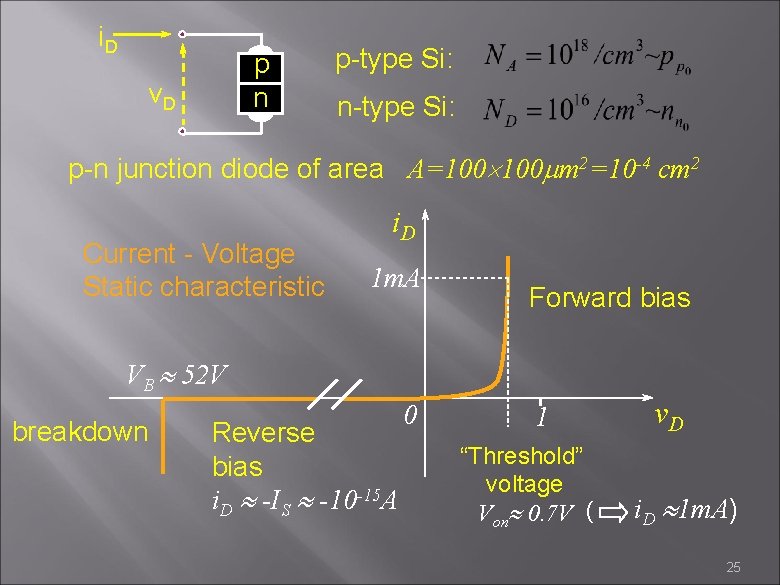

Example: abrupt p-n junction (Si, T = 300 ºK) i. D v. D p n p-type Si: n-type Si: P-n junction diode of area A=100 m 2=10 -4 cm 2 Current - Voltage Static characteristic i. D Forward bias VB breakdown Reverse bias 0 Von 1 “Threshold” voltage v. D 22

p-type Si parameters Majority carriers Minority carriers: n-type Si parameters Majority carriers Minority carriers: 23

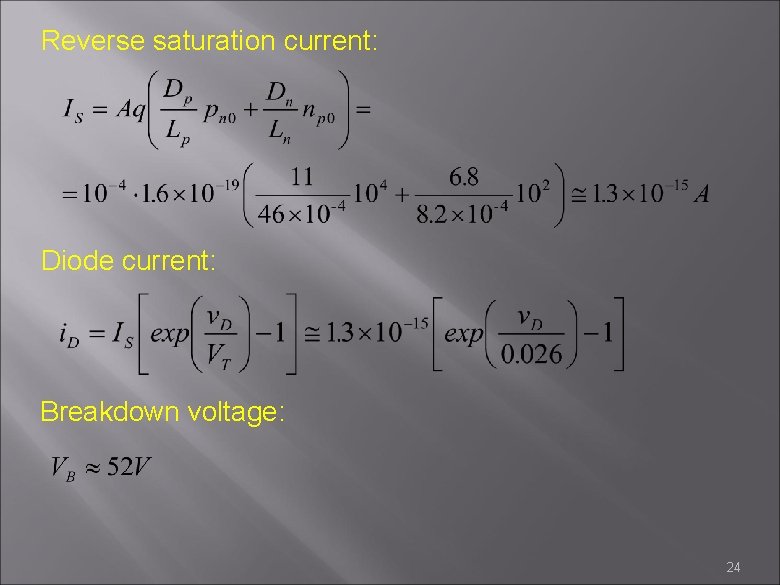

Reverse saturation current: Diode current: Breakdown voltage: 24

i. D p n v. D p-type Si: n-type Si: p-n junction diode of area A=100 m 2=10 -4 cm 2 Current - Voltage Static characteristic i. D 1 m. A Forward bias VB 52 V breakdown Reverse bias i. D -IS -10 -15 A 0 1 “Threshold” voltage Von 0. 7 V ( v. D i. D 1 m. A) 25

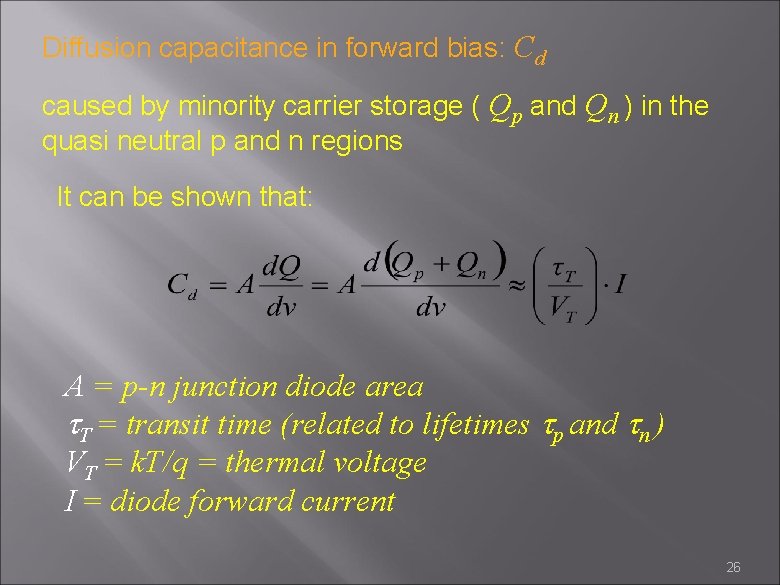

Diffusion capacitance in forward bias: Cd caused by minority carrier storage ( Qp and Qn ) in the quasi neutral p and n regions It can be shown that: A = p-n junction diode area T = transit time (related to lifetimes p and n ) VT = k. T/q = thermal voltage I = diode forward current 26

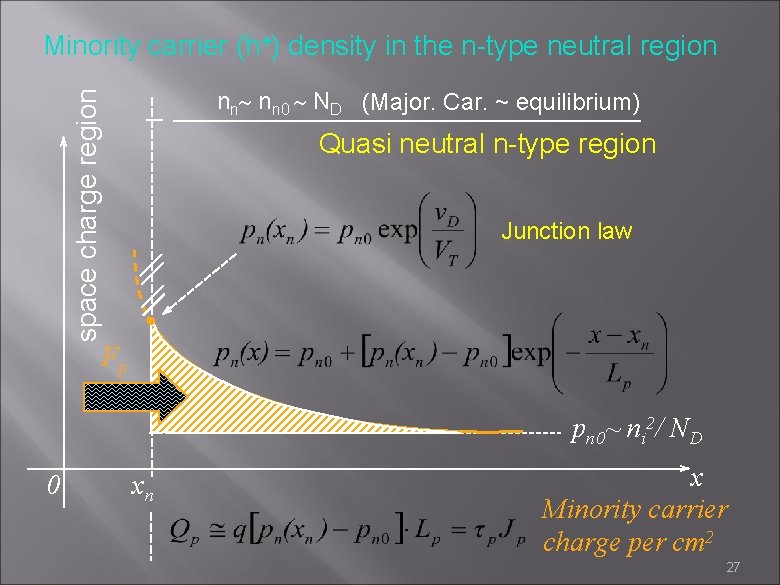

Minority carrier (h+) density in the n-type neutral region space charge region nn~ nn 0 ~ ND (Major. Car. ~ equilibrium) Quasi neutral n-type region Junction law Fp pn 0~ ni 2/ ND 0 xn x Minority carrier charge per cm 2 27

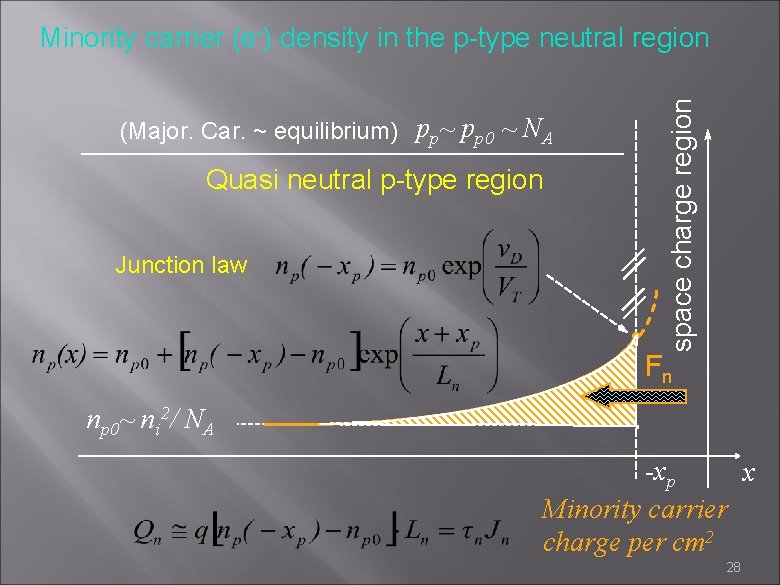

(Major. Car. ~ equilibrium) pp~ pp 0 ~ NA Quasi neutral p-type region Junction law space charge region Minority carrier (e-) density in the p-type neutral region Fn np 0~ ni 2/ NA -xp x Minority carrier charge per cm 2 28

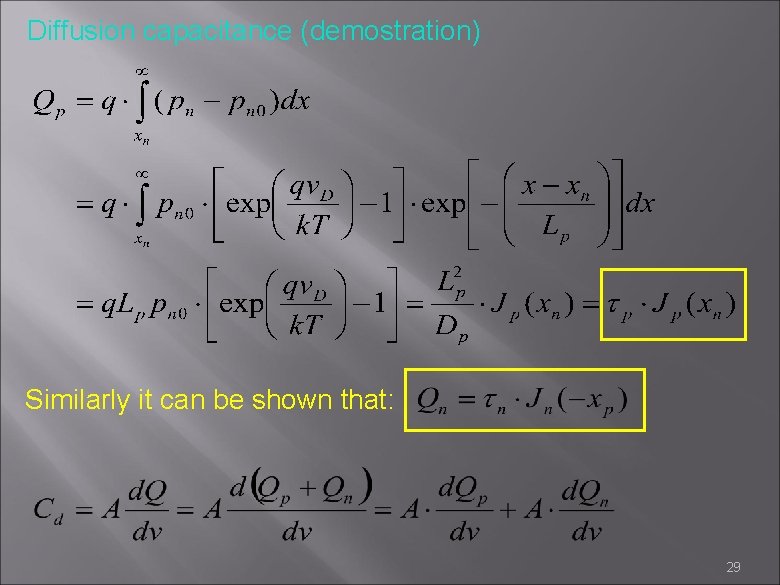

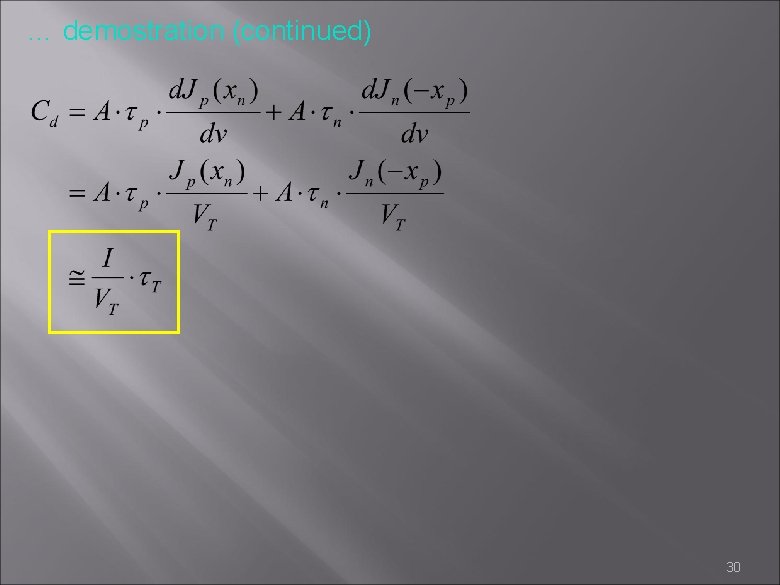

Diffusion capacitance (demostration) Similarly it can be shown that: 29

… demostration (continued) 30

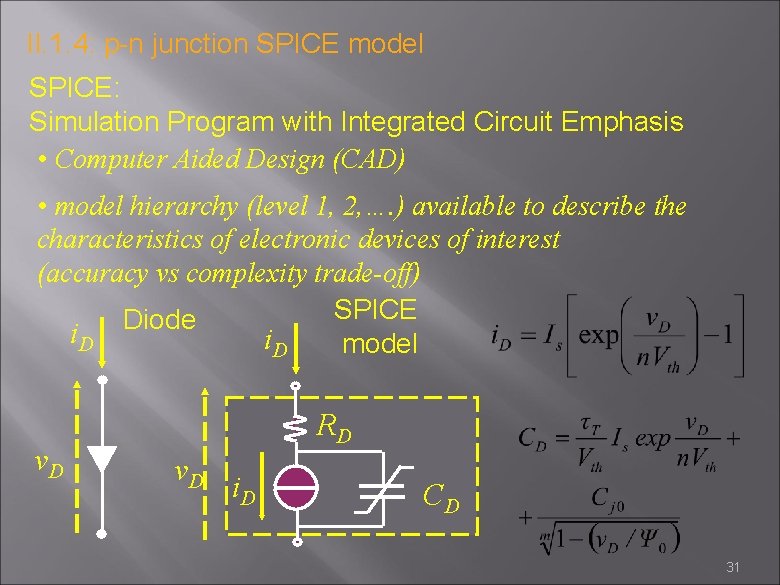

II. 1. 4: p-n junction SPICE model SPICE: Simulation Program with Integrated Circuit Emphasis • Computer Aided Design (CAD) • model hierarchy (level 1, 2, …. ) available to describe the characteristics of electronic devices of interest (accuracy vs complexity trade-off) SPICE Diode i. D model v. D RD v. D i. D CD 31

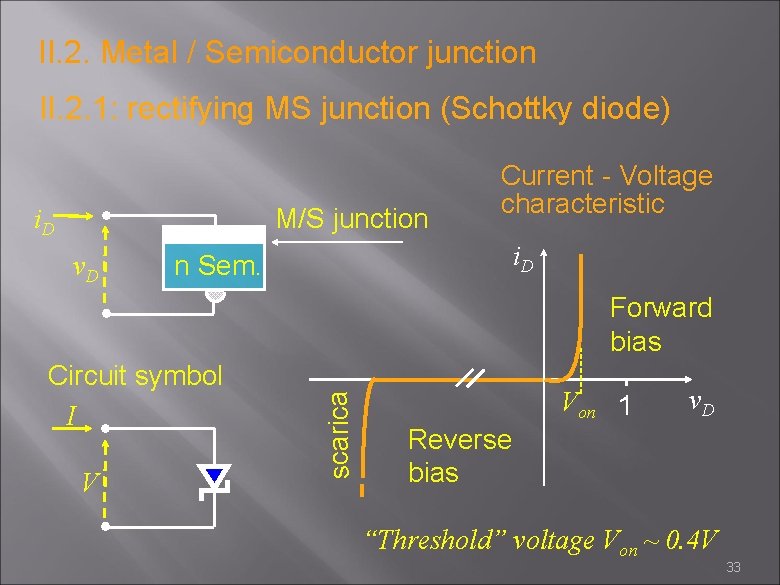

diode level 1 SPICE model Model parameters Reverse saturation current IS Symbol default IS 10 -14 A Ideality coefficient n N 1 Parasitic resistance RS RS 0 VJ 1 V CJ 0 0 F Capacitance grading coefficient m M 2 Transit time T TT 0 s Breakdown voltage VB BV V Built-in voltage 0 Equilibrium capacitance CJ 0 temperature T 300°K 32

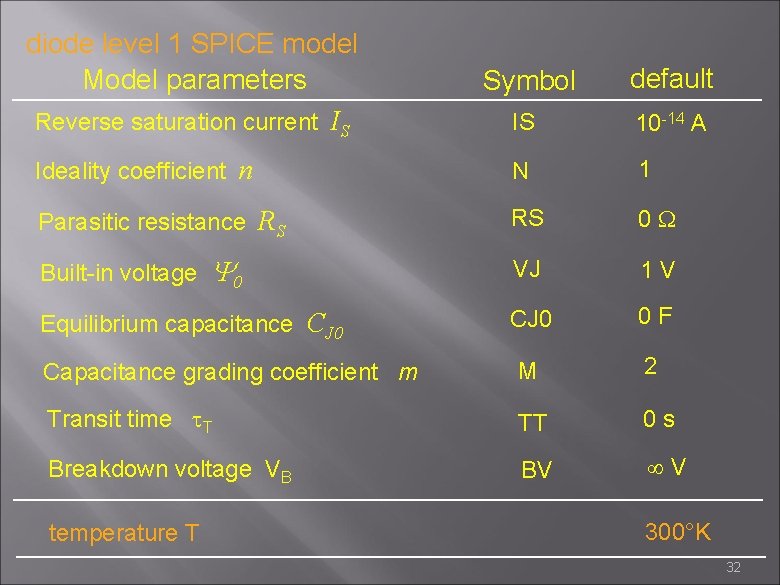

II. 2. Metal / Semiconductor junction II. 2. 1: rectifying MS junction (Schottky diode) M/S junction i. D v. D Current - Voltage characteristic i. D n Sem. Circuit symbol I V scarica Forward bias Von 1 v. D Reverse bias “Threshold” voltage Von ~ 0. 4 V 33

![Schottky diode law: [A] Vth=k. T/q : thermal voltage ~ 0. 026 V (T=300°K) Schottky diode law: [A] Vth=k. T/q : thermal voltage ~ 0. 026 V (T=300°K)](http://slidetodoc.com/presentation_image_h/2c32bb9adfb25a2a042aa0318e86d635/image-34.jpg)

Schottky diode law: [A] Vth=k. T/q : thermal voltage ~ 0. 026 V (T=300°K) IS: reverse saturation current ~ 0 n 1. 2 2 ideality coefficient (technology dependent) for v. D < - (3÷ 4)Vth i. D for v. D > (3÷ 4)Vth 0 1 v. D 34

Schottky diode vs. p-n junction diode: • higher reverse saturation current density (10 -7 – 10 -5 A/cm 2 vs 10 -11 A/cm 2) • lower (and not easily controllable) breakdown voltage • lower threshold voltage Von • M/S interface technology is rather complex and not easily reproducible Nowadays seldom used in microelectronics. In the past, significant use in TTL Schottky, low-power logic 35

![MS junction: forward current density Bias voltage V > (3 4) Vth I [A] MS junction: forward current density Bias voltage V > (3 4) Vth I [A]](http://slidetodoc.com/presentation_image_h/2c32bb9adfb25a2a042aa0318e86d635/image-36.jpg)

MS junction: forward current density Bias voltage V > (3 4) Vth I [A] pt. Si/n. Si p+/n Al/n. Si 0 0. 2 0. 4 0. 6 V on 0. 8 V [V] Lower threshold voltage Von wrt p-n junction 36

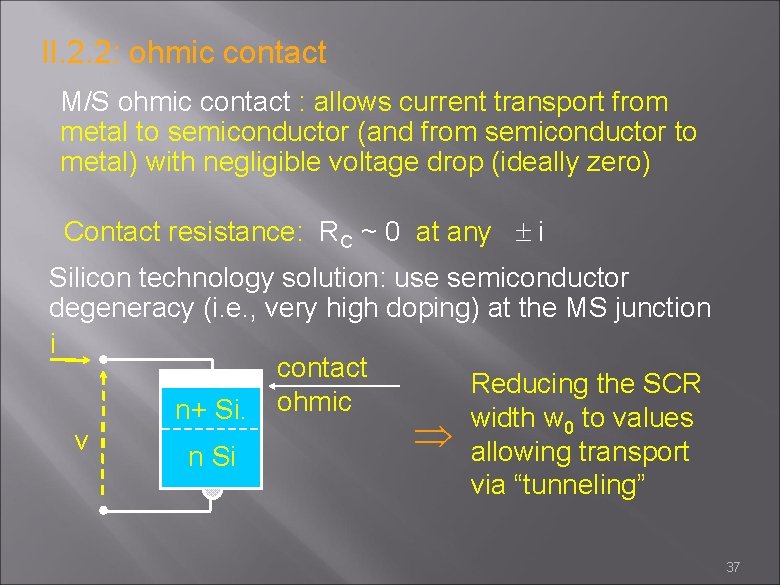

II. 2. 2: ohmic contact M/S ohmic contact : allows current transport from metal to semiconductor (and from semiconductor to metal) with negligible voltage drop (ideally zero) Contact resistance: RC ~ 0 at any ± i Silicon technology solution: use semiconductor degeneracy (i. e. , very high doping) at the MS junction i contact Reducing the SCR n+ Si. ohmic width w 0 to values Þ v allowing transport n Si via “tunneling” 37

- Slides: 37