PMD 101 Frank Effenberger Huawei Technologies Introduction Two

PMD 101 Frank Effenberger Huawei Technologies

Introduction • Two issues involve the interaction of PMD speed and sensitivity – FEC link rate increase – Dual rate OLT receivers • This presentation is meant to describe, in a simple way, the basic design of PMDs • This should allow the membership to make educated judgments when choosing alternatives that impact speed/sensitivity

Photodetectors • PIN diode – Responsivity (A/W) – Dark current (n. A) – Intrinsic capacitance (p. F) – Transit time (ps) • APD – All the above, plus… – Gain () – Excess Noise Factor ()

Noise, and the first amplifier • There are several noise sources – – RIN noise (from the transmitter) Shot noise (from signal and dark current) Excess noise (from avalanche gain process) Thermal noise (from the circuit itself) • In PIN receivers, thermal noise dominates • In APDs, shot and excess noise play a role • The SNR out of the first amplifier tells the story in any (properly designed) circuit

Trans-Impedance Amplifier • All modern optical PMDs use this topology • The key idea is that the amplifier’s gain reduces the effective impedance as regards the speed of response • Thus, a higher impedance value can be used (better SNR) while maintaining a high response speed (faster)

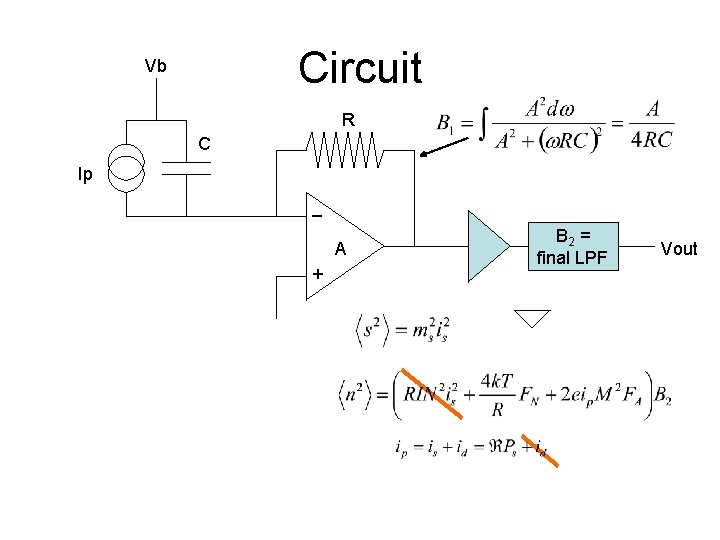

Circuit Vb R C Ip _ A + B 2 = final LPF Vout

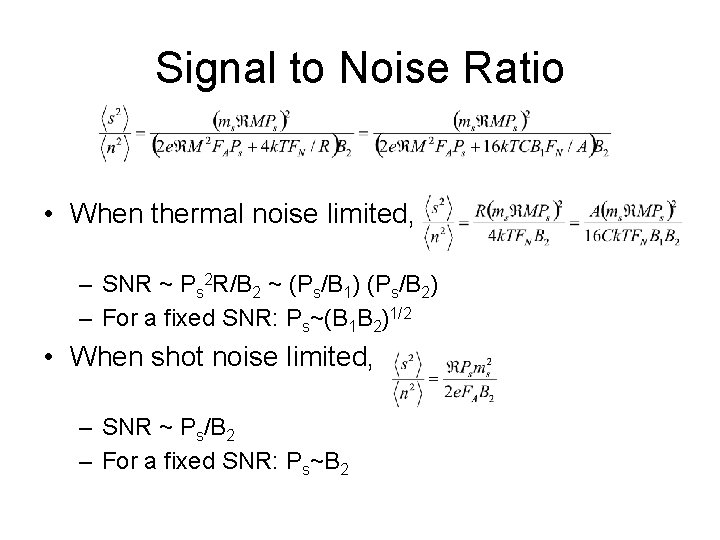

Signal to Noise Ratio • When thermal noise limited, – SNR ~ Ps 2 R/B 2 ~ (Ps/B 1) (Ps/B 2) – For a fixed SNR: Ps~(B 1 B 2)1/2 • When shot noise limited, – SNR ~ Ps/B 2 – For a fixed SNR: Ps~B 2

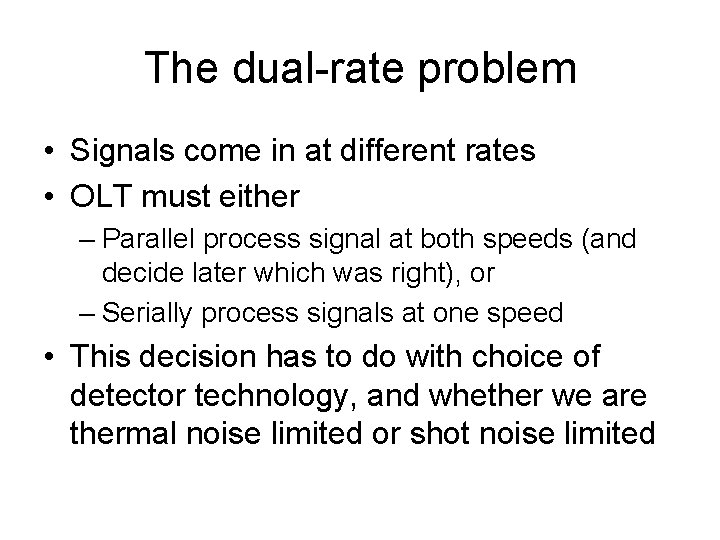

The dual-rate problem • Signals come in at different rates • OLT must either – Parallel process signal at both speeds (and decide later which was right), or – Serially process signals at one speed • This decision has to do with choice of detector technology, and whether we are thermal noise limited or shot noise limited

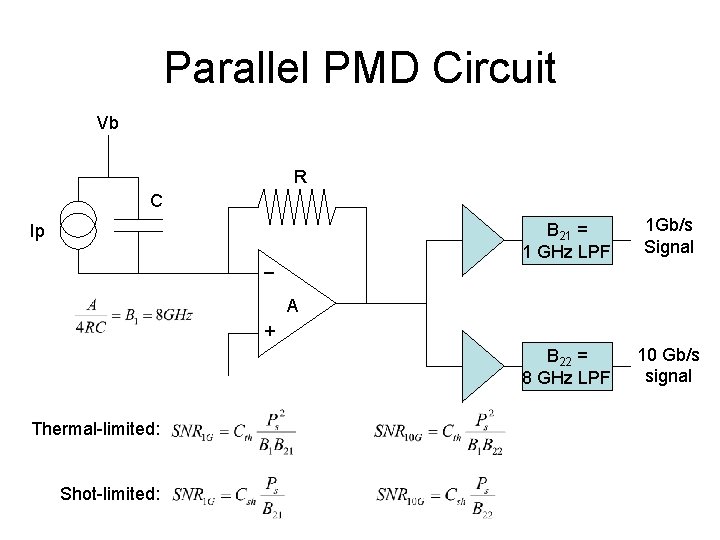

Parallel PMD Circuit Vb R C Ip _ B 21 = 1 GHz LPF 1 Gb/s Signal B 22 = 8 GHz LPF 10 Gb/s signal A + Thermal-limited: Shot-limited:

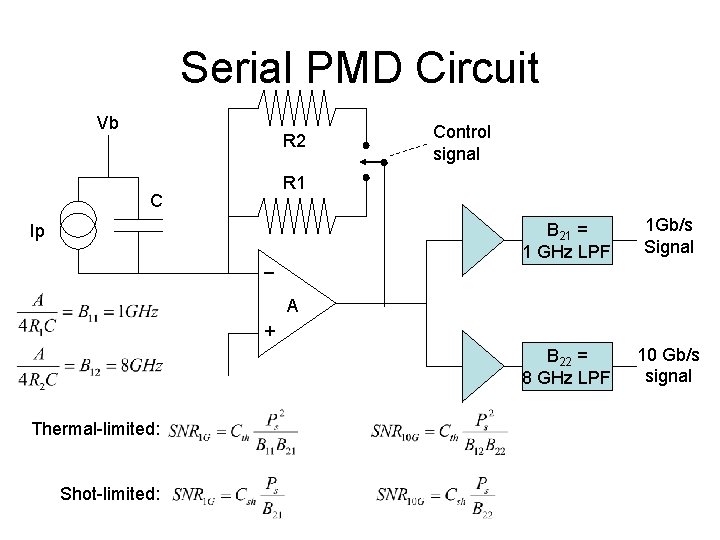

Serial PMD Circuit Vb R 2 Control signal R 1 C Ip _ B 21 = 1 GHz LPF 1 Gb/s Signal B 22 = 8 GHz LPF 10 Gb/s signal A + Thermal-limited: Shot-limited:

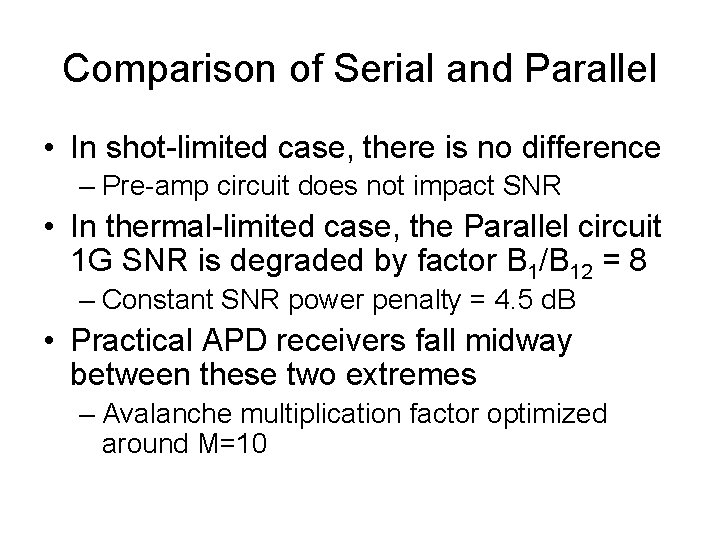

Comparison of Serial and Parallel • In shot-limited case, there is no difference – Pre-amp circuit does not impact SNR • In thermal-limited case, the Parallel circuit 1 G SNR is degraded by factor B 1/B 12 = 8 – Constant SNR power penalty = 4. 5 d. B • Practical APD receivers fall midway between these two extremes – Avalanche multiplication factor optimized around M=10

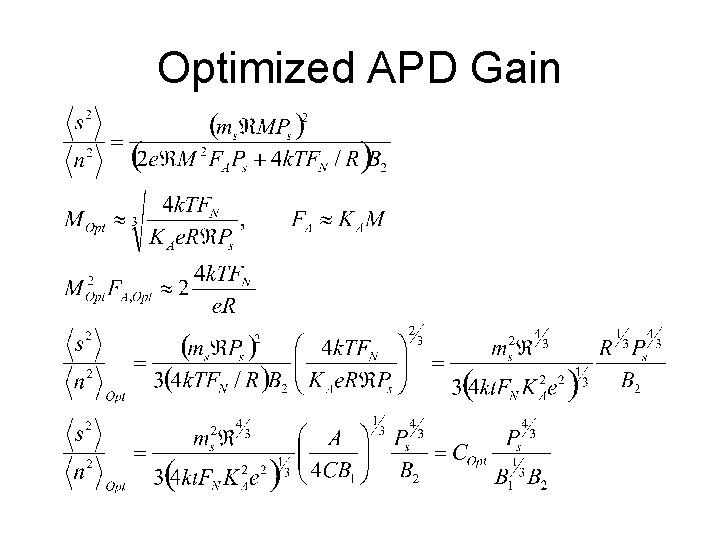

Optimized APD Gain

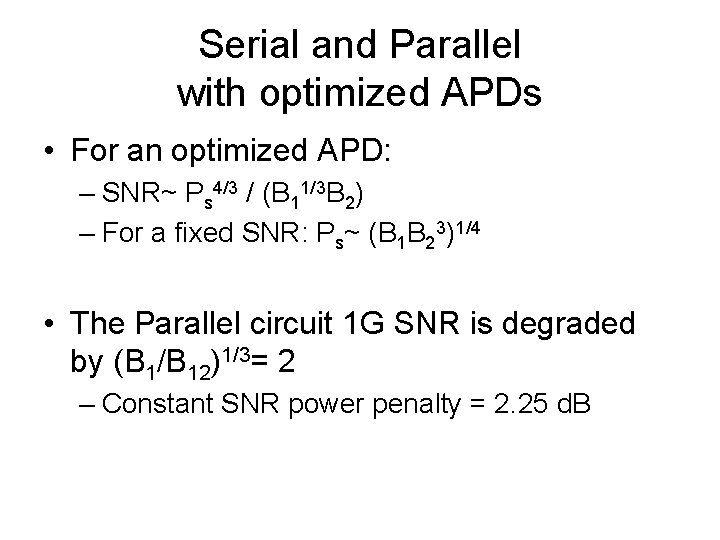

Serial and Parallel with optimized APDs • For an optimized APD: – SNR~ Ps 4/3 / (B 11/3 B 2) – For a fixed SNR: Ps~ (B 1 B 23)1/4 • The Parallel circuit 1 G SNR is degraded by (B 1/B 12)1/3= 2 – Constant SNR power penalty = 2. 25 d. B

Overall Conclusions • Dual rate optics present us with a choice: • Implement the ‘serial’ circuit approach – No sensitivity penalty – Complexity of transimpedance control • Implement the ‘parallel’ circuit approach – Simpler transimpedance amplifier – Approximately 2~3 d. B sensitivity penalty (APD) or 4. 5 d. B penalty (pin)

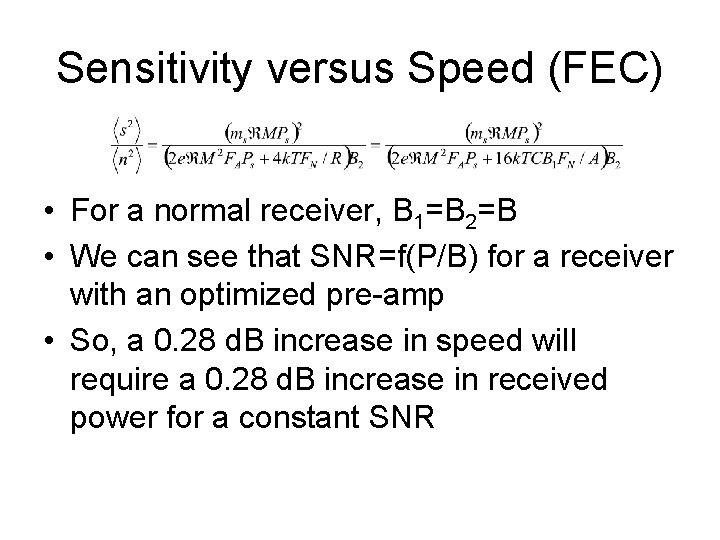

Sensitivity versus Speed (FEC) • For a normal receiver, B 1=B 2=B • We can see that SNR=f(P/B) for a receiver with an optimized pre-amp • So, a 0. 28 d. B increase in speed will require a 0. 28 d. B increase in received power for a constant SNR

- Slides: 15