PLL with VCO Band Selection KoChi Kuo Auto

PLL with VCO Band Selection Ko-Chi Kuo

Auto Band Selection Outline PART I: Concept Review n n Auto Band Selection Concept Auto Band Selection Interface with other Blocks(PLLs, VCOs, S. I. ) PART II: Circuit Design Review n n n n Divide 8 and ECL to CMOS Circuit and Simulation 9 Bit Programmable Counter and Simulation Band Selection Interface Schematic and Simulation Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Simulation Summary

PART I: Band Selection Concept Review PART I: Concept Review n n Auto Band Selection Concept Auto Band Selection Interface with other Blocks(PLLs, VCOs, S. I. )

Auto Band Selection Concept n n n The need of Auto Band Selection Multi-Band Solution Using CMOS Binary Digital Varactor Frequency Coverage of RFVCO over 8 Bands Requirements for Band Selection Algorithm to Work How the Band Selection Works Frequency Comparison Concept Frequency Resolution with 8 Band RF VCO Frequency Resolution with 4 Band IF VCO Band Select Circuit Design Band Select Circuit Timing Diagram Summary

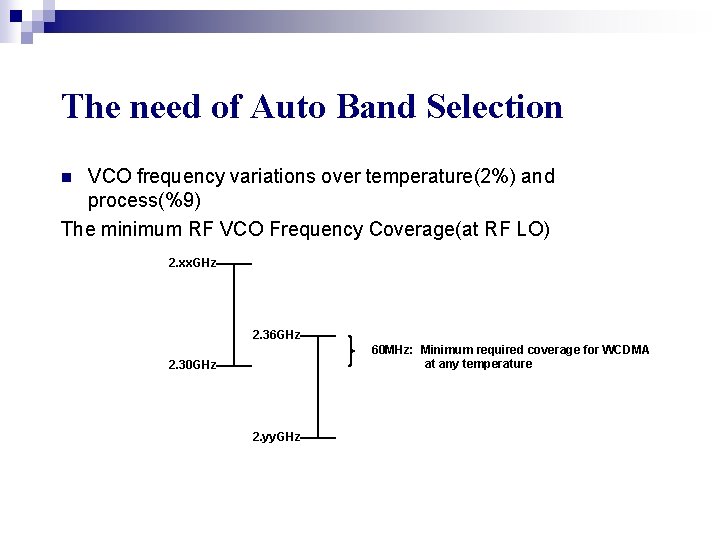

The need of Auto Band Selection VCO frequency variations over temperature(2%) and process(%9) The minimum RF VCO Frequency Coverage(at RF LO) n 2. xx. GHz 2. 36 GHz 60 MHz: Minimum required coverage for WCDMA at any temperature 2. 30 GHz 2. yy. GHz

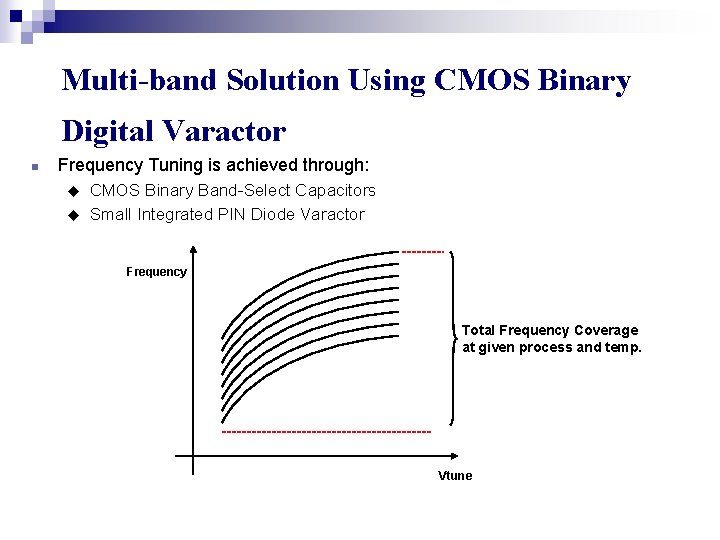

Multi-band Solution Using CMOS Binary Digital Varactor n Frequency Tuning is achieved through: u u CMOS Binary Band-Select Capacitors Small Integrated PIN Diode Varactor Frequency Total Frequency Coverage at given process and temp. Vtune

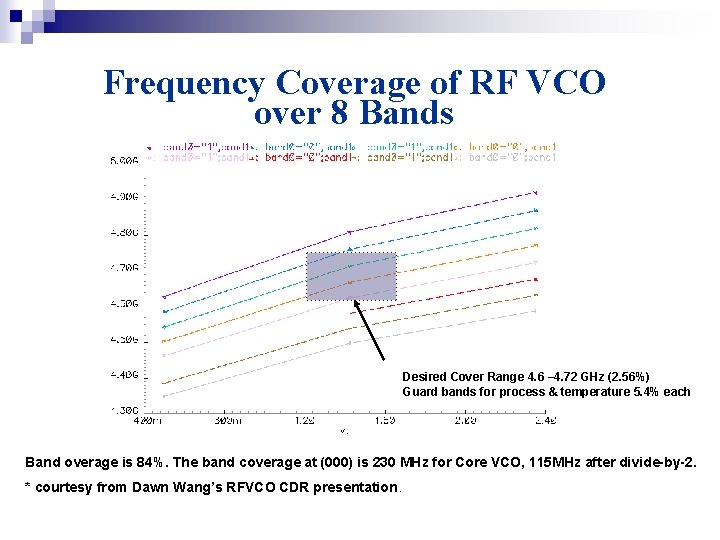

Frequency Coverage of RF VCO over 8 Bands Desired Cover Range 4. 6 – 4. 72 GHz (2. 56%) Guard bands for process & temperature 5. 4% each Band overage is 84%. The band coverage at (000) is 230 MHz for Core VCO, 115 MHz after divide-by-2. * courtesy from Dawn Wang’s RFVCO CDR presentation.

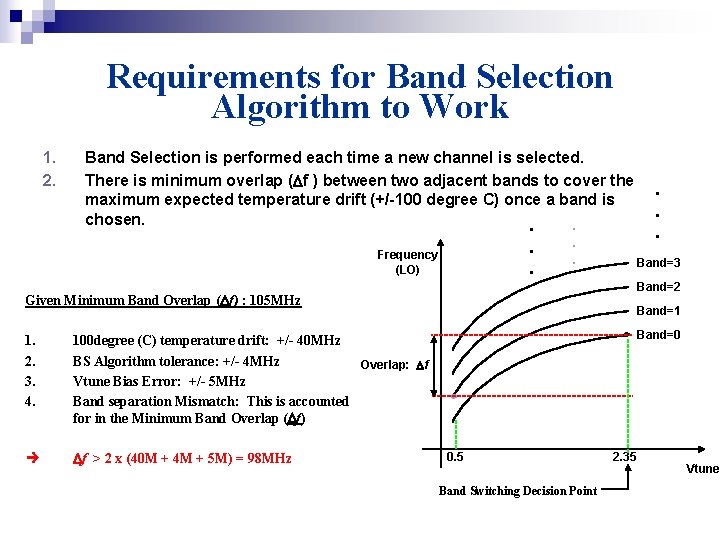

Requirements for Band Selection Algorithm to Work 1. 2. Band Selection is performed each time a new channel is selected. There is minimum overlap ( f ) between two adjacent bands to cover the maximum expected temperature drift (+/-100 degree C) once a band is chosen. . . Frequency (LO) . . Band=3 Band=2 Given Minimum Band Overlap ( f) : 105 MHz 1. 2. 3. 4. 100 degree (C) temperature drift: +/- 40 MHz BS Algorithm tolerance: +/- 4 MHz Overlap: f Vtune Bias Error: +/- 5 MHz Band separation Mismatch: This is accounted for in the Minimum Band Overlap ( f) è f > 2 x (40 M + 4 M + 5 M) = 98 MHz . . . Band=1 Band=0 0. 5 Band Switching Decision Point 2. 35 Vtune

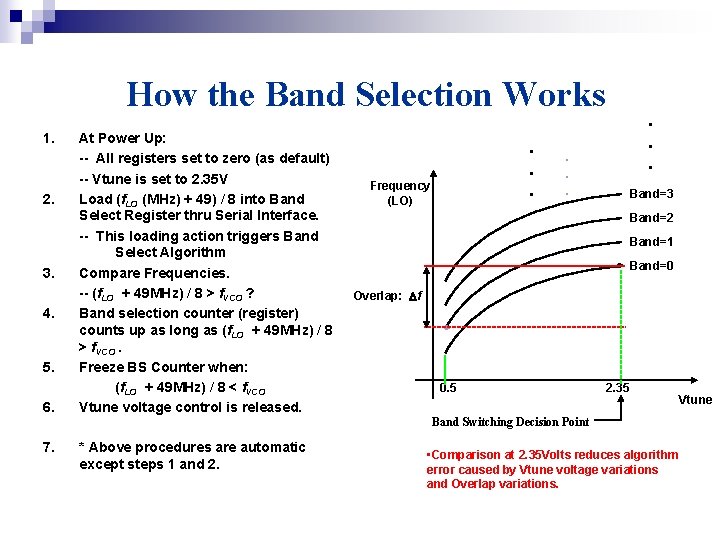

How the Band Selection Works 1. 2. 3. 4. 5. 6. At Power Up: -- All registers set to zero (as default) -- Vtune is set to 2. 35 V Load (f. LO (MHz) + 49) / 8 into Band Select Register thru Serial Interface. -- This loading action triggers Band Select Algorithm Compare Frequencies. -- (f. LO + 49 MHz) / 8 > f. VCO ? Band selection counter (register) counts up as long as (f. LO + 49 MHz) / 8 > f. VCO. Freeze BS Counter when: (f. LO + 49 MHz) / 8 < f. VCO Vtune voltage control is released. . Frequency (LO) . . . Band=3 Band=2 Band=1 Band=0 Overlap: f 0. 5 2. 35 Band Switching Decision Point 7. * Above procedures are automatic except steps 1 and 2. • Comparison at 2. 35 Volts reduces algorithm error caused by Vtune voltage variations and Overlap variations. Vtune

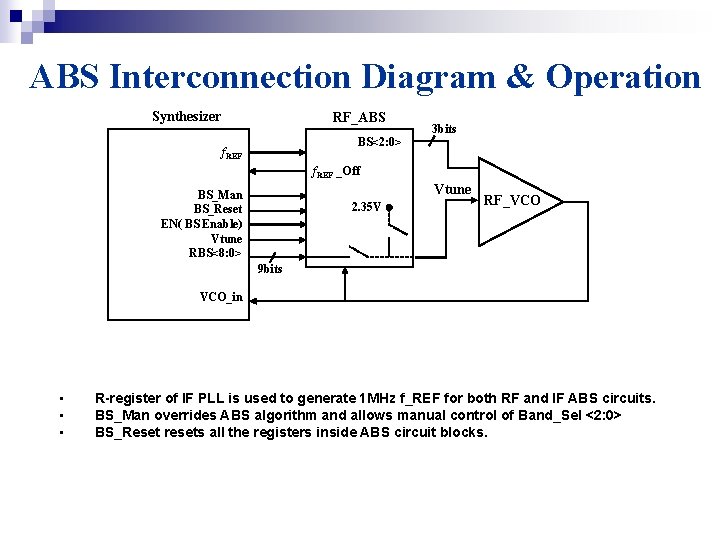

ABS Interconnection Diagram & Operation Synthesizer RF_ABS BS<2: 0> f. REF 3 bits f. REF _Off Vtune BS_Man BS_Reset EN( BS Enable) Vtune RBS<8: 0> 2. 35 V RF_VCO 9 bits VCO_in • • • R-register of IF PLL is used to generate 1 MHz f_REF for both RF and IF ABS circuits. BS_Man overrides ABS algorithm and allows manual control of Band_Sel <2: 0> BS_Reset resets all the registers inside ABS circuit blocks.

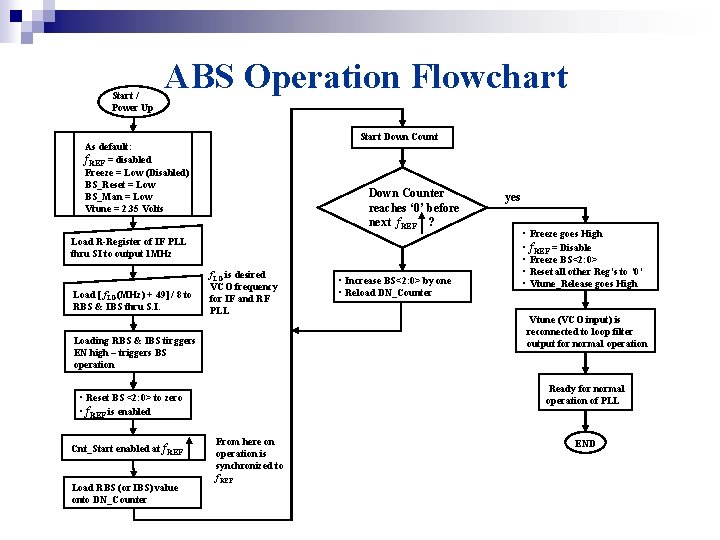

Start / Power Up ABS Operation Flowchart Start Down Count As default: f. REF = disabled Freeze = Low (Disabled) BS_Reset = Low BS_Man = Low Vtune = 2. 35 Volts Down Counter reaches ‘ 0’ before next f. REF ? Load R-Register of IF PLL thru SI to output 1 MHz Load [ f. LO(MHz) + 49] / 8 to RBS & IBS thru S. I. f. LO is desired VCO frequency for IF and RF PLL Loading RBS & IBS tirggers EN high – triggers BS operation Load RBS (or IBS) value onto DN_Counter • Freeze goes High • f. REF = Disable • Freeze BS<2: 0> • Reset all other Reg’s to ‘ 0’ • Vtune_Release goes High Vtune (VCO input) is reconnected to loop filter output for normal operation Ready for normal operation of PLL • Reset BS <2: 0> to zero • f. REF is enabled Cnt_Start enabled at f. REF • Increase BS<2: 0> by one • Reload DN_Counter yes From here on operation is synchronized to f. REF END

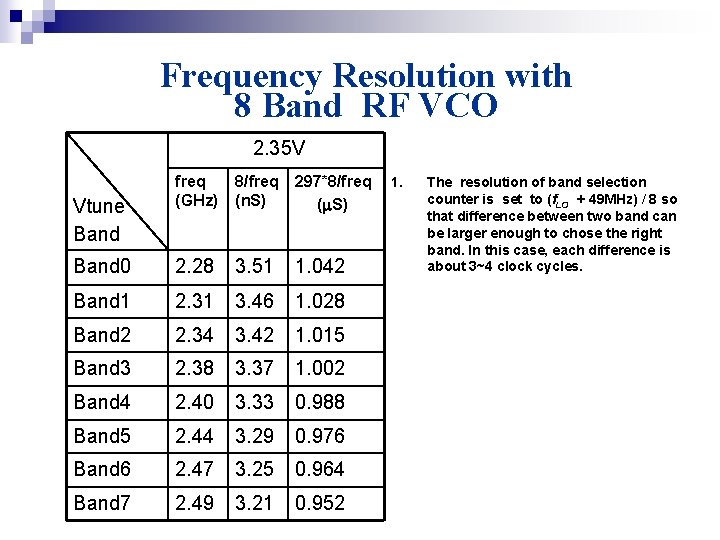

Frequency Resolution with 8 Band RF VCO 2. 35 V freq (GHz) 8/freq (n. S) 297*8/freq ( S) Band 0 2. 28 3. 51 1. 042 Band 1 2. 31 3. 46 1. 028 Band 2 2. 34 3. 42 1. 015 Band 3 2. 38 3. 37 1. 002 Band 4 2. 40 3. 33 0. 988 Band 5 2. 44 3. 29 0. 976 Band 6 2. 47 3. 25 0. 964 Band 7 2. 49 3. 21 0. 952 Vtune Band 1. The resolution of band selection counter is set to (f. LO + 49 MHz) / 8 so that difference between two band can be larger enough to chose the right band. In this case, each difference is about 3~4 clock cycles.

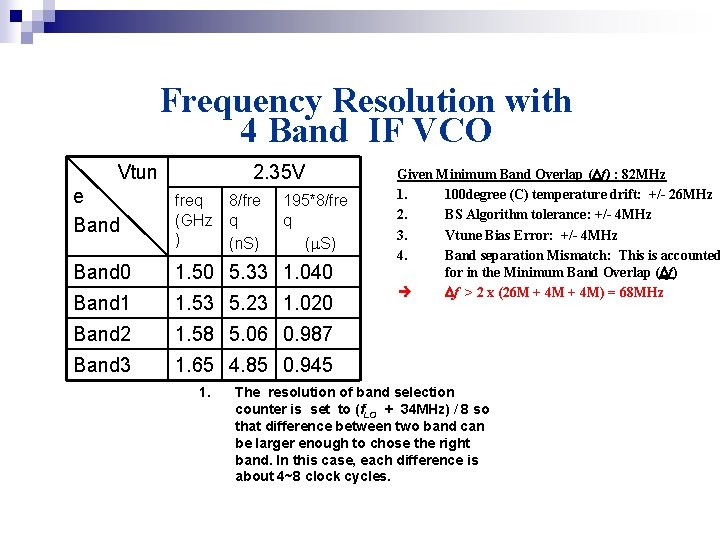

Frequency Resolution with 4 Band IF VCO Vtun 2. 35 V e Band freq (GHz ) Band 0 1. 50 5. 33 1. 040 Band 1 1. 53 5. 23 1. 020 Band 2 1. 58 5. 06 0. 987 Band 3 1. 65 4. 85 0. 945 1. 8/fre q (n. S) 195*8/fre q ( S) Given Minimum Band Overlap ( f) : 82 MHz 1. 100 degree (C) temperature drift: +/- 26 MHz 2. BS Algorithm tolerance: +/- 4 MHz 3. Vtune Bias Error: +/- 4 MHz 4. Band separation Mismatch: This is accounted for in the Minimum Band Overlap ( f) è f > 2 x (26 M + 4 M) = 68 MHz The resolution of band selection counter is set to (f. LO + 34 MHz) / 8 so that difference between two band can be larger enough to chose the right band. In this case, each difference is about 4~8 clock cycles.

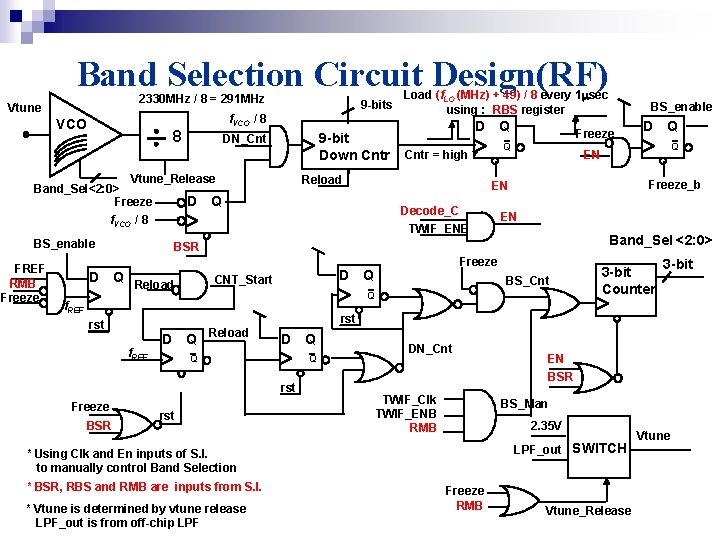

Band Selection Circuit Design(RF) 2330 MHz / 8 = 291 MHz Vtune VCO 9 -bits f. VCO / 8 8 9 -bit Down Cntr DN_Cnt Vtune_Release Band_Sel<2: 0> Freeze D Q FREF RMB Freeze D Q CNT_Start Freeze_b EN Band_Sel <2: 0> Freeze BS_Cnt Q 3 -bit Counter 3 -bit rst f. REF D Q Reload D Q Q Q rst BSR Q EN D Q EN BSR Reload BS_enable Freeze Q Cntr = high ? Decode_C TWIF_ENB f. REF Freeze D Q Reload f. VCO / 8 BS_enable Load (f. LO (MHz) + 49) / 8 every 1 sec using : RBS register rst DN_Cnt TWIF_Clk TWIF_ENB RMB BS_Man 2. 35 V LPF_out SWITCH * Using Clk and En inputs of S. I. to manually control Band Selection * BSR, RBS and RMB are inputs from S. I. * Vtune is determined by vtune release LPF_out is from off-chip LPF EN BSR Freeze RMB Vtune_Release Vtune

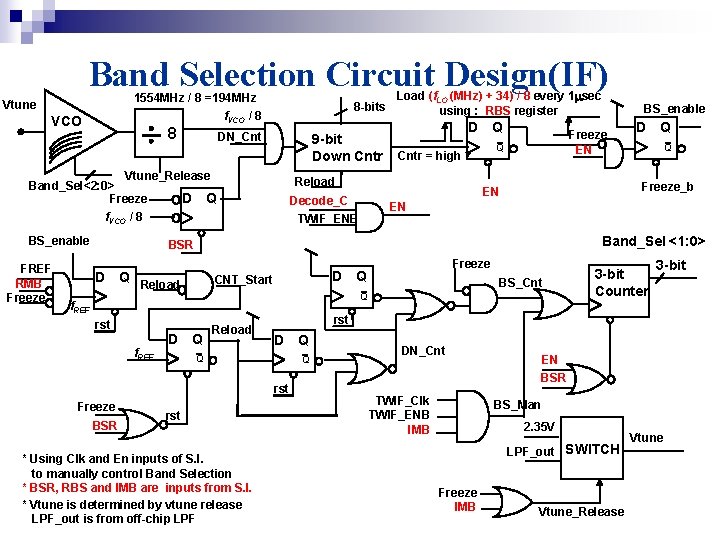

Band Selection Circuit Design(IF) 1554 MHz / 8 =194 MHz Vtune VCO 8 -bits f. VCO / 8 8 DN_Cnt 9 -bit Down Cntr Vtune_Release Band_Sel<2: 0> Freeze D Q FREF RMB Freeze D Q Decode_C TWIF_ENB EN CNT_Start BSR BS_Cnt Q D Q Reload D Q Q rst * Using Clk and En inputs of S. I. to manually control Band Selection * BSR, RBS and IMB are inputs from S. I. * Vtune is determined by vtune release LPF_out is from off-chip LPF 3 -bit Counter 3 -bit rst Q rst Freeze D Q f. REF Q Band_Sel <1: 0> Reload rst D Q Freeze_b EN BSR D Q BS_enable Freeze EN Q Cntr = high ? Reload f. VCO / 8 BS_enable Load (f. LO (MHz) + 34) / 8 every 1 sec using : RBS register DN_Cnt EN BSR TWIF_Clk TWIF_ENB IMB BS_Man 2. 35 V LPF_out SWITCH Freeze IMB Vtune_Release Vtune

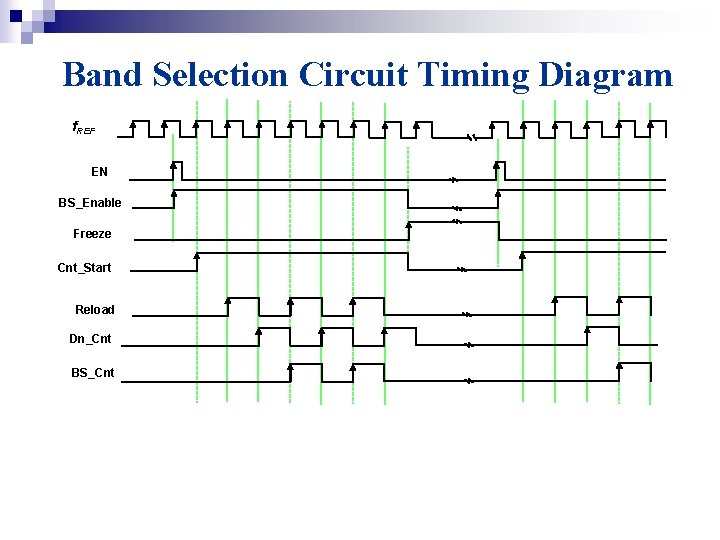

Band Selection Circuit Timing Diagram f. REF EN BS_Enable Freeze Cnt_Start Reload Dn_Cnt BS_Cnt

Summary of Auto Band Selection Algorithm n n Band Selection is necessary for the RF and IF VCOs in order to overcome the VCO frequency drift due to the process and temperature variations. The proposed Band Selection Algorithm takes 2 sec per band less than 20 sec(RF)/12 sec(IF) to accomplish Automatic Band Selection. Frequency comparison is made through counting the frequency of f. RF/8 signal during 1 sec (all digital solution. ) Small overhead in silicon area and No Extra Current Consumption.

PART I: Band Selection Concept Review PART I: Concept Review n n Auto Band Selection Concept Auto Band Selection Interface with other Blocks(PLLs, VCOs, S. I. )

Auto Band Selection Interface with other Blocks(PLL, VCO, LPF, S. I. ) n n RF Top Schematic of ABS, PLL, VCO, LPF, and S. I. IF Top Schematic of ABS, PLL, VCO, LPF, and S. I.

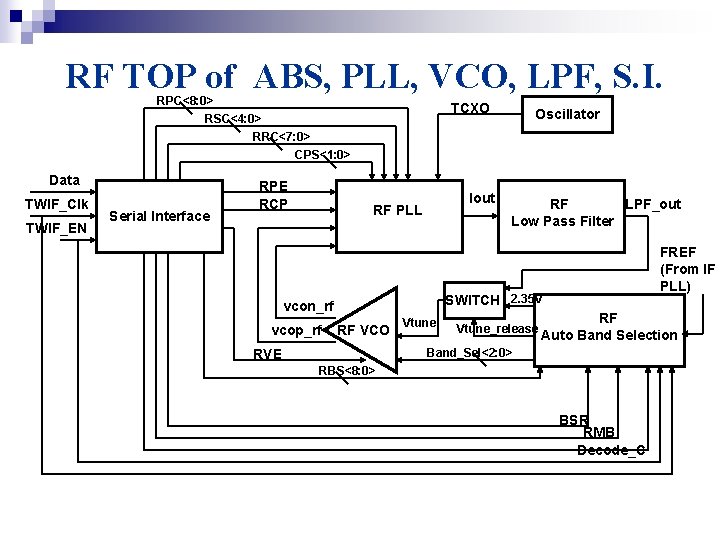

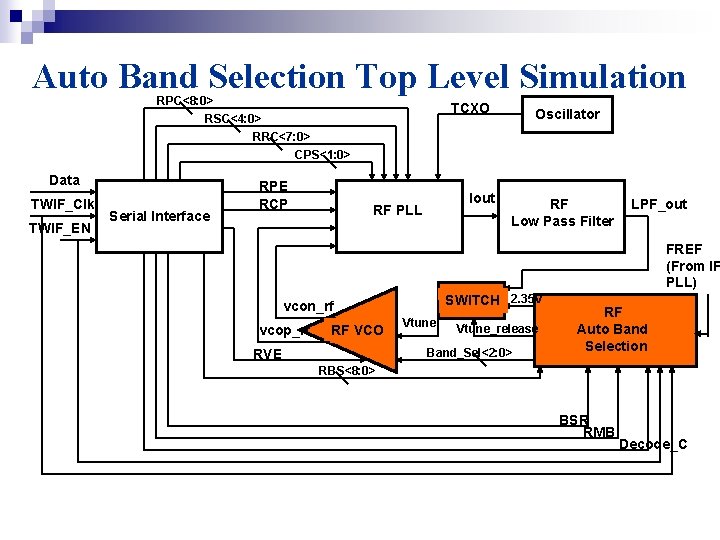

RF TOP of ABS, PLL, VCO, LPF, S. I. RPC<8: 0> RSC<4: 0> TCXO Oscillator RRC<7: 0> CPS<1: 0> Data TWIF_Clk TWIF_EN Serial Interface RPE RCP Iout RF PLL FREF (From IF PLL) SWITCH 2. 35 V vcon_rf vcop_rf RF LPF_out Low Pass Filter RF VCO Vtune_release RF Auto Band Selection Band_Sel<2: 0> RVE RBS<8: 0> BSR RMB Decode_C

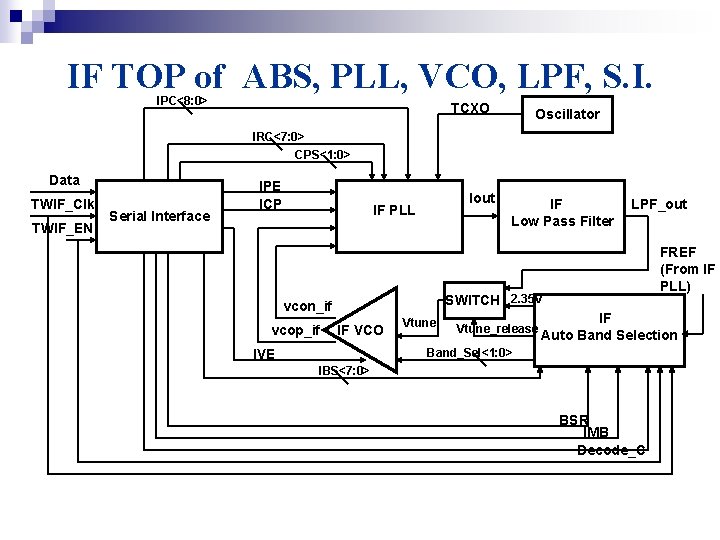

IF TOP of ABS, PLL, VCO, LPF, S. I. IPC<8: 0> TCXO Oscillator IRC<7: 0> CPS<1: 0> Data TWIF_Clk TWIF_EN Serial Interface IPE ICP Iout IF PLL LPF_out FREF (From IF PLL) SWITCH 2. 35 V vcon_if vcop_if IF Low Pass Filter IF VCO Vtune_release IF Auto Band Selection Band_Sel<1: 0> IVE IBS<7: 0> BSR IMB Decode_C

PART II: Band Selection Circuit Design Review PART II: Circuit Design Review n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Band Selection Interface Schematic and Simulation Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

Auto Band Selection: Divide 8, Biasing, CML to CMOS Circuits n n Auto Band Selection: Divide 8, Biasing Corner Simulation Condition Circuit Simulation Result Simulation Summary

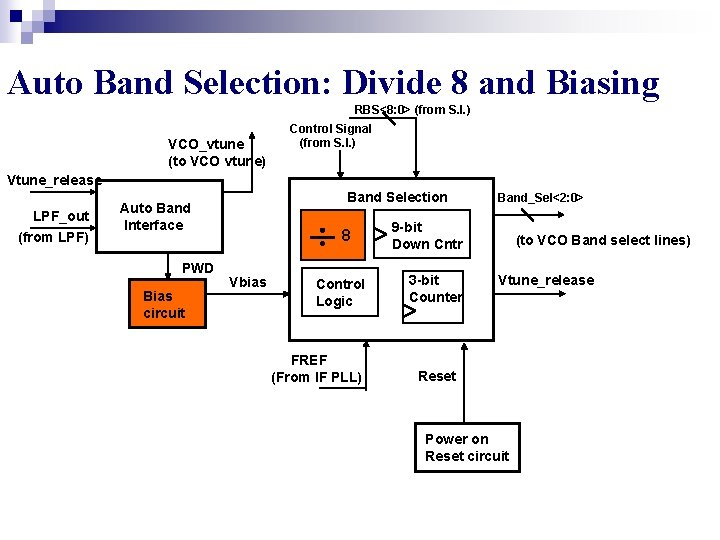

Auto Band Selection: Divide 8 and Biasing RBS<8: 0> (from S. I. ) VCO_vtune (to VCO vtune) Control Signal (from S. I. ) Vtune_release LPF_out (from LPF) Band Selection Auto Band Interface PWD Bias circuit 8 Vbias Control Logic FREF (From IF PLL) Band_Sel<2: 0> 9 -bit Down Cntr 3 -bit Counter (to VCO Band select lines) Vtune_release Reset Power on Reset circuit

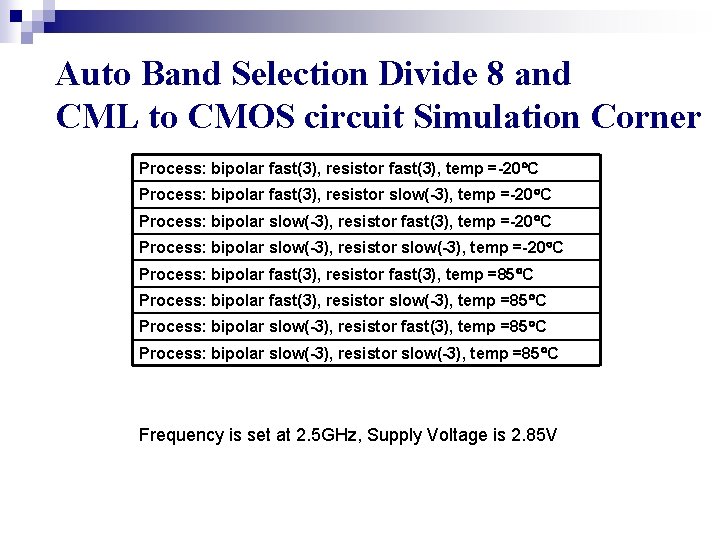

Auto Band Selection Divide 8 and CML to CMOS circuit Simulation Corner Process: bipolar fast(3), resistor fast(3), temp =-20 C Process: bipolar fast(3), resistor slow(-3), temp =-20 C Process: bipolar slow(-3), resistor fast(3), temp =-20 C Process: bipolar slow(-3), resistor slow(-3), temp =-20 C Process: bipolar fast(3), resistor fast(3), temp =85 C Process: bipolar fast(3), resistor slow(-3), temp =85 C Process: bipolar slow(-3), resistor fast(3), temp =85 C Process: bipolar slow(-3), resistor slow(-3), temp =85 C Frequency is set at 2. 5 GHz, Supply Voltage is 2. 85 V

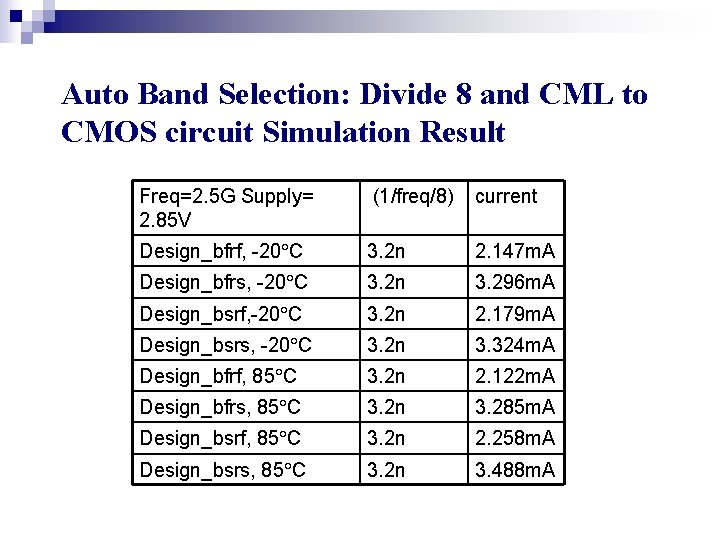

Auto Band Selection: Divide 8 and CML to CMOS circuit Simulation Result Freq=2. 5 G Supply= 2. 85 V (1/freq/8) current Design_bfrf, -20 C 3. 2 n 2. 147 m. A Design_bfrs, -20 C 3. 2 n 3. 296 m. A Design_bsrf, -20 C 3. 2 n 2. 179 m. A Design_bsrs, -20 C 3. 2 n 3. 324 m. A Design_bfrf, 85 C 3. 2 n 2. 122 m. A Design_bfrs, 85 C 3. 2 n 3. 285 m. A Design_bsrf, 85 C 3. 2 n 2. 258 m. A Design_bsrs, 85 C 3. 2 n 3. 488 m. A

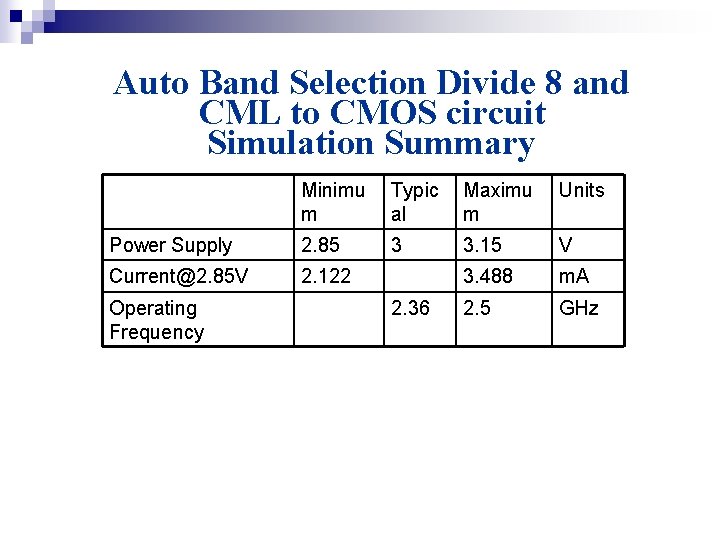

Auto Band Selection Divide 8 and CML to CMOS circuit Simulation Summary Minimu m Typic al Maximu m Units Power Supply 2. 85 3 3. 15 V Current@2. 85 V 2. 122 3. 488 m. A 2. 5 GHz Operating Frequency 2. 36

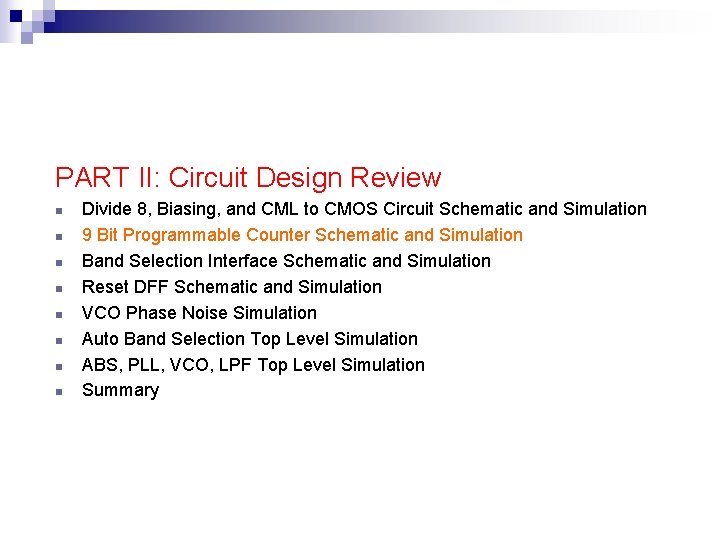

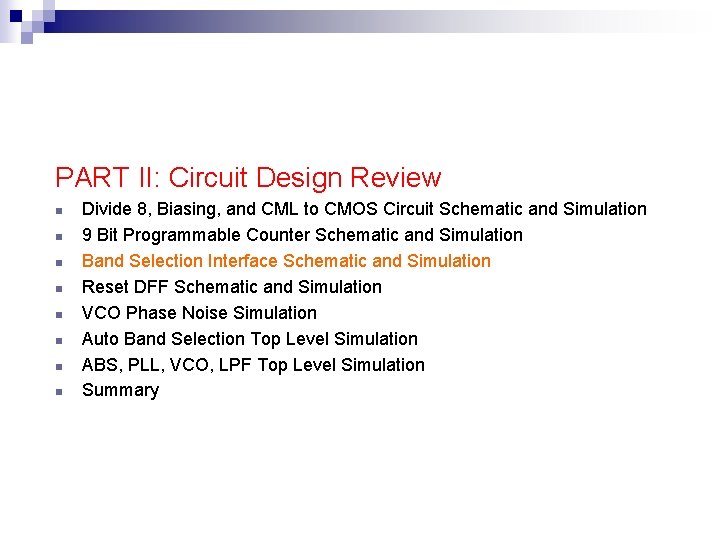

PART II: Circuit Design Review n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Band Selection Interface Schematic and Simulation Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

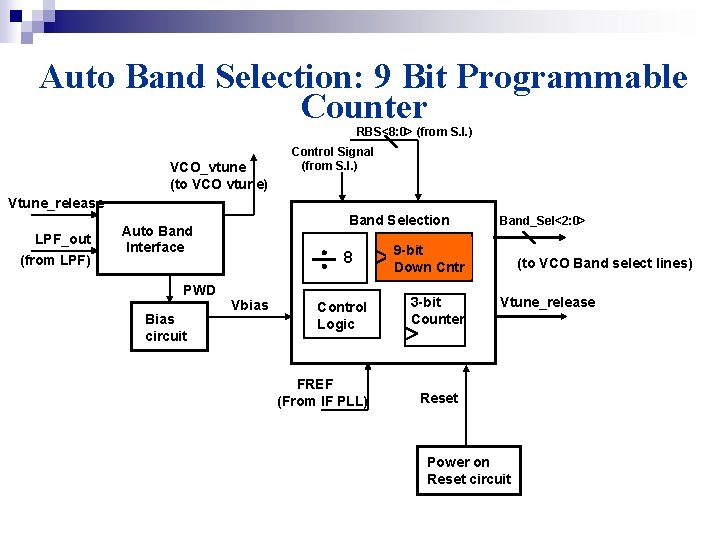

Auto Band Selection: 9 Bit Programmable Counter n n n Auto Band Selection: 9 Bit Programmable Counter Corner Simulation Condition Circuit Simulation Result Power down/up Simulation Result Corner Simulation Result Simulation Summary

Auto Band Selection: 9 Bit Programmable Counter RBS<8: 0> (from S. I. ) VCO_vtune (to VCO vtune) Control Signal (from S. I. ) Vtune_release LPF_out (from LPF) Band Selection Auto Band Interface PWD Bias circuit 8 Vbias Control Logic FREF (From IF PLL) Band_Sel<2: 0> 9 -bit Down Cntr 3 -bit Counter (to VCO Band select lines) Vtune_release Reset Power on Reset circuit

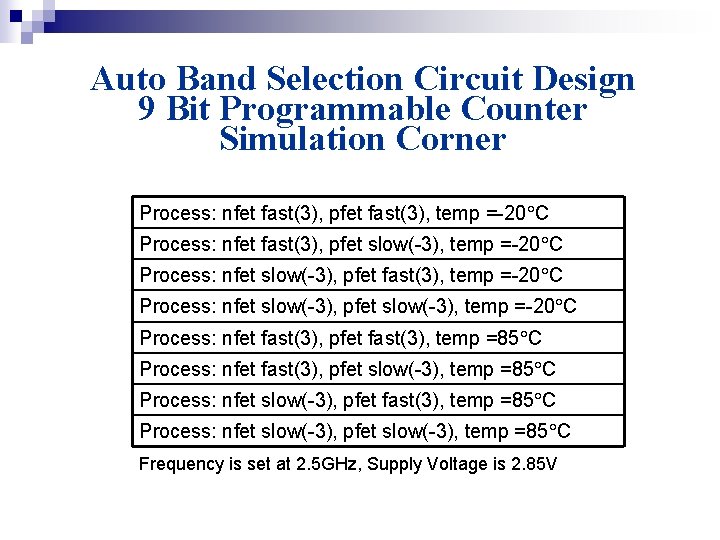

Auto Band Selection Circuit Design 9 Bit Programmable Counter Simulation Corner Process: nfet fast(3), pfet fast(3), temp =-20 C Process: nfet fast(3), pfet slow(-3), temp =-20 C Process: nfet slow(-3), pfet fast(3), temp =-20 C Process: nfet slow(-3), pfet slow(-3), temp =-20 C Process: nfet fast(3), pfet fast(3), temp =85 C Process: nfet fast(3), pfet slow(-3), temp =85 C Process: nfet slow(-3), pfet fast(3), temp =85 C Process: nfet slow(-3), pfet slow(-3), temp =85 C Frequency is set at 2. 5 GHz, Supply Voltage is 2. 85 V

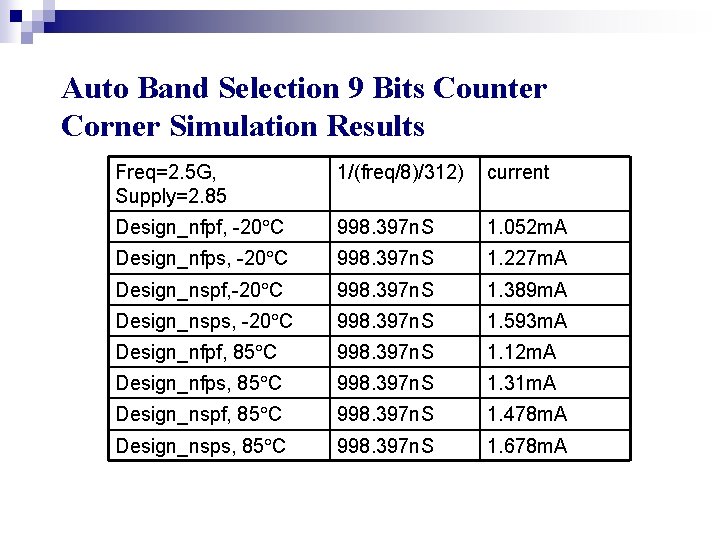

Auto Band Selection 9 Bits Counter Corner Simulation Results Freq=2. 5 G, Supply=2. 85 1/(freq/8)/312) current Design_nfpf, -20 C 998. 397 n. S 1. 052 m. A Design_nfps, -20 C 998. 397 n. S 1. 227 m. A Design_nspf, -20 C 998. 397 n. S 1. 389 m. A Design_nsps, -20 C 998. 397 n. S 1. 593 m. A Design_nfpf, 85 C 998. 397 n. S 1. 12 m. A Design_nfps, 85 C 998. 397 n. S 1. 31 m. A Design_nspf, 85 C 998. 397 n. S 1. 478 m. A Design_nsps, 85 C 998. 397 n. S 1. 678 m. A

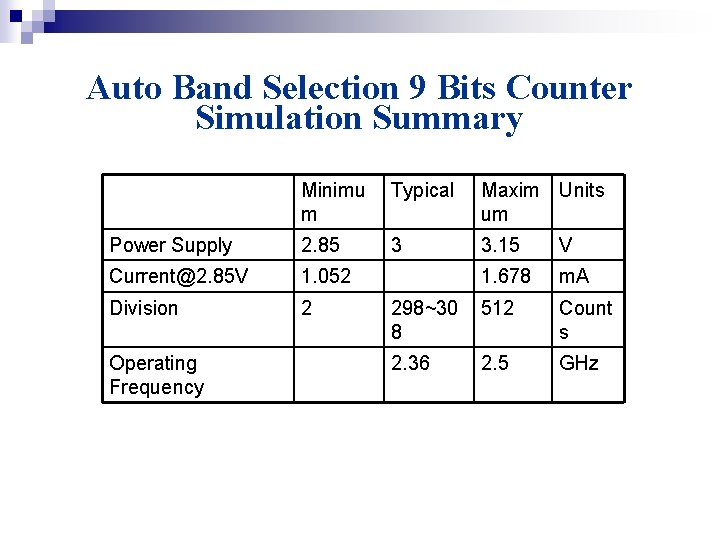

Auto Band Selection 9 Bits Counter Simulation Summary Minimu m Typical Maxim Units um Power Supply 2. 85 3 3. 15 V Current@2. 85 V 1. 052 1. 678 m. A Division 2 298~30 8 512 Count s 2. 36 2. 5 GHz Operating Frequency

PART II: Circuit Design Review n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Band Selection Interface Schematic and Simulation Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

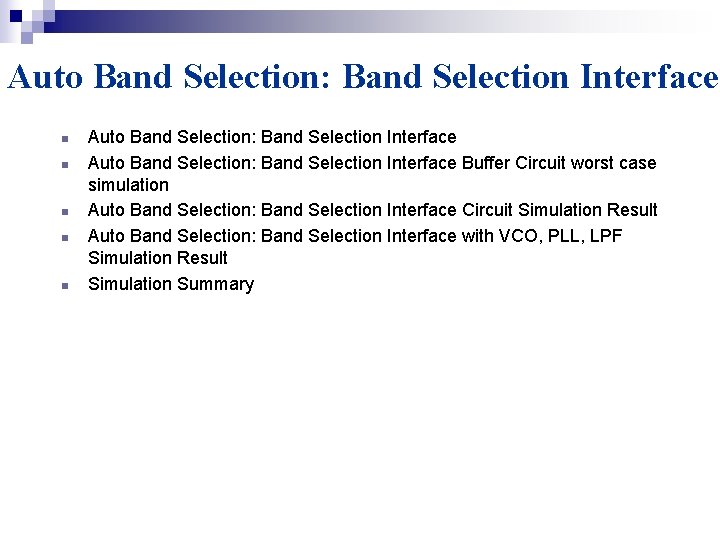

Auto Band Selection: Band Selection Interface n n n Auto Band Selection: Band Selection Interface Buffer Circuit worst case simulation Auto Band Selection: Band Selection Interface Circuit Simulation Result Auto Band Selection: Band Selection Interface with VCO, PLL, LPF Simulation Result Simulation Summary

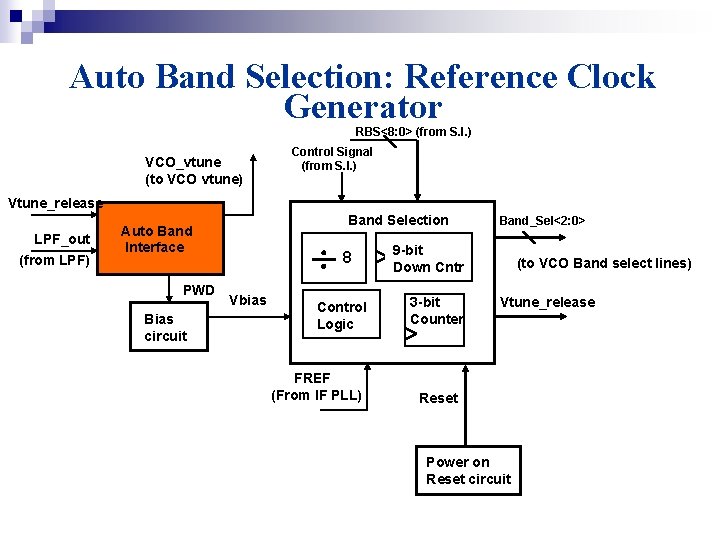

Auto Band Selection: Reference Clock Generator RBS<8: 0> (from S. I. ) VCO_vtune (to VCO vtune) Control Signal (from S. I. ) Vtune_release LPF_out (from LPF) Band Selection Auto Band Interface PWD Bias circuit 8 Vbias Control Logic FREF (From IF PLL) Band_Sel<2: 0> 9 -bit Down Cntr 3 -bit Counter (to VCO Band select lines) Vtune_release Reset Power on Reset circuit

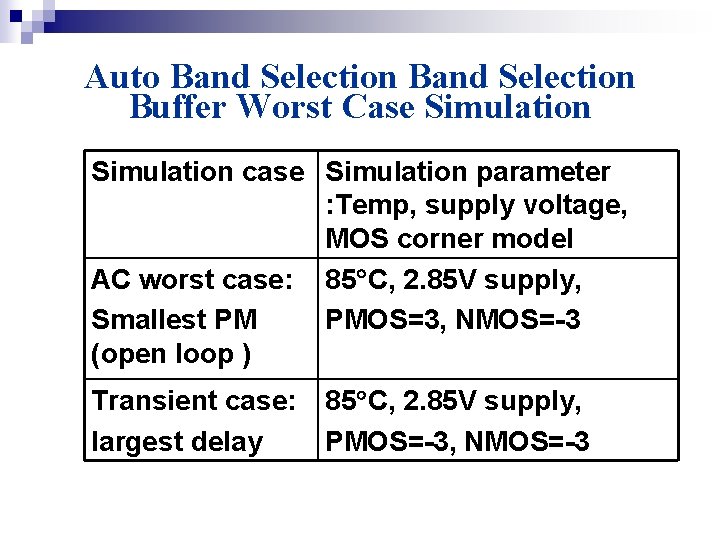

Auto Band Selection Buffer Worst Case Simulation case Simulation parameter : Temp, supply voltage, MOS corner model AC worst case: 85 C, 2. 85 V supply, Smallest PM PMOS=3, NMOS=-3 (open loop ) Transient case: largest delay 85 C, 2. 85 V supply, PMOS=-3, NMOS=-3

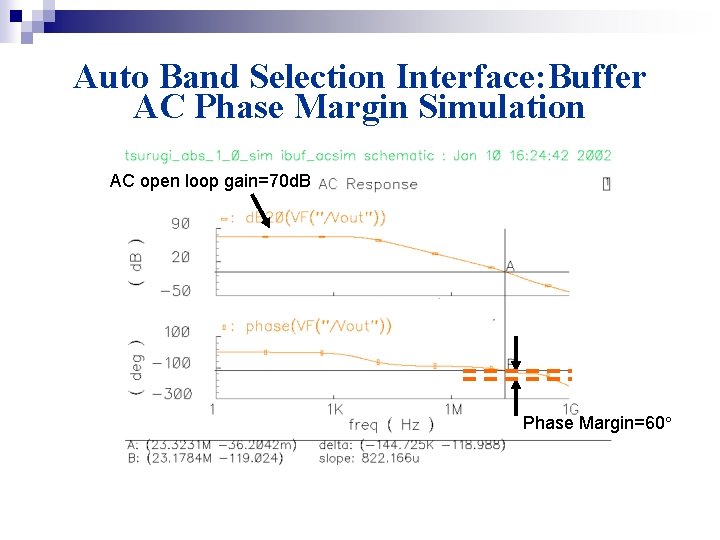

Auto Band Selection Interface: Buffer AC Phase Margin Simulation AC open loop gain=70 d. B Phase Margin=60

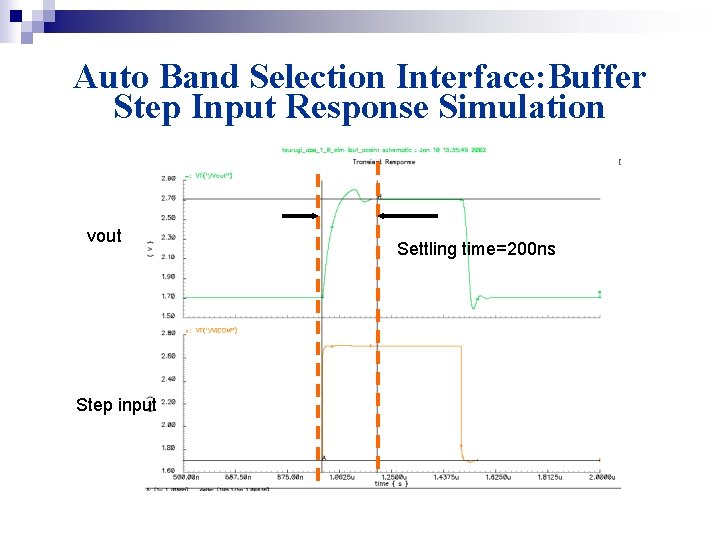

Auto Band Selection Interface: Buffer Step Input Response Simulation vout Step input Settling time=200 ns

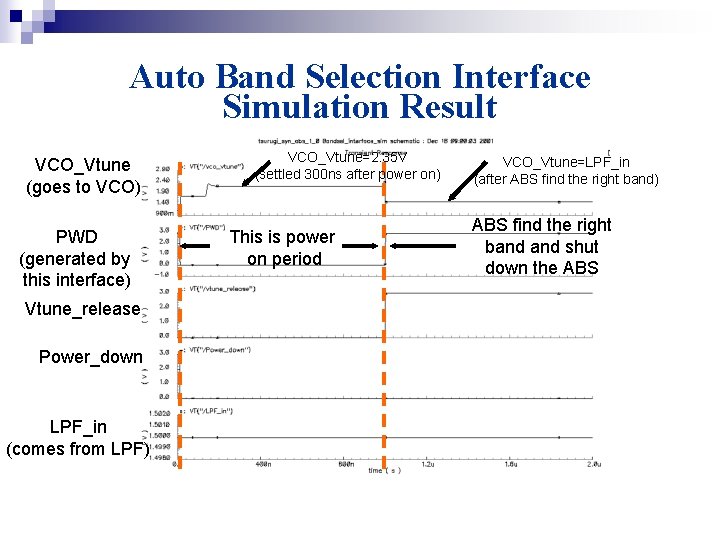

Auto Band Selection Interface Simulation Result VCO_Vtune (goes to VCO) PWD (generated by this interface) Vtune_release Power_down LPF_in (comes from LPF) VCO_Vtune=2. 35 V (settled 300 ns after power on) This is power on period VCO_Vtune=LPF_in (after ABS find the right band) ABS find the right band shut down the ABS

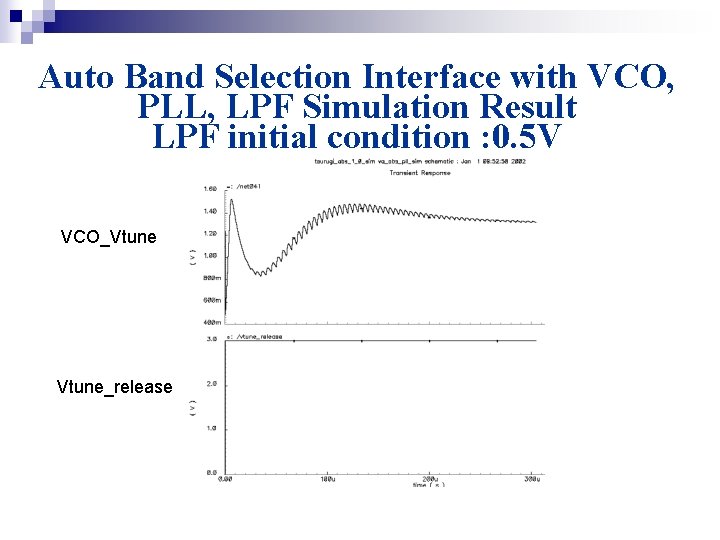

Auto Band Selection Interface with VCO, PLL, LPF Simulation Result LPF initial condition : 0. 5 V VCO_Vtune_release

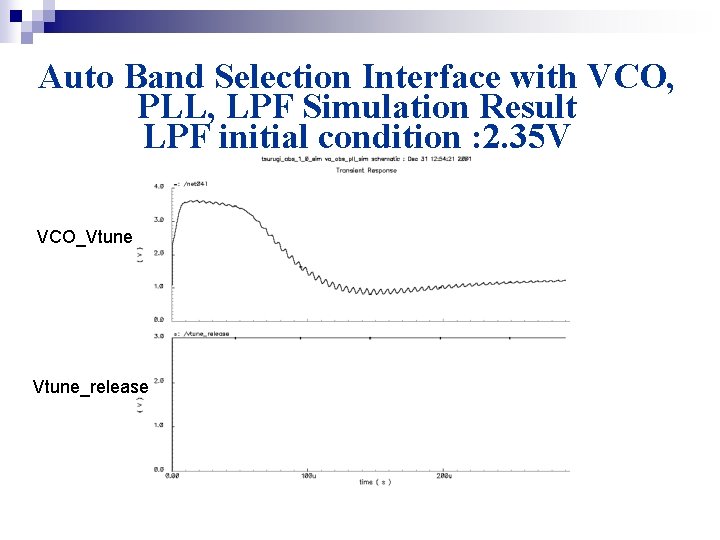

Auto Band Selection Interface with VCO, PLL, LPF Simulation Result LPF initial condition : 2. 35 V VCO_Vtune_release

Auto Band Selection Interface Simulation Summary n n n The Interface circuit provides the VCO vtune voltage based on ABS status, one is a fixed 2. 35 V, the other source is from off-chip LPF output. When ABS select the right band, it generates the power down signal to shut down the current of ABS circuit. Simulation result shows that after interface circuit shut down ABS, PLL and VCO can still handle LPF initial condition.

PART II: Circuit Design Review n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Selection Interface Schematic and Simulation Band Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

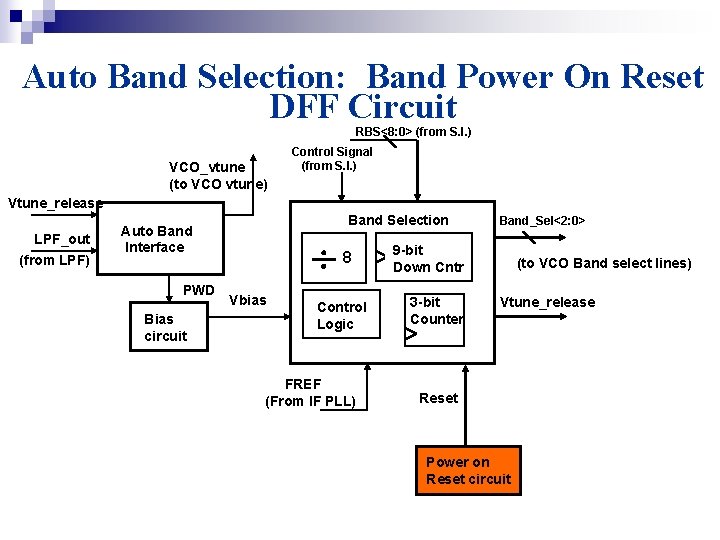

Auto Band Selection: Band Power On Reset DFF Circuit n n Auto Band Selection: Band Power On Reset DFF Circuit Simulation Result

Auto Band Selection: Band Power On Reset DFF Circuit RBS<8: 0> (from S. I. ) VCO_vtune (to VCO vtune) Control Signal (from S. I. ) Vtune_release LPF_out (from LPF) Band Selection Auto Band Interface PWD Bias circuit 8 Vbias Control Logic FREF (From IF PLL) Band_Sel<2: 0> 9 -bit Down Cntr 3 -bit Counter (to VCO Band select lines) Vtune_release Reset Power on Reset circuit

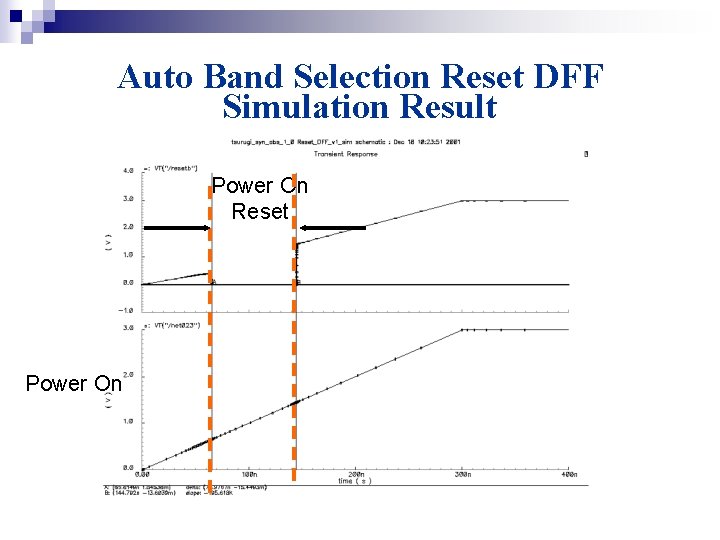

Auto Band Selection Reset DFF Simulation Result Power On Reset Power On

PART II: Circuit Design Review n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Selection Interface Schematic and Simulation Band Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

Auto Band Selection: VCO and Switch Phase Noise Test n n Circuit Simulation Result Auto Band Selection: VCO and Switch (with divide 2) Phase Noise Test Bench Circuit Simulation Result Simulation Summary

Auto Band Selection: VCO and Switch Phase Noise Test n n n Circuit Simulation Result Simulation Summary

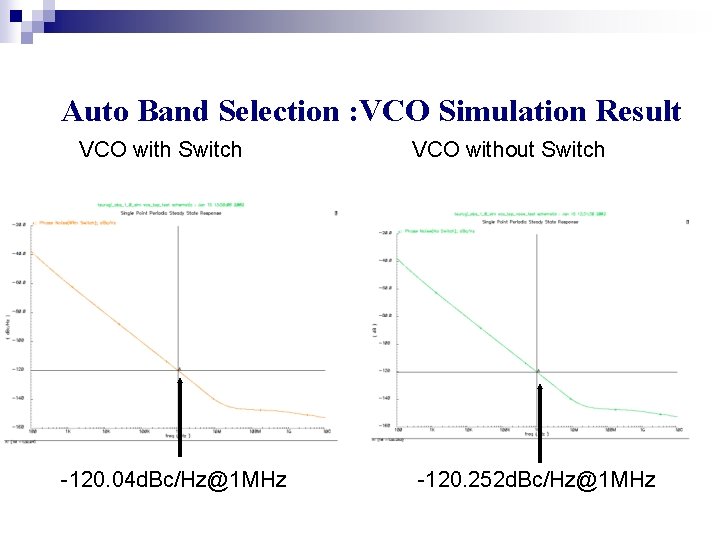

Auto Band Selection : VCO Simulation Result VCO with Switch -120. 04 d. Bc/Hz@1 MHz VCO without Switch -120. 252 d. Bc/Hz@1 MHz

Auto Band Selection VCO and Switch Simulation Summary n n n Auto Band Selection: VCO and Switch Phase Noise Test Bench Simulation result shows no degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) Phase Noise Test Bench Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) PSS Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch

Auto Band Selection VCO and Switch Simulation Summary n n n Auto Band Selection: VCO and Switch Phase Noise Test Bench Simulation result shows no degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) Phase Noise Test Bench Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) PSS Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch

Auto Band Selection VCO and Switch Simulation Summary n n n Auto Band Selection: VCO and Switch Phase Noise Test Bench Simulation result shows no degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) Phase Noise Test Bench Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch. Auto Band Selection: VCO and Switch(with Divide 2) PSS Simulation result shows 0. 15 d. Bc/Hz@1 MHz degradation between VCO with switch and VCO without switch

Auto Band Selection Top Level Simulation RPC<8: 0> RSC<4: 0> TCXO Oscillator RRC<7: 0> CPS<1: 0> Data TWIF_Clk TWIF_EN Serial Interface RPE RCP Iout RF PLL RF Low Pass Filter LPF_out FREF (From IF PLL) SWITCH 2. 35 V vcon_rf vcop_rf RF VCO Vtune_release Band_Sel<2: 0> RVE RF Auto Band Selection RBS<8: 0> BSR RMB Decode_C

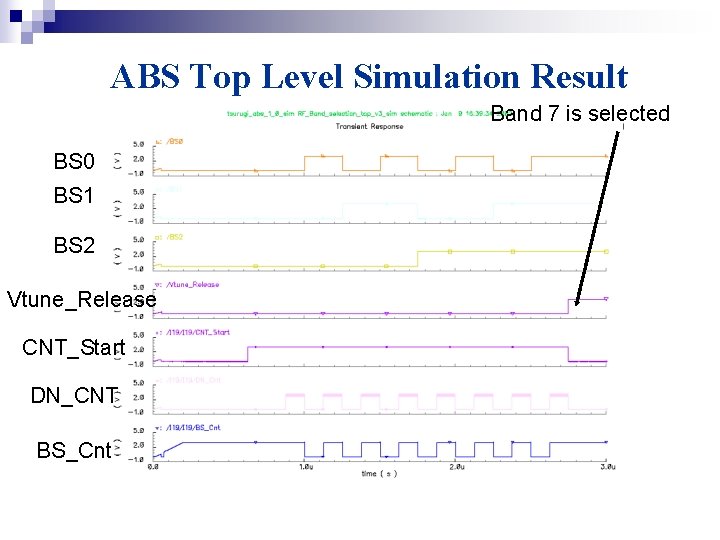

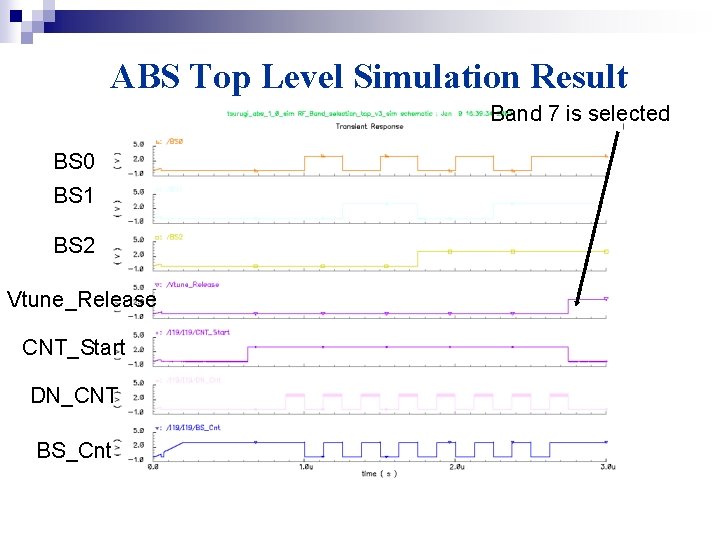

ABS Top Level Simulation Result Band 7 is selected BS 0 BS 1 BS 2 Vtune_Release CNT_Start DN_CNT BS_Cnt

ABS Top Level Simulation Result Band 7 is selected BS 0 BS 1 BS 2 Vtune_Release CNT_Start DN_CNT BS_Cnt

ABS, PLL, LPF, VCO Top Level Simulation n ABS, PLL, LPF, VCO : Top Level Simulation Circuit Simulation Result ABS, PLL, LPF, VCO, S. I Top Level Schematic and List of interconnection

ABS, PLL, LPF, VCO Top Level Simulation n ABS, PLL, LPF, VCO : Top Level Simulation Circuit Simulation Result ABS, PLL, LPF, VCO, S. I Top Level Schematic and List of interconnection

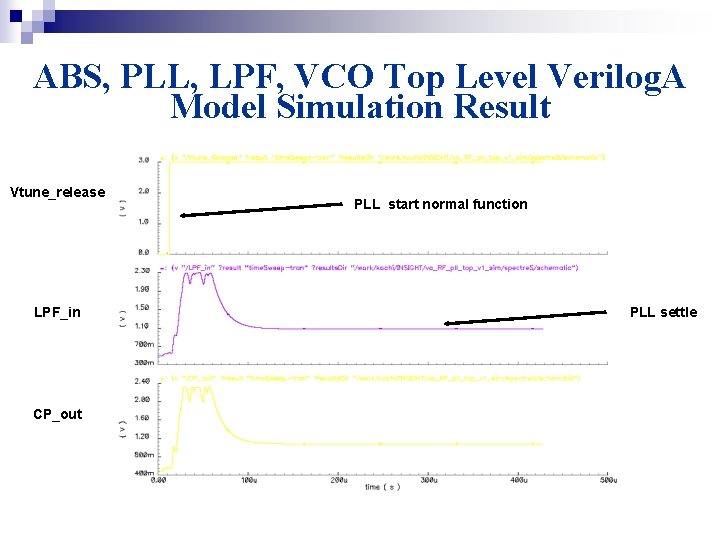

ABS, PLL, LPF, VCO Top Level Verilog. A Model Simulation Result Vtune_release LPF_in CP_out PLL start normal function PLL settle

PART II: Circuit Design Review n n n n n Divide 8, Biasing, and CML to CMOS Circuit Schematic and Simulation 9 Bit Programmable Counter Schematic and Simulation Reference Clock Schematic and Simulation Selection Interface Schematic and Simulation Band Reset DFF Schematic and Simulation VCO Phase Noise Simulation Auto Band Selection Top Level Simulation ABS, PLL, VCO, LPF Top Level Simulation Summary

Auto Band Selection Circuit Simulation Summary n n n Band Selection Circuit start chose band 2 S after EN signal enabled and takes additional up to 16 S to chose the right band for VCO. The total selection time is 18 S(RF), 10 S(IF). The Power Up takes 1 S which is smaller than 2 S. Whenever channel changed, both RF and IF ABS will be enabled to select the right band again. Band Selection Circuit will shut down when the right band is selected. The simulation of Verilog. A model: PLL, VCO, ABS, LPF shows that ABS can work properly with other related blocks. The phase noise of VCO has 0. 15 d. Bc/Hz @ 1 MHz degradation by adding additional switch on the vtune line.

- Slides: 62