Platform ASICs Reliability Bob Madge Miguel Vilchis Vish

Platform ASICs Reliability Bob Madge Miguel Vilchis Vish Bhide LSI Logic , Milpitas, CA

Three Aspects of Reliability Bob Madge u Infant Mortality Failures (Latent Defects and active defects that are not screenable with Testing) u Environmental induced Failures (SER etc. . ) u Intrinsic Failures (Stress migration , electromigration , Wear-out , performance degradation) 2 #141 MAPLD 2005

Methods for Optimizing Reliability Bob Madge u Design For Reliability n Design for Defect Tolerance n Design for SER tolerance n Design for Stress Migration Tolerance n Redundancy u Process Improvements n Defect Density Reduction n Excursion Control u Test Improvements n Resistive Defect Fault Coverage n Un-modeled fault coverage n Statistical Testing 3 #141 MAPLD 2005

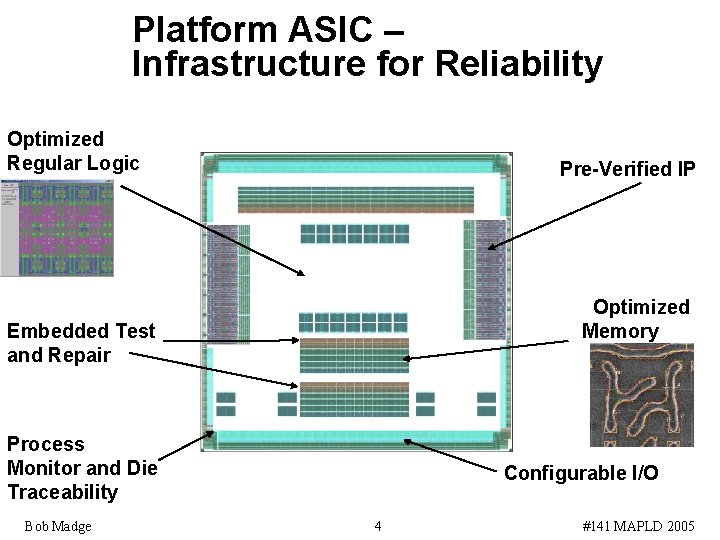

Platform ASIC – Infrastructure for Reliability Optimized Regular Logic Pre-Verified IP Optimized Memory Embedded Test and Repair Process Monitor and Die Traceability Bob Madge Configurable I/O 4 #141 MAPLD 2005

Platform ASIC Design For Reliability u Allowable antenna ratios have a 3 x margin u Additional protection against plasma induced damage u Protection against wearout mechanisms u Stress Migration l Electro Migration l Hot Carrier Injection l Time Dependent Dielectric Breakdown l Vt stability The rules are considered conservative within the industry l u The rules are tested for fabrication capability, yield and reliability during qualification u The libraries and layout tools strictly follow the design rules n u Cells with intentional design rule violations require qualification Tools such as relmil, BERT are available to the designers Bob Madge 5 #141 MAPLD 2005

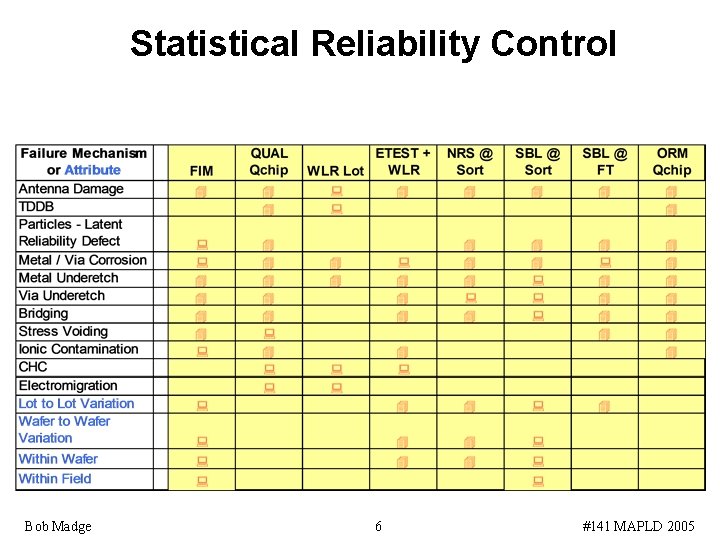

Statistical Reliability Control Bob Madge 6 #141 MAPLD 2005

Continuous feedback and improvement u During Development: n n u Library elements are redesigned during the development cycle if design rules change Process/Tool changes are made if the libraries cannot change During production: n n n The customer issues are continuously fed back Process changes are made if applicable Cell changes are made if necessary l l Bob Madge Current customers are protected by the MRB/TRB systems Redesigns incorporate the changes if necessary Future customers only receive the revised version Identification of issues by one customer benefits all others 7 #141 MAPLD 2005

Single Event Effects Mitigation u LSI Logic platform ASICs using 0. 18 um CMOS commercial process are designed using best practices for SEE mitigation n optimization of n-well spacing and profile n buried layer for latchup mitigation u The mitigation strategies lead to SEL immunity to atmospheric neutron fluence of 5 E 10 n/cm 2 and SEU cross section of 4 E-14 cm 2/bit. This performance is superior to a typical commercial grade product. u On chip error correction codes (ECC) for memory devices are available n Bob Madge word interleaving for multi bit error mitigation 8 #141 MAPLD 2005

Radiation Performance u Unlike commercial grade products, Platform ASICs using a 0. 18 um CMOS modified process have been characterized for Total Ionizing Dose (TID), n functional up to the maximum dose level of 300 krad-Si n no noticeable degradation up to a total dose of 90 krad-Si. u Unlike commercial grade products, Platform ASICs using a 0. 18 um CMOS modified process have been characterized for heavy ion Single Event Effects (SEE) n At LET of 75 Me. V cm 2/mg logic and SRAM blocks are immune to single event latchup (SEL) 2 l Single Event Upset saturation cross sections are 1 E-06 cm /bit and 7 E-07 cm 2/flip-flop l u Additionally, Platform ASICs using a 0. 115 um CMOS modified process have been characterized for heavy ion Single Event Effects (SEE) n At LET of 108 Me. V cm 2/mg l l Bob Madge logic and SRAM blocks are immune to single event latchup (SEL) Single Event Upset cross sections data is under evaluation 9 #141 MAPLD 2005

Efficient Netlist Implementation u Early and Intrinsic Failure rates and Soft Error Rates are proportional to the number of used gates and SRAM u The platform ASICs implement the RTL with minimum overhead of logic gates and require no configuration SRAM u Efficient Implementation through mask configuration leads to lower product failure rate than a product that requires more gates to implement the same functionality Bob Madge 10 #141 MAPLD 2005

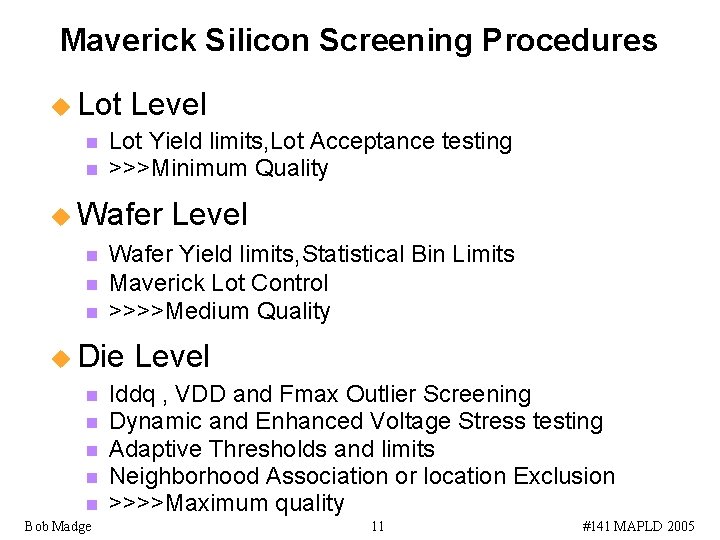

Maverick Silicon Screening Procedures u Lot n n Level Lot Yield limits, Lot Acceptance testing >>>Minimum Quality u Wafer n n n Wafer Yield limits, Statistical Bin Limits Maverick Lot Control >>>>Medium Quality u Die n n n Bob Madge Level Iddq , VDD and Fmax Outlier Screening Dynamic and Enhanced Voltage Stress testing Adaptive Thresholds and limits Neighborhood Association or location Exclusion >>>>Maximum quality 11 #141 MAPLD 2005

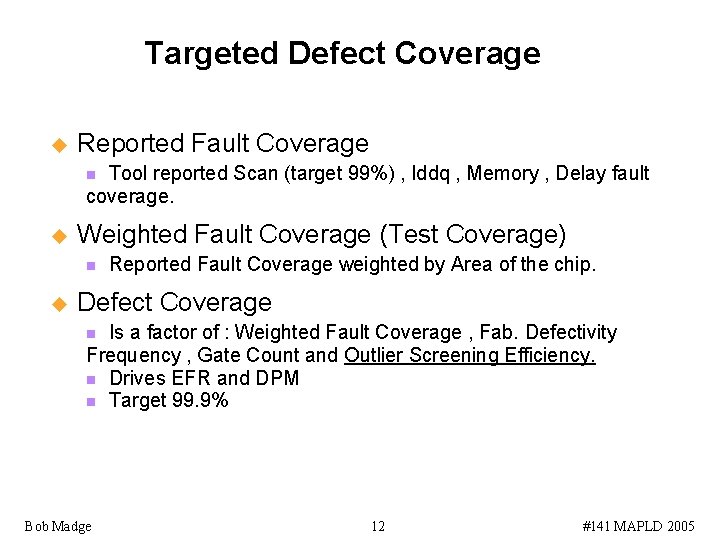

Targeted Defect Coverage u Reported Fault Coverage Tool reported Scan (target 99%) , Iddq , Memory , Delay fault coverage. n u Weighted Fault Coverage (Test Coverage) n u Reported Fault Coverage weighted by Area of the chip. Defect Coverage Is a factor of : Weighted Fault Coverage , Fab. Defectivity Frequency , Gate Count and Outlier Screening Efficiency. n Drives EFR and DPM n Target 99. 9% n Bob Madge 12 #141 MAPLD 2005

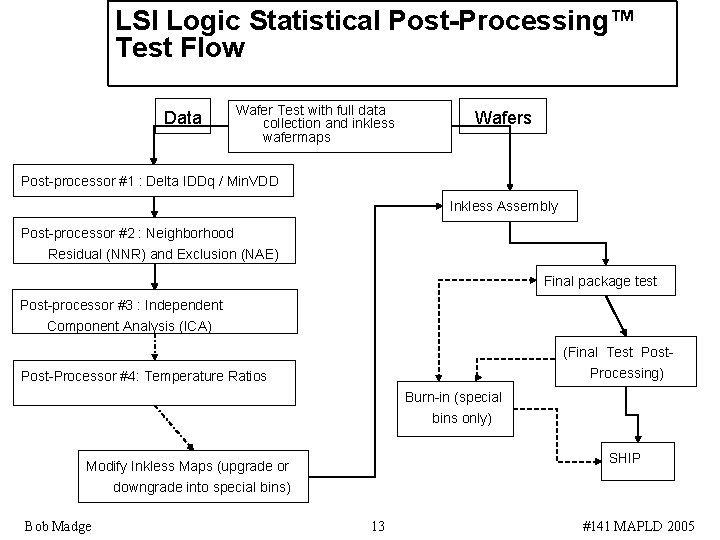

LSI Logic Statistical Post-Processing™ Test Flow Data Wafer Test with full data collection and inkless wafermaps Wafers Post-processor #1 : Delta IDDq / Min. VDD Inkless Assembly Post-processor #2 : Neighborhood Residual (NNR) and Exclusion (NAE) Final package test Post-processor #3 : Independent Component Analysis (ICA) (Final Test Post. Processing) Post-Processor #4: Temperature Ratios Burn-in (special bins only) SHIP Modify Inkless Maps (upgrade or downgrade into special bins) Bob Madge 13 #141 MAPLD 2005

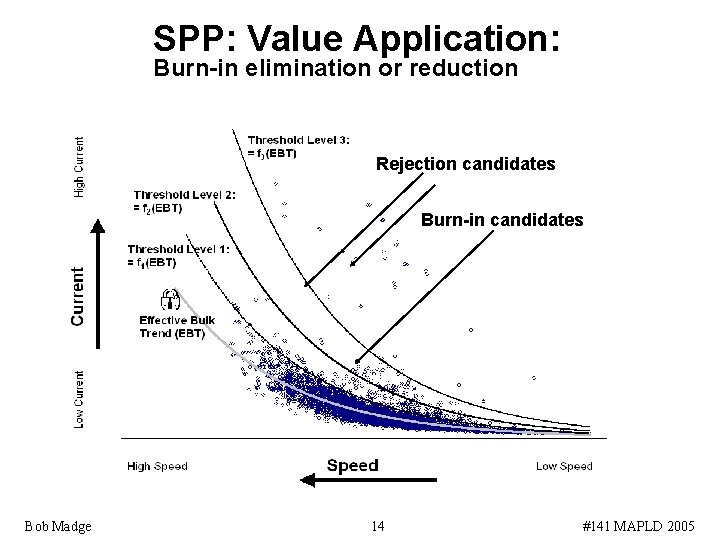

SPP: Value Application: Burn-in elimination or reduction Rejection candidates Burn-in candidates Bob Madge 14 #141 MAPLD 2005

Signal Overlap in Current Vs Speed Current Count Bob Madge Speed 15 #141 MAPLD 2005

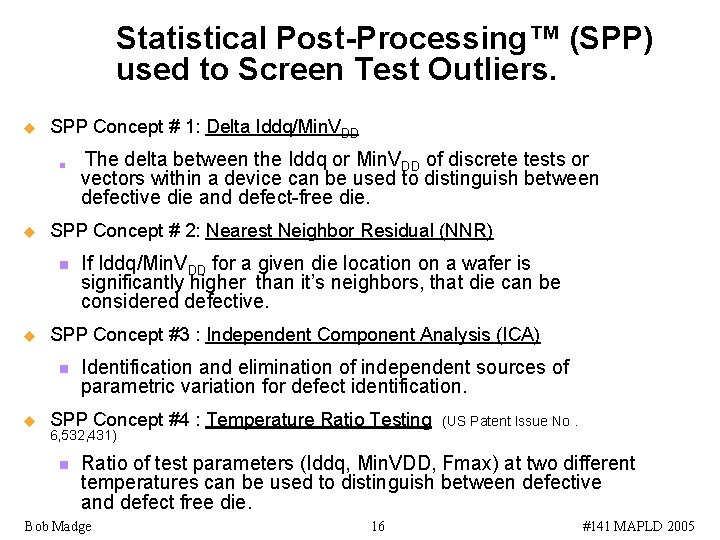

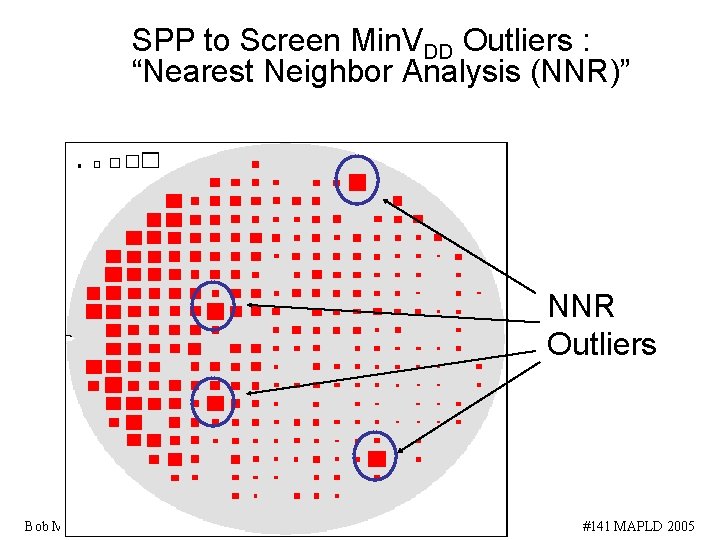

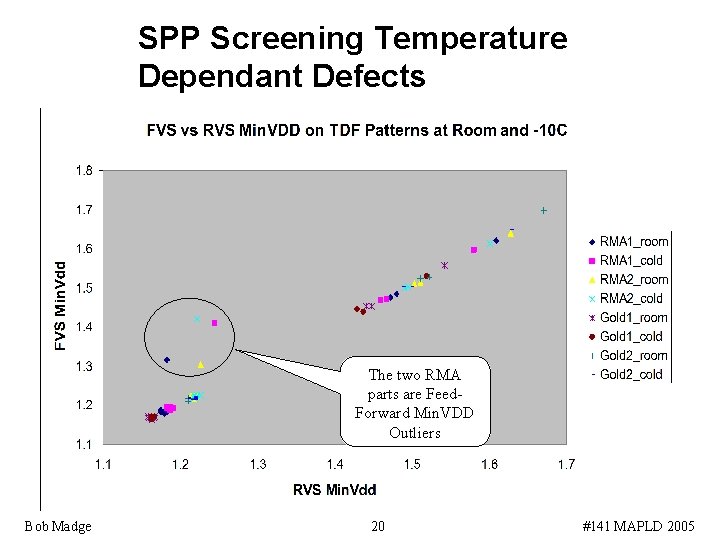

Statistical Post-Processing™ (SPP) used to Screen Test Outliers. u SPP Concept # 1: Delta Iddq/Min. VDD n u SPP Concept # 2: Nearest Neighbor Residual (NNR) n u If Iddq/Min. VDD for a given die location on a wafer is significantly higher than it’s neighbors, that die can be considered defective. SPP Concept #3 : Independent Component Analysis (ICA) n u The delta between the Iddq or Min. VDD of discrete tests or vectors within a device can be used to distinguish between defective die and defect-free die. Identification and elimination of independent sources of parametric variation for defect identification. SPP Concept #4 : Temperature Ratio Testing 6, 532, 431) n (US Patent Issue No. Ratio of test parameters (Iddq, Min. VDD, Fmax) at two different temperatures can be used to distinguish between defective and defect free die. Bob Madge 16 #141 MAPLD 2005

SPP to Screen Min. VDD Outliers : “Nearest Neighbor Analysis (NNR)” NNR Outliers Bob Madge 17 #141 MAPLD 2005

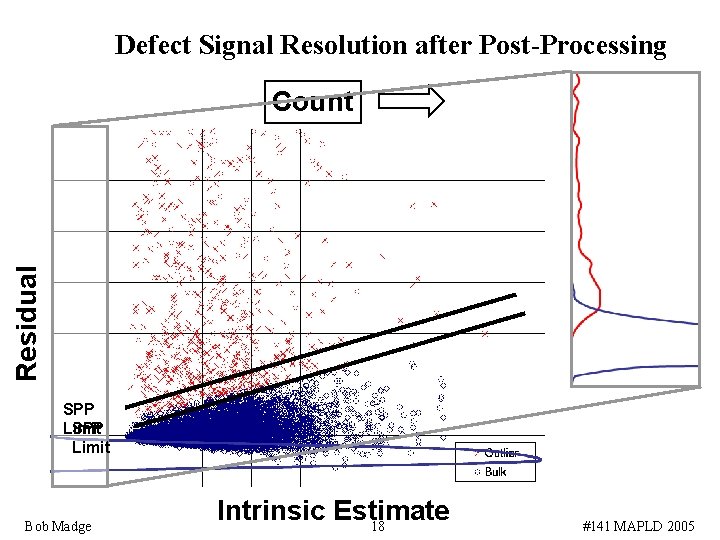

Defect Signal Resolution after Post-Processing Residual Count SPP Limit Bob Madge Intrinsic Estimate 18 #141 MAPLD 2005

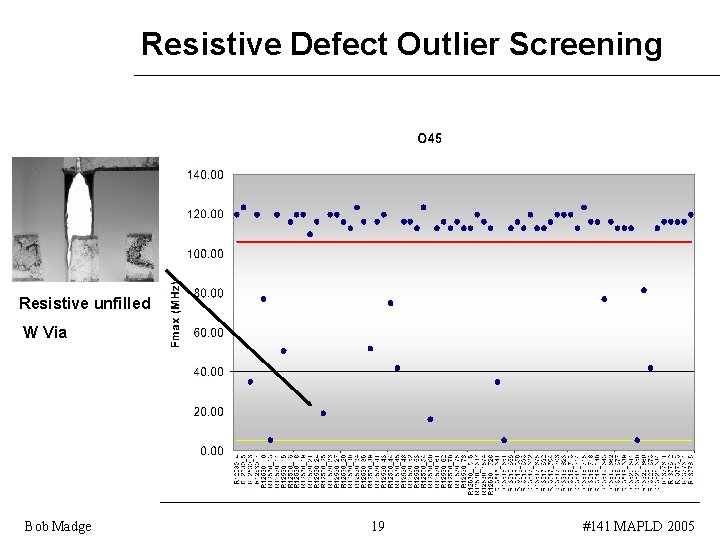

Resistive Defect Outlier Screening Resistive unfilled W Via Bob Madge 19 #141 MAPLD 2005

SPP Screening Temperature Dependant Defects The two RMA parts are Feed. Forward Min. VDD Outliers Bob Madge 20 #141 MAPLD 2005

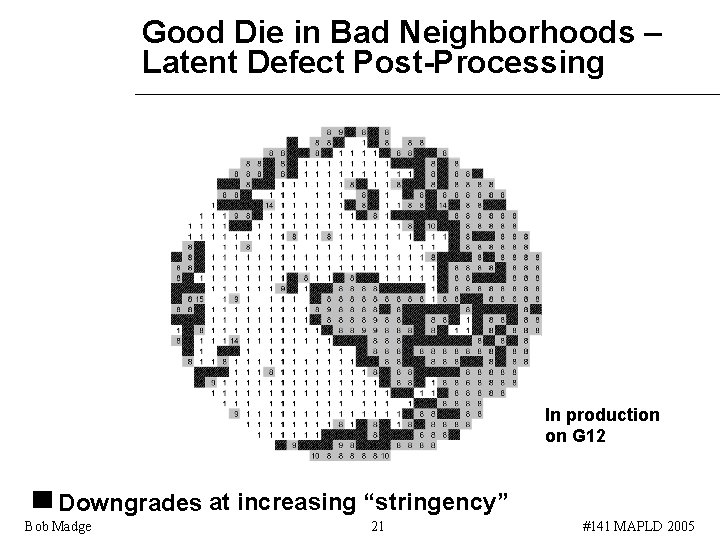

Good Die in Bad Neighborhoods – Latent Defect Post-Processing In production on G 12 Downgrades at increasing “stringency” Bob Madge 21 #141 MAPLD 2005

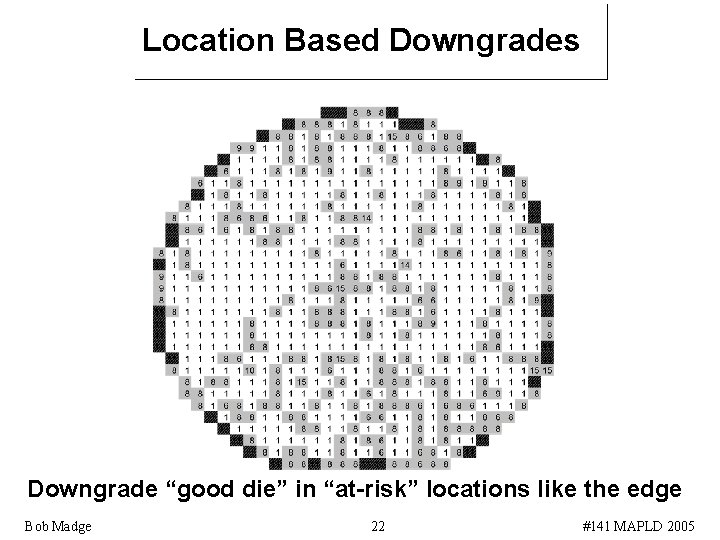

Location Based Downgrades Downgrade “good die” in “at-risk” locations like the edge Bob Madge 22 #141 MAPLD 2005

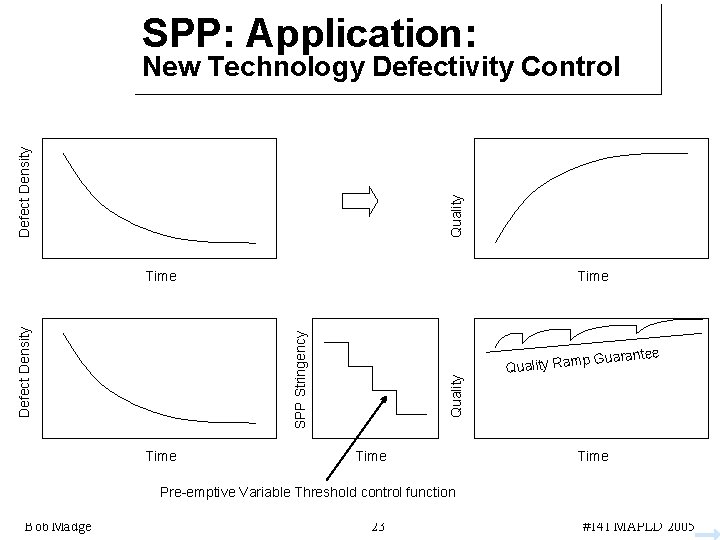

SPP: Application: Quality Defect Density New Technology Defectivity Control Time Quality SPP Stringency Defect Density Time p Quality Ram Guarantee Time Pre-emptive Variable Threshold control function Bob Madge 23 #141 MAPLD 2005

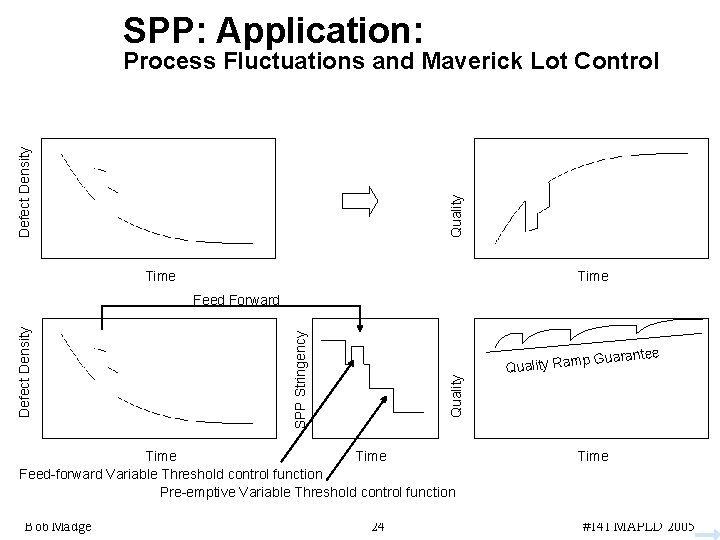

SPP: Application: Quality Defect Density Process Fluctuations and Maverick Lot Control Time Quality SPP Stringency Defect Density Feed Forward Time Feed-forward Variable Threshold control function Pre-emptive Variable Threshold control function Bob Madge 24 p Quality Ram Guarantee Time #141 MAPLD 2005

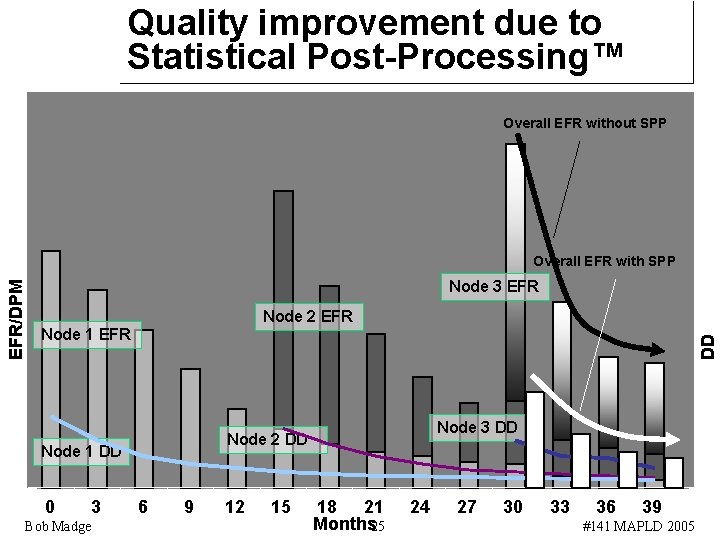

Quality improvement due to Statistical Post-Processing™ Overall EFR without SPP Node 3 EFR Node 2 EFR Node 1 EFR DD EFR/DPM Overall EFR with SPP Node 1 DD 0 Bob Madge 3 Node 3 DD Node 2 DD 6 9 12 15 18 21 Months 25 24 27 30 33 36 39 #141 MAPLD 2005

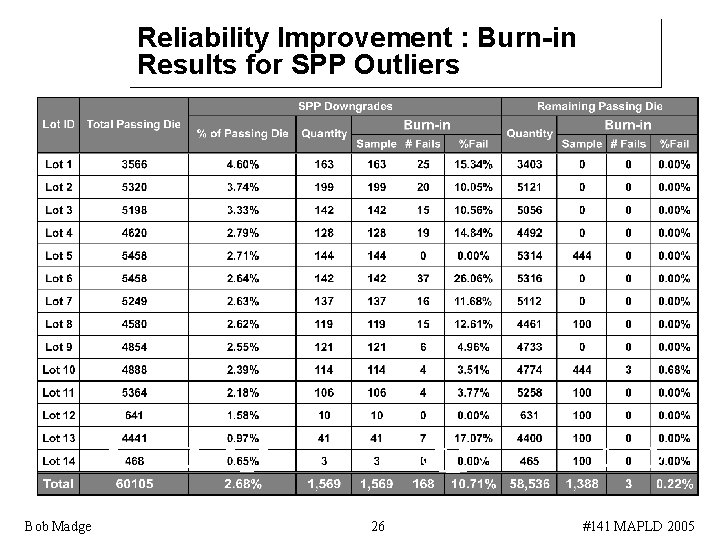

Reliability Improvement : Burn-in Results for SPP Outliers Bob Madge 26 #141 MAPLD 2005

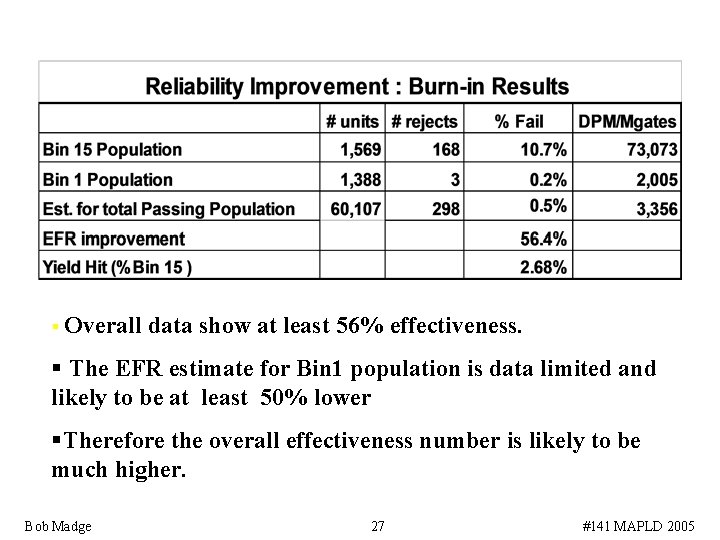

§ Overall data show at least 56% effectiveness. § The EFR estimate for Bin 1 population is data limited and likely to be at least 50% lower §Therefore the overall effectiveness number is likely to be much higher. Bob Madge 27 #141 MAPLD 2005

- Slides: 27