PIXSIC dtecteur silicium pixelis pour application intracrbrale JeanClaude

PIXSIC : détecteur silicium pixelisé pour application intracérébrale Jean-Claude Clémens, Denis Fougeron, Michel Jevaud, Julia Maerk, Mohsine Menouni CPPM-CNRS-Université de la Méditerranée-Marseille 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3

contexte q Projet ANR (Financement : ANR-09 -BLAN-0102 -02) q Il repose sur la collaboration de 5 laboratoires : § 1: CPPM (Centre de Physique de Particules de Marseille) § 2: IMNC (Imagerie et Modélisation en Neurobiologie et Cancérologie) § 3: CERN § 4: CERMEP (Centre d’Etude et de Recherche Multimodal et Pluridisciplinaire en Imagerie du vivant) § 5: CNPS (Centre de Neuroscience de Paris-Sud L. Balasse 2, D. Benoit 2, M. Benoit 3, J. C. Clemens 1, S. Fieux 4, D. Fougeron 1, A. Genoux 2, P. Gisquet-Verrier 5, J. Graber-Bolis 1, B. Janvier 2, M. Jevaud 1, P. Laniece 2, J. Maerk 1, M. Menouni 1, C. Morel 1, F. Pain 2, C. Tourvielle 4, L. Zimmer 4 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 2/10

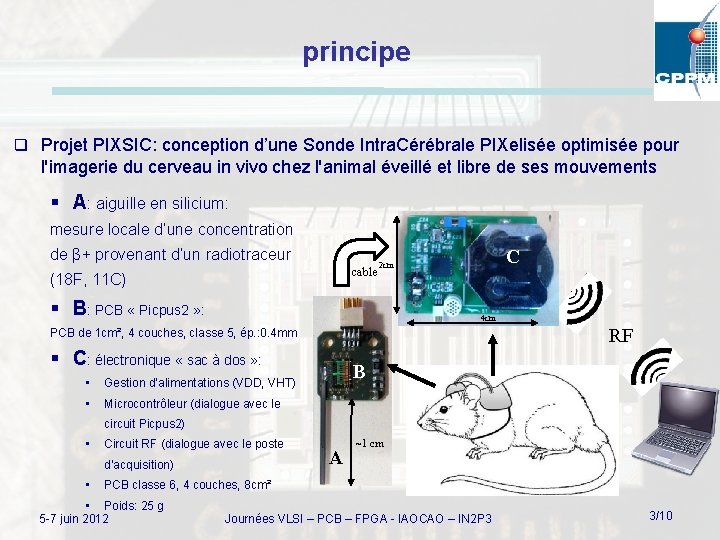

principe q Projet PIXSIC: conception d’une Sonde Intra. Cérébrale PIXelisée optimisée pour l'imagerie du cerveau in vivo chez l'animal éveillé et libre de ses mouvements § A: aiguille en silicium: mesure locale d’une concentration de β+ provenant d’un radiotraceur cable (18 F, 11 C) C 2 cm § B: PCB « Picpus 2 » : 4 cm RF PCB de 1 cm², 4 couches, classe 5, ép. : 0. 4 mm § C: électronique « sac à dos » : • Gestion d’alimentations (VDD, VHT) • Microcontrôleur (dialogue avec le B circuit Picpus 2) • Circuit RF (dialogue avec le poste d’acquisition) • A ~1 cm PCB classe 6, 4 couches, 8 cm² • Poids: 25 g 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 3/10

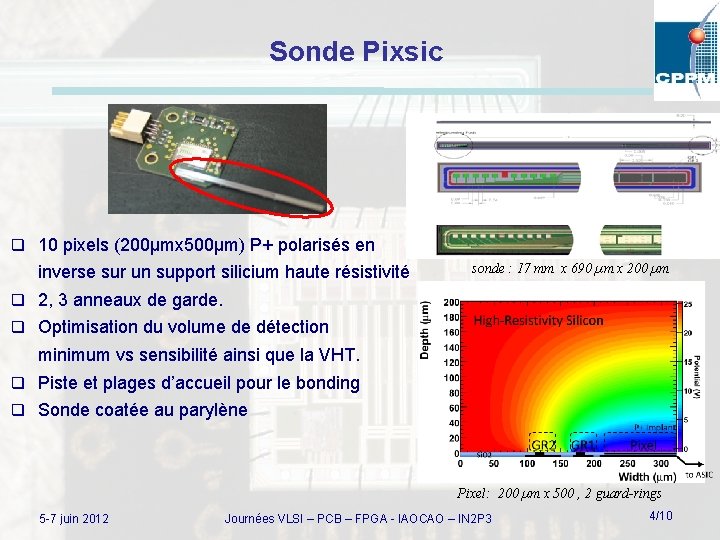

Sonde Pixsic q 10 pixels (200µmx 500µm) P+ polarisés en inverse sur un support silicium haute résistivité sonde : 17 mm x 690 µm x 200 µm q 2, 3 anneaux de garde. q Optimisation du volume de détection minimum vs sensibilité ainsi que la VHT. q Piste et plages d’accueil pour le bonding q Sonde coatée au parylène Pixel: 200 µm x 500 , 2 guard-rings 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 4/10

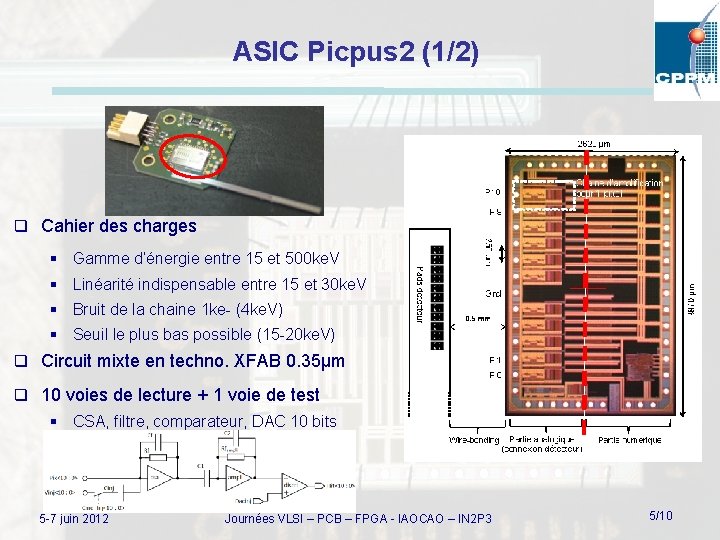

ASIC Picpus 2 (1/2) q Cahier des charges § Gamme d’énergie entre 15 et 500 ke. V § Linéarité indispensable entre 15 et 30 ke. V § Bruit de la chaine 1 ke- (4 ke. V) § Seuil le plus bas possible (15 -20 ke. V) q Circuit mixte en techno. XFAB 0. 35µm q 10 voies de lecture + 1 voie de test § CSA, filtre, comparateur, DAC 10 bits 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 5/10

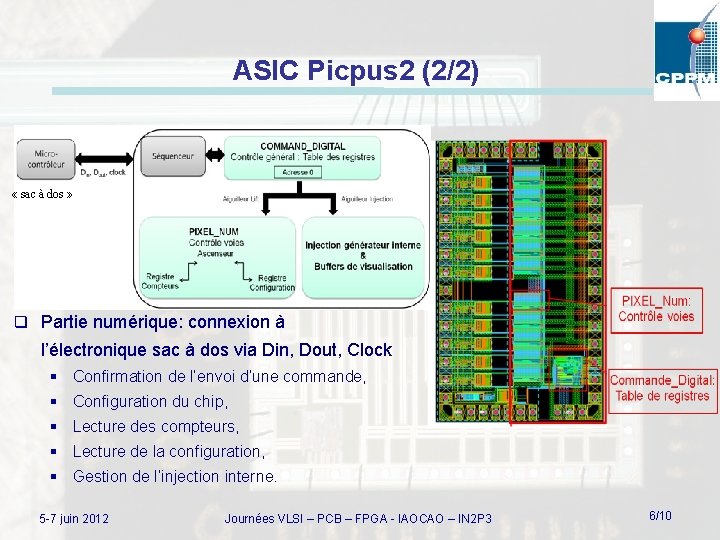

ASIC Picpus 2 (2/2) « sac à dos » q Partie numérique: connexion à l’électronique sac à dos via Din, Dout, Clock § Confirmation de l’envoi d’une commande, § Configuration du chip, § Lecture des compteurs, § Lecture de la configuration, § Gestion de l’injection interne. 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 6/10

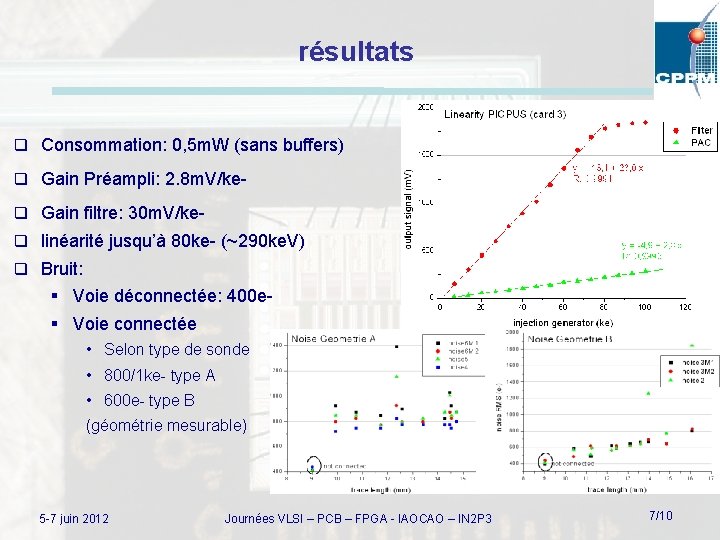

résultats q Consommation: 0, 5 m. W (sans buffers) q Gain Préampli: 2. 8 m. V/keq Gain filtre: 30 m. V/keq linéarité jusqu’à 80 ke- (~290 ke. V) q Bruit: § Voie déconnectée: 400 e§ Voie connectée • Selon type de sonde • 800/1 ke- type A • 600 e- type B (géométrie mesurable) 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 7/10

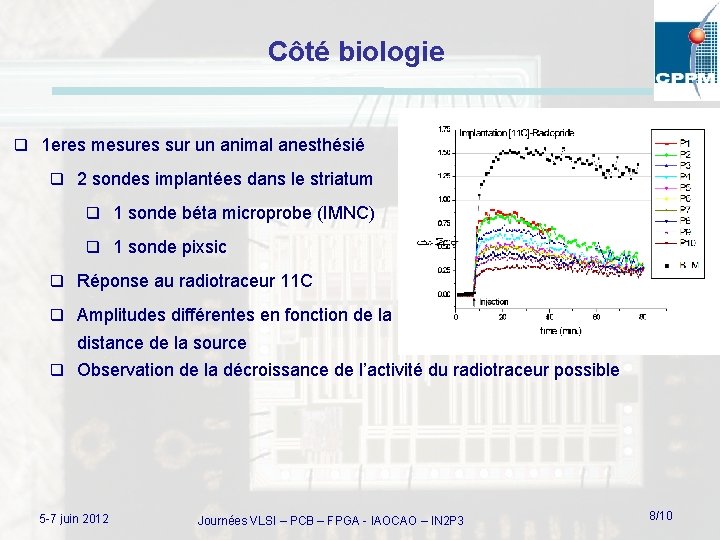

Côté biologie q 1 eres mesures sur un animal anesthésié q 2 sondes implantées dans le striatum q 1 sonde béta microprobe (IMNC) q 1 sonde pixsic q Réponse au radiotraceur 11 C q Amplitudes différentes en fonction de la distance de la source q Observation de la décroissance de l’activité du radiotraceur possible 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 8/10

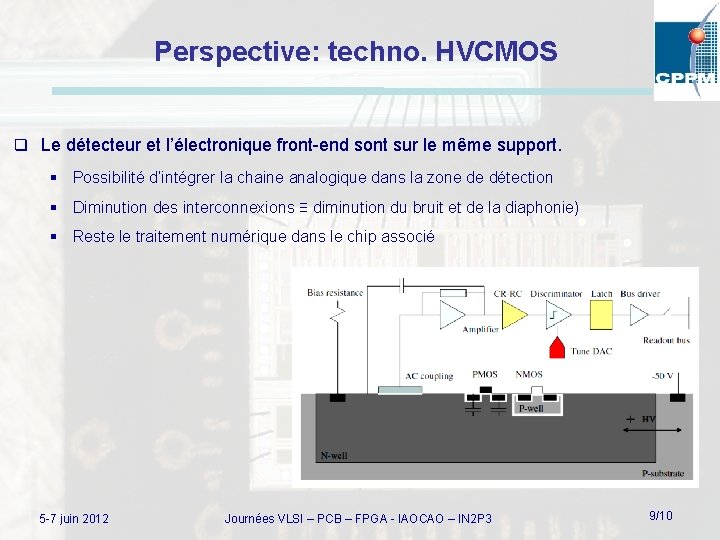

Perspective: techno. HVCMOS q Le détecteur et l’électronique front-end sont sur le même support. § Possibilité d’intégrer la chaine analogique dans la zone de détection § Diminution des interconnexions ≡ diminution du bruit et de la diaphonie) § Reste le traitement numérique dans le chip associé 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 9/10

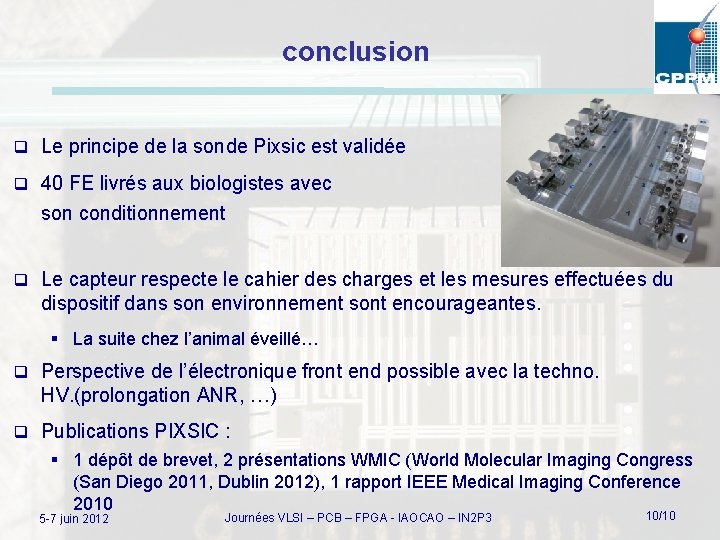

conclusion q Le principe de la sonde Pixsic est validée q 40 FE livrés aux biologistes avec son conditionnement q Le capteur respecte le cahier des charges et les mesures effectuées du dispositif dans son environnement sont encourageantes. § La suite chez l’animal éveillé… q Perspective de l’électronique front end possible avec la techno. HV. (prolongation ANR, …) q Publications PIXSIC : § 1 dépôt de brevet, 2 présentations WMIC (World Molecular Imaging Congress (San Diego 2011, Dublin 2012), 1 rapport IEEE Medical Imaging Conference 2010 5 -7 juin 2012 Journées VLSI – PCB – FPGA - IAOCAO – IN 2 P 3 10/10

- Slides: 10