Pixel System Architecture Giovanni Darbo INFN Genova Email

Pixel System Architecture Giovanni Darbo / INFN - Genova E-mail: Giovanni. Darbo@ge. infn. it Talk highlights: MCC history. System Arcitecture. MCC implementations. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002

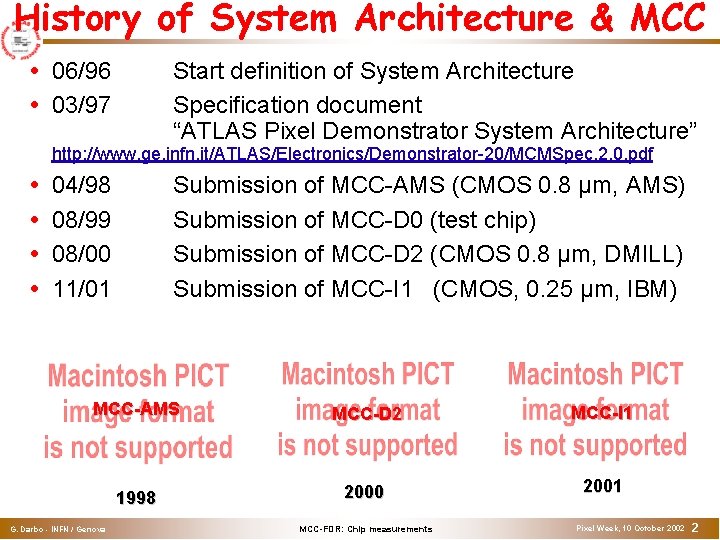

History of System Architecture & MCC 06/96 03/97 Start definition of System Architecture Specification document “ATLAS Pixel Demonstrator System Architecture” http: //www. ge. infn. it/ATLAS/Electronics/Demonstrator-20/MCMSpec. 2. 0. pdf 04/98 08/99 08/00 11/01 Submission of MCC-AMS (CMOS 0. 8 µm, AMS) Submission of MCC-D 0 (test chip) Submission of MCC-D 2 (CMOS 0. 8 µm, DMILL) Submission of MCC-I 1 (CMOS, 0. 25 µm, IBM) MCC-AMS MCC-D 2 MCC-I 1 1998 2000 2001 G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 2

Rad Soft Demonstrator Module G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 3

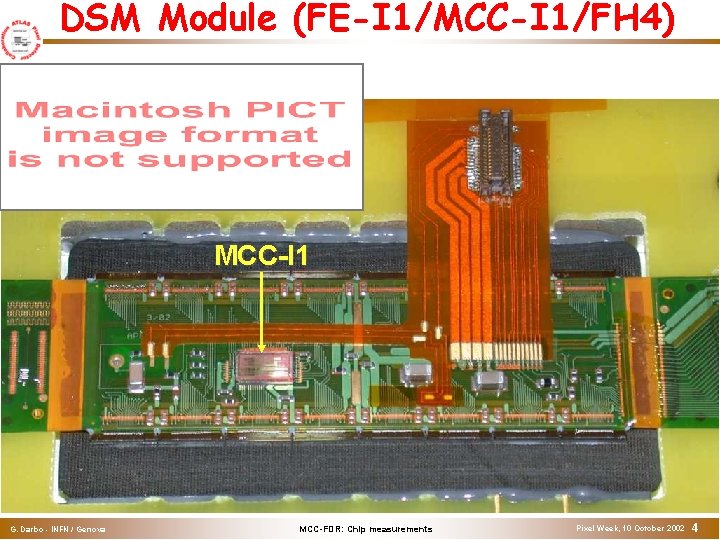

DSM Module (FE-I 1/MCC-I 1/FH 4) MCC-I 1 G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 4

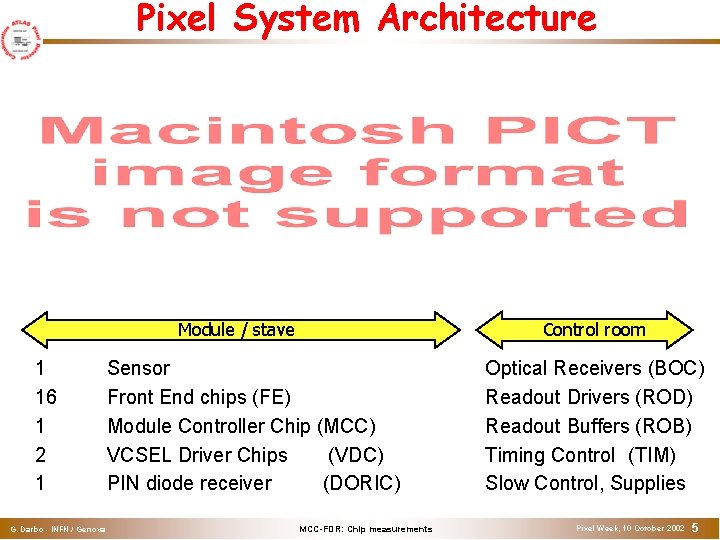

Pixel System Architecture Module / stave 1 16 1 2 1 G. Darbo - INFN / Genova Control room Sensor Front End chips (FE) Module Controller Chip (MCC) VCSEL Driver Chips (VDC) PIN diode receiver (DORIC) MCC-FDR: Chip measurements Optical Receivers (BOC) Readout Drivers (ROD) Readout Buffers (ROB) Timing Control (TIM) Slow Control, Supplies Pixel Week, 10 October 2002 5

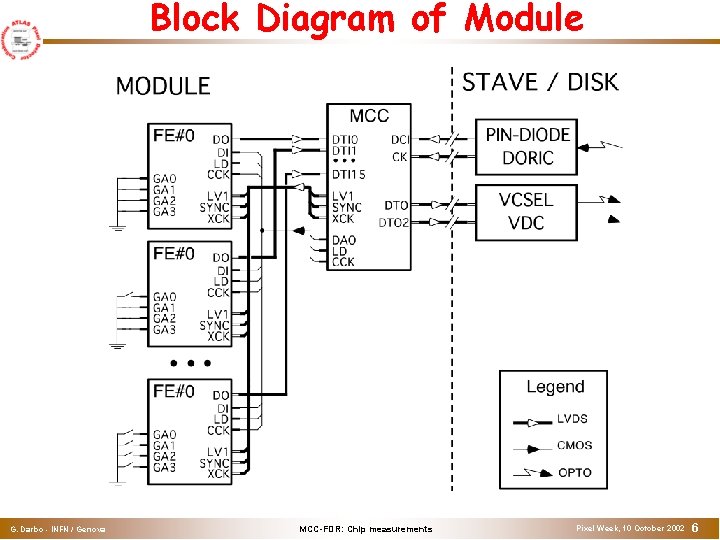

Block Diagram of Module G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 6

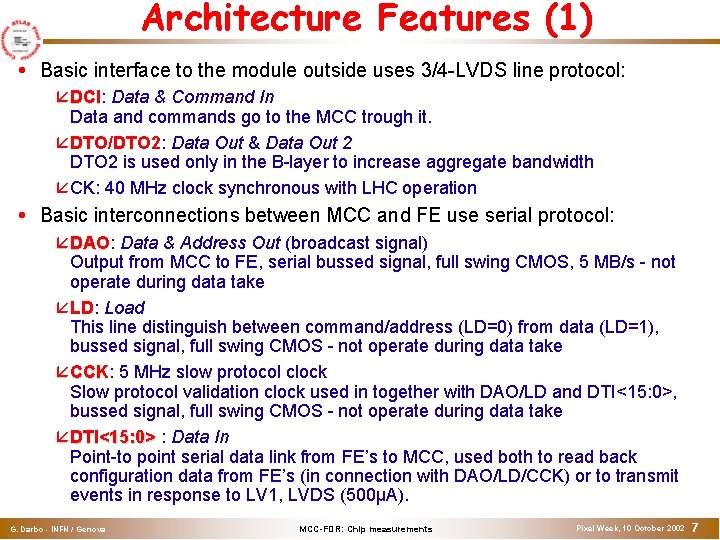

Architecture Features (1) Basic interface to the module outside uses 3/4 -LVDS line protocol: DCI: DCI Data & Command In Data and commands go to the MCC trough it. DTO/DTO 2: DTO/DTO 2 Data Out & Data Out 2 DTO 2 is used only in the B-layer to increase aggregate bandwidth CK: 40 MHz clock synchronous with LHC operation Basic interconnections between MCC and FE use serial protocol: DAO: DAO Data & Address Out (broadcast signal) Output from MCC to FE, serial bussed signal, full swing CMOS, 5 MB/s - not operate during data take LD: LD Load This line distinguish between command/address (LD=0) from data (LD=1), bussed signal, full swing CMOS - not operate during data take CCK: CCK 5 MHz slow protocol clock Slow protocol validation clock used in together with DAO/LD and DTI<15: 0>, bussed signal, full swing CMOS - not operate during data take DTI<15: 0> : Data In Point-to point serial data link from FE’s to MCC, used both to read back configuration data from FE’s (in connection with DAO/LD/CCK) or to transmit events in response to LV 1, LVDS (500µA). G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 7

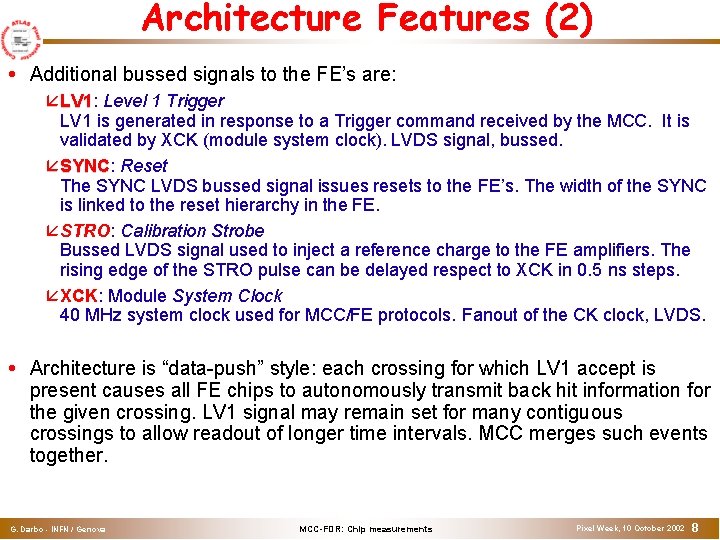

Architecture Features (2) Additional bussed signals to the FE’s are: LV 1: LV 1 Level 1 Trigger LV 1 is generated in response to a Trigger command received by the MCC. It is validated by XCK (module system clock). LVDS signal, bussed. SYNC: SYNC Reset The SYNC LVDS bussed signal issues resets to the FE’s. The width of the SYNC is linked to the reset hierarchy in the FE. STRO: Calibration Strobe Bussed LVDS signal used to inject a reference charge to the FE amplifiers. The rising edge of the STRO pulse can be delayed respect to XCK in 0. 5 ns steps. XCK: XCK Module System Clock 40 MHz system clock used for MCC/FE protocols. Fanout of the CK clock, LVDS. Architecture is “data-push” style: each crossing for which LV 1 accept is present causes all FE chips to autonomously transmit back hit information for the given crossing. LV 1 signal may remain set for many contiguous crossings to allow readout of longer time intervals. MCC merges such events together. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 8

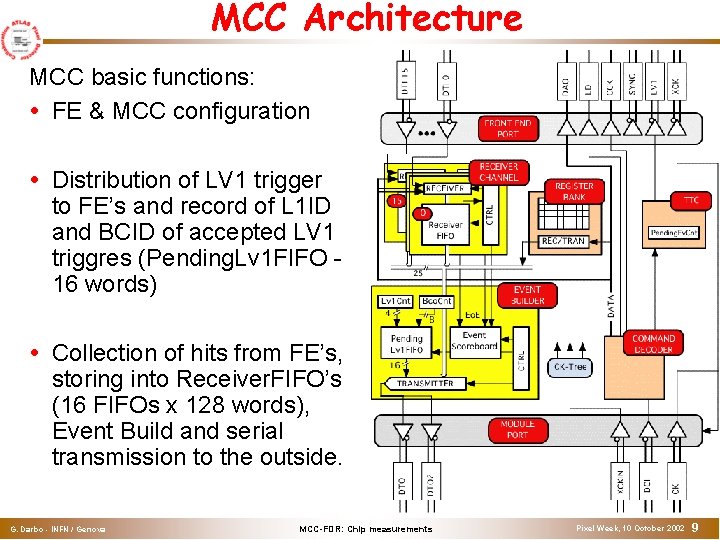

MCC Architecture MCC basic functions: FE & MCC configuration Distribution of LV 1 trigger to FE’s and record of L 1 ID and BCID of accepted LV 1 triggres (Pending. Lv 1 FIFO 16 words) Collection of hits from FE’s, storing into Receiver. FIFO’s (16 FIFOs x 128 words), Event Build and serial transmission to the outside. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 9

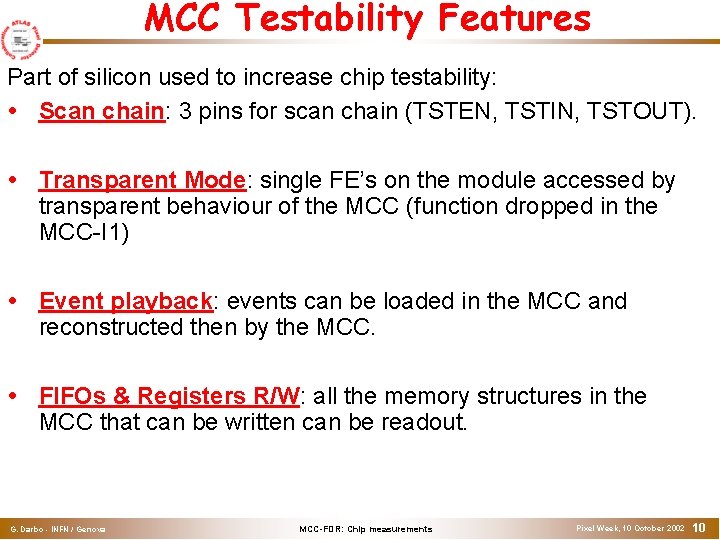

MCC Testability Features Part of silicon used to increase chip testability: Scan chain: 3 pins for scan chain (TSTEN, TSTIN, TSTOUT). Transparent Mode: single FE’s on the module accessed by transparent behaviour of the MCC (function dropped in the MCC-I 1) Event playback: events can be loaded in the MCC and reconstructed then by the MCC. FIFOs & Registers R/W: all the memory structures in the MCC that can be written can be readout. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 10

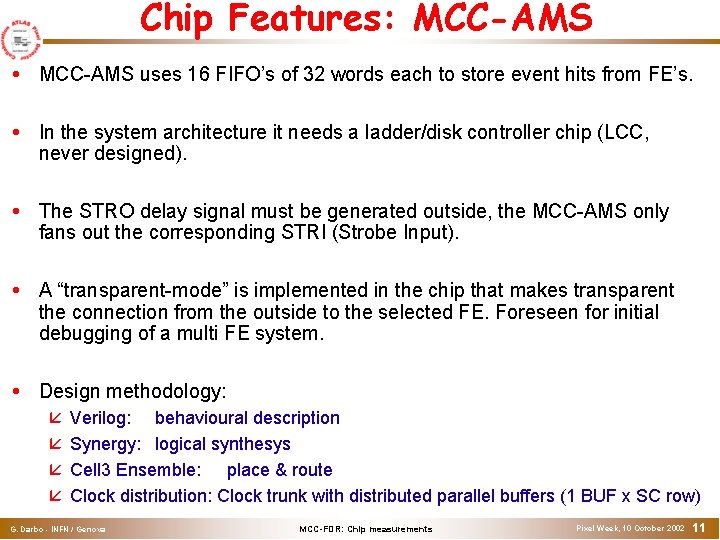

Chip Features: MCC-AMS uses 16 FIFO’s of 32 words each to store event hits from FE’s. In the system architecture it needs a ladder/disk controller chip (LCC, never designed). The STRO delay signal must be generated outside, the MCC-AMS only fans out the corresponding STRI (Strobe Input). A “transparent-mode” is implemented in the chip that makes transparent the connection from the outside to the selected FE. Foreseen for initial debugging of a multi FE system. Design methodology: Verilog: behavioural description Synergy: logical synthesys Cell 3 Ensemble: place & route Clock distribution: Clock trunk with distributed parallel buffers (1 BUF x SC row) G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 11

MCC-AMS layout No. of SC: No. of Trans. : No. of Pins: Chip Size: G. Darbo - INFN / Genova 17, 922 layout = 416, 464 schematics = 363, 016 83 10. 6 x 6. 3 = 66. 8 mm 2 MCC-FDR: Chip measurements Pixel Week, 10 October 2002 12

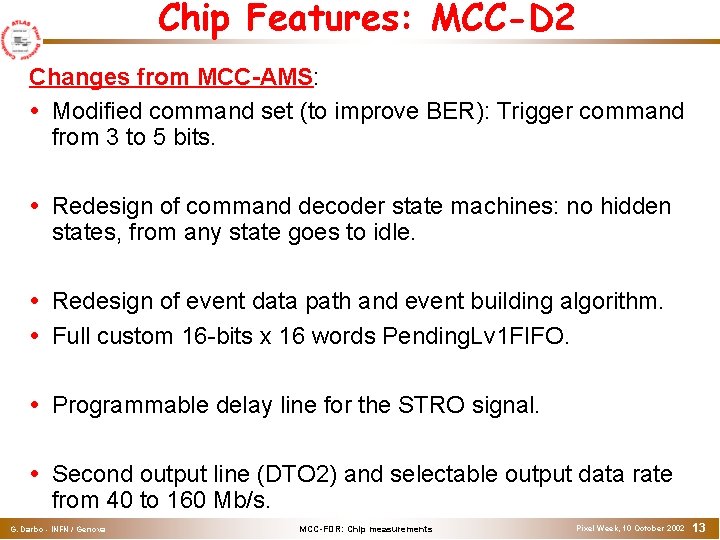

Chip Features: MCC-D 2 Changes from MCC-AMS: Modified command set (to improve BER): Trigger command from 3 to 5 bits. Redesign of command decoder state machines: no hidden states, from any state goes to idle. Redesign of event data path and event building algorithm. Full custom 16 -bits x 16 words Pending. Lv 1 FIFO. Programmable delay line for the STRO signal. Second output line (DTO 2) and selectable output data rate from 40 to 160 Mb/s. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 13

MCC-D 2 layout No. of Standard Cells: 13, 446 No. of Transistors: 351, 964 Chip size: 11. 939 mm x 8. 361 mm = 99. 8 mm 2 Full custom FIFO’s Delay Line Pending LV 1 FIFO G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 14

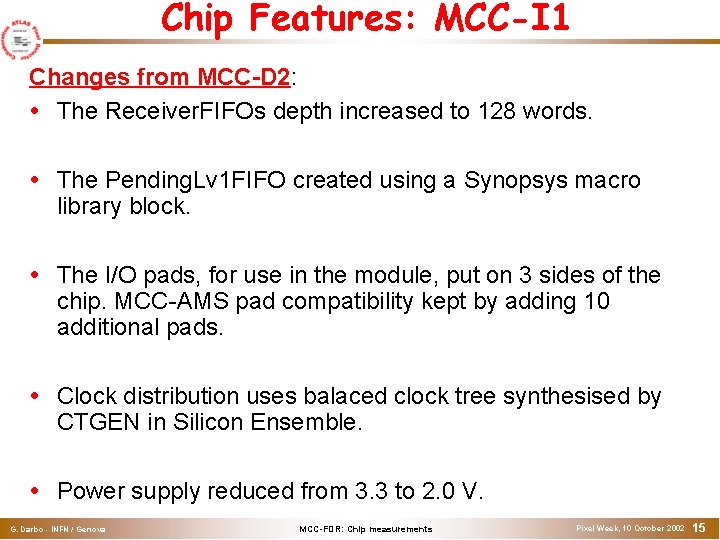

Chip Features: MCC-I 1 Changes from MCC-D 2: The Receiver. FIFOs depth increased to 128 words. The Pending. Lv 1 FIFO created using a Synopsys macro library block. The I/O pads, for use in the module, put on 3 sides of the chip. MCC-AMS pad compatibility kept by adding 10 additional pads. Clock distribution uses balaced clock tree synthesised by CTGEN in Silicon Ensemble. Power supply reduced from 3. 3 to 2. 0 V. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 15

MCC-I 1 layout No. of Standard Cells: 33, 210 No. of Transistors: layout = 660, 286 schematics = 627, 972 Chip size: 6. 380 mm x 3. 980 mm = 25. 4 mm 2 Full custom FIFO’s Delay Line G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 16

Summary Specifications for the Pixel system architecture defined in ‘ 97 with revision and back compatibility in ‘ 00. First chip (MCC-AMS) produced in 1998 with radsoft modules built and operated from 1998 to 2001. DMILL version of FE and MCC produced in 2000, no modules built due to low chip yield and insufficient rad tolerance. First DSM chip versions produced in 2002. Both FE and MCC operated on detector modules successfully. Minor errors will be fixed for next submission. G. Darbo - INFN / Genova MCC-FDR: Chip measurements Pixel Week, 10 October 2002 17

- Slides: 17