Pipelining lts 1 Pipelining adalah teknik pemrosesan dengan

![Eksekusi instruksi RR (operandnya terletak dalam register) reg[R 1] op reg[R 2] • IF: Eksekusi instruksi RR (operandnya terletak dalam register) reg[R 1] op reg[R 2] • IF:](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-19.jpg)

![Eksekusi instruksi percabangan bersyarat • IF: Instruction fetch IR IMemory[PC] PC incr. PC • Eksekusi instruksi percabangan bersyarat • IF: Instruction fetch IR IMemory[PC] PC incr. PC •](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-21.jpg)

![Eksekusi instruksi percabangan bersyarat misal BRZ a • IF: Instruction fetch IR IMemory[PC] PC Eksekusi instruksi percabangan bersyarat misal BRZ a • IF: Instruction fetch IR IMemory[PC] PC](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-40.jpg)

- Slides: 59

Pipelining lts 1

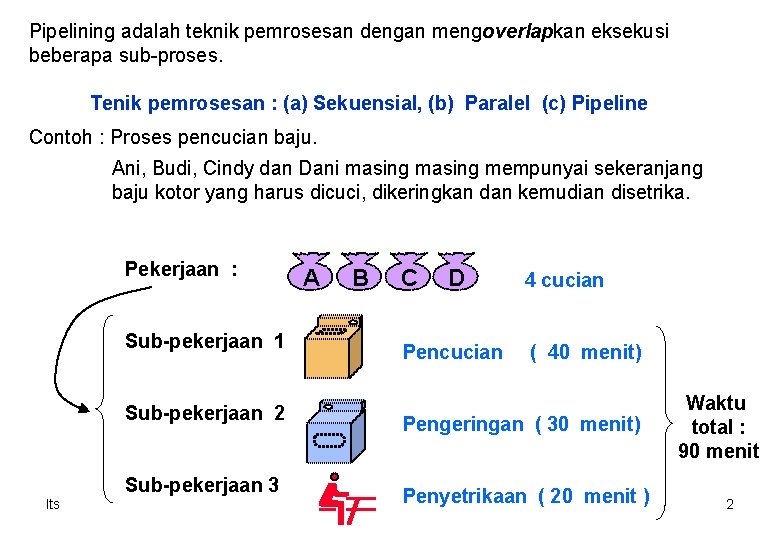

Pipelining adalah teknik pemrosesan dengan mengoverlapkan eksekusi beberapa sub-proses. Tenik pemrosesan : (a) Sekuensial, (b) Paralel (c) Pipeline Contoh : Proses pencucian baju. Ani, Budi, Cindy dan Dani masing mempunyai sekeranjang baju kotor yang harus dicuci, dikeringkan dan kemudian disetrika. Pekerjaan : Sub-pekerjaan 1 Sub-pekerjaan 2 Sub-pekerjaan 3 lts A B C D Pencucian 4 cucian ( 40 menit) Pengeringan ( 30 menit) Penyetrikaan ( 20 menit ) Waktu total : 90 menit 2

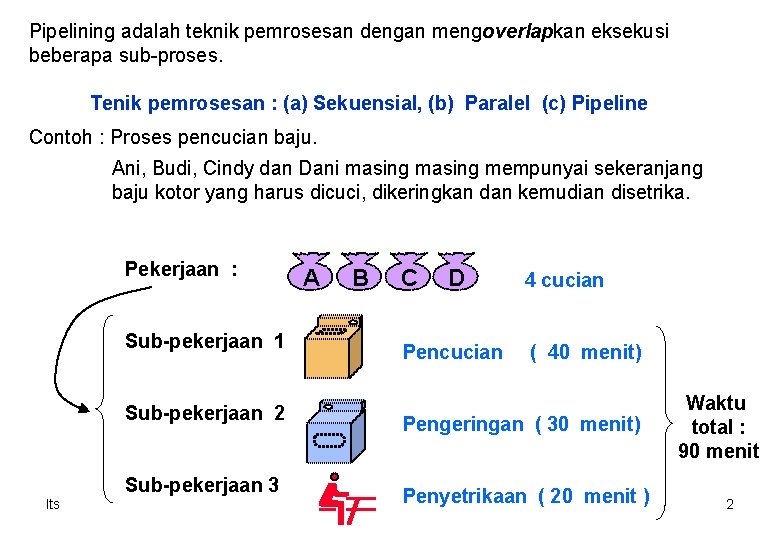

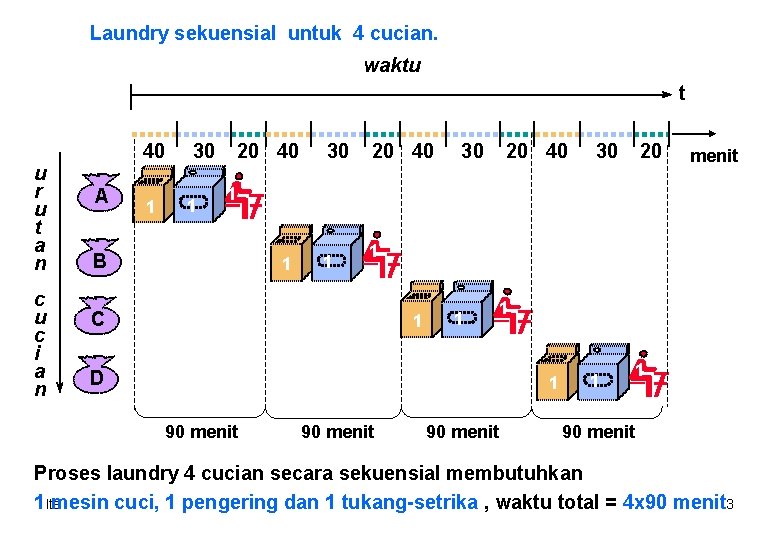

Laundry sekuensial untuk 4 cucian. waktu t u r u t a n c u c i a n A 40 30 1 1 20 40 30 20 menit 1 B 1 1 1 C 1 1 D 1 1 90 menit 1 1 90 menit Proses laundry 4 cucian secara sekuensial membutuhkan 1 ltsmesin cuci, 1 pengering dan 1 tukang-setrika , waktu total = 4 x 90 menit 3

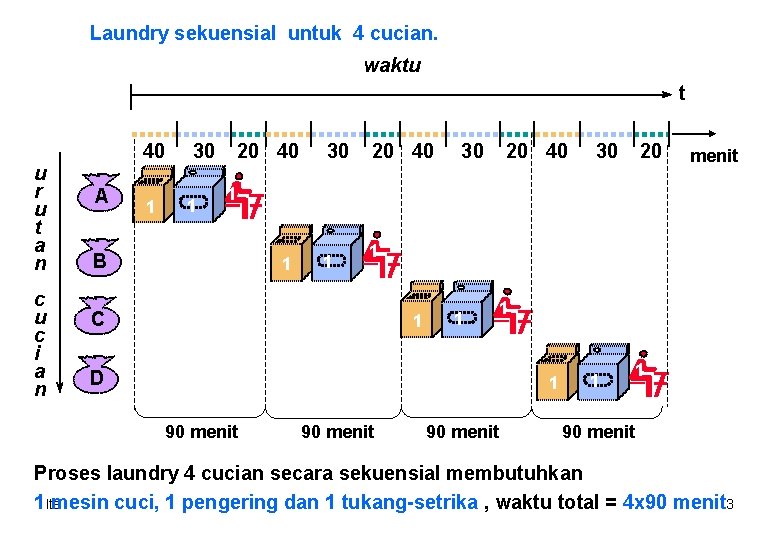

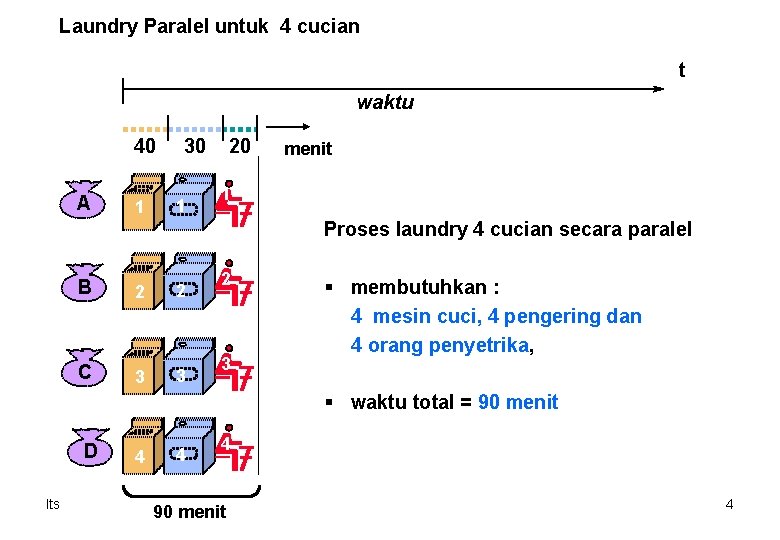

Laundry Paralel untuk 4 cucian t waktu 40 A 1 30 1 20 menit 1 Proses laundry 4 cucian secara paralel B 2 2 C 3 3 2 3 § membutuhkan : 4 mesin cuci, 4 pengering dan 4 orang penyetrika, § waktu total = 90 menit D lts 4 4 4 90 menit 4

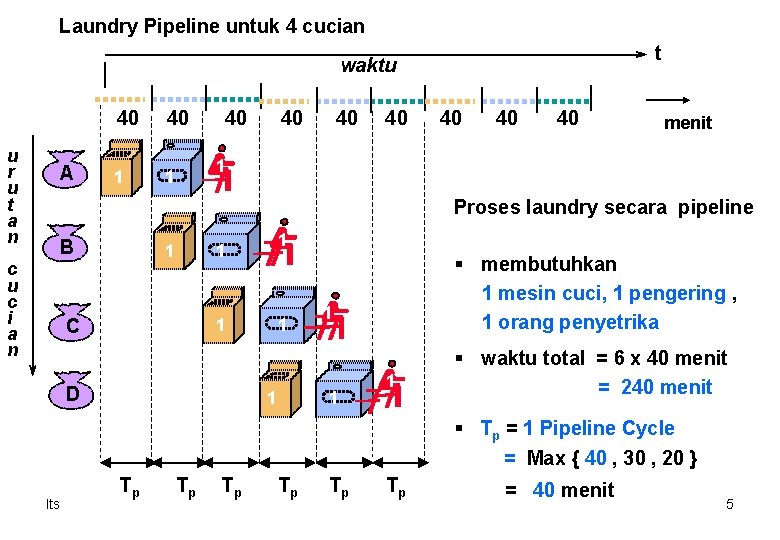

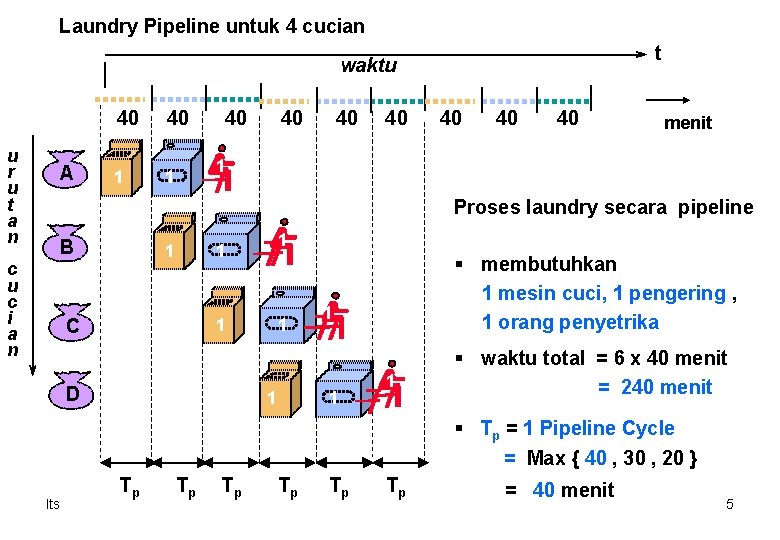

Laundry Pipeline untuk 4 cucian t waktu u r u t a n A 40 40 1 1 40 40 menit 1 Proses laundry secara pipeline B c u c i a n 1 1 1 C D 1 § membutuhkan 1 mesin cuci, 1 pengering , 1 orang penyetrika 1 1 1 § waktu total = 6 x 40 menit = 240 menit § Tp = 1 Pipeline Cycle = Max { 40 , 30 , 20 } lts Tp Tp Tp = 40 menit 5

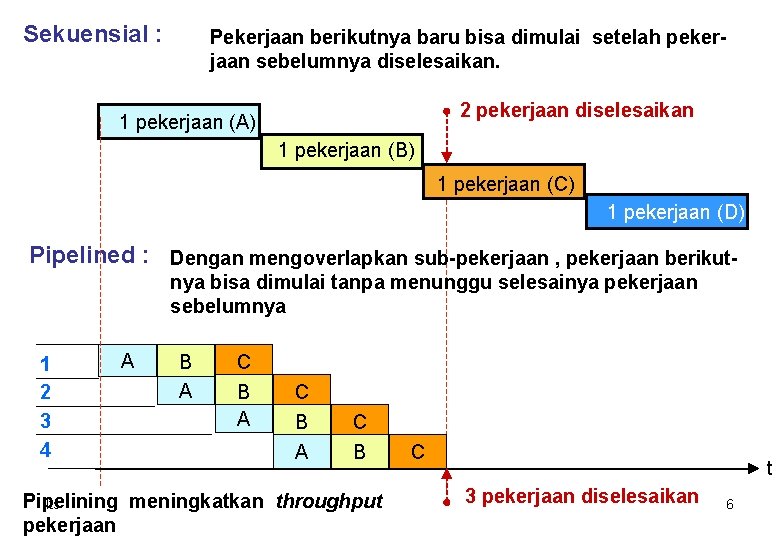

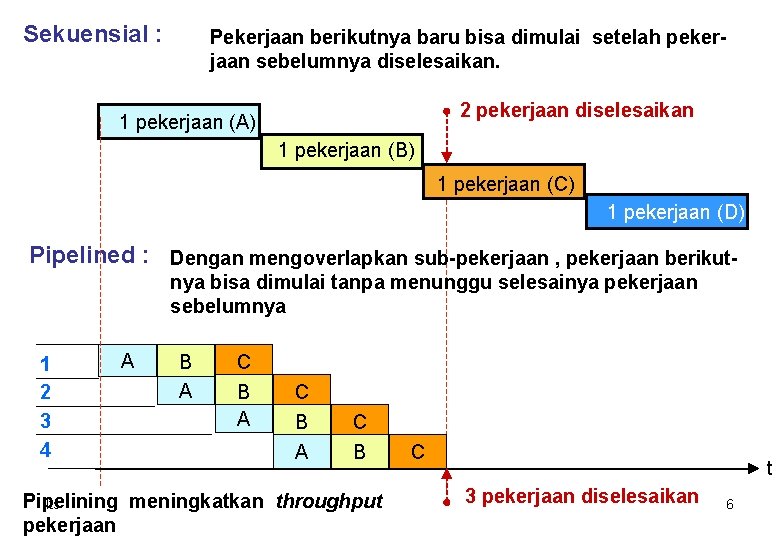

Sekuensial : Pekerjaan berikutnya baru bisa dimulai setelah pekerjaan sebelumnya diselesaikan. 2 pekerjaan diselesaikan 1 pekerjaan (A) 1 pekerjaan (B) 1 pekerjaan (C) 1 pekerjaan (D) Pipelined : Dengan mengoverlapkan sub-pekerjaan , pekerjaan berikutnya bisa dimulai tanpa menunggu selesainya pekerjaan sebelumnya 1 2 3 4 A B A C B C A B Pipelining meningkatkan throughput lts pekerjaan C t 3 pekerjaan diselesaikan 6

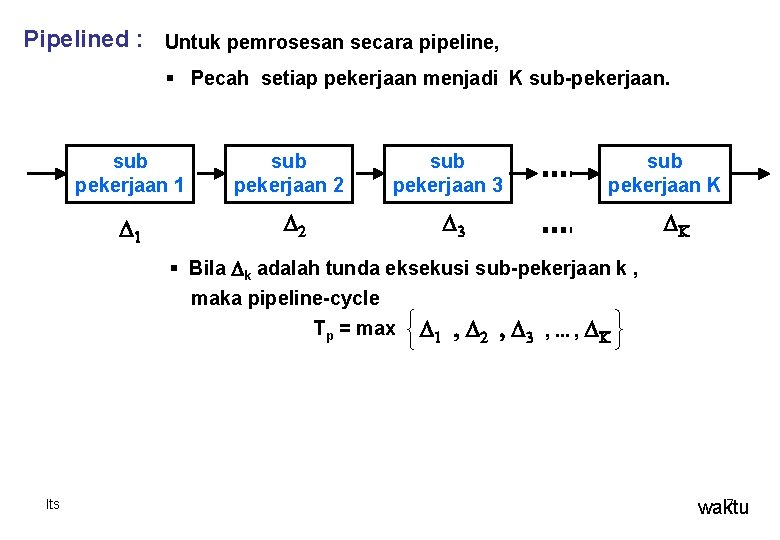

Pipelined : Untuk pemrosesan secara pipeline, § Pecah setiap pekerjaan menjadi K sub-pekerjaan. sub pekerjaan 1 D 1 sub pekerjaan 2 D 2 sub pekerjaan 3 sub pekerjaan K D 3 DK § Bila Dk adalah tunda eksekusi sub-pekerjaan k , maka pipeline-cycle Tp = max D 1 , D 2 , D 3 , . . . , DK lts 7 waktu

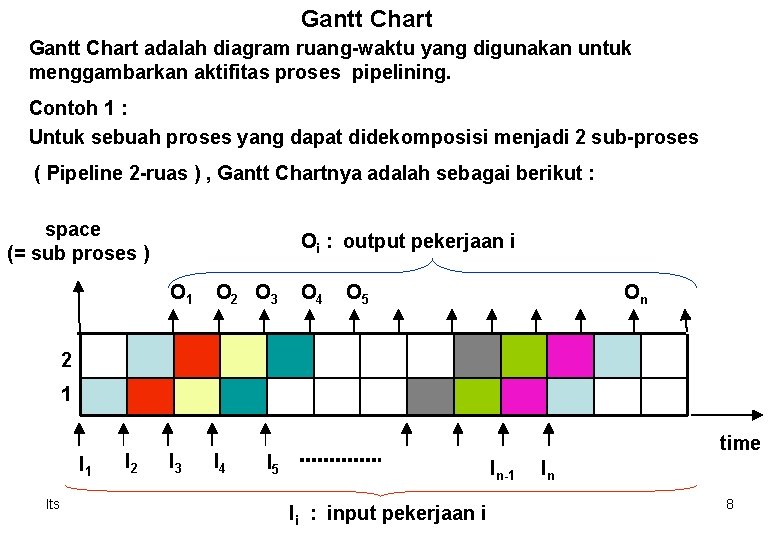

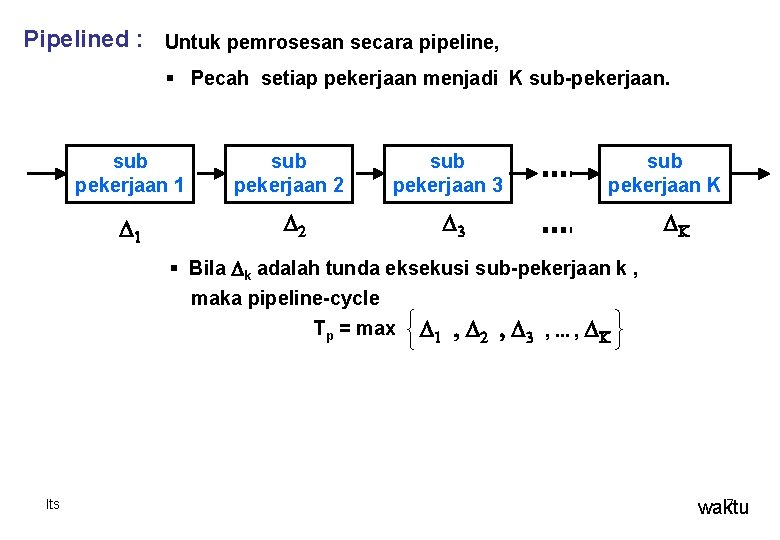

Gantt Chart adalah diagram ruang-waktu yang digunakan untuk menggambarkan aktifitas proses pipelining. Contoh 1 : Untuk sebuah proses yang dapat didekomposisi menjadi 2 sub-proses ( Pipeline 2 -ruas ) , Gantt Chartnya adalah sebagai berikut : space (= sub proses ) Oi : output pekerjaan i O 1 O 2 O 3 O 4 O 5 On 2 1 I 1 lts I 2 I 3 I 4 time I 5 In-1 Ii : input pekerjaan i In 8

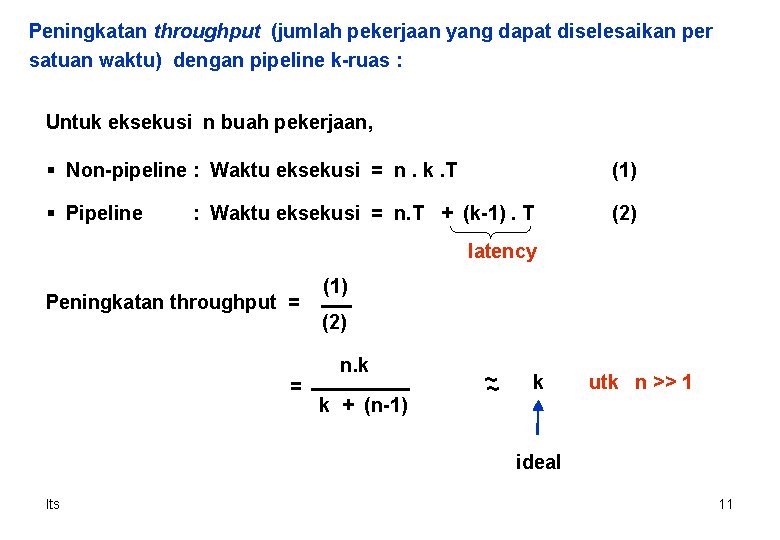

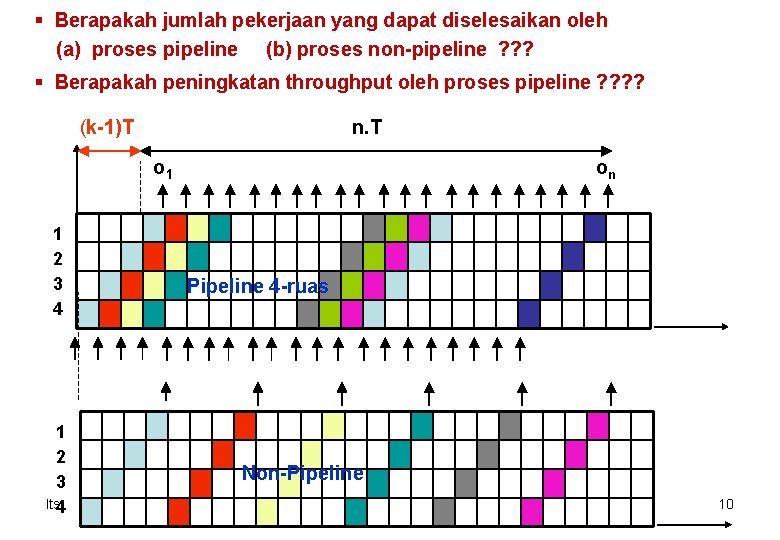

Contoh 2 : 0 output Pipeline 4 -ruas, K = 4 n output T 1 2 3 4 (k-1)T n. T In latency Pada daerah latency , pipeline belum menghasilkan output lts 9

§ Berapakah jumlah pekerjaan yang dapat diselesaikan oleh (a) proses pipeline (b) proses non-pipeline ? ? ? § Berapakah peningkatan throughput oleh proses pipeline ? ? (k-1)T n. T o 1 1 2 3 4 1 2 3 lts 4 on Pipeline 4 -ruas Non-Pipeline 10

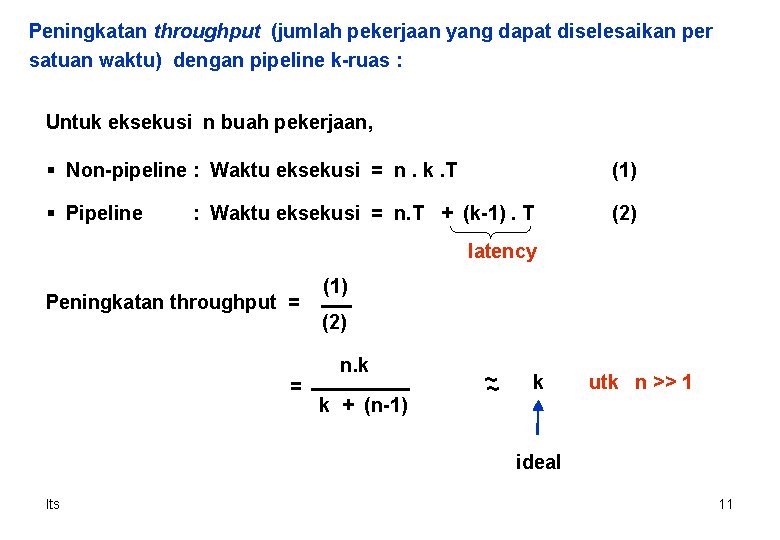

Peningkatan throughput (jumlah pekerjaan yang dapat diselesaikan per satuan waktu) dengan pipeline k-ruas : Untuk eksekusi n buah pekerjaan, § Non-pipeline : Waktu eksekusi = n. k. T (1) § Pipeline (2) : Waktu eksekusi = n. T + (k-1). T latency Peningkatan throughput = = (1) (2) n. k k + (n-1) ~ ~ k utk n >> 1 ideal lts 11

Peningkatan throughput dengan pipeline Peningkatan throughput eksekusi instruksi dengan pendekatan pipeline INSTRUCTION PIPELINE lts 12

INSTRUCTION PIPELINE Arsitektur pipeline untuk pekerjaan eksekusi instruksi I 1 eksekusi instruksi I 2 eksekusi instruksi I 3 eksekusi instruksi I 4 t § Eksekusi sebuah instruksi disebut 1 instruction-cycle. Sub pekerjaan lts § 1 instruction cycle mempunyai pola beraturan (sama untuk semua instruksi) 13

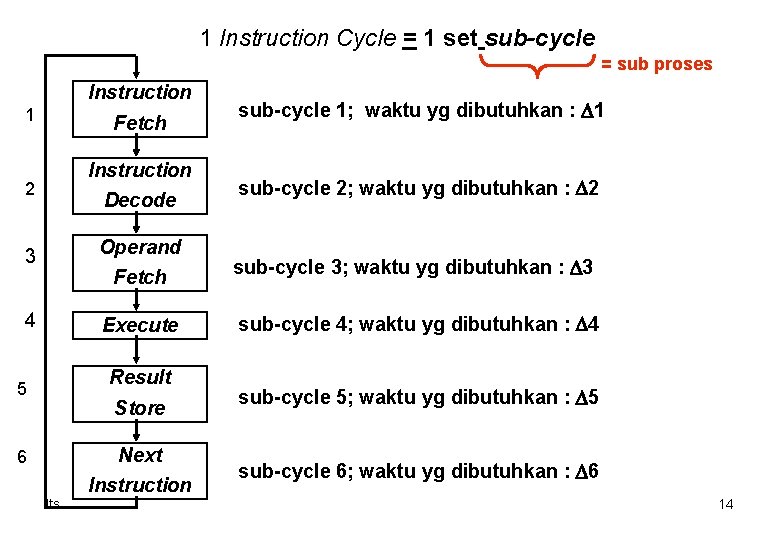

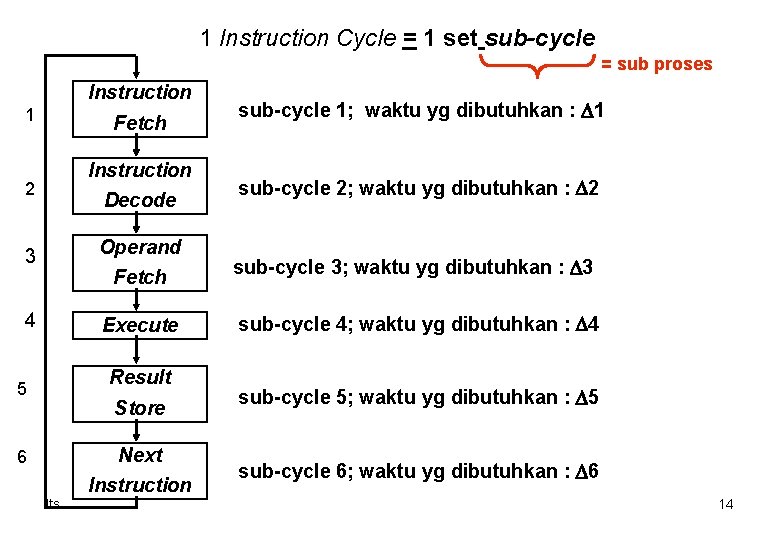

1 Instruction Cycle = 1 set sub-cycle = sub proses Instruction 1 Fetch Instruction 2 Decode sub-cycle 1; waktu yg dibutuhkan : D 1 sub-cycle 2; waktu yg dibutuhkan : D 2 3 Operand Fetch sub-cycle 3; waktu yg dibutuhkan : D 3 4 Execute sub-cycle 4; waktu yg dibutuhkan : D 4 Result 5 Store Next 6 Instruction lts sub-cycle 5; waktu yg dibutuhkan : D 5 sub-cycle 6; waktu yg dibutuhkan : D 6 14

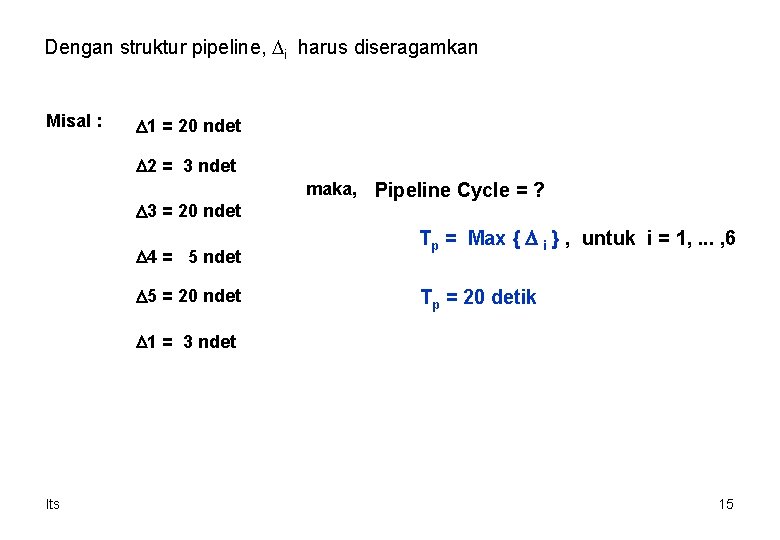

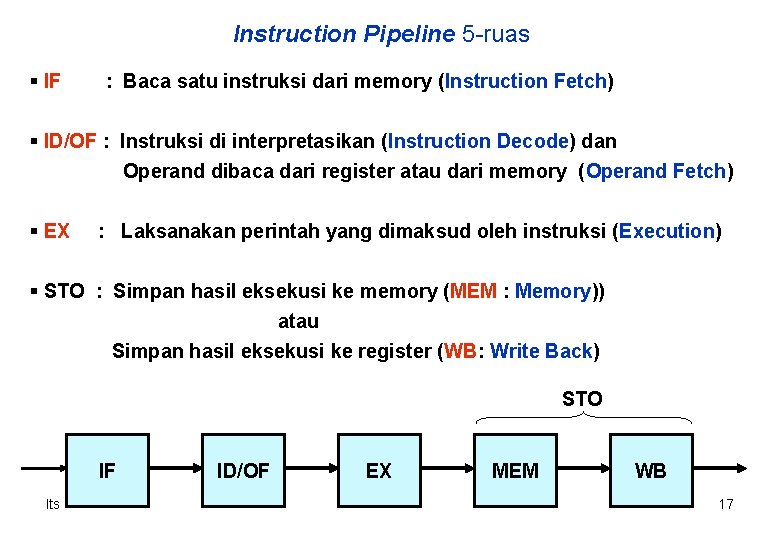

Dengan struktur pipeline, Di harus diseragamkan Misal : D 1 = 20 ndet D 2 = 3 ndet D 3 = 20 ndet D 4 = 5 ndet D 5 = 20 ndet maka, Pipeline Cycle = ? Tp = Max { D i } , untuk i = 1, . . . , 6 Tp = 20 detik D 1 = 3 ndet lts 15

Instruction T Fetch Instruction T Decode Operand T Fetch Execute T Result T Store Next T Instruction lts T=20 ndet masalah ! Instruction 20 idle Fetch T 23 25 Instruction 3 20 Decode Operand 20 25 25 Fetch T Execute 5 20 Result 20 23 25 Store Next 3 20 diatasi dengan Pengelompokan sub-cycle T Instruction 16 T = Max{23, 25, 23} = 25 ndet

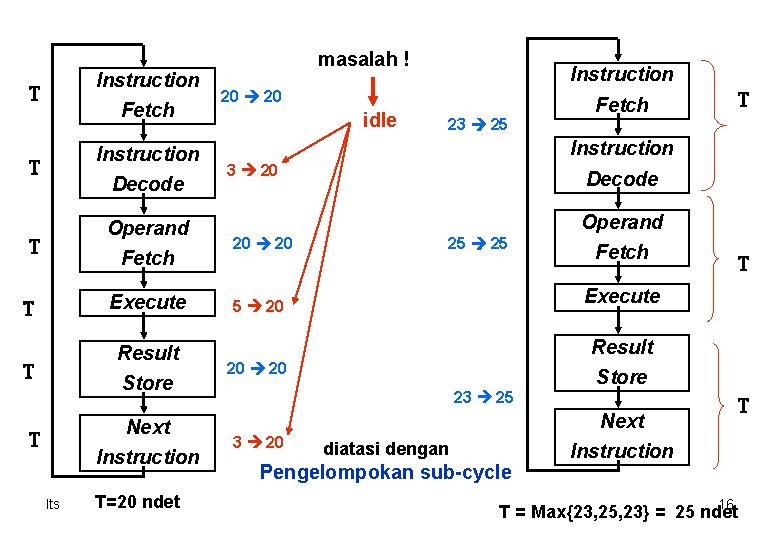

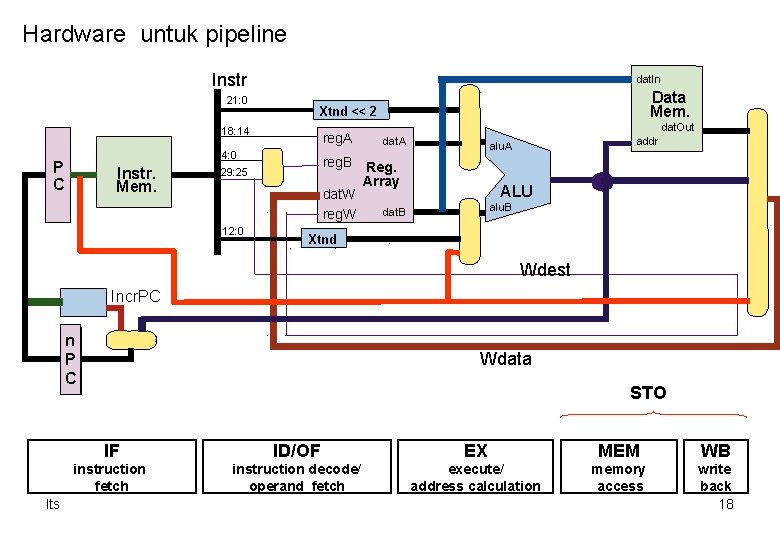

Instruction Pipeline 5 -ruas § IF : Baca satu instruksi dari memory (Instruction Fetch) § ID/OF : Instruksi di interpretasikan (Instruction Decode) dan Operand dibaca dari register atau dari memory (Operand Fetch) § EX : Laksanakan perintah yang dimaksud oleh instruksi (Execution) § STO : Simpan hasil eksekusi ke memory (MEM : Memory)) atau Simpan hasil eksekusi ke register (WB: Write Back) STO IF lts ID/OF EX MEM WB 17

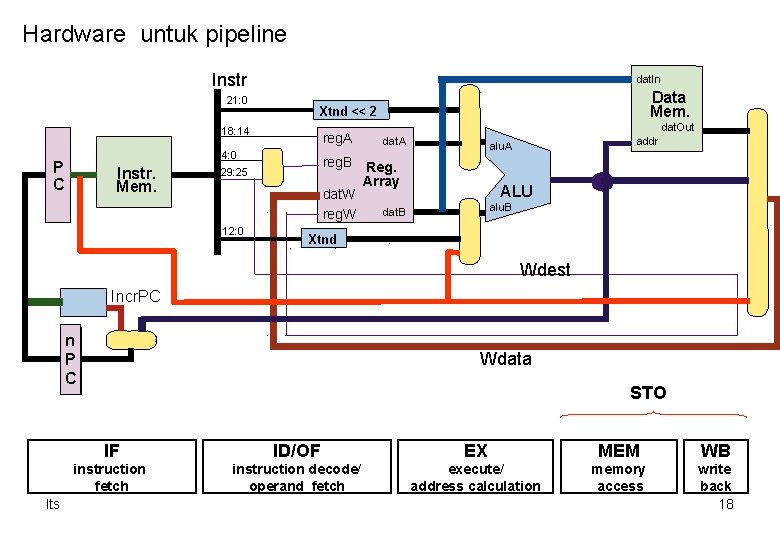

Hardware untuk pipeline Instr 21: 0 dat. In 18: 14 reg. A 4: 0 P C Instr. Mem. dat. Out dat. A addr alu. A reg. B Reg. Array dat. W dat. B reg. W 29: 25 12: 0 Data Mem. Xtnd << 2 ALU alu. B Xtnd Wdest Incr. PC n P C lts Wdata STO IF ID/OF EX MEM WB instruction fetch instruction decode/ operand fetch execute/ address calculation memory access write back 18

![Eksekusi instruksi RR operandnya terletak dalam register regR 1 op regR 2 IF Eksekusi instruksi RR (operandnya terletak dalam register) reg[R 1] op reg[R 2] • IF:](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-19.jpg)

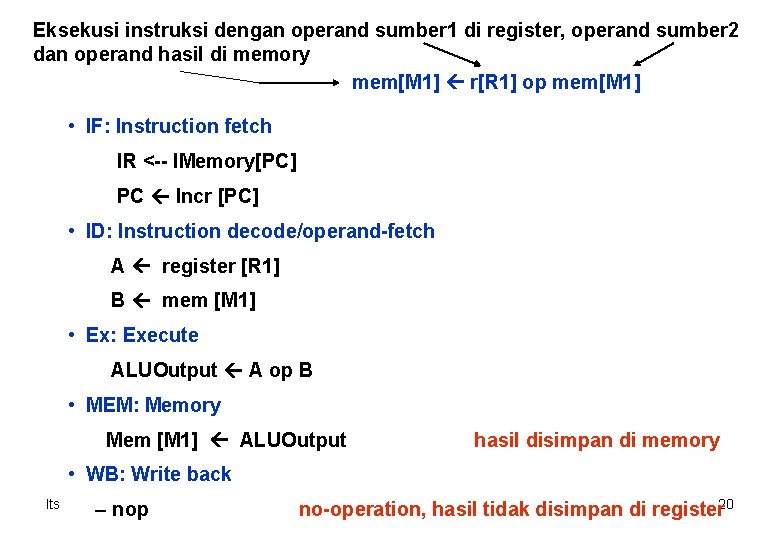

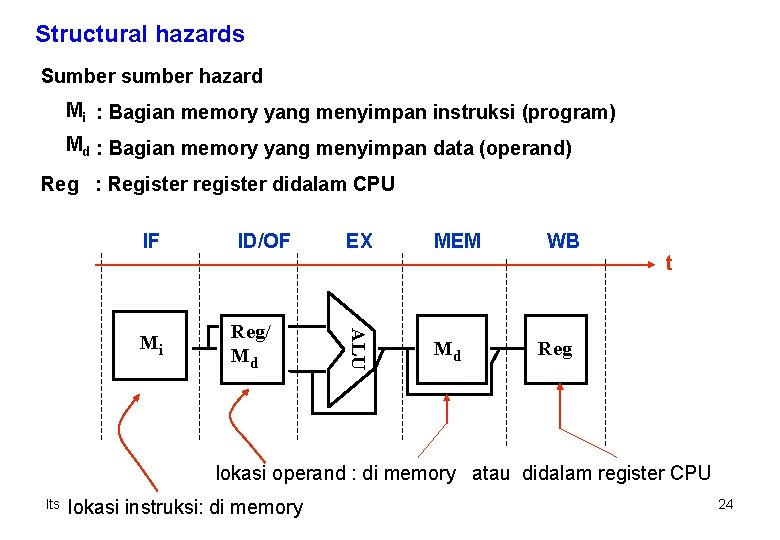

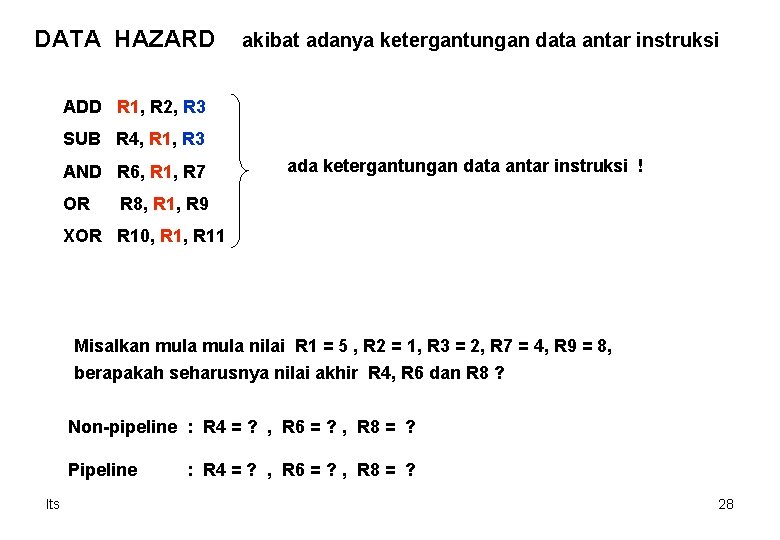

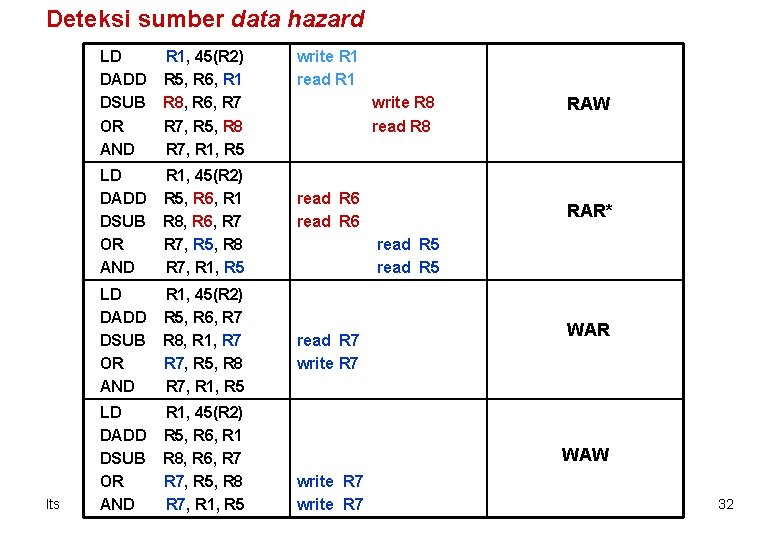

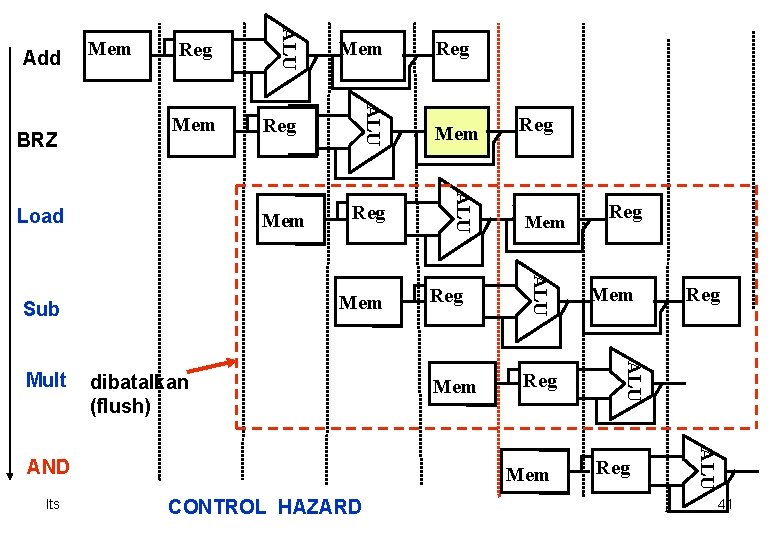

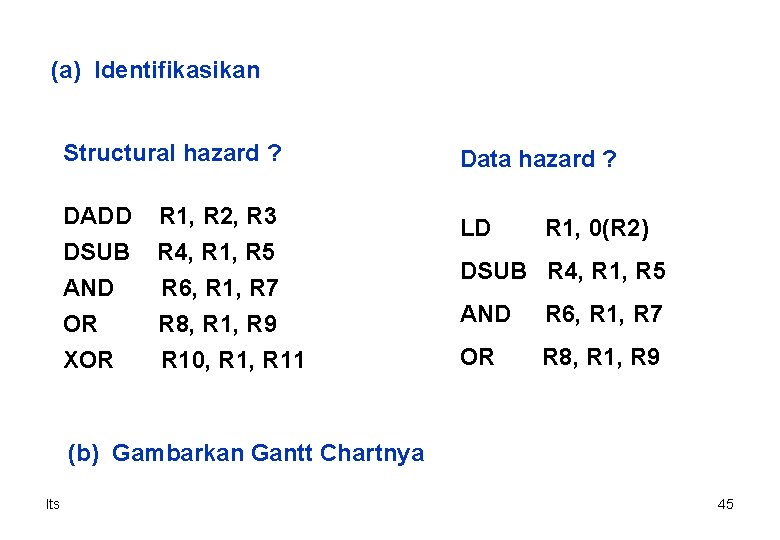

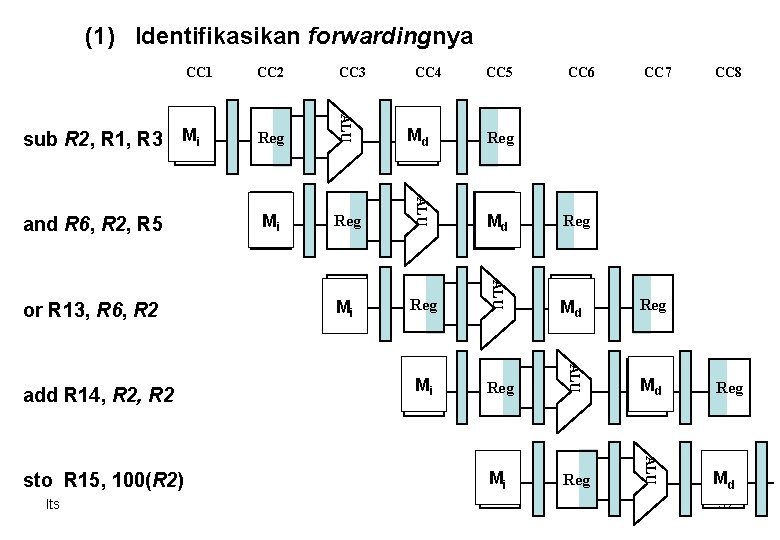

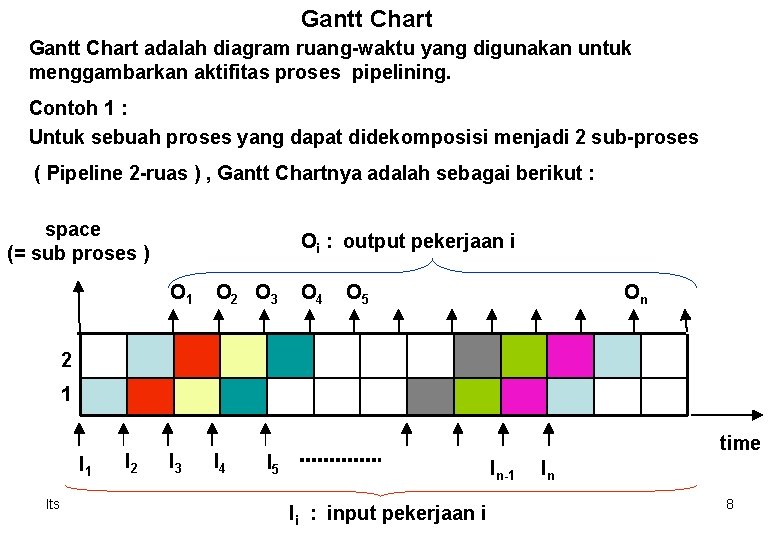

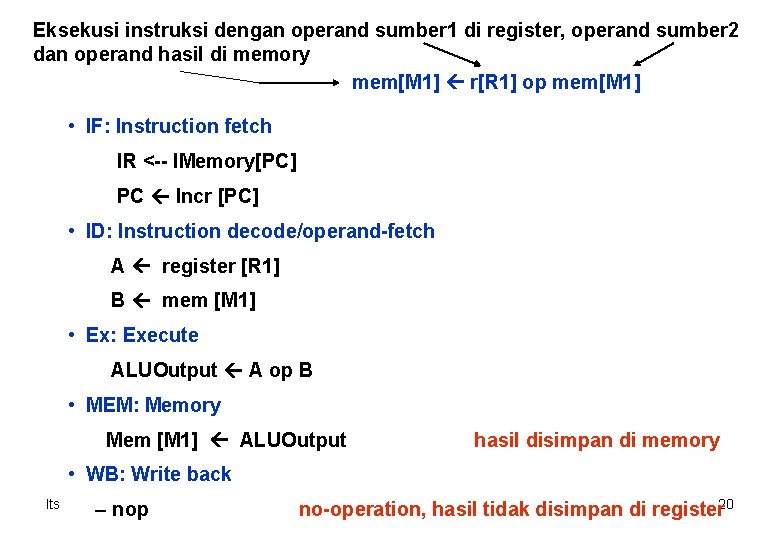

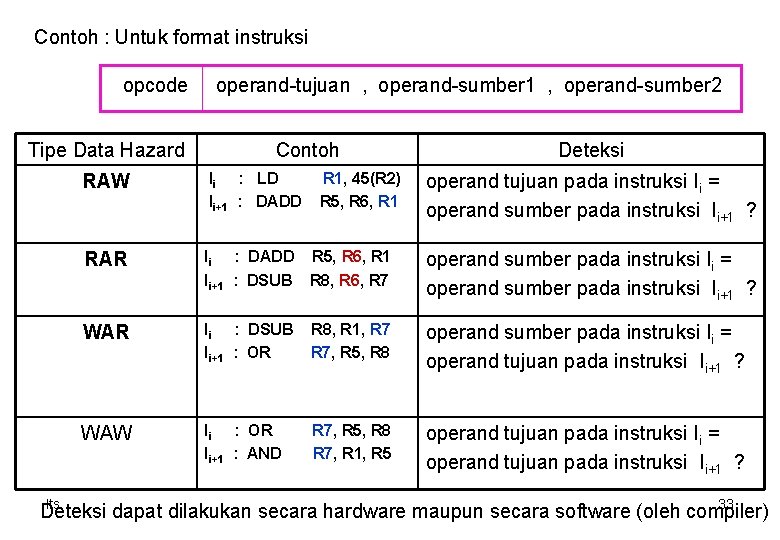

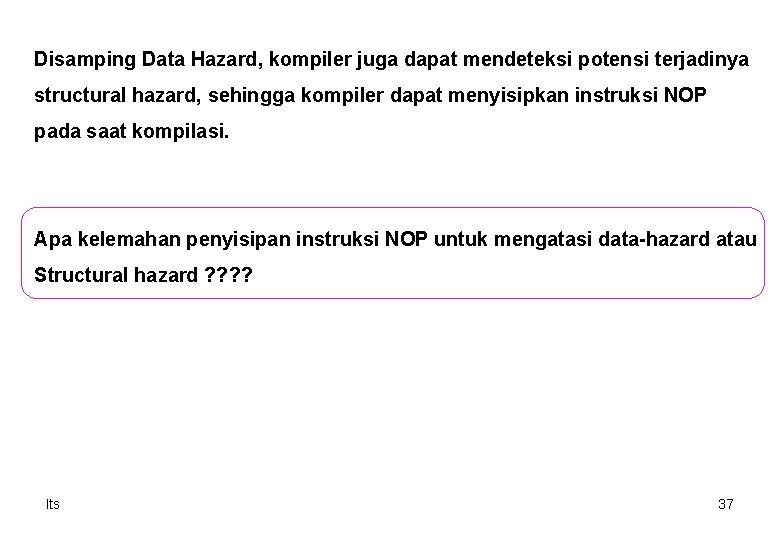

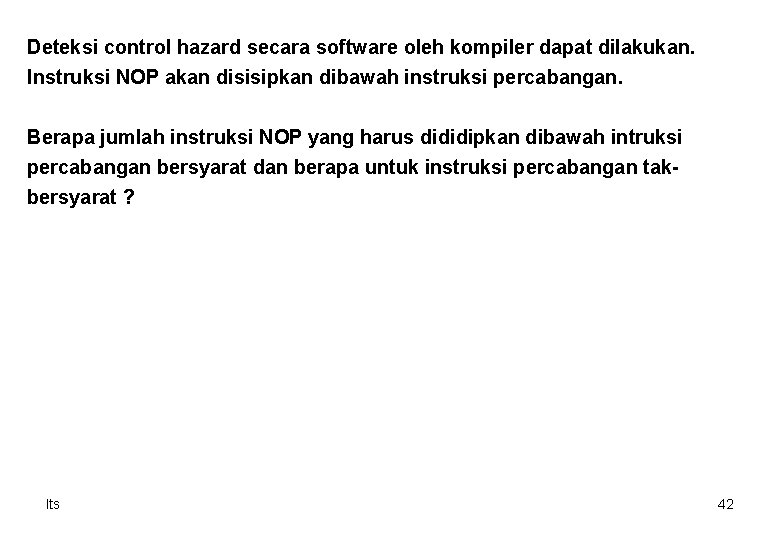

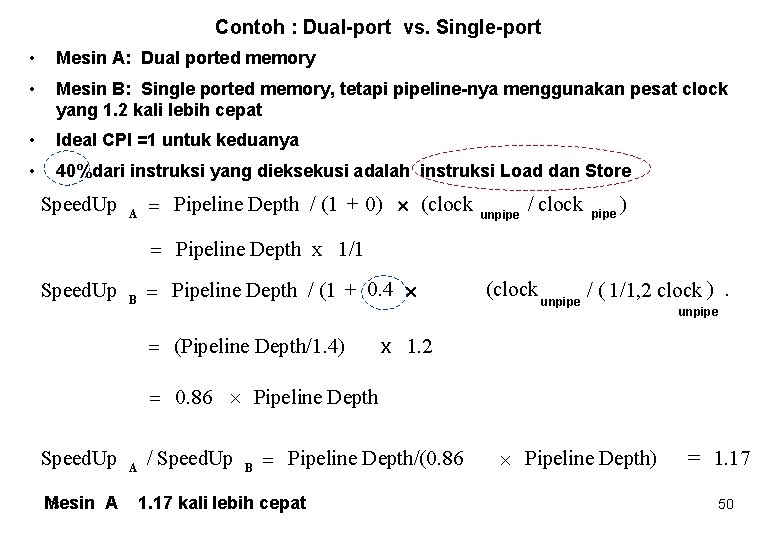

Eksekusi instruksi RR (operandnya terletak dalam register) reg[R 1] op reg[R 2] • IF: Instruction fetch IR Memory[PC] PC increment [PC] (alamat instruksi yang akan dieksekusi pada instruction cycle berikutnya) • ID: Instruction decode/operand-fetch A register [R 1] A dan B: register pada bagian B register [R 2] input ALU • Ex: Execute ALUOutput A op B • MEM: Memory nop (nop = no operation, tidak ada penulisan hasil ALU ke memory) • WB: Write back lts Register[R 1] ALUOutput (menuliskan hasil ALU ke register R 1) 19

Eksekusi instruksi dengan operand sumber 1 di register, operand sumber 2 dan operand hasil di memory mem[M 1] r[R 1] op mem[M 1] • IF: Instruction fetch IR <-- IMemory[PC] PC Incr [PC] • ID: Instruction decode/operand-fetch A register [R 1] B mem [M 1] • Ex: Execute ALUOutput A op B • MEM: Memory Mem [M 1] ALUOutput hasil disimpan di memory • WB: Write back lts – nop no-operation, hasil tidak disimpan di register 20

![Eksekusi instruksi percabangan bersyarat IF Instruction fetch IR IMemoryPC PC incr PC Eksekusi instruksi percabangan bersyarat • IF: Instruction fetch IR IMemory[PC] PC incr. PC •](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-21.jpg)

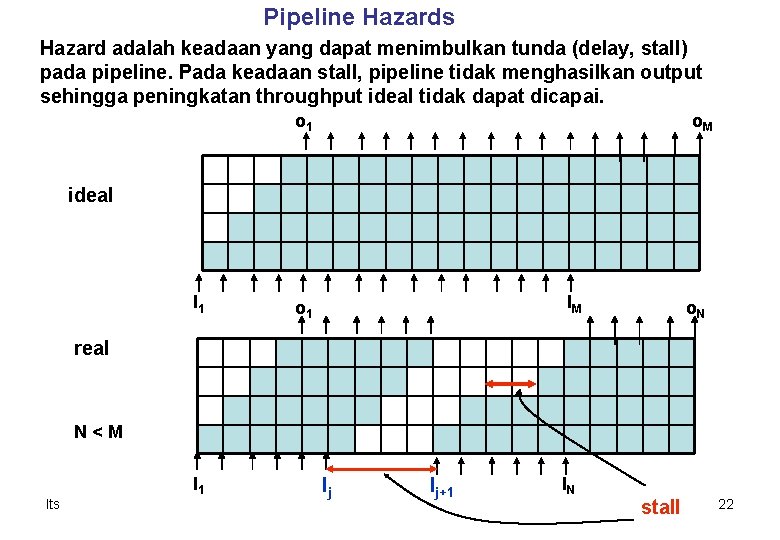

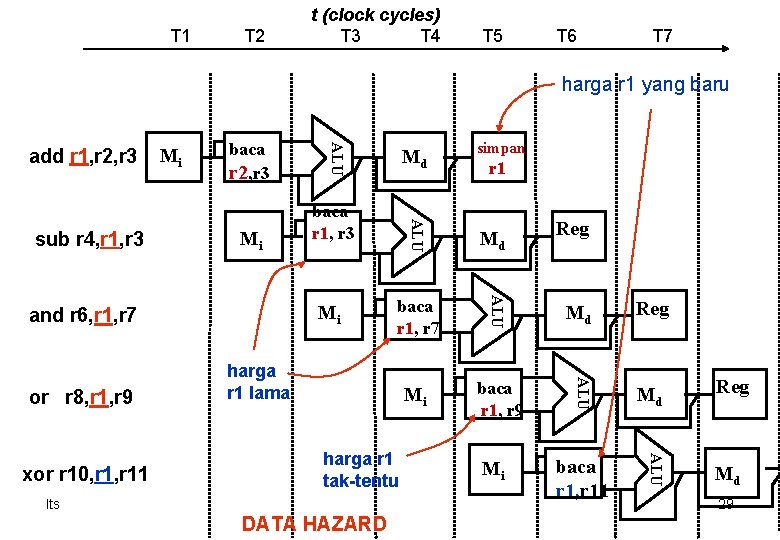

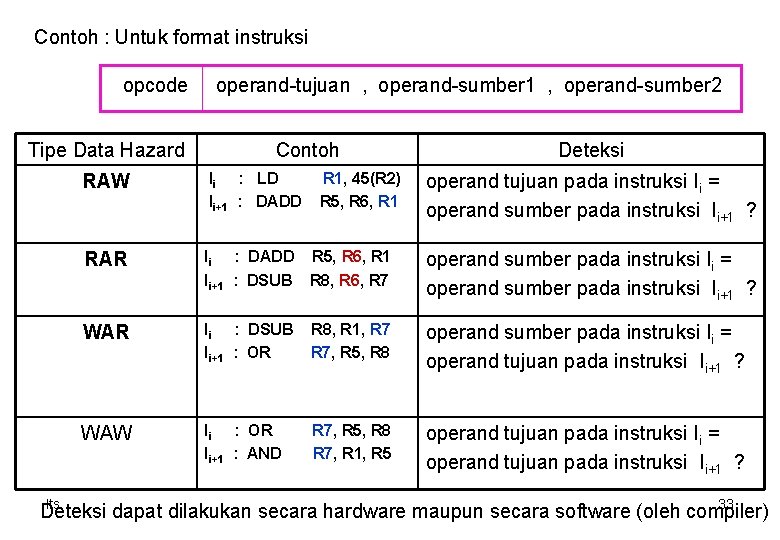

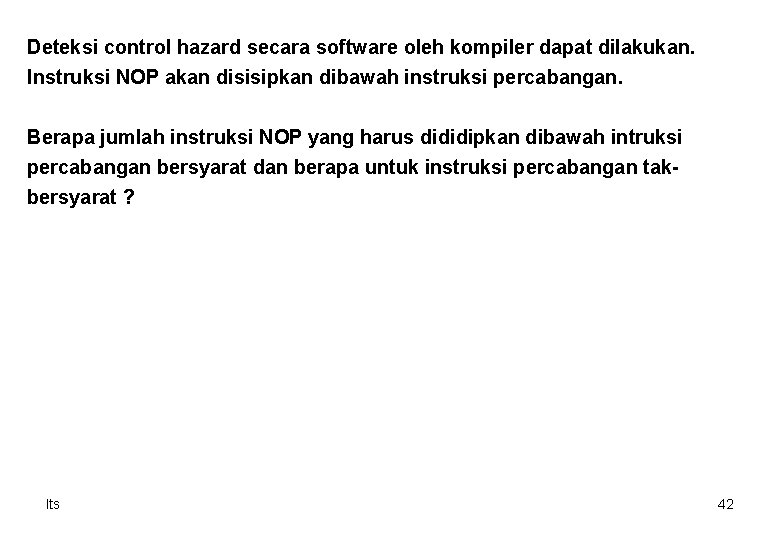

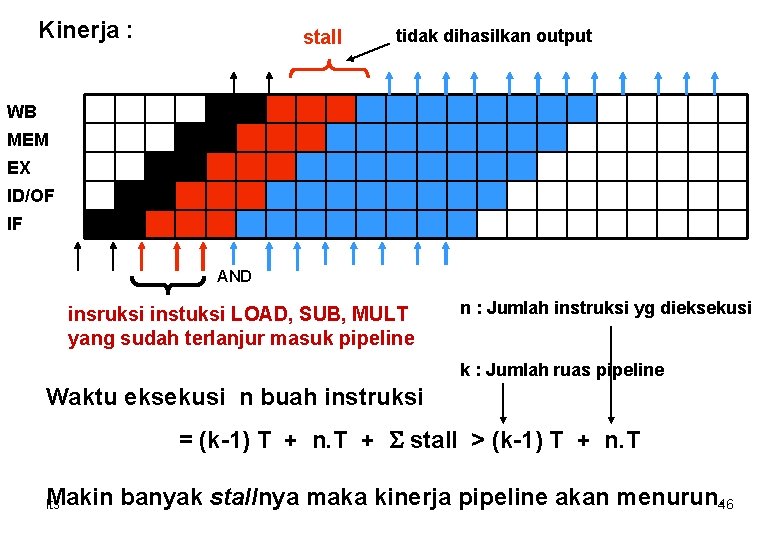

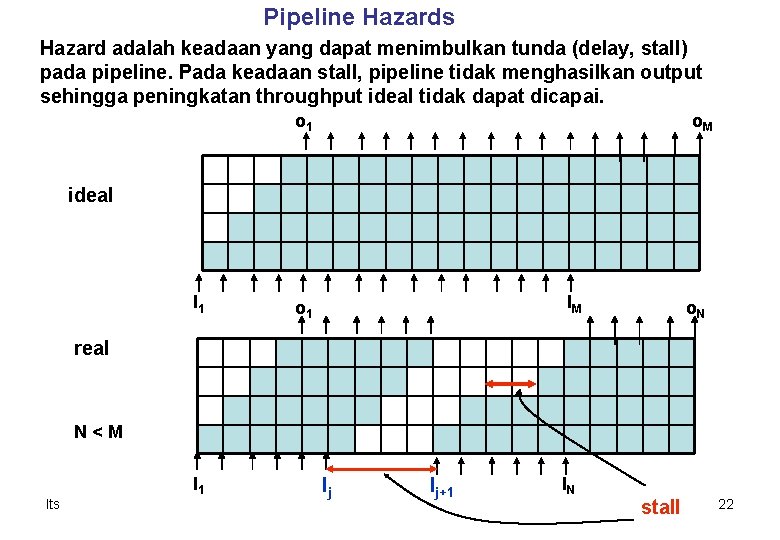

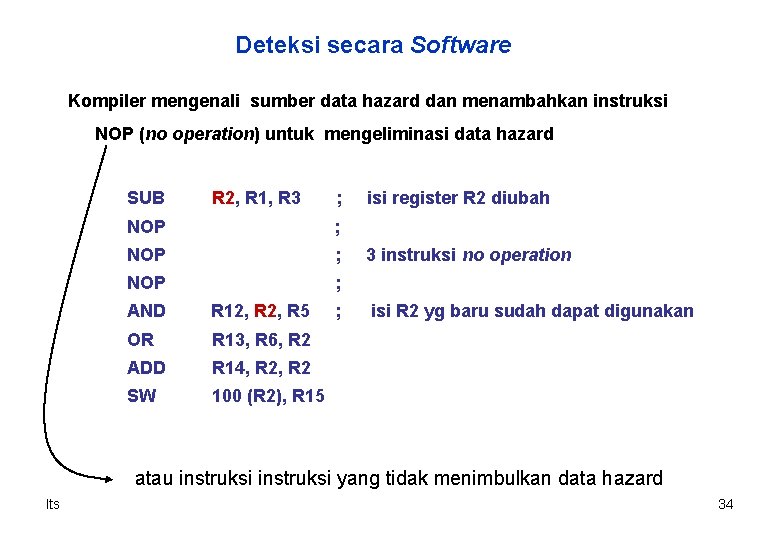

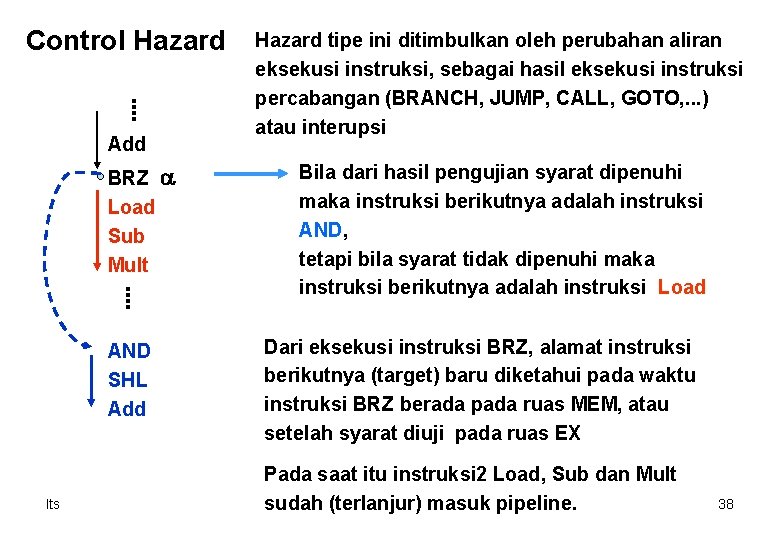

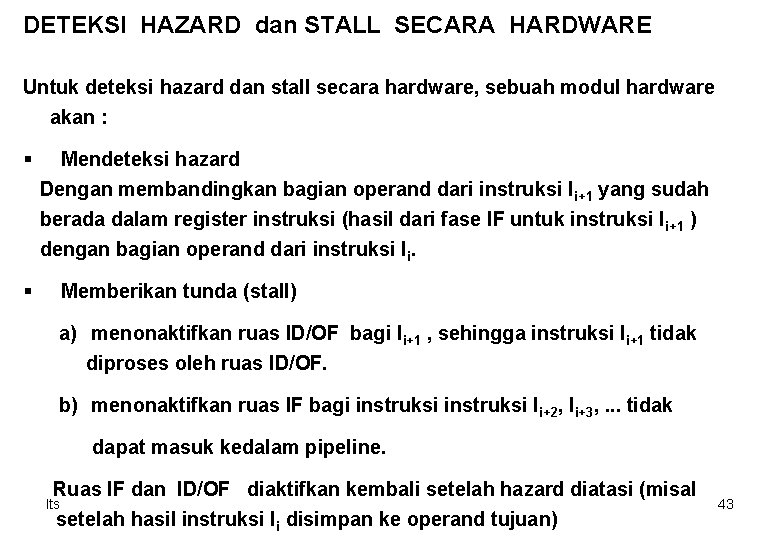

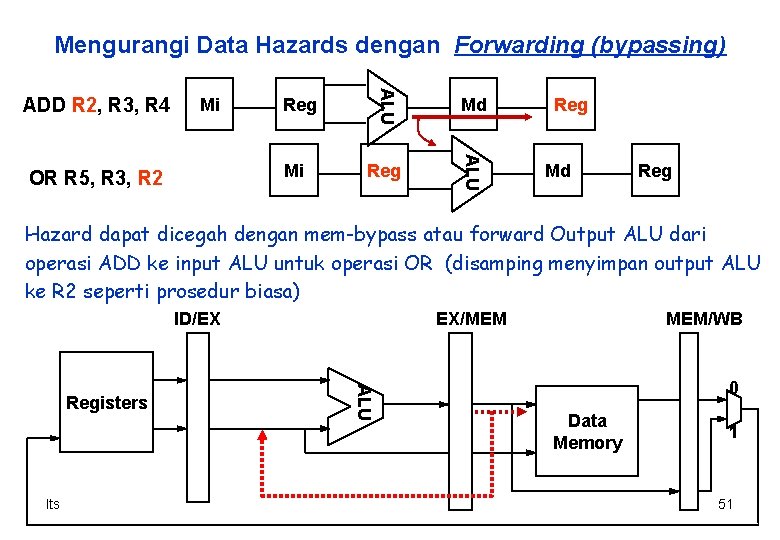

Eksekusi instruksi percabangan bersyarat • IF: Instruction fetch IR IMemory[PC] PC incr. PC • ID: Instruction decode/operand-fetch nop • Ex: Execute Target PC + displacement • MEM: Memory PC Target atau • WB: Write back nop lts BRZ a Branch if Zero syarat percabangan displacement (relative addressing mode) tidak ada operand-fetch menghitung alamat target (= alamat instruksi berikutnya) Bila syarat percabangan dipenuhi alamat penyimpanan instruksi berikutnya tergantung dari hasil pengujian syarat (hasil ALU = 0 ? ) 21

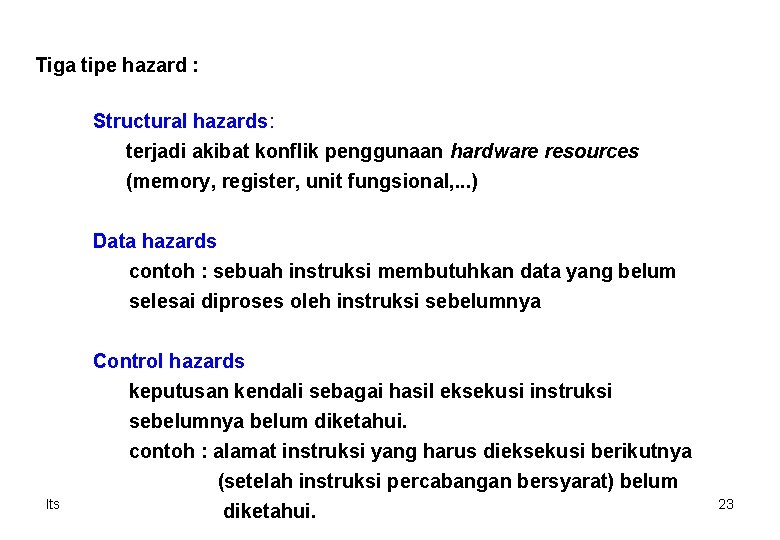

Pipeline Hazards Hazard adalah keadaan yang dapat menimbulkan tunda (delay, stall) pada pipeline. Pada keadaan stall, pipeline tidak menghasilkan output sehingga peningkatan throughput ideal tidak dapat dicapai. o 1 o. M ideal I 1 IM o 1 o. N real N<M lts I 1 Ij Ij+1 IN stall 22

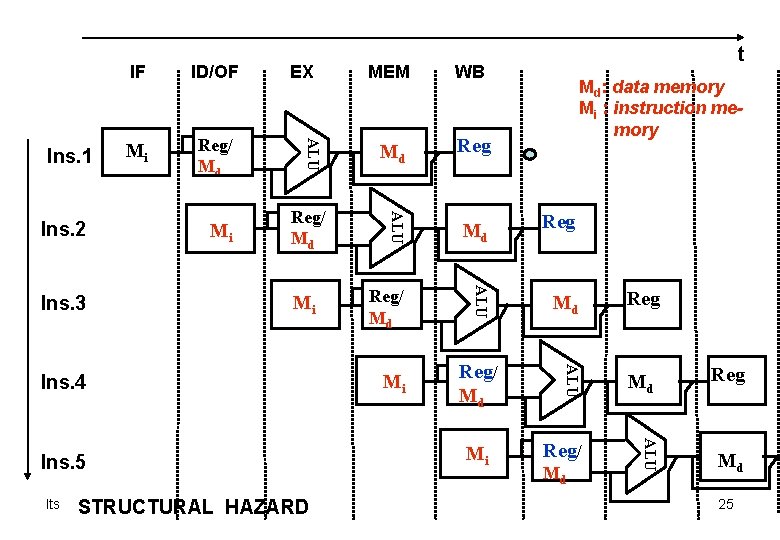

Tiga tipe hazard : Structural hazards: terjadi akibat konflik penggunaan hardware resources (memory, register, unit fungsional, . . . ) Data hazards contoh : sebuah instruksi membutuhkan data yang belum selesai diproses oleh instruksi sebelumnya Control hazards keputusan kendali sebagai hasil eksekusi instruksi sebelumnya belum diketahui. contoh : alamat instruksi yang harus dieksekusi berikutnya (setelah instruksi percabangan bersyarat) belum lts diketahui. 23

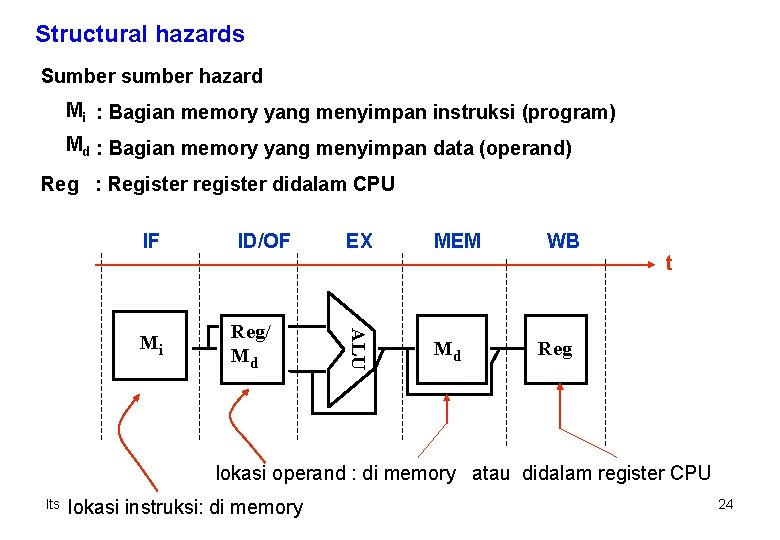

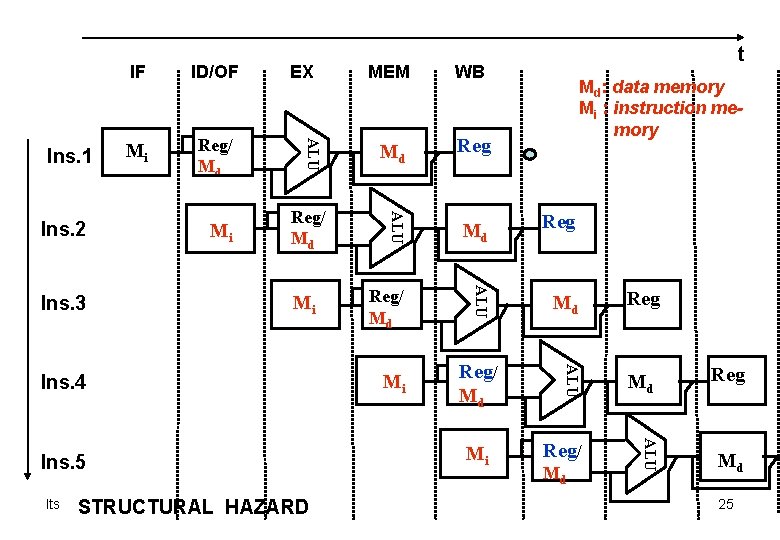

Structural hazards Sumber sumber hazard Mi : Bagian memory yang menyimpan instruksi (program) Md : Bagian memory yang menyimpan data (operand) Reg : Register register didalam CPU IF ID/OF EX MEM WB t Reg/ Md ALU Mi Md Reg lokasi operand : di memory atau didalam register CPU lts lokasi instruksi: di memory 24

Reg/ Md Mi WB Md Reg/ Md ALU Ins. 3 Mi MEM ALU Ins. 2 ID/OF ALU Ins. 1 IF EX Mi lts STRUCTURAL HAZARD Reg/ Md Mi Reg Md Reg/ ALU Ins. 5 Mi Md: data memory Mi : instruction memory ALU Ins. 4 t Md Reg Md 25

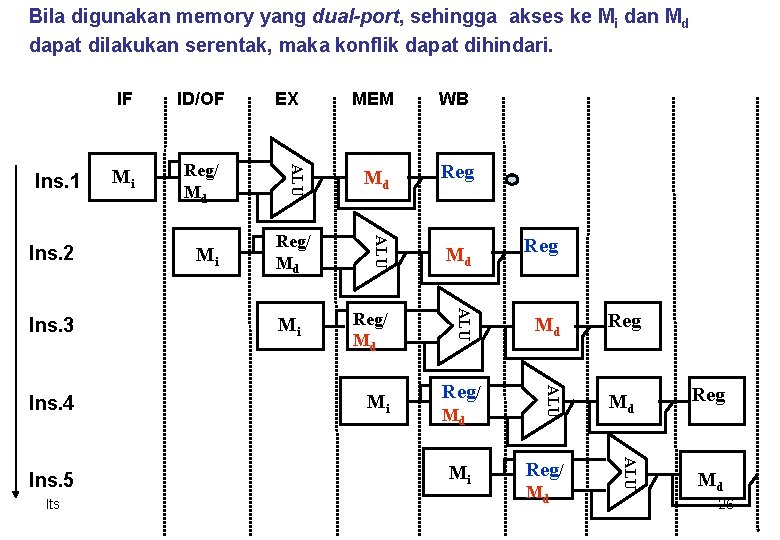

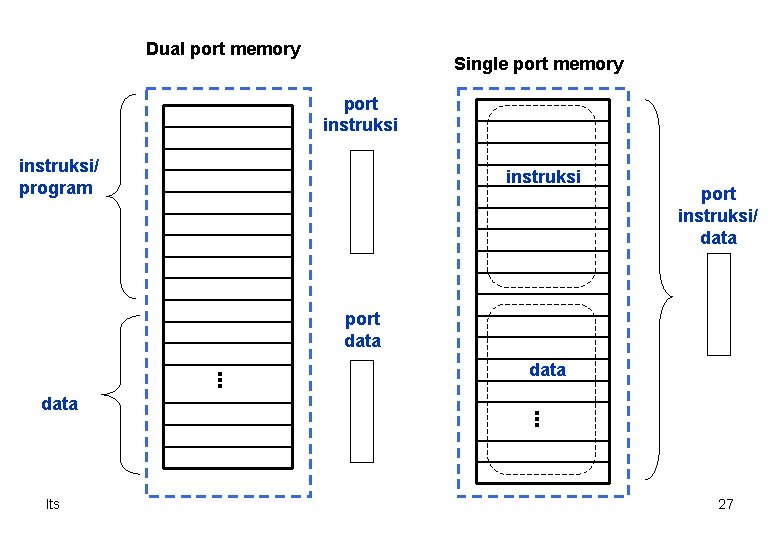

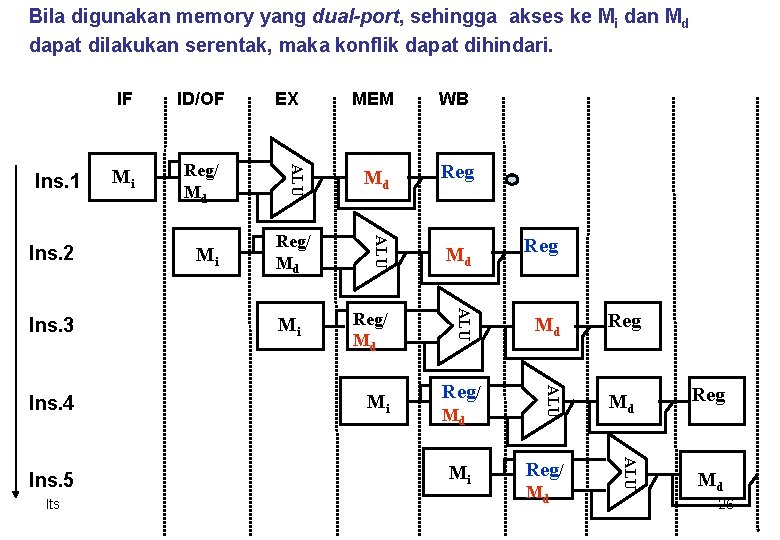

Bila digunakan memory yang dual-port, sehingga akses ke Mi dan Md dapat dilakukan serentak, maka konflik dapat dihindari. lts Md Reg/ Md Mi Mi Reg/ Md Mi Reg Md Reg/ ALU Ins. 5 Mi EX ALU Ins. 4 Reg/ Md WB ALU Ins. 3 Mi MEM ALU Ins. 2 ID/OF ALU Ins. 1 IF Md Reg Md 26

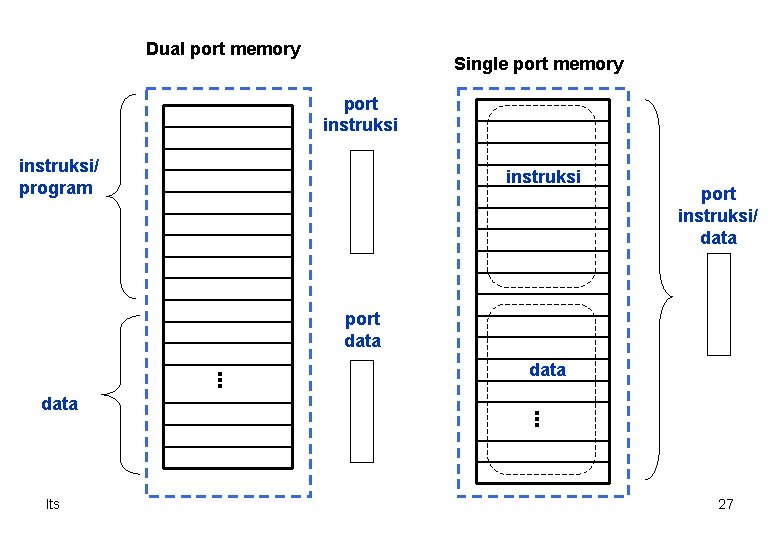

Dual port memory Single port memory port instruksi/ program instruksi port instruksi/ data port data lts 27

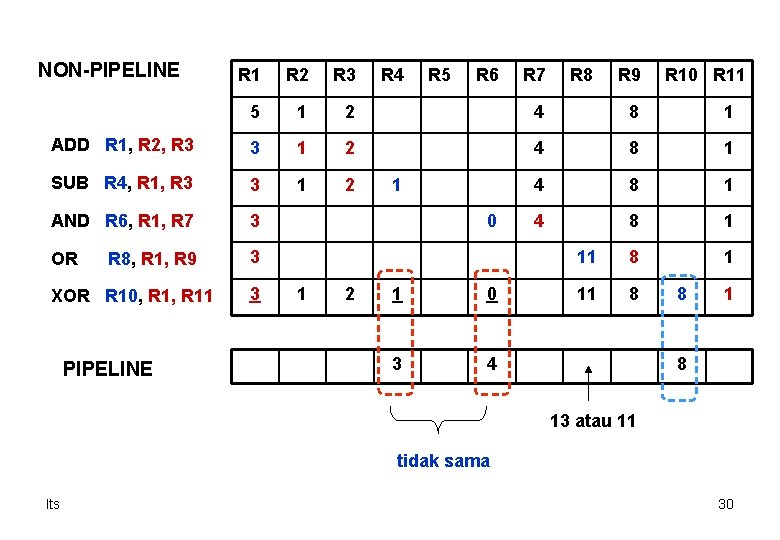

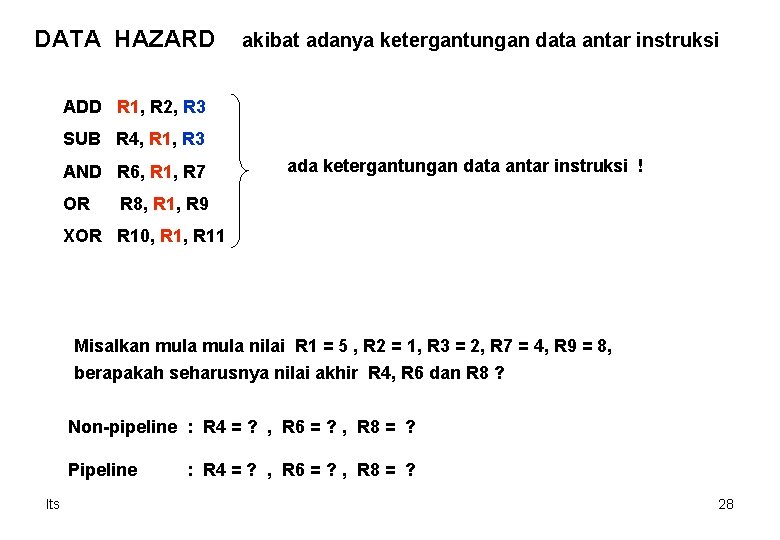

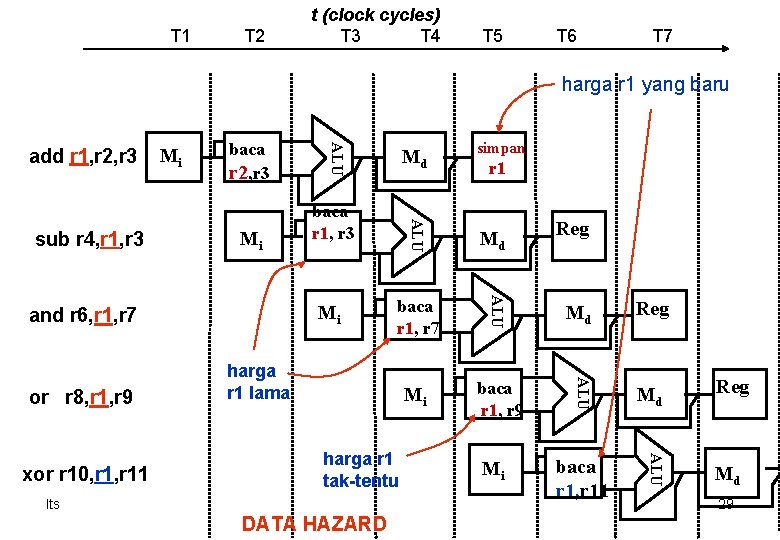

DATA HAZARD akibat adanya ketergantungan data antar instruksi ADD R 1, R 2, R 3 SUB R 4, R 1, R 3 AND R 6, R 1, R 7 OR ada ketergantungan data antar instruksi ! R 8, R 1, R 9 XOR R 10, R 11 Misalkan mula nilai R 1 = 5 , R 2 = 1, R 3 = 2, R 7 = 4, R 9 = 8, berapakah seharusnya nilai akhir R 4, R 6 dan R 8 ? Non-pipeline : R 4 = ? , R 6 = ? , R 8 = ? Pipeline lts : R 4 = ? , R 6 = ? , R 8 = ? 28

T 1 T 2 t (clock cycles) T 3 T 4 T 5 T 6 T 7 harga r 1 yang baru baca r 2, r 3 Mi Md baca r 1, r 7 Mi harga r 1 lama DATA HAZARD Reg Md Reg baca r 1, r 9 Md Mi baca r 1, r 11 ALU harga r 1 tak-tentu lts r 1 ALU xor r 10, r 11 simpan ALU or r 8, r 1, r 9 baca r 1, r 3 Mi and r 6, r 1, r 7 Md ALU sub r 4, r 1, r 3 Mi ALU add r 1, r 2, r 3 Reg Md 29

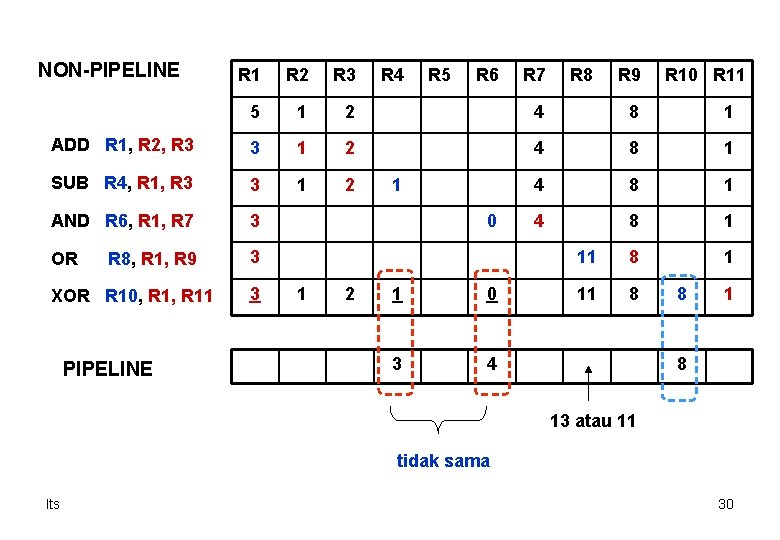

NON-PIPELINE R 1 R 2 R 3 5 1 2 4 8 1 ADD R 1, R 2, R 3 3 1 2 4 8 1 SUB R 4, R 1, R 3 3 1 2 4 8 1 AND R 6, R 1, R 7 3 4 8 1 OR 3 11 8 1 11 8 R 8, R 1, R 9 XOR R 10, R 11 PIPELINE 3 R 4 R 5 R 6 1 0 1 2 1 0 3 4 R 7 R 8 R 9 R 10 R 11 8 13 atau 11 tidak sama lts 30

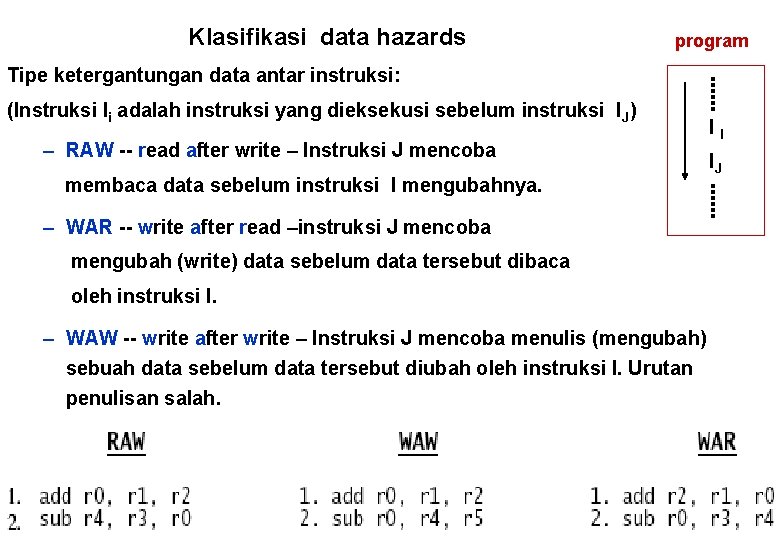

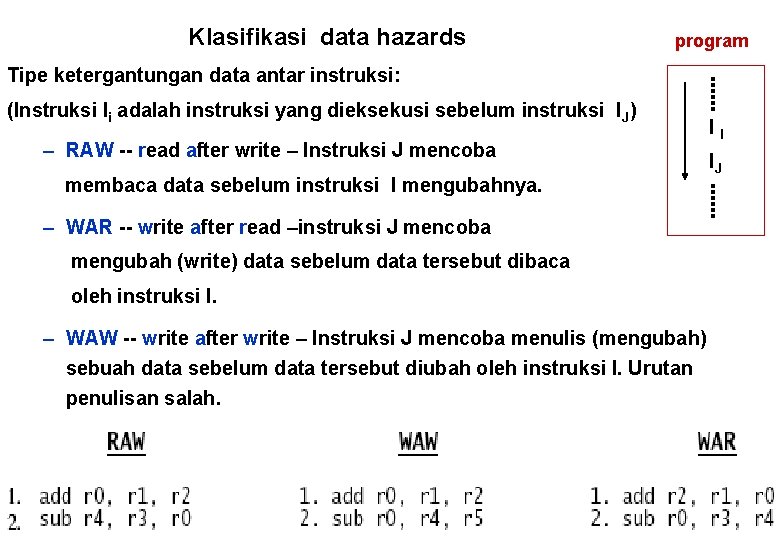

Klasifikasi data hazards program Tipe ketergantungan data antar instruksi: (Instruksi Ii adalah instruksi yang dieksekusi sebelum instruksi IJ) – RAW -- read after write – Instruksi J mencoba membaca data sebelum instruksi I mengubahnya. II IJ – WAR -- write after read –instruksi J mencoba mengubah (write) data sebelum data tersebut dibaca oleh instruksi I. – WAW -- write after write – Instruksi J mencoba menulis (mengubah) sebuah data sebelum data tersebut diubah oleh instruksi I. Urutan penulisan salah. lts 31

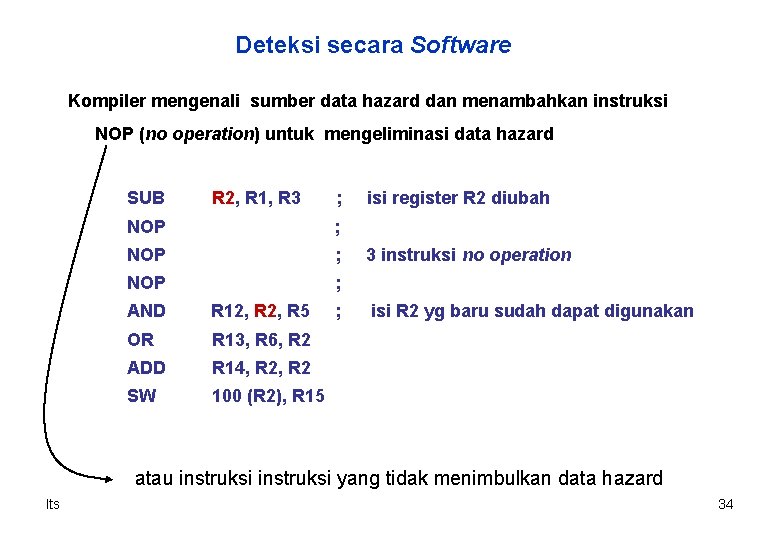

Deteksi sumber data hazard lts LD DADD DSUB OR AND R 1, 45(R 2) R 5, R 6, R 1 R 8, R 6, R 7 R 7, R 5, R 8 R 7, R 1, R 5 LD DADD DSUB OR AND R 1, 45(R 2) R 5, R 6, R 7 R 8, R 1, R 7, R 5, R 8 R 7, R 1, R 5 LD DADD DSUB OR AND R 1, 45(R 2) R 5, R 6, R 1 R 8, R 6, R 7, R 5, R 8 R 7, R 1, R 5 write R 1 read R 1 write R 8 read R 6 RAW RAR* read R 5 read R 7 write R 7 WAR WAW write R 7 32

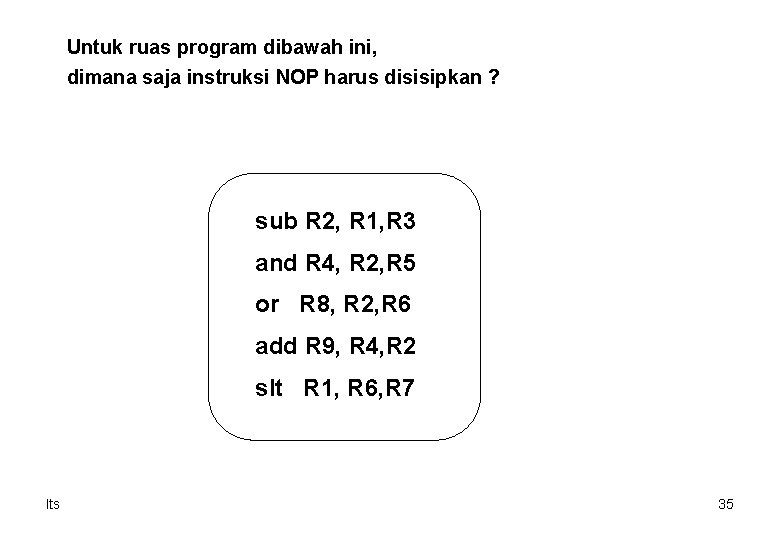

Contoh : Untuk format instruksi opcode Tipe Data Hazard operand-tujuan , operand-sumber 1 , operand-sumber 2 Contoh R 1, 45(R 2) R 5, R 6, R 1 Deteksi RAW Ii : LD Ii+1 : DADD RAR Ii : DADD R 5, R 6, R 1 Ii+1 : DSUB R 8, R 6, R 7 operand sumber pada instruksi Ii = operand sumber pada instruksi Ii+1 ? WAR Ii : DSUB Ii+1 : OR R 8, R 1, R 7, R 5, R 8 operand sumber pada instruksi Ii = operand tujuan pada instruksi Ii+1 ? WAW Ii : OR Ii+1 : AND R 7, R 5, R 8 R 7, R 1, R 5 operand tujuan pada instruksi Ii = operand tujuan pada instruksi Ii+1 ? operand tujuan pada instruksi Ii = operand sumber pada instruksi Ii+1 ? lts 33 Deteksi dapat dilakukan secara hardware maupun secara software (oleh compiler)

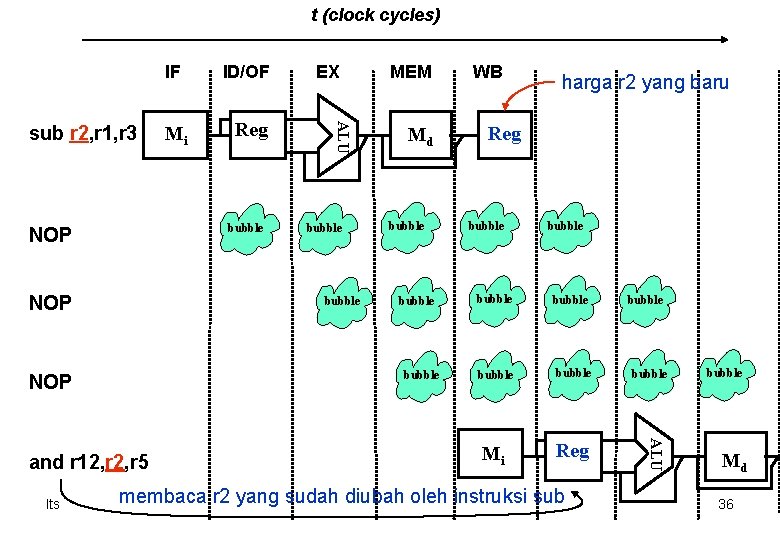

Deteksi secara Software Kompiler mengenali sumber data hazard dan menambahkan instruksi NOP (no operation) untuk mengeliminasi data hazard SUB R 2, R 1, R 3 ; NOP ; AND R 12, R 5 OR R 13, R 6, R 2 ADD R 14, R 2 SW 100 (R 2), R 15 ; isi register R 2 diubah 3 instruksi no operation isi R 2 yg baru sudah dapat digunakan atau instruksi yang tidak menimbulkan data hazard lts 34

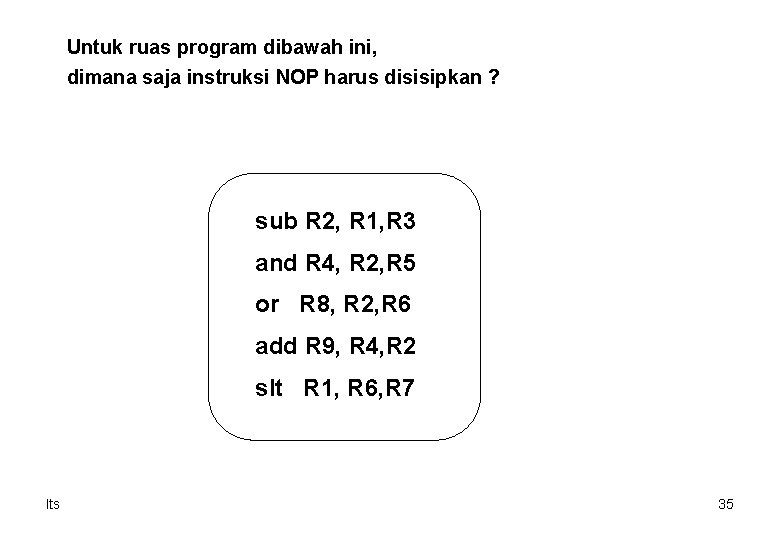

Untuk ruas program dibawah ini, dimana saja instruksi NOP harus disisipkan ? sub R 2, R 1, R 3 and R 4, R 2, R 5 or R 8, R 2, R 6 add R 9, R 4, R 2 slt R 1, R 6, R 7 lts 35

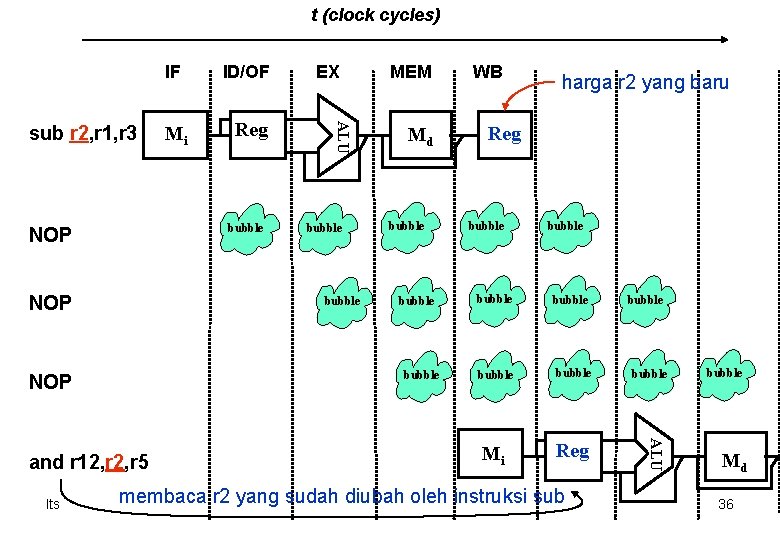

t (clock cycles) Mi Reg bubble NOP EX bubble MEM Md bubble and r 12, r 5 WB harga r 2 yang baru Reg bubble bubble Mi Reg ALU bubble NOP lts ID/OF ALU sub r 2, r 1, r 3 IF membaca r 2 yang sudah diubah oleh instruksi sub bubble Md 36

Disamping Data Hazard, kompiler juga dapat mendeteksi potensi terjadinya structural hazard, sehingga kompiler dapat menyisipkan instruksi NOP pada saat kompilasi. Apa kelemahan penyisipan instruksi NOP untuk mengatasi data-hazard atau Structural hazard ? ? lts 37

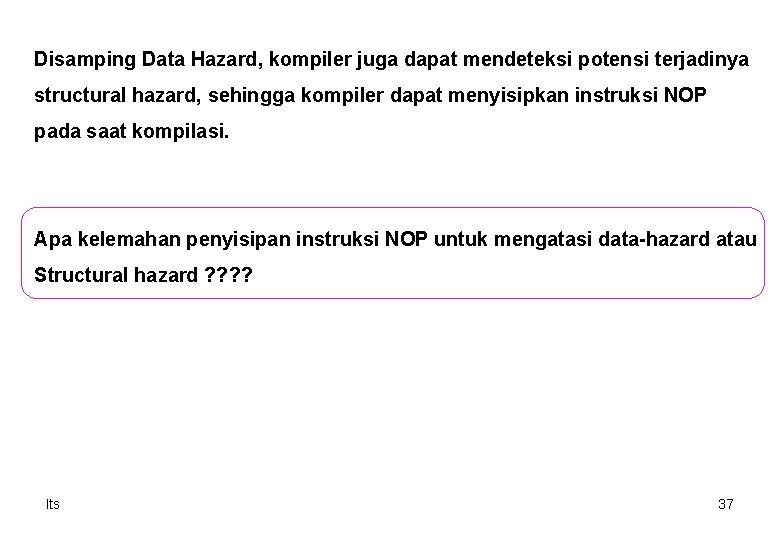

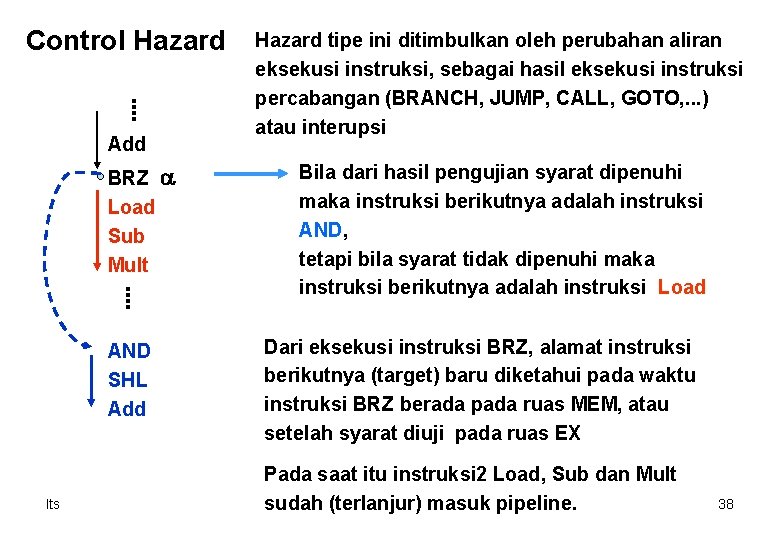

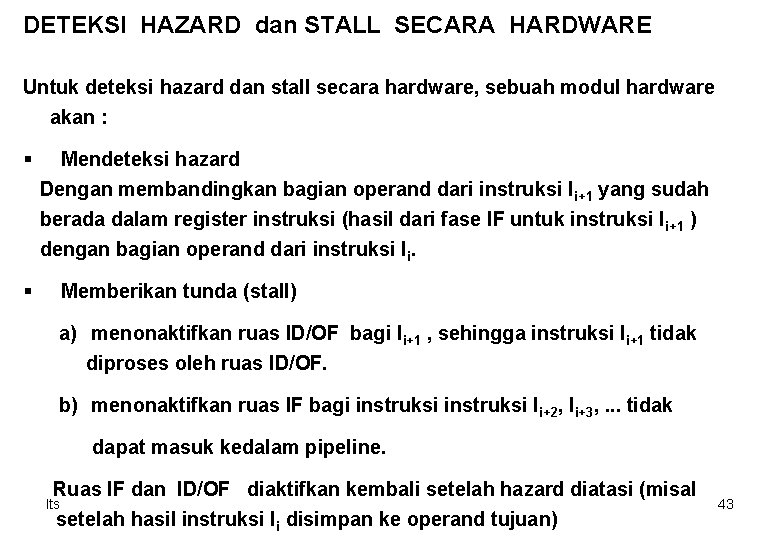

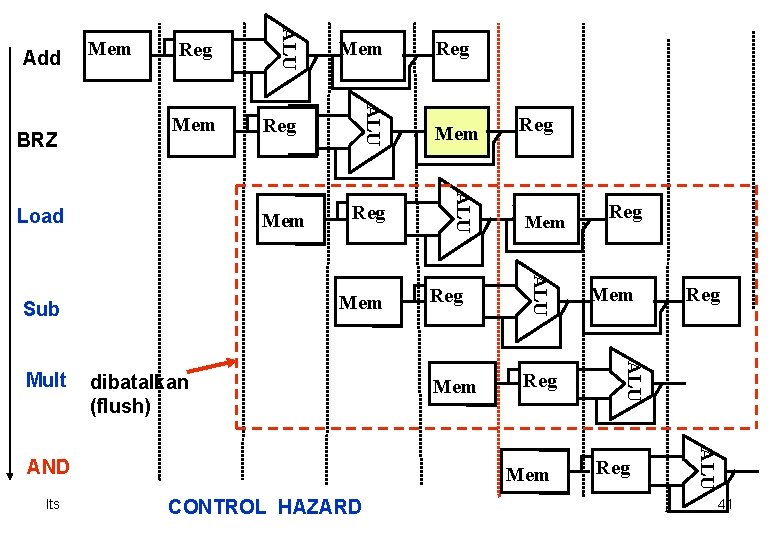

Control Hazard Add BRZ a Load Sub Mult AND SHL Add lts Hazard tipe ini ditimbulkan oleh perubahan aliran eksekusi instruksi, sebagai hasil eksekusi instruksi percabangan (BRANCH, JUMP, CALL, GOTO, . . . ) atau interupsi Bila dari hasil pengujian syarat dipenuhi maka instruksi berikutnya adalah instruksi AND, tetapi bila syarat tidak dipenuhi maka instruksi berikutnya adalah instruksi Load Dari eksekusi instruksi BRZ, alamat instruksi berikutnya (target) baru diketahui pada waktu instruksi BRZ berada pada ruas MEM, atau setelah syarat diuji pada ruas EX Pada saat itu instruksi 2 Load, Sub dan Mult sudah (terlanjur) masuk pipeline. 38

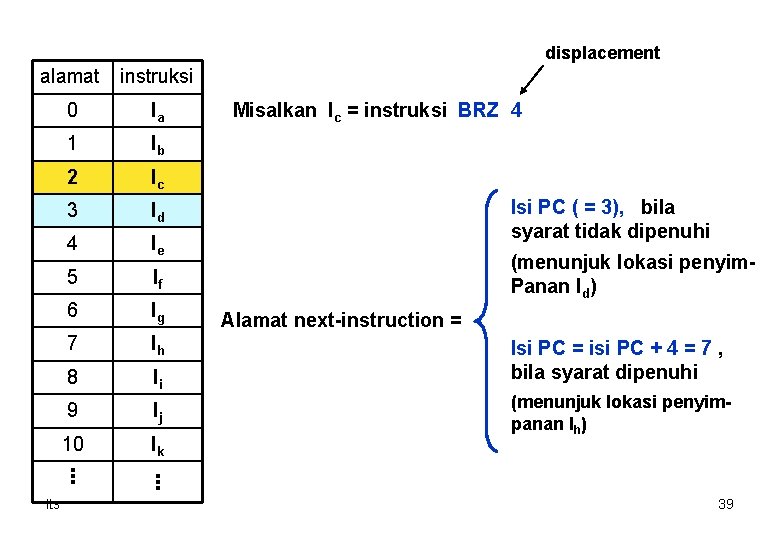

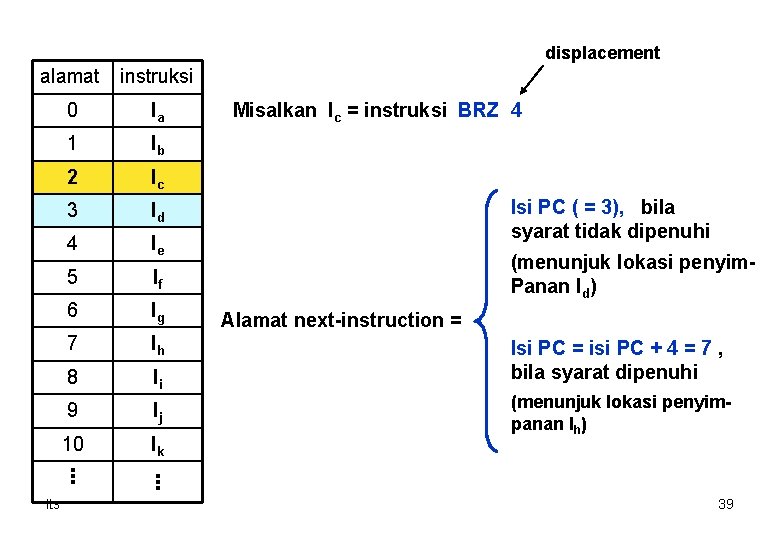

displacement alamat instruksi 0 Ia 1 Ib 2 Ic 3 Id 4 Ie 5 If 6 Ig 7 Ih 8 Ii 9 Ij 10 Ik lts Misalkan Ic = instruksi BRZ 4 Isi PC ( = 3), bila syarat tidak dipenuhi (menunjuk lokasi penyim. Panan Id) Alamat next-instruction = Isi PC = isi PC + 4 = 7 , bila syarat dipenuhi (menunjuk lokasi penyimpanan Ih) 39

![Eksekusi instruksi percabangan bersyarat misal BRZ a IF Instruction fetch IR IMemoryPC PC Eksekusi instruksi percabangan bersyarat misal BRZ a • IF: Instruction fetch IR IMemory[PC] PC](https://slidetodoc.com/presentation_image/3326753df685152aaaba20ba090b80fe/image-40.jpg)

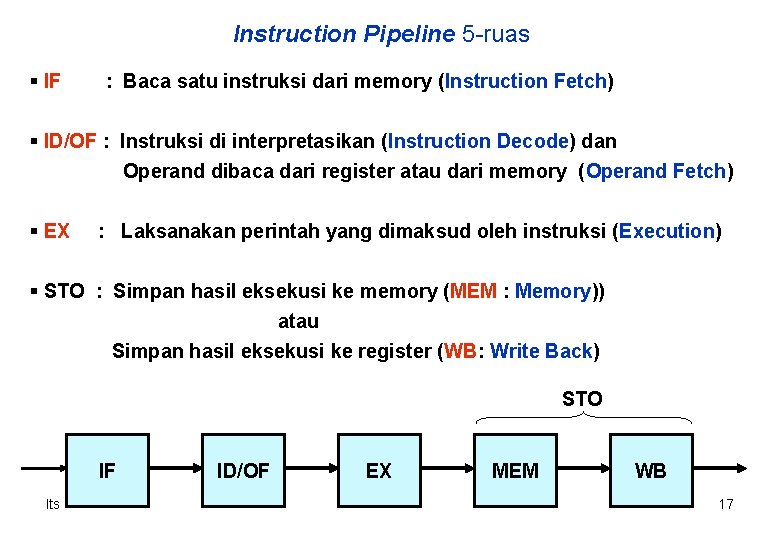

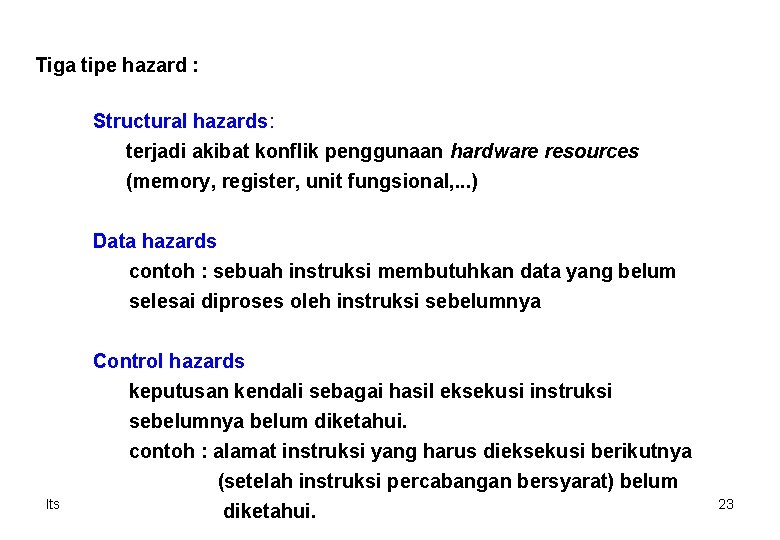

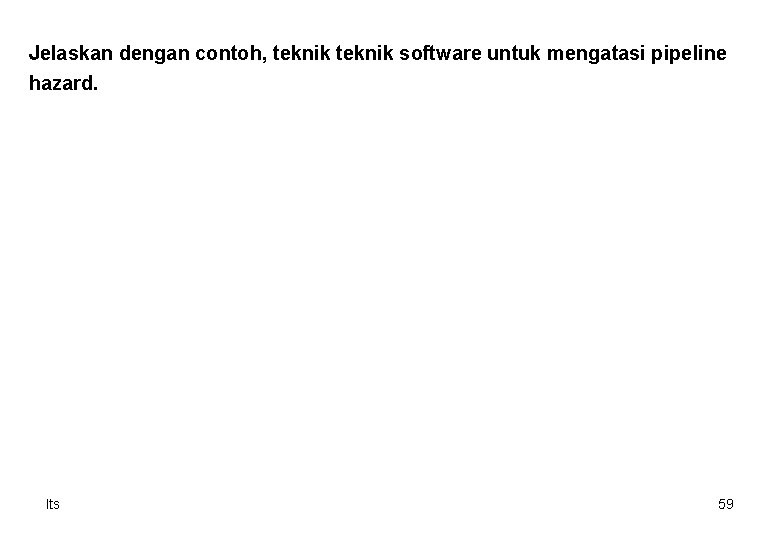

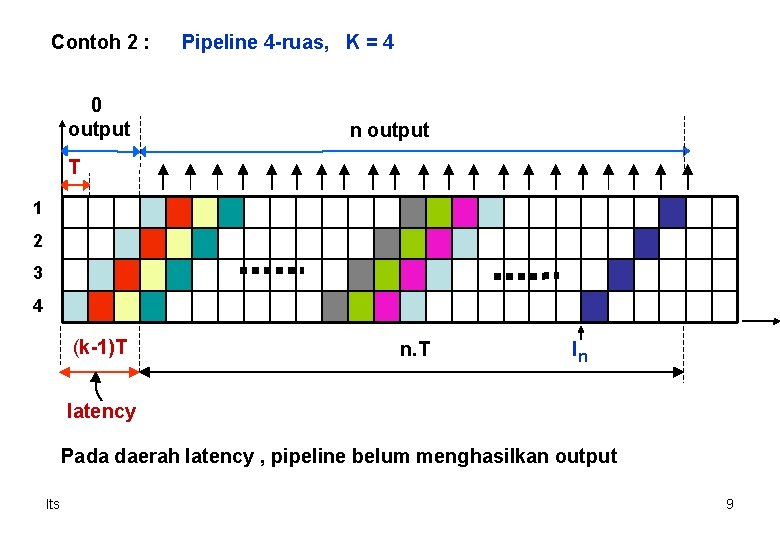

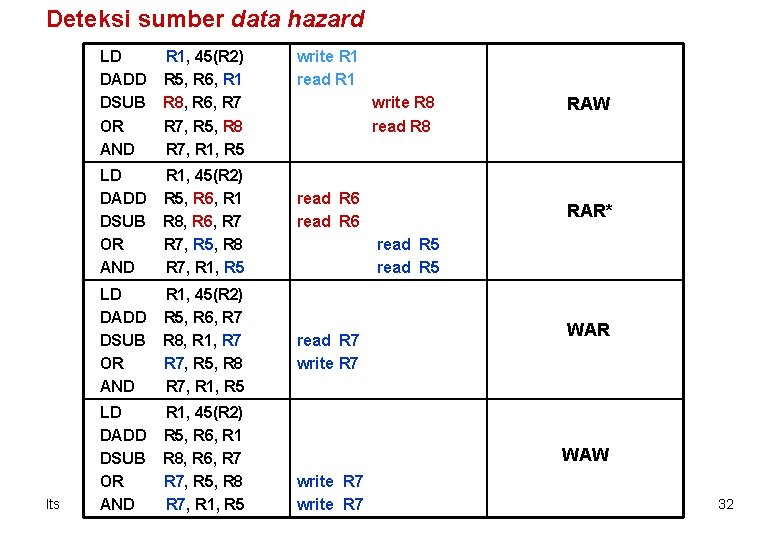

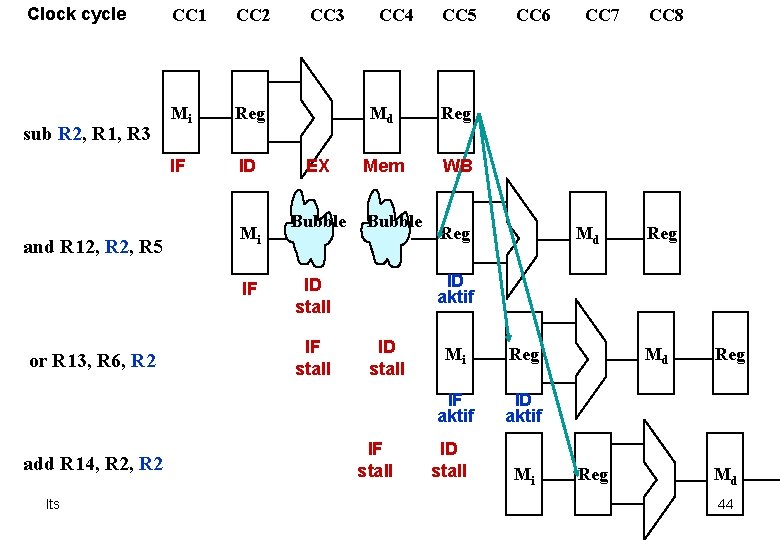

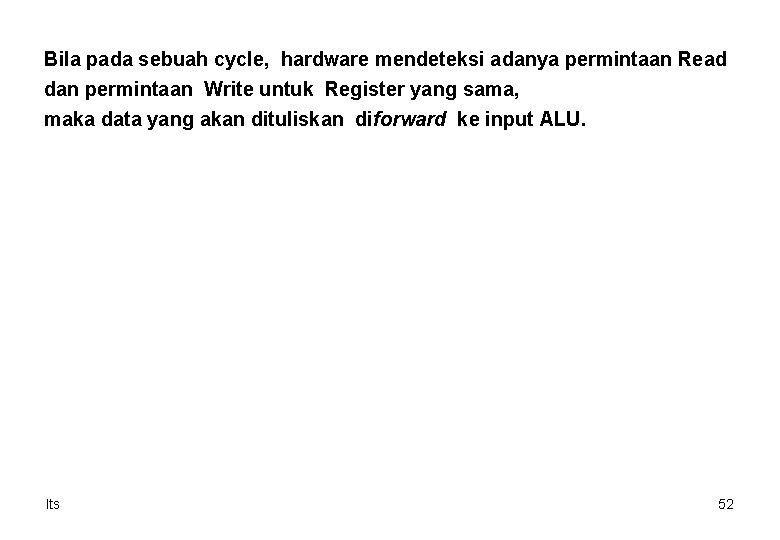

Eksekusi instruksi percabangan bersyarat misal BRZ a • IF: Instruction fetch IR IMemory[PC] PC incr. PC alamat next-instruction • ID: Instruction decode/operand-fetch nop tidak ada operand-fetch • Ex: Execute pengujian syarat apakah hasil ALU = 0 ? Target PC +displacement menghitung alamat target (alamat instruksi berikutnya) • MEM: Memory PC Target Bila syarat percabangan dipenuhi. Bila tidak dipenuhi mk digunakan isi PC hasil inrement pada fase IF • WB: Write back Tergantung hasil pengujian lts nop syarat pada fase EX 40

Reg Mem Mem Reg ALU BRZ Mem ALU Add Load dibatalkan (flush) lts Reg Mem CONTROL HAZARD Reg Mem Reg ALU AND Mem Mem ALU Mult Reg ALU Mem Sub Reg 41

Deteksi control hazard secara software oleh kompiler dapat dilakukan. Instruksi NOP akan disisipkan dibawah instruksi percabangan. Berapa jumlah instruksi NOP yang harus dididipkan dibawah intruksi percabangan bersyarat dan berapa untuk instruksi percabangan takbersyarat ? lts 42

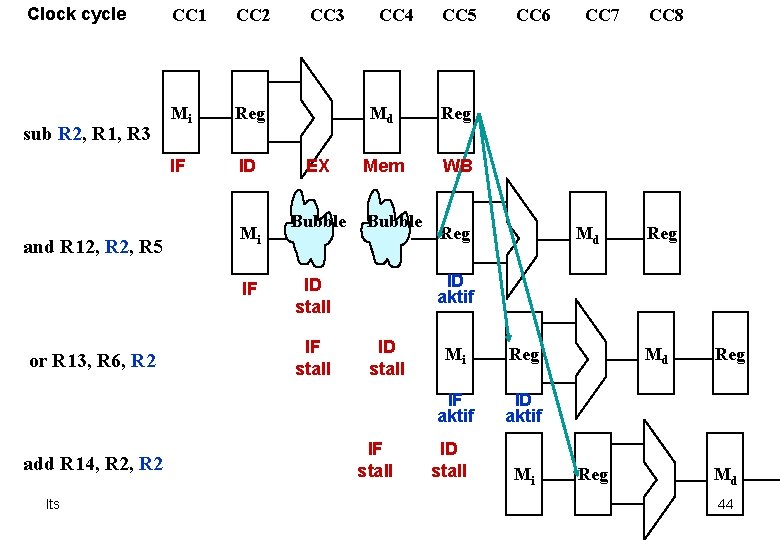

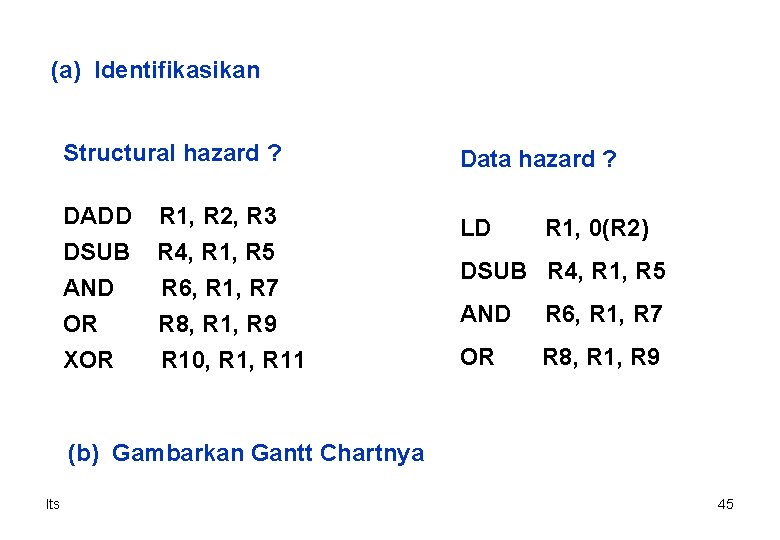

DETEKSI HAZARD dan STALL SECARA HARDWARE Untuk deteksi hazard dan stall secara hardware, sebuah modul hardware akan : § Mendeteksi hazard Dengan membandingkan bagian operand dari instruksi I i+1 yang sudah berada dalam register instruksi (hasil dari fase IF untuk instruksi I i+1 ) dengan bagian operand dari instruksi Ii. § Memberikan tunda (stall) a) menonaktifkan ruas ID/OF bagi Ii+1 , sehingga instruksi Ii+1 tidak diproses oleh ruas ID/OF. b) menonaktifkan ruas IF bagi instruksi Ii+2, Ii+3, . . . tidak dapat masuk kedalam pipeline. Ruas IF dan ID/OF diaktifkan kembali setelah hazard diatasi (misal lts setelah hasil instruksi Ii disimpan ke operand tujuan) 43

Clock cycle sub R 2, R 1, R 3 and R 12, R 5 CC 1 CC 2 Mi Reg IF ID Mi IF or R 13, R 6, R 2 add R 14, R 2 lts CC 3 EX Bubble CC 4 Md Reg Mem WB Bubble CC 6 Reg CC 7 Md CC 8 Reg ID aktif ID stall IF stall CC 5 ID stall IF stall Mi Reg IF aktif ID stall Mi Md Reg Md 44

(a) Identifikasikan Structural hazard ? Data hazard ? DADD DSUB AND OR XOR LD R 1, R 2, R 3 R 4, R 1, R 5 R 6, R 1, R 7 R 8, R 1, R 9 R 10, R 11 R 1, 0(R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 (b) Gambarkan Gantt Chartnya lts 45

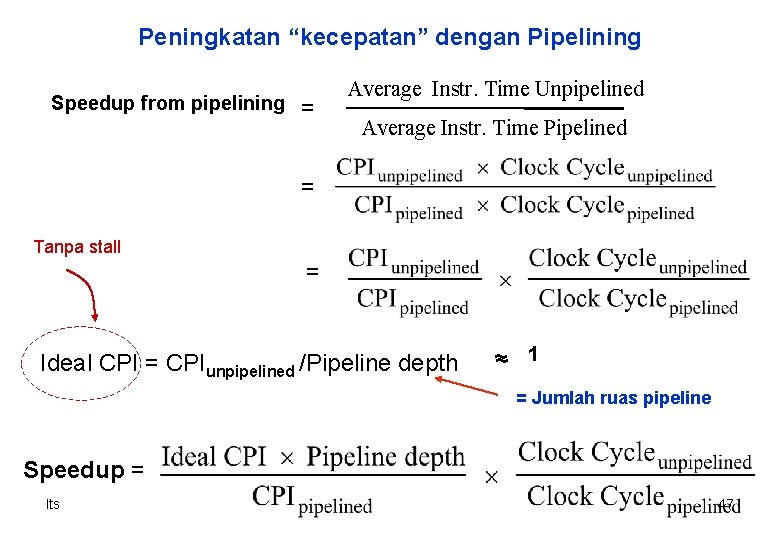

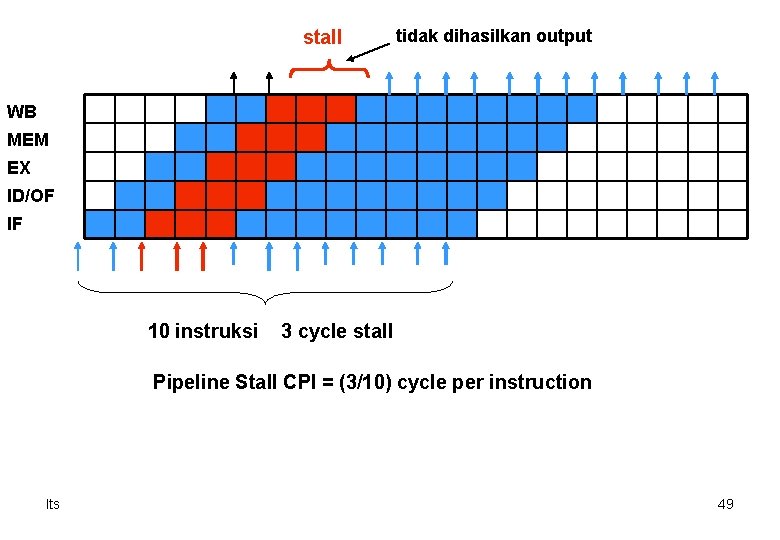

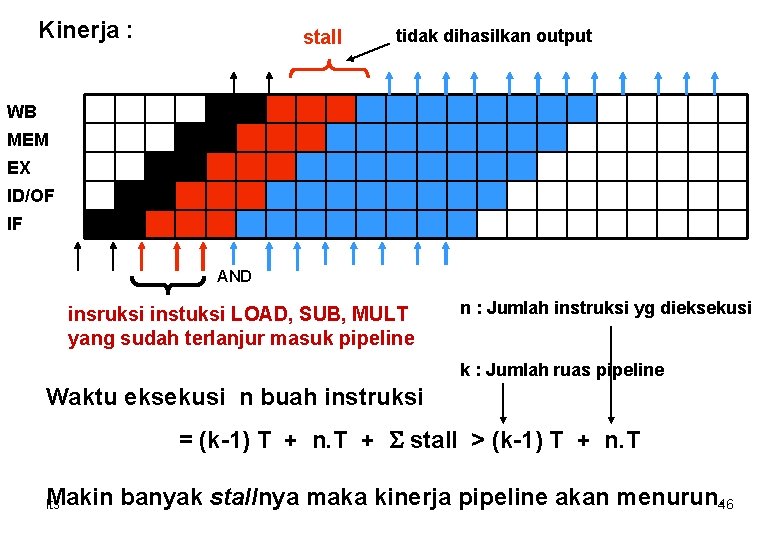

Kinerja : stall tidak dihasilkan output WB MEM EX ID/OF IF AND insruksi instuksi LOAD, SUB, MULT yang sudah terlanjur masuk pipeline n : Jumlah instruksi yg dieksekusi k : Jumlah ruas pipeline Waktu eksekusi n buah instruksi = (k-1) T + n. T + S stall > (k-1) T + n. T Makin banyak stallnya maka kinerja pipeline akan menurun. 46 lts

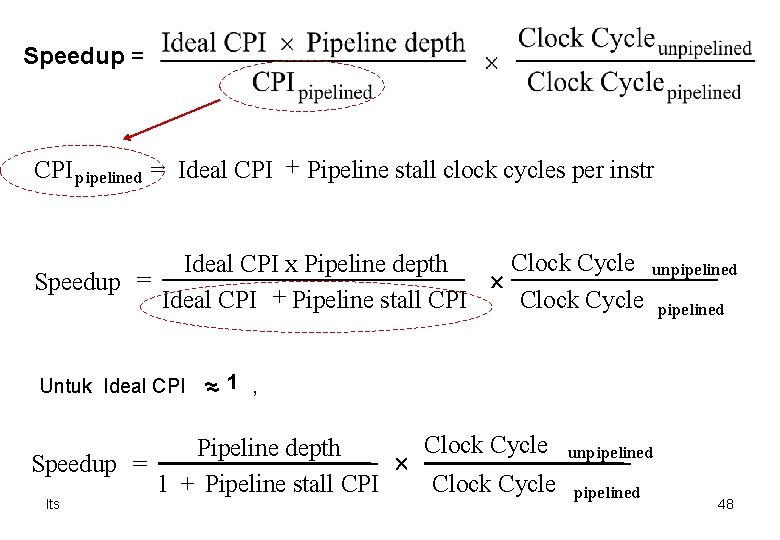

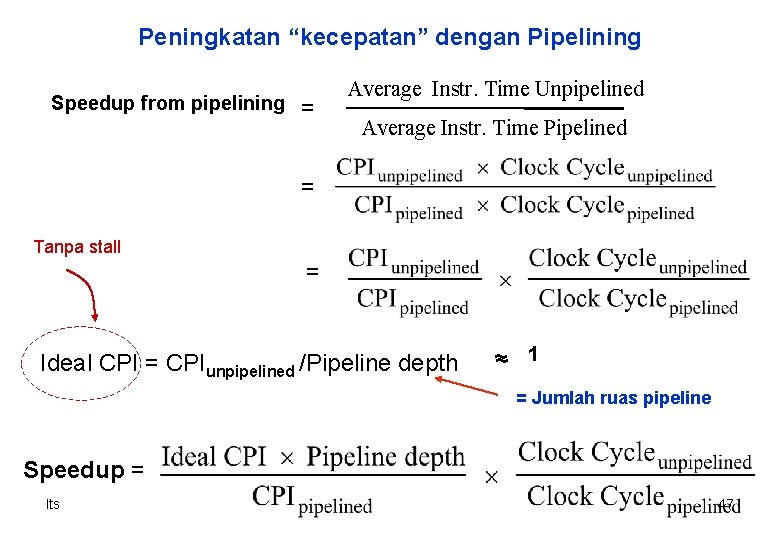

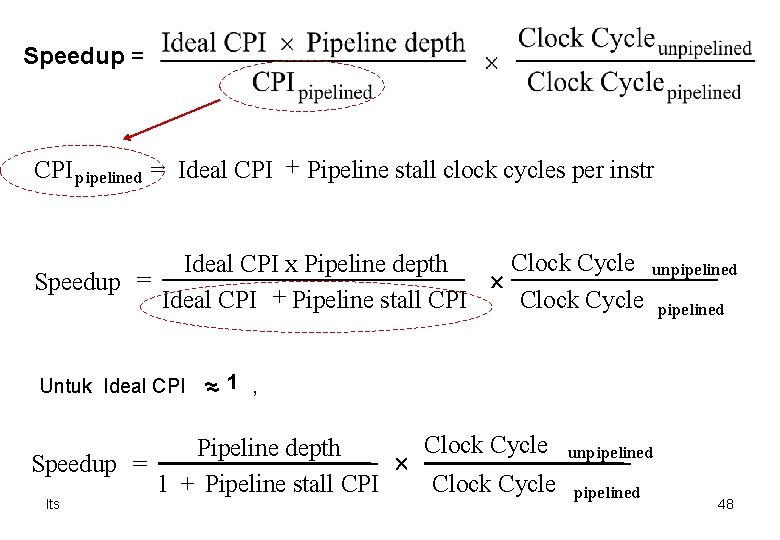

Peningkatan “kecepatan” dengan Pipelining Speedup from pipelining = Average Instr. Time Unpipelined Average Instr. Time Pipelined = Tanpa stall = Ideal CPI = CPIunpipelined /Pipeline depth ~ 1 = Jumlah ruas pipeline Speedup = lts 47

Speedup = CPI pipelined = Ideal CPI + Pipeline stall clock cycles per instr Clock Cycle Ideal CPI x Pipeline depth ´ Speedup = Ideal CPI + Pipeline stall CPI Clock Cycle Untuk Ideal CPI pipelined ~1 , Clock Cycle Pipeline depth ´ Speedup = 1 + Pipeline stall CPI Clock Cycle lts unpipelined 48

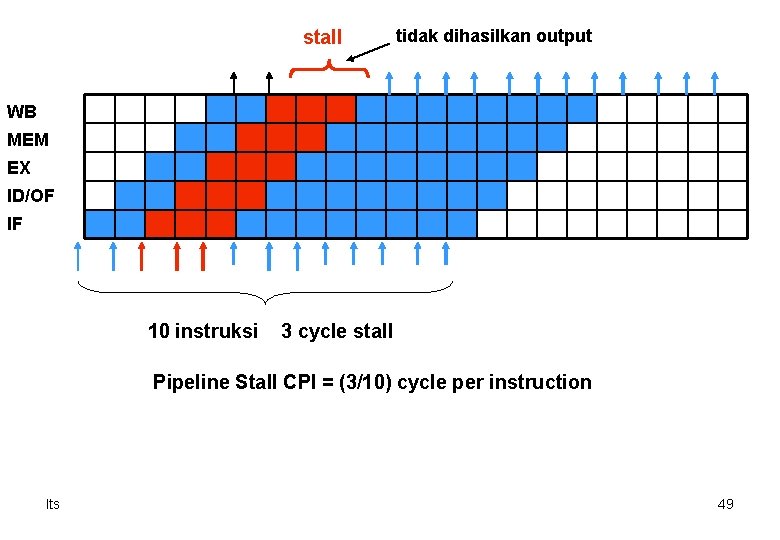

stall tidak dihasilkan output WB MEM EX ID/OF IF 10 instruksi 3 cycle stall Pipeline Stall CPI = (3/10) cycle per instruction lts 49

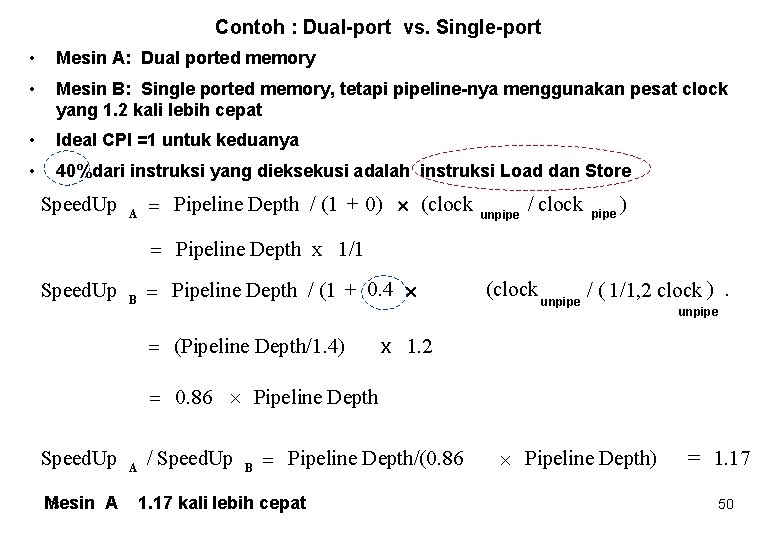

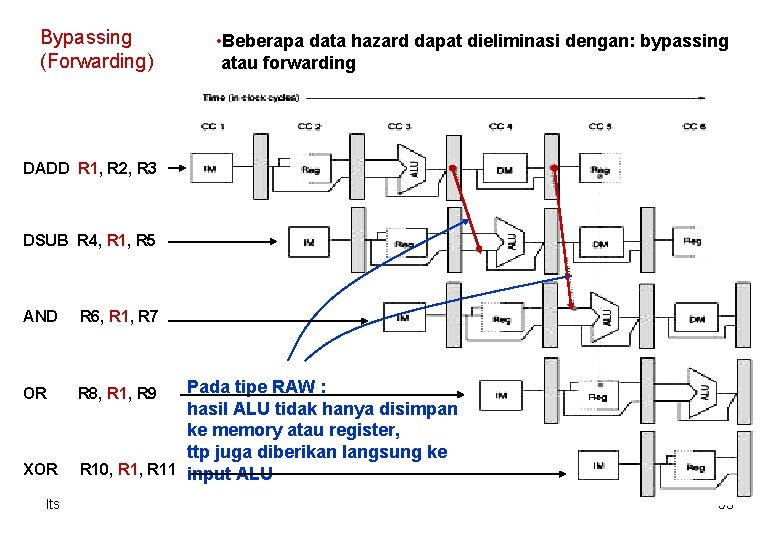

Contoh : Dual-port vs. Single-port • Mesin A: Dual ported memory • Mesin B: Single ported memory, tetapi pipeline-nya menggunakan pesat clock yang 1. 2 kali lebih cepat • Ideal CPI =1 untuk keduanya • 40%dari instruksi yang dieksekusi adalah instruksi Load dan Store Speed. Up A = Pipeline Depth / (1 + 0) ´ (clock unpipe / clock pipe ) = Pipeline Depth x 1/1 Speed. Up B = Pipeline Depth / (1 + 0. 4 ´ (clock unpipe / ( 1/1, 2 clock ). unpipe = (Pipeline Depth/1. 4) x 1. 2 = 0. 86 ´ Pipeline Depth Speed. Up lts Mesin A A / Speed. Up B = Pipeline Depth/(0. 86 1. 17 kali lebih cepat ´ Pipeline Depth) = 1. 17 50

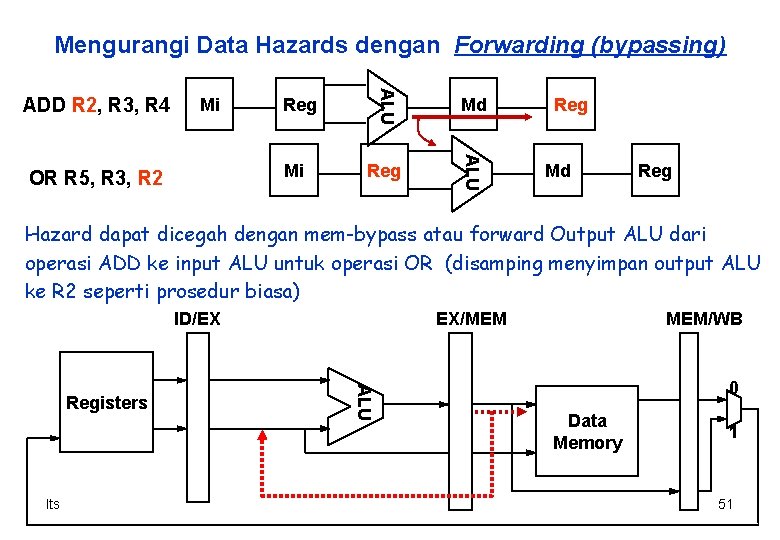

Mengurangi Data Hazards dengan Forwarding (bypassing) Reg Mi OR R 5, R 3, R 2 Md ALU Mi ALU ADD R 2, R 3, R 4 Reg Md Reg Hazard dapat dicegah dengan mem-bypass atau forward Output ALU dari operasi ADD ke input ALU untuk operasi OR (disamping menyimpan output ALU ke R 2 seperti prosedur biasa) ID/EX lts ALU Registers EX/MEM MEM/WB 0 Data Memory 1 51

Bila pada sebuah cycle, hardware mendeteksi adanya permintaan Read dan permintaan Write untuk Register yang sama, maka data yang akan dituliskan diforward ke input ALU. lts 52

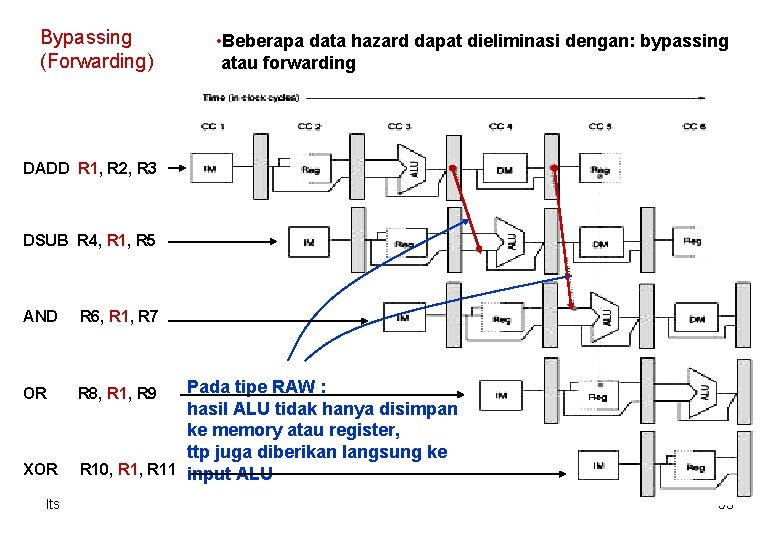

Bypassing (Forwarding) • Beberapa data hazard dapat dieliminasi dengan: bypassing atau forwarding DADD R 1, R 2, R 3 DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 XOR lts Pada tipe RAW : hasil ALU tidak hanya disimpan ke memory atau register, ttp juga diberikan langsung ke R 10, R 11 input ALU 53

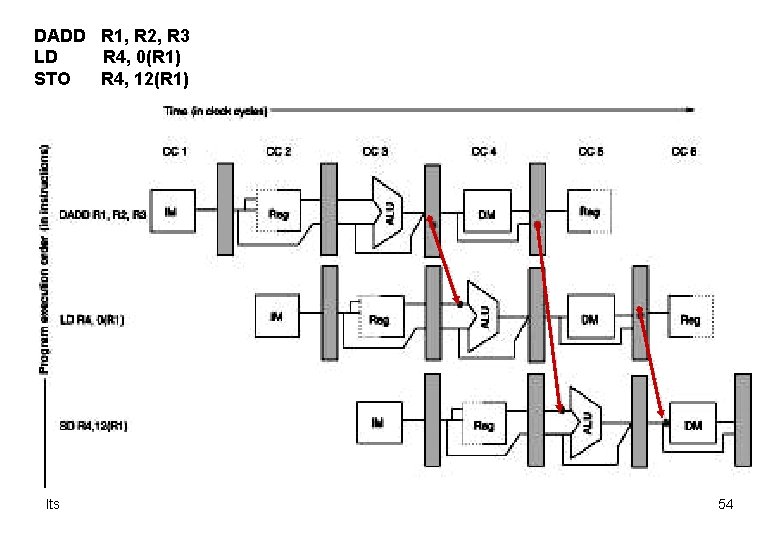

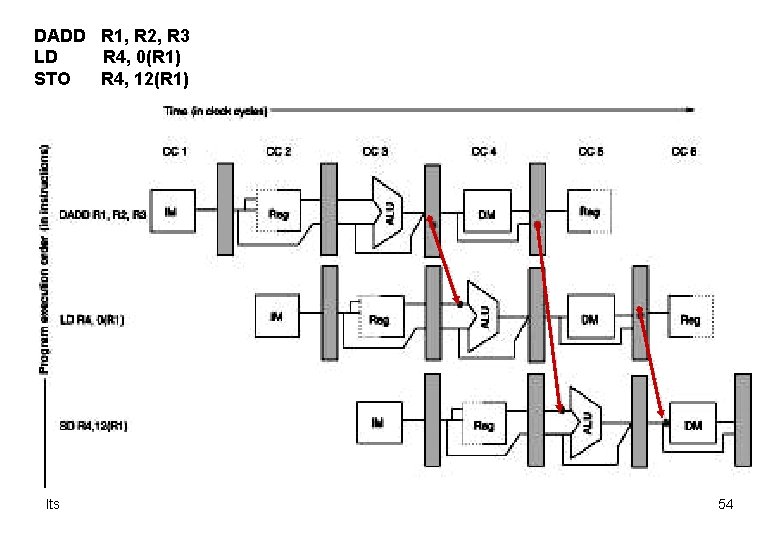

DADD R 1, R 2, R 3 LD R 4, 0(R 1) STO R 4, 12(R 1) lts 54

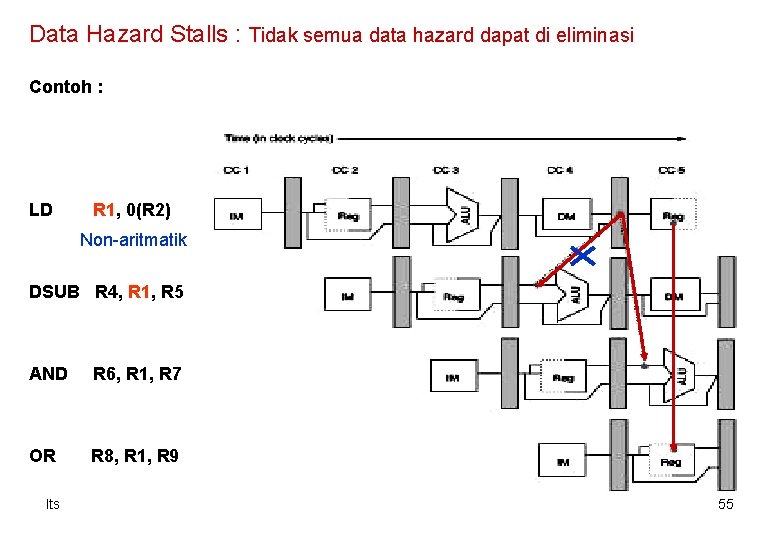

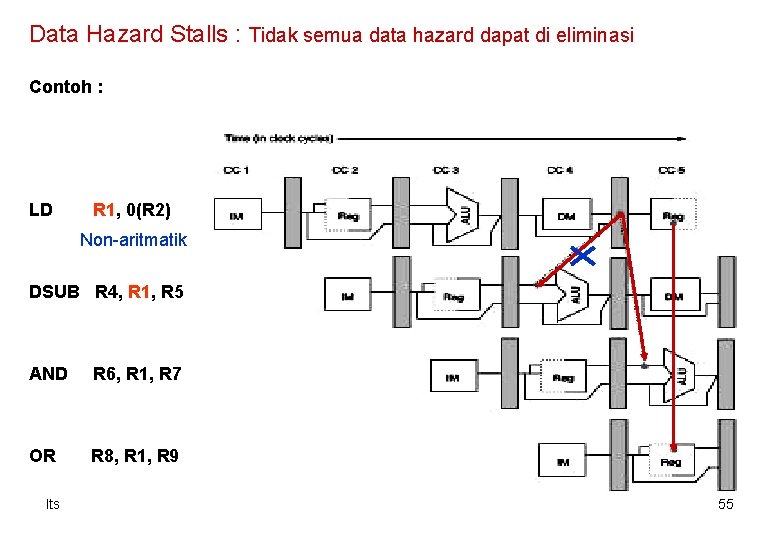

Data Hazard Stalls : Tidak semua data hazard dapat di eliminasi Contoh : LD R 1, 0(R 2) Non-aritmatik DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 lts 55

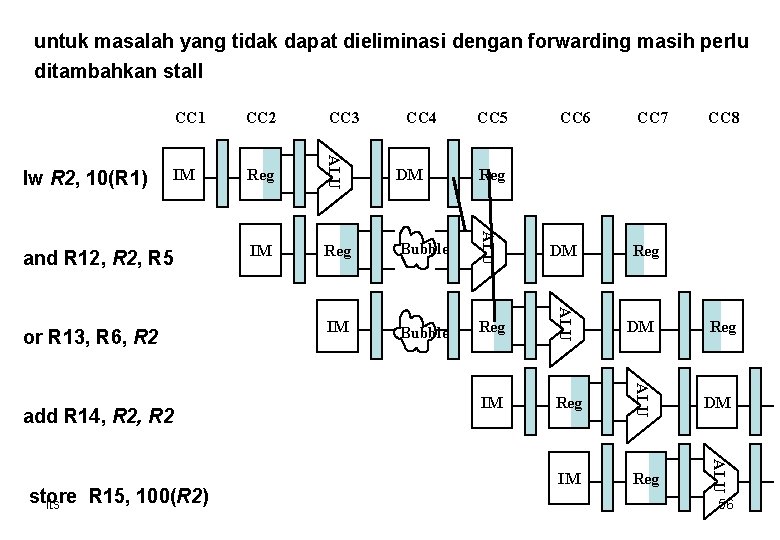

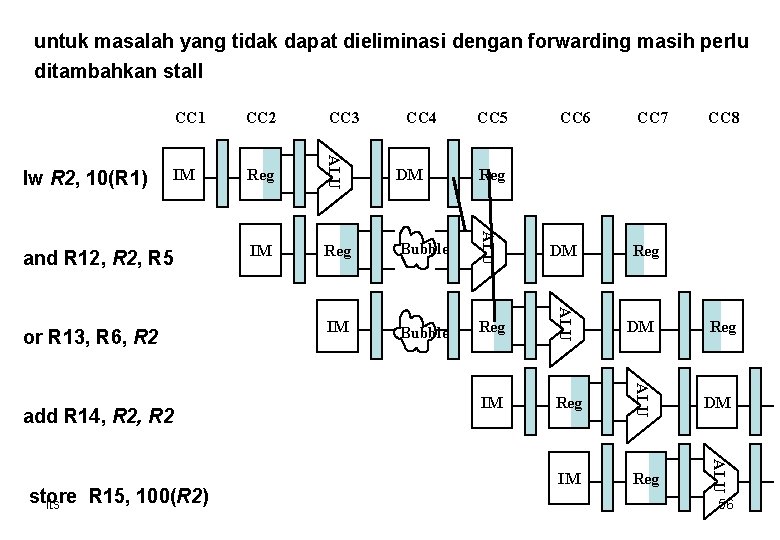

untuk masalah yang tidak dapat dieliminasi dengan forwarding masih perlu ditambahkan stall IM and R 12, R 5 or R 13, R 6, R 2 add R 14, R 2 store R 15, 100(R 2) lts CC 6 CC 7 CC 8 DM Reg Bubble DM IM Bubble Reg DM IM Reg ALU Reg CC 5 ALU IM CC 4 ALU CC 3 ALU CC 2 ALU lw R 2, 10(R 1) CC 1 Reg 56

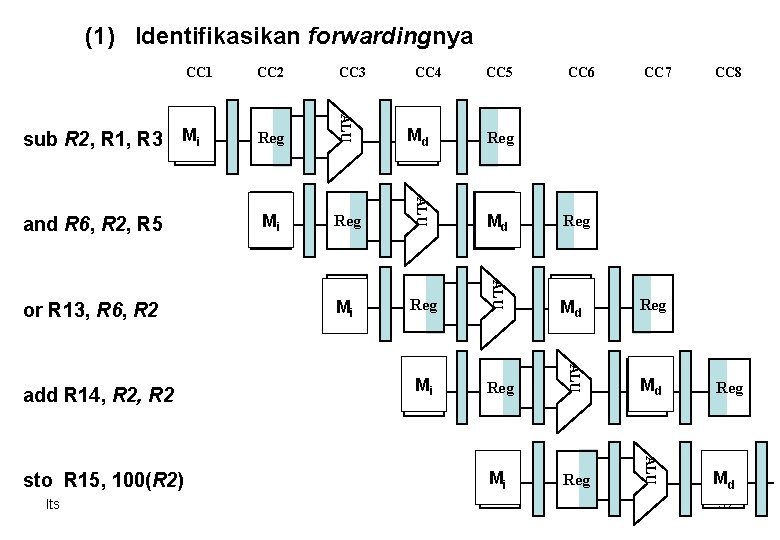

(1) Identifikasikan forwardingnya CC 2 CC 3 sub R 2, R 1, R 3 MMi Reg ALU M Md and R 6, R 2, R 5 Mi M Reg ALU IM M i Reg ALU DM M Mi IM Reg ALU Md DM M IMi Reg ALU CC 1 or R 13, R 6, R 2 add R 14, R 2 sto R 15, 100(R 2) lts CC 4 CC 5 CC 6 CC 7 CC 8 Reg Md Reg Reg Md DM 57

(2) Tunjukkan stalls dan forwarding untuk kode dibawah ini add R 3, R 2, R 1 load R 4, 100(R 3) and R 6, R 4, R 3 sub R 7, R 6, R 2 lts 58

Jelaskan dengan contoh, teknik software untuk mengatasi pipeline hazard. lts 59