Pipelining III Andreas Klappenecker CPSC 321 Computer Architecture

- Slides: 23

Pipelining III Andreas Klappenecker CPSC 321 Computer Architecture

Administrative Issues n Talk by Laszlo Kish n n Quantum Computing Seminar, Thursday 10: 00 am-11: 00 am, HRBB 302 Projects: Get started!!!

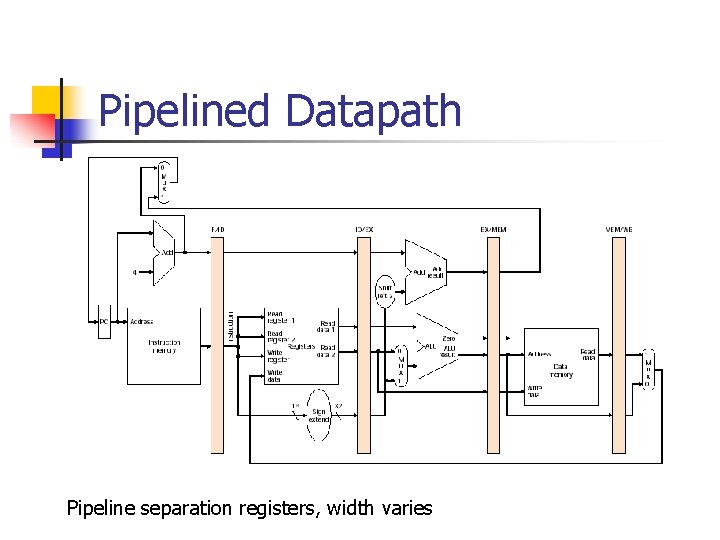

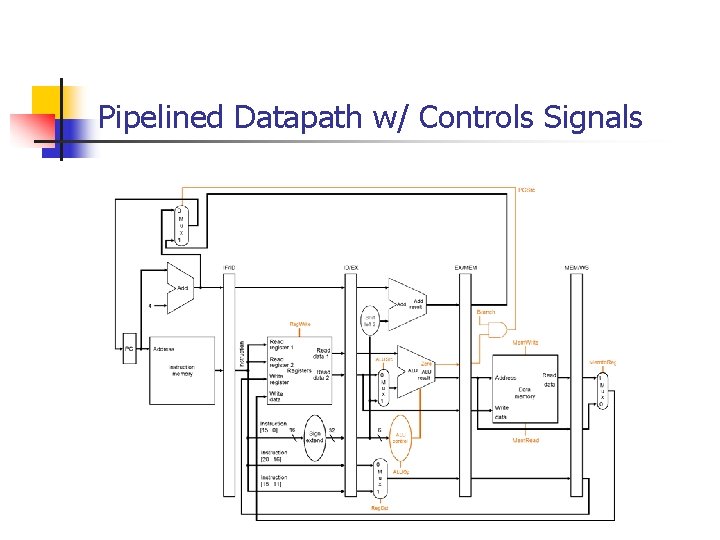

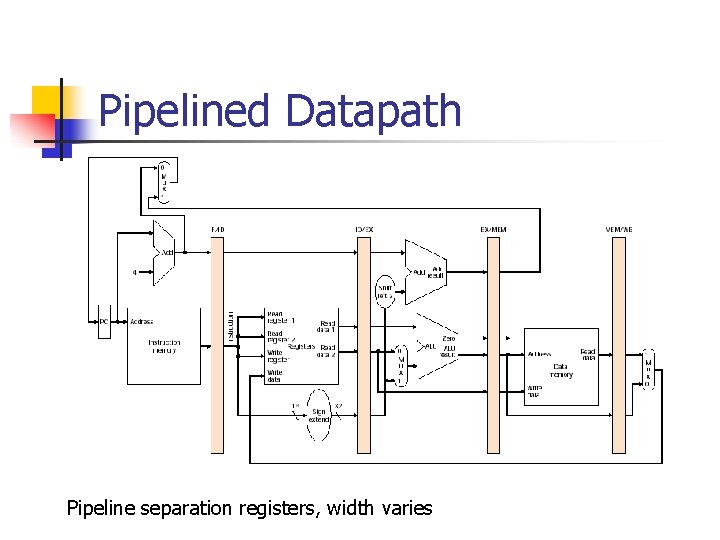

Pipelined Datapath Pipeline separation registers, width varies

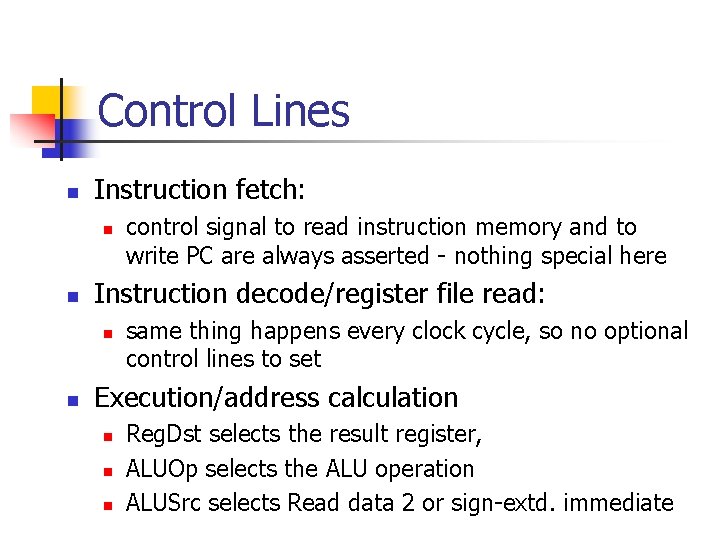

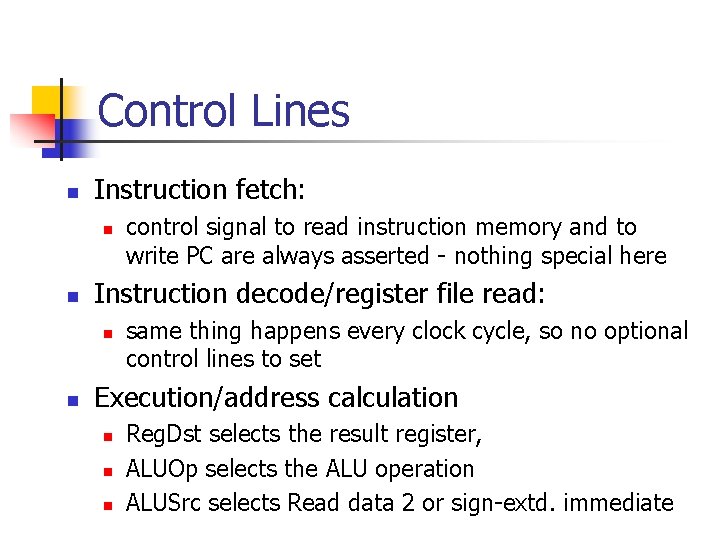

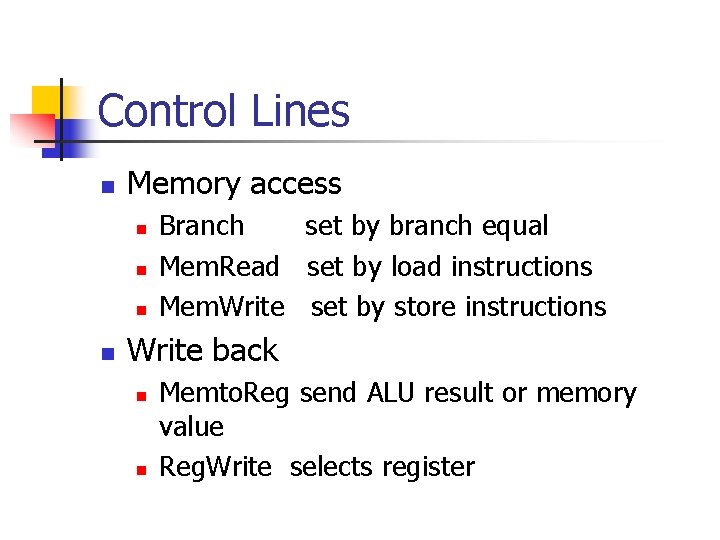

Control Lines n Instruction fetch: n n Instruction decode/register file read: n n control signal to read instruction memory and to write PC are always asserted - nothing special here same thing happens every clock cycle, so no optional control lines to set Execution/address calculation n Reg. Dst selects the result register, ALUOp selects the ALU operation ALUSrc selects Read data 2 or sign-extd. immediate

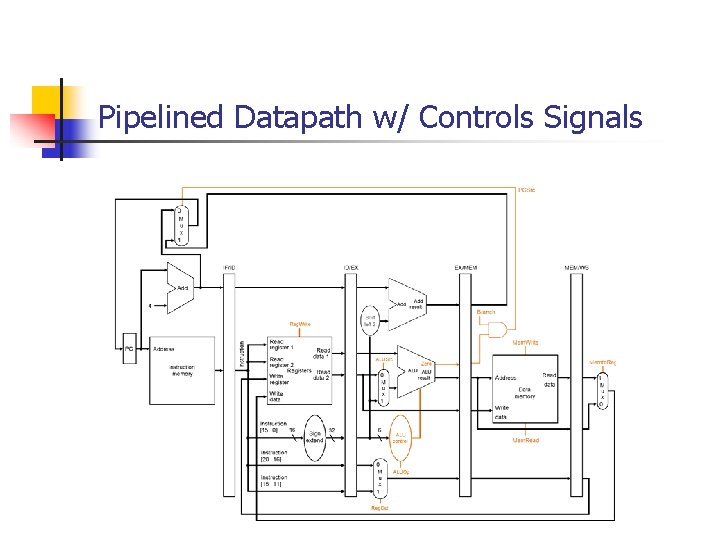

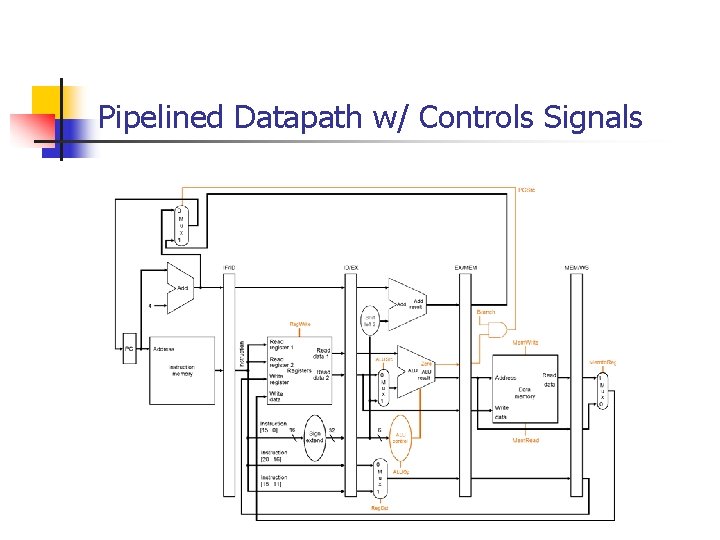

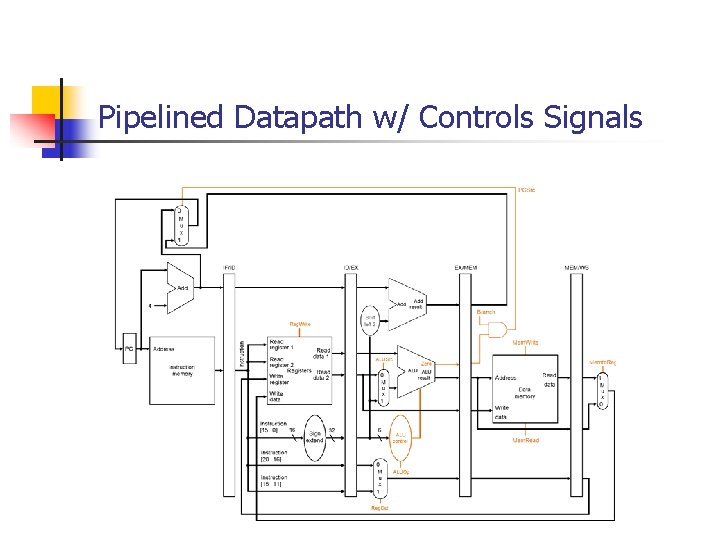

Pipelined Datapath w/ Controls Signals

Control Lines n Memory access n n Branch set by branch equal Mem. Read set by load instructions Mem. Write set by store instructions Write back n n Memto. Reg send ALU result or memory value Reg. Write selects register

Pipelined Datapath w/ Controls Signals

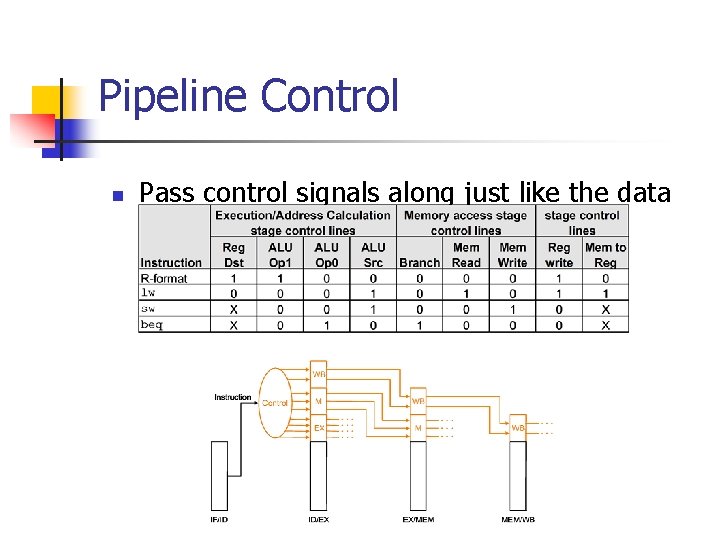

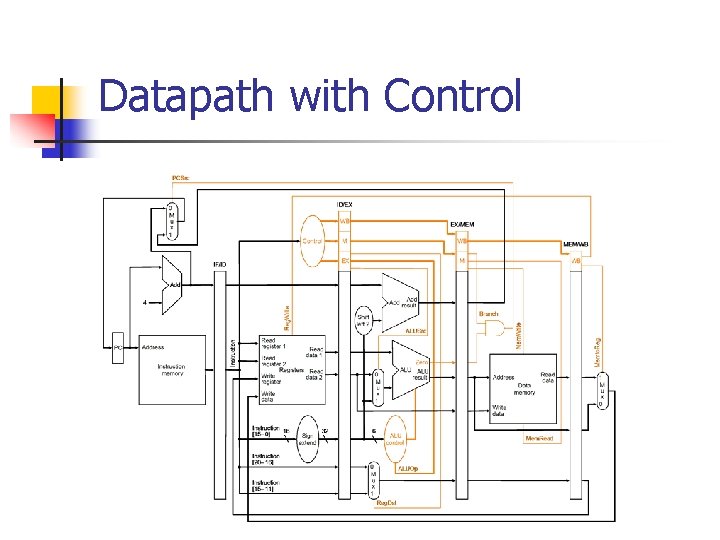

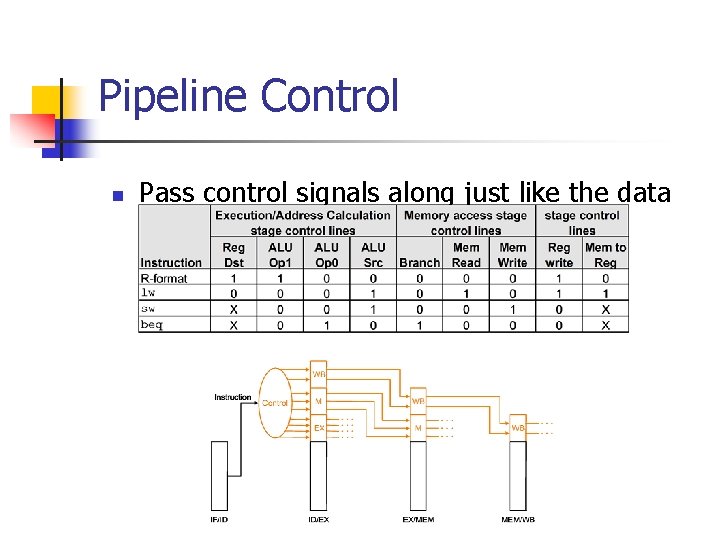

Pipeline Control n Pass control signals along just like the data

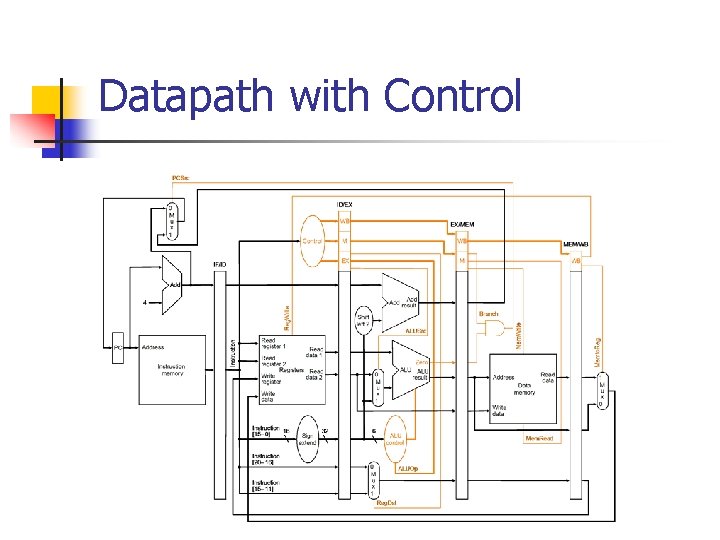

Datapath with Control

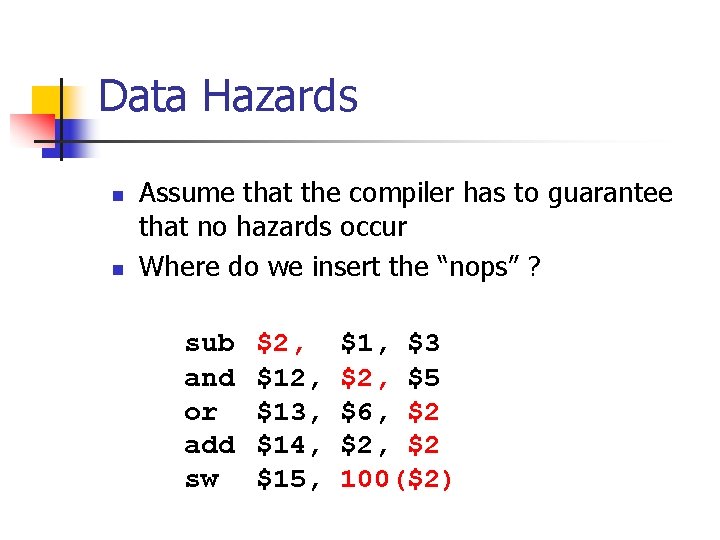

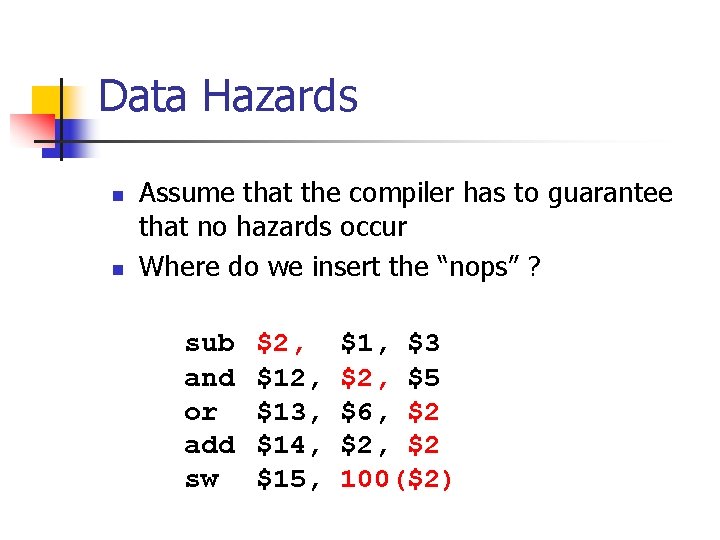

Data Hazards n n Assume that the compiler has to guarantee that no hazards occur Where do we insert the “nops” ? sub and or add sw $2, $13, $14, $15, $1, $3 $2, $5 $6, $2 $2, $2 100($2)

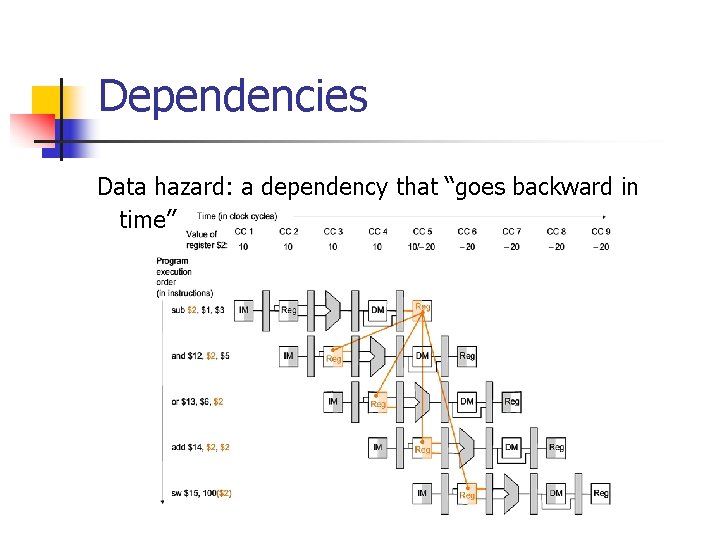

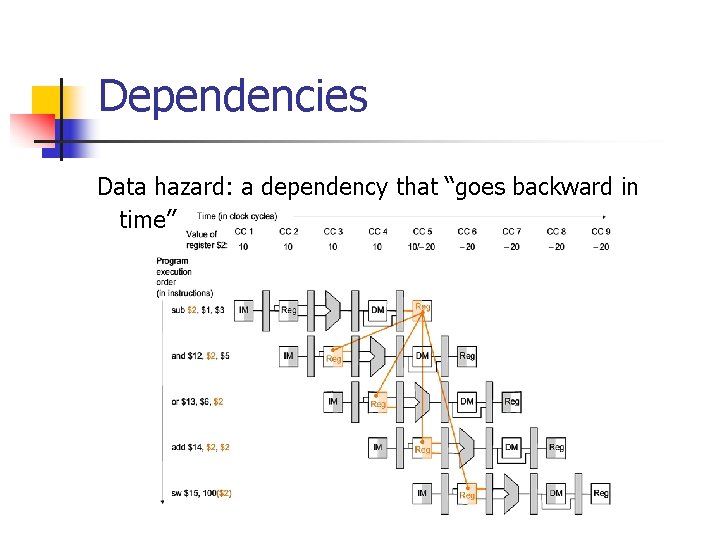

Dependencies Data hazard: a dependency that “goes backward in time”

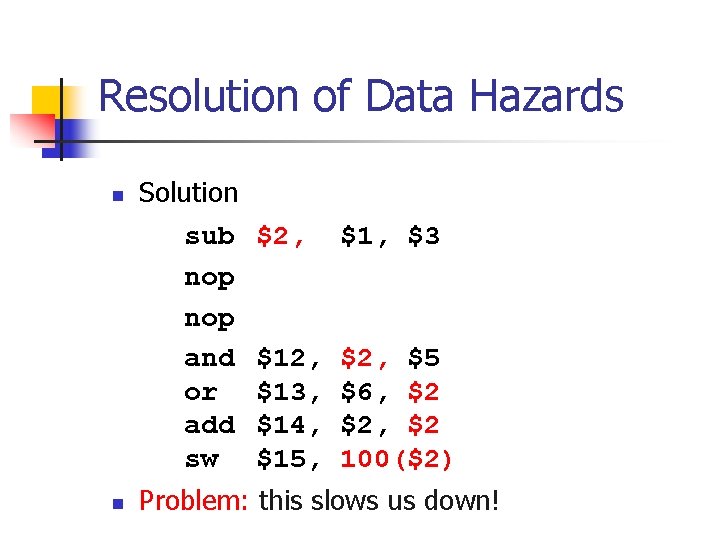

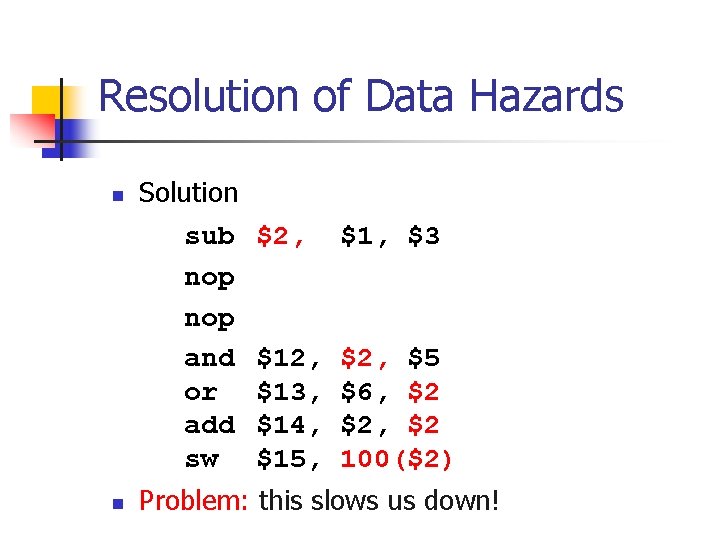

Resolution of Data Hazards n n Solution sub nop and or add sw $2, $1, $3 $12, $13, $14, $15, $2, $5 $6, $2 $2, $2 100($2) Problem: this slows us down!

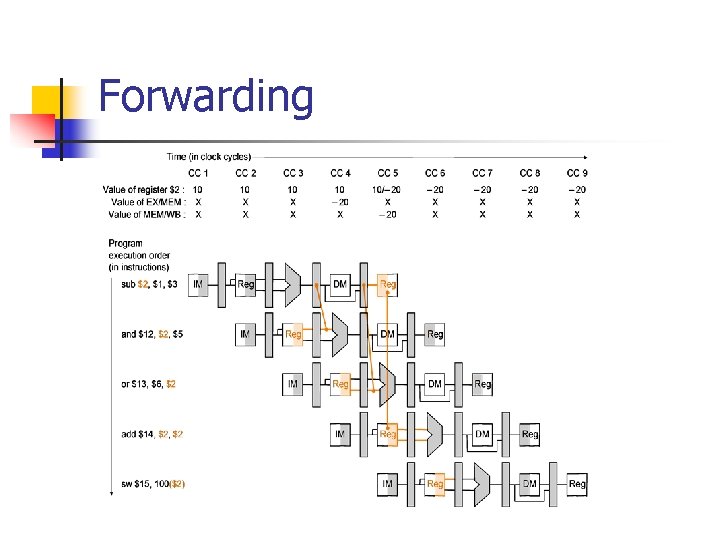

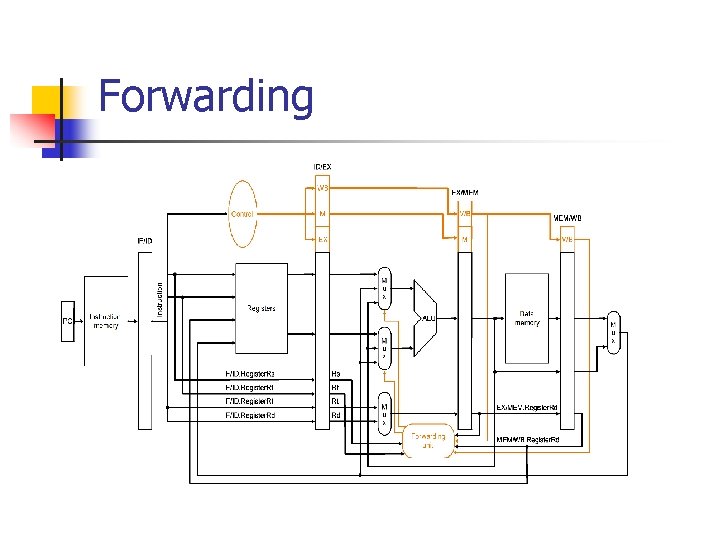

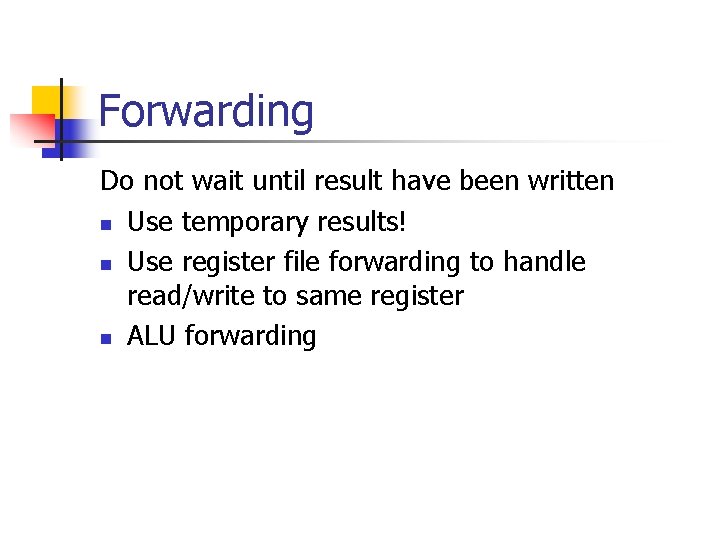

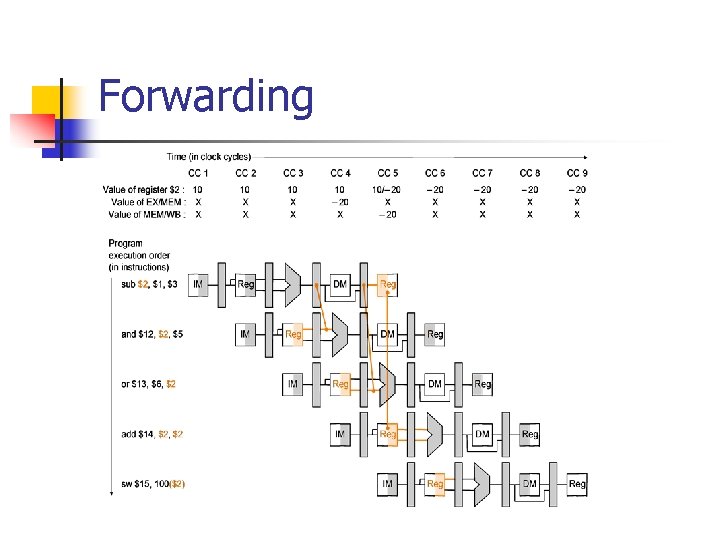

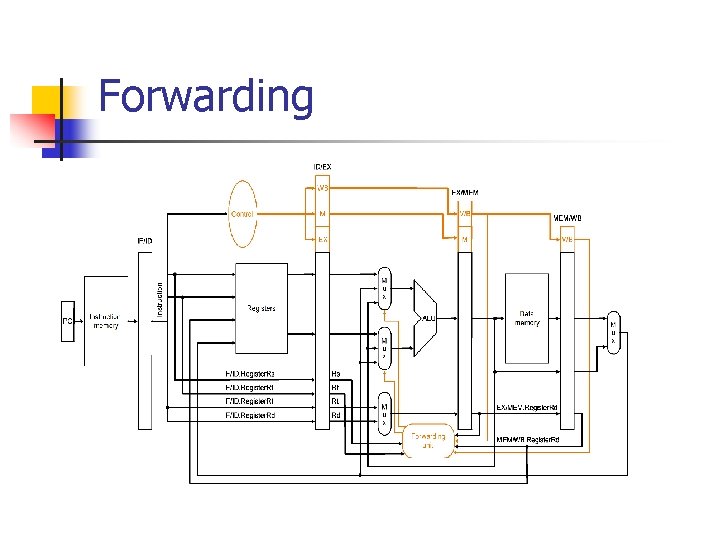

Forwarding Do not wait until result have been written n Use temporary results! n Use register file forwarding to handle read/write to same register n ALU forwarding

Forwarding

Forwarding

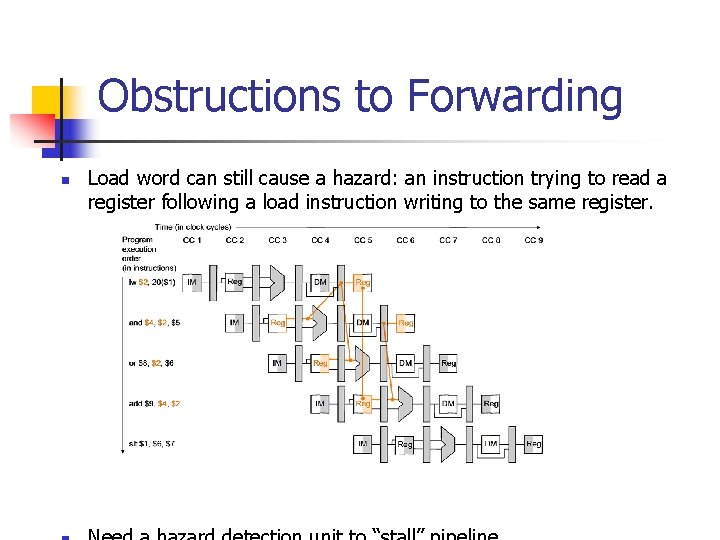

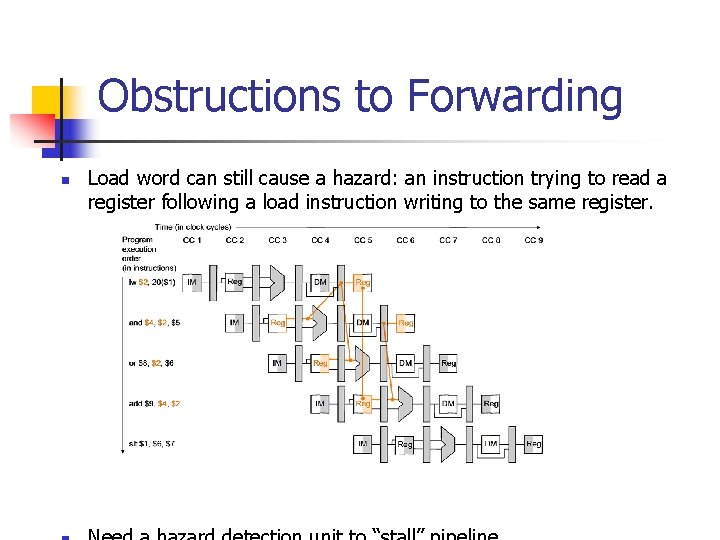

Obstructions to Forwarding n Load word can still cause a hazard: an instruction trying to read a register following a load instruction writing to the same register.

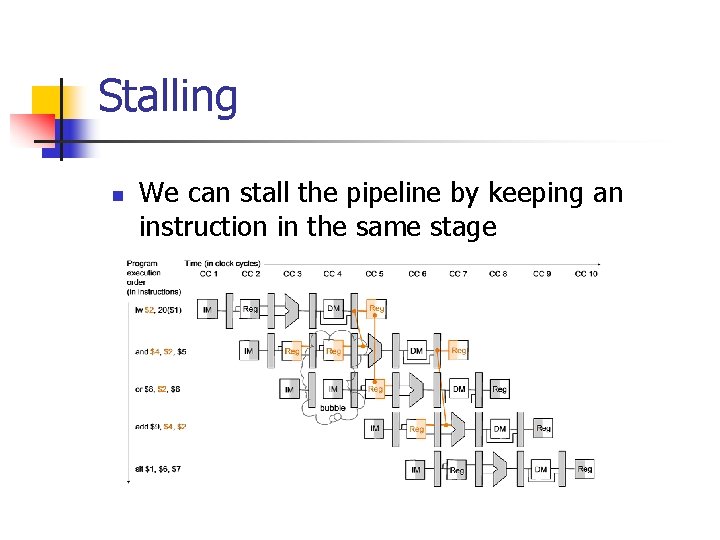

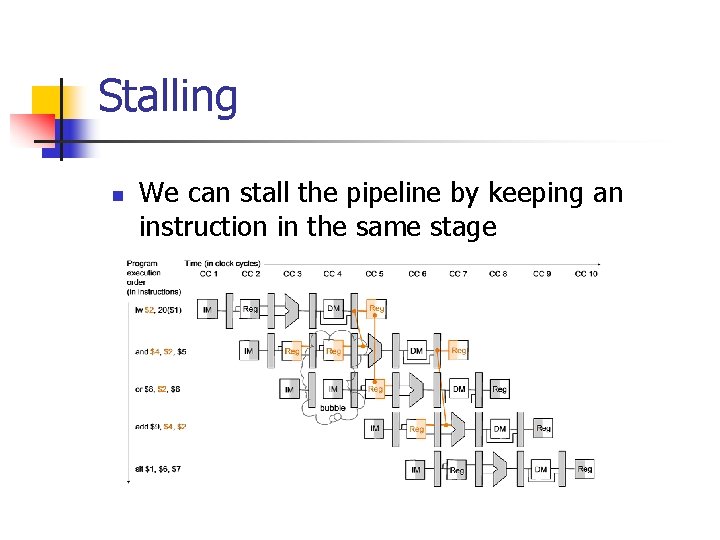

Stalling n We can stall the pipeline by keeping an instruction in the same stage

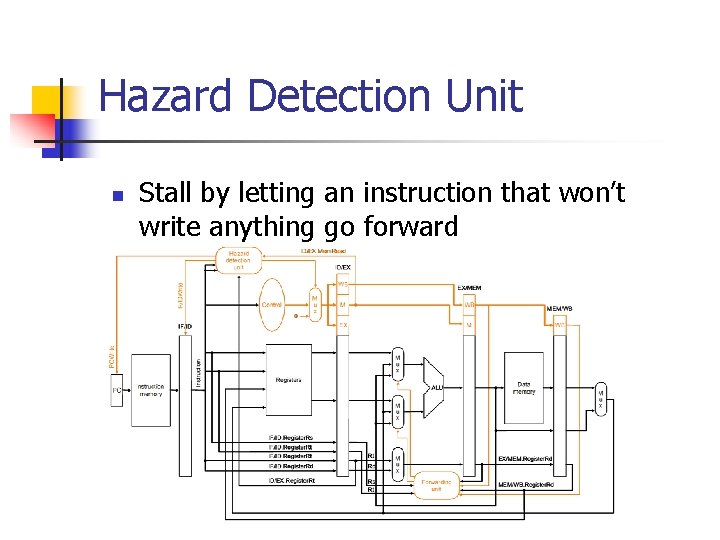

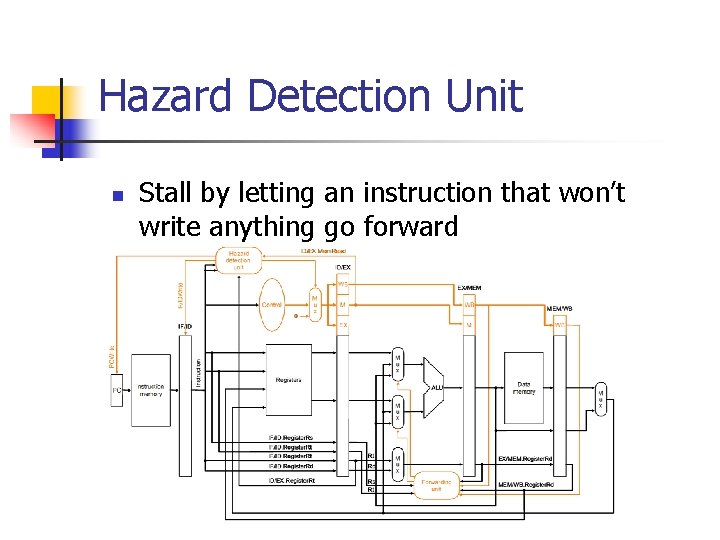

Hazard Detection Unit n Stall by letting an instruction that won’t write anything go forward

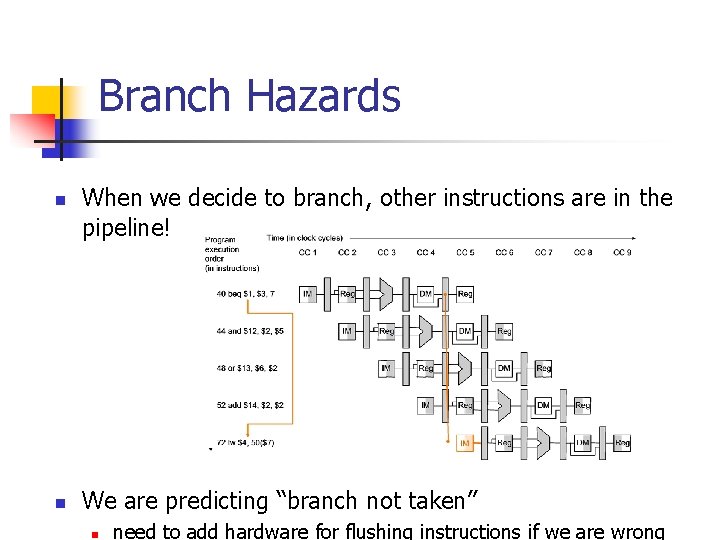

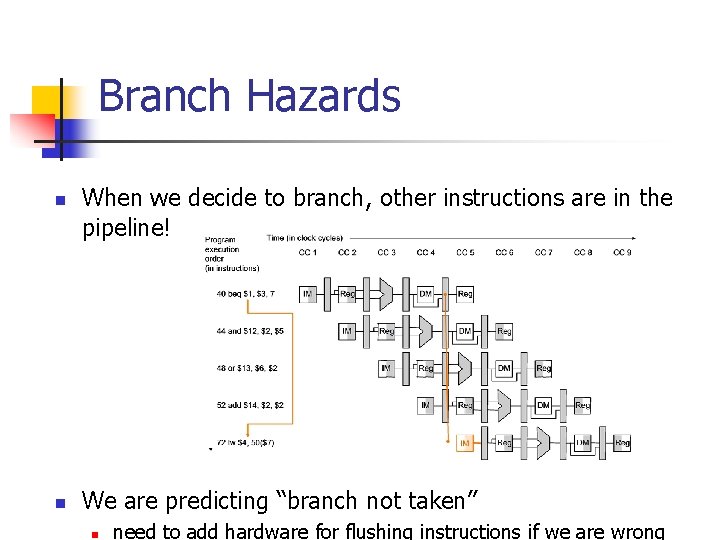

Branch Hazards n n When we decide to branch, other instructions are in the pipeline! We are predicting “branch not taken” n need to add hardware for flushing instructions if we are wrong

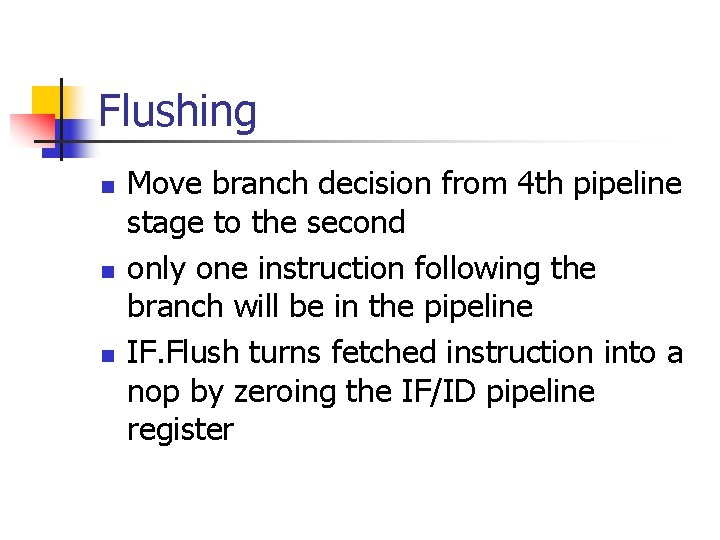

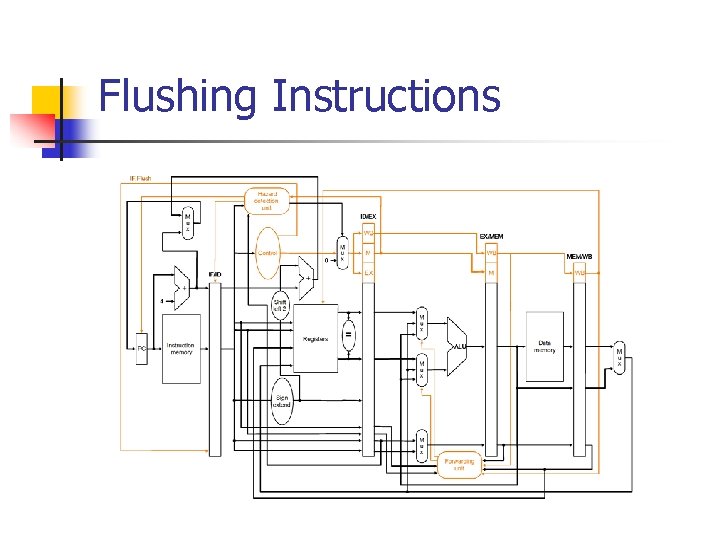

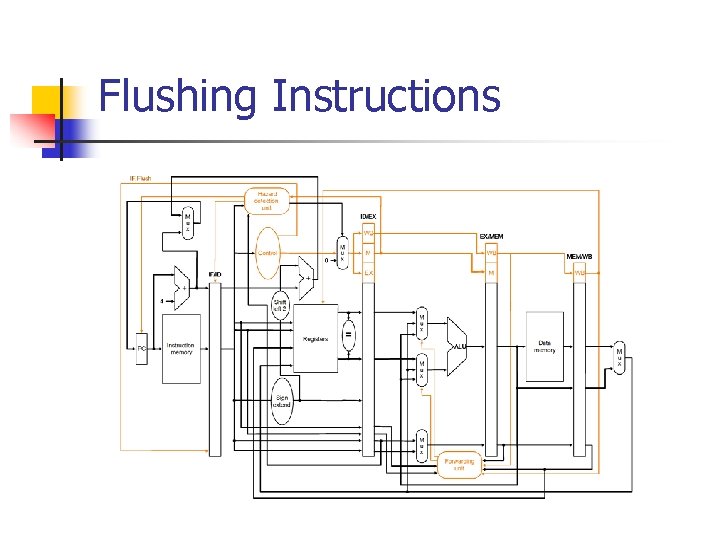

Flushing n n n Move branch decision from 4 th pipeline stage to the second only one instruction following the branch will be in the pipeline IF. Flush turns fetched instruction into a nop by zeroing the IF/ID pipeline register

Flushing Instructions

Improving Performance n n Try and avoid stalls by reordering instructions Add a “branch delay slot” n n n the next instruction after a branch is always executed rely on compiler to “fill” the slot with something useful Superscalar: start more than one instruction in the same cycle

Dynamic Scheduling n n The hardware performs the “scheduling” n hardware tries to find instructions to execute n out of order execution is possible n speculative execution and dynamic branch prediction All modern processors are very complicated n DEC Alpha 21264: 9 stage pipeline, 6 instruction issue n Power. PC and Pentium: branch history table n Compiler technology important This class has given you the background you need to learn more - read Chapter 6! More material will be posted!