Pipelining Datapath y control Pipelined Datapath El datapath

- Slides: 35

Pipelining Datapath y control

Pipelined Datapath El datapath de la CPU secuencial se puede reusar. Se separa en 5 partes: IF – instruction fetch. ID – instruction decode and register file read. EX – execution or address calculation. MEM – data memory access. WB – write back. Universidad de Sonora Arquitectura de Computadoras 2

Pipelined Datapath Fuente: COD 5, p. 287 Universidad de Sonora Arquitectura de Computadoras 3

Pipelined Datapath Las instrucciones y los datos se mueven de izquierda a derecha. Dos excepciones: 1. Etapa WB – el resultado se escribe en el banco de registros. 2. La selección del siguiente valor del PC. a) PC + 4 (no hubo brinco). b) PC + offset (si hubo brinco) Universidad de Sonora Arquitectura de Computadoras 4

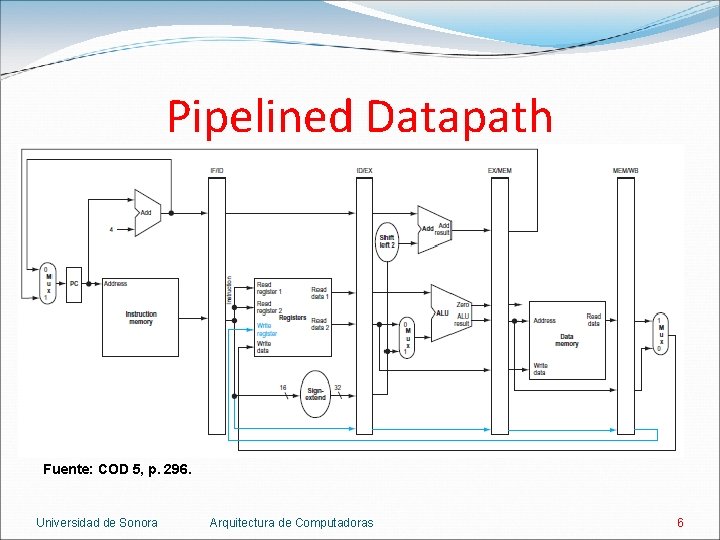

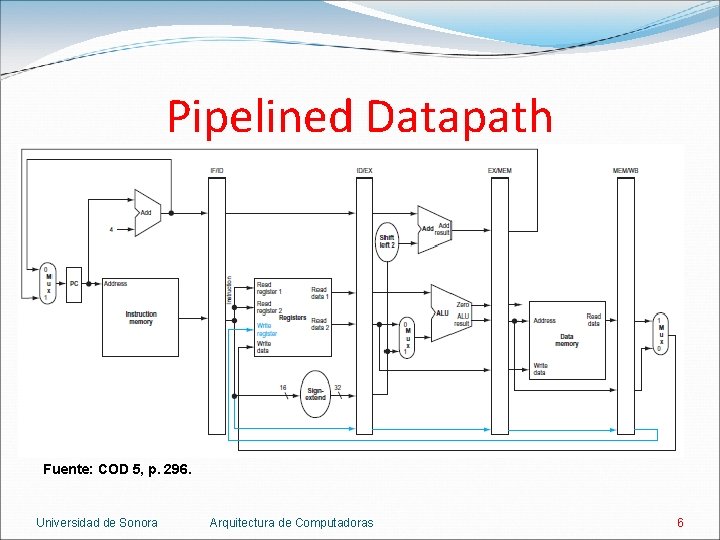

Pipelined Datapath 1. 2. 3. 4. Se colocan registros entre cada etapa. Sirven para pasar valores de una etapa a otra. Hay 4 registros: IF/ID. ID/EX. EX/MEM. MEM/WB. Universidad de Sonora Arquitectura de Computadoras 5

Pipelined Datapath Fuente: COD 5, p. 296. Universidad de Sonora Arquitectura de Computadoras 6

Ejemplo Mostrar como avanza una instrucción lw en el datapath. Imágenes del COD 5, p. 291 – 293. Universidad de Sonora Arquitectura de Computadoras 7

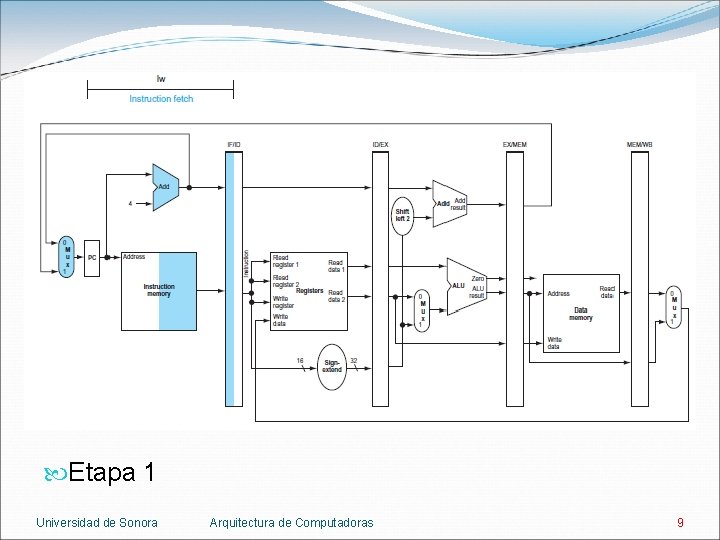

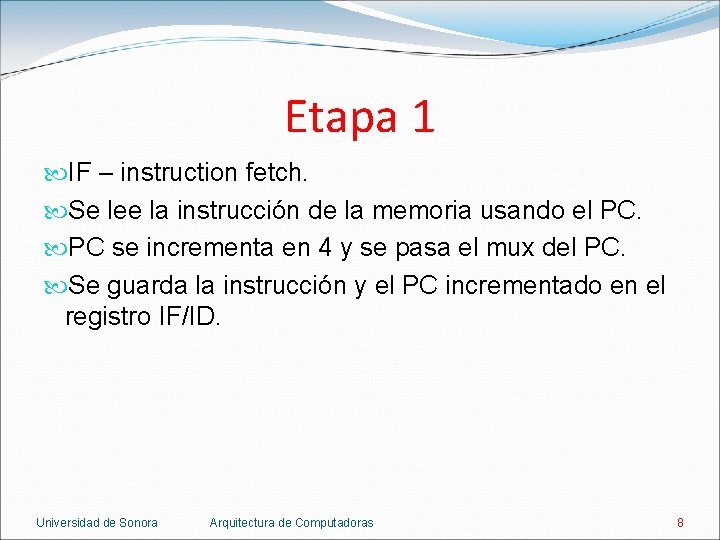

Etapa 1 IF – instruction fetch. Se lee la instrucción de la memoria usando el PC. PC se incrementa en 4 y se pasa el mux del PC. Se guarda la instrucción y el PC incrementado en el registro IF/ID. Universidad de Sonora Arquitectura de Computadoras 8

Ejemplo Etapa 1 Universidad de Sonora Arquitectura de Computadoras 9

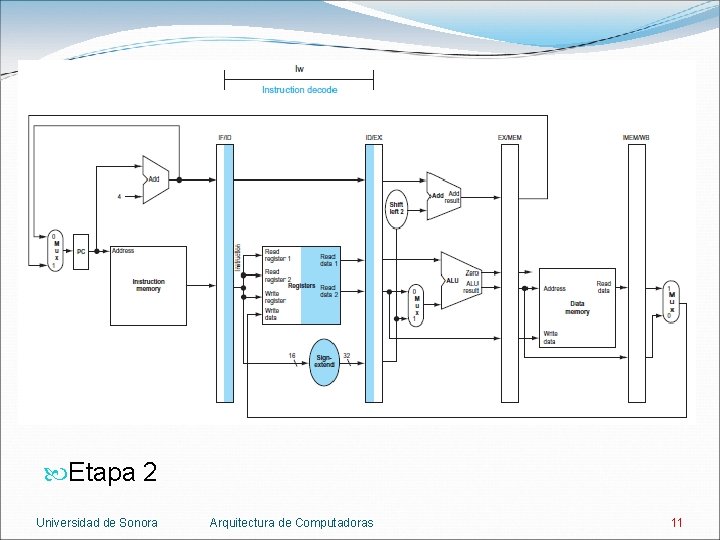

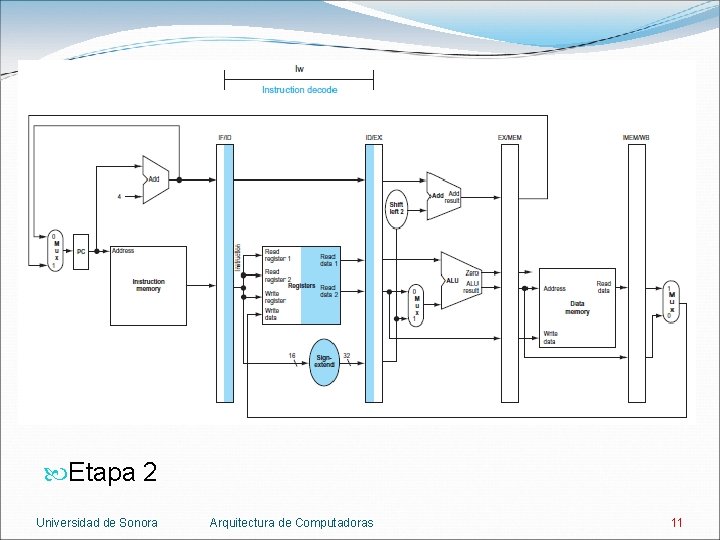

Etapa 2 ID – instruction decode and register file read. Se lee el registro base en el banco de registros. Se obtiene el offset (dos bytes más bajos de la instrucción). Se extiende el offset a 4 bytes (32 bits) usando el extensor de signo. Se guarda el PC, el registro base y el offset extendido en el registro ID/EX. Universidad de Sonora Arquitectura de Computadoras 10

Ejemplo Etapa 2 Universidad de Sonora Arquitectura de Computadoras 11

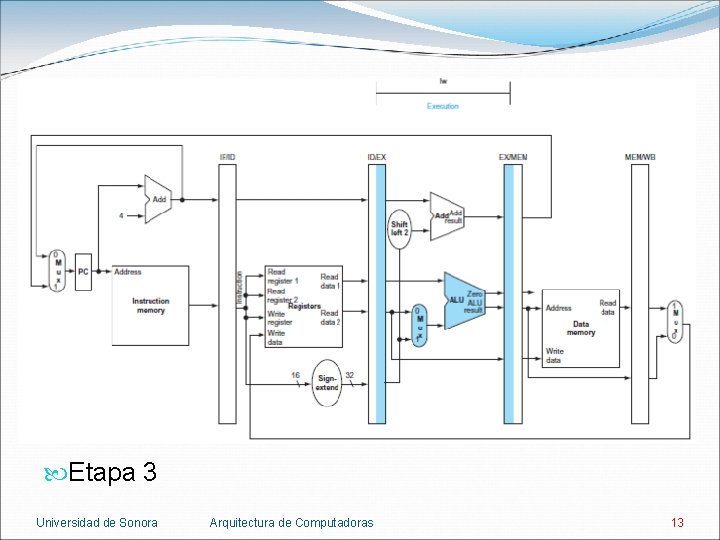

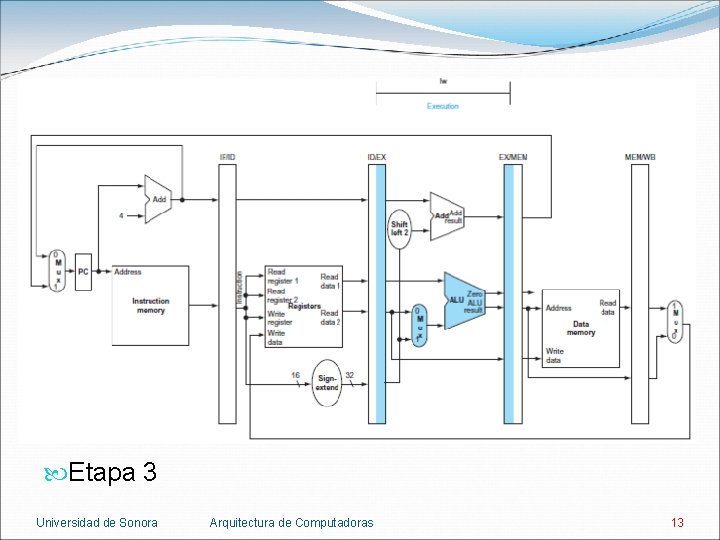

Etapa 3 EX – execute or address calculation. La ALU suma el registro base más el offset. Se guarda el resultado en el registro EX/MEM. Notar que las demás partes del registro EX/MEM almacenan datos que no se van a usar. Universidad de Sonora Arquitectura de Computadoras 12

Ejemplo Etapa 3 Universidad de Sonora Arquitectura de Computadoras 13

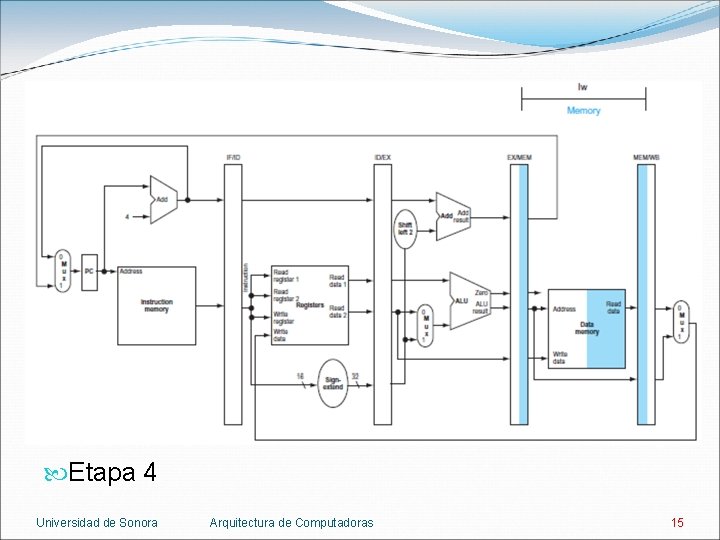

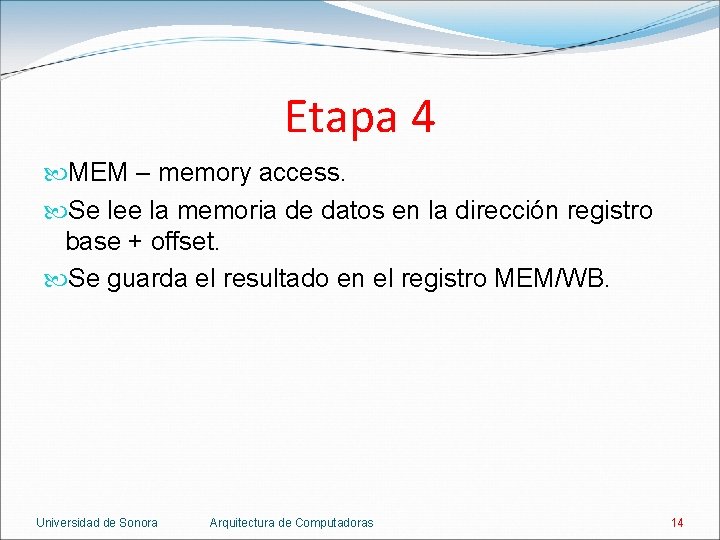

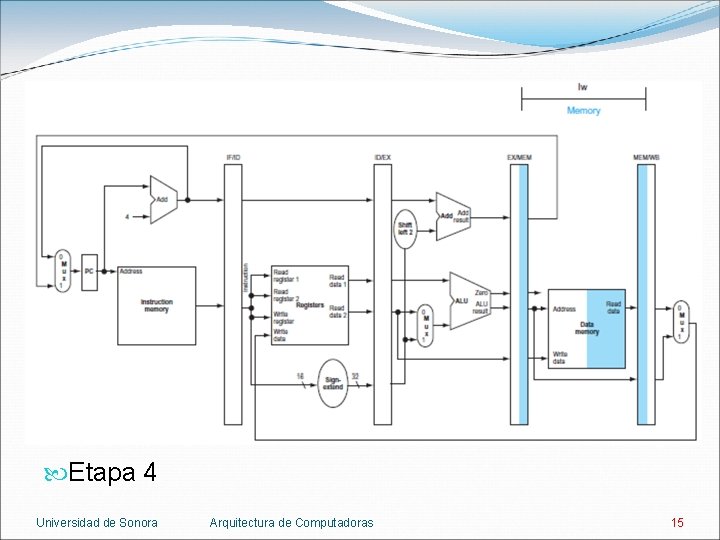

Etapa 4 MEM – memory access. Se lee la memoria de datos en la dirección registro base + offset. Se guarda el resultado en el registro MEM/WB. Universidad de Sonora Arquitectura de Computadoras 14

Ejemplo Etapa 4 Universidad de Sonora Arquitectura de Computadoras 15

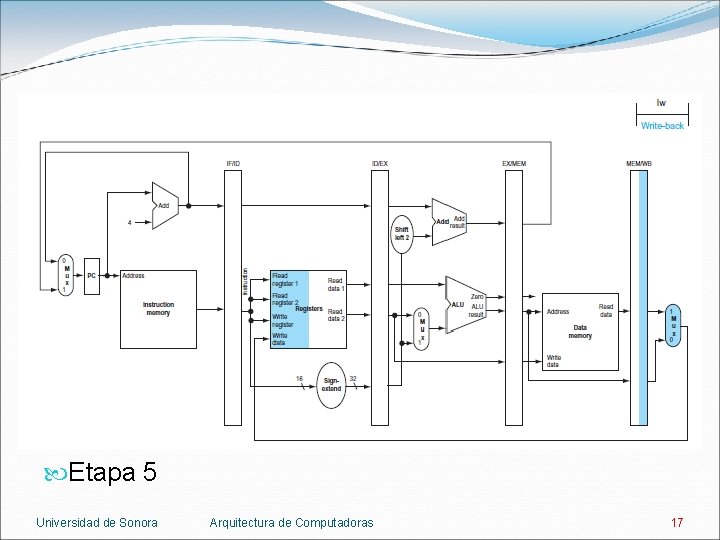

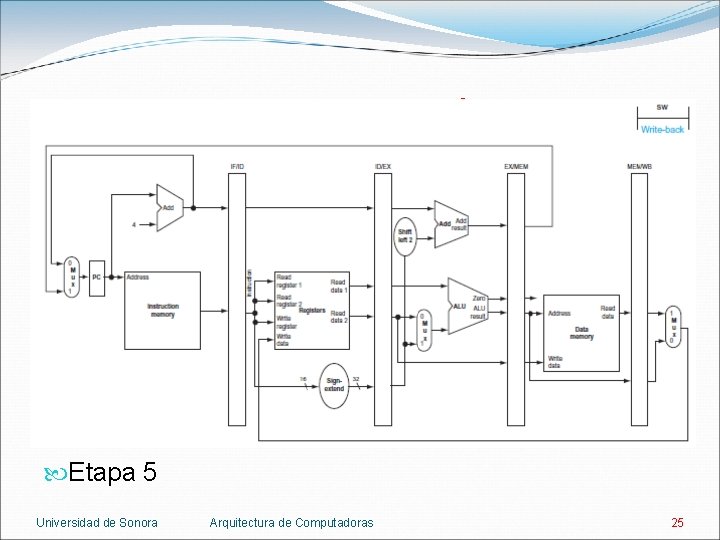

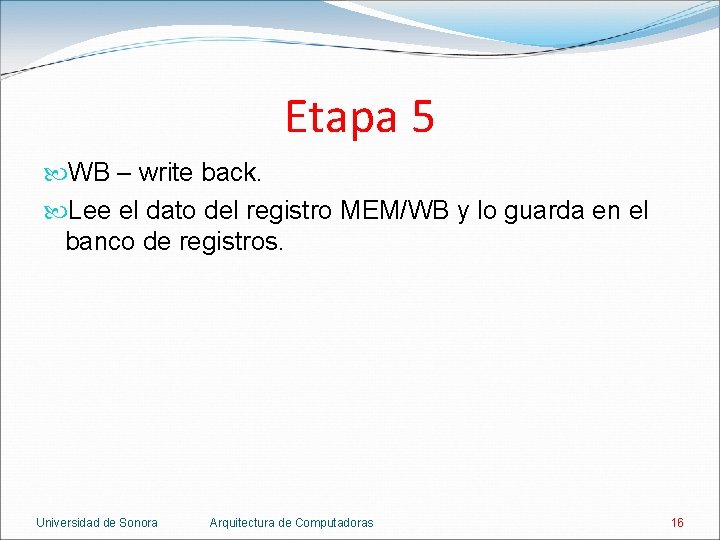

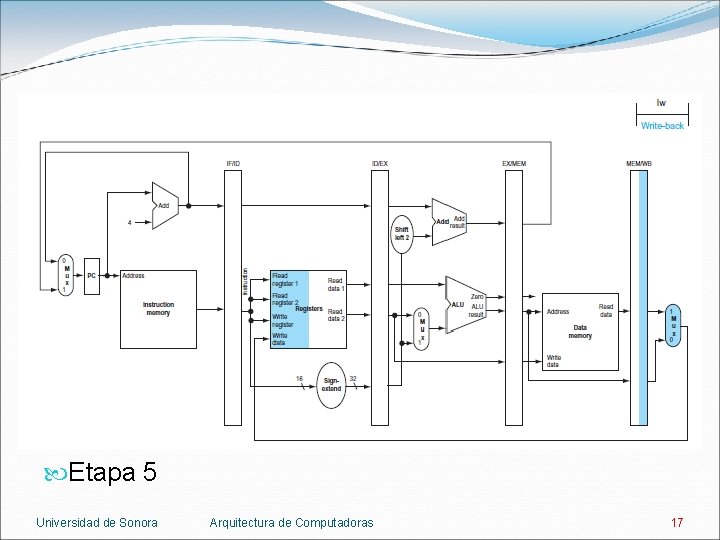

Etapa 5 WB – write back. Lee el dato del registro MEM/WB y lo guarda en el banco de registros. Universidad de Sonora Arquitectura de Computadoras 16

Ejemplo Etapa 5 Universidad de Sonora Arquitectura de Computadoras 17

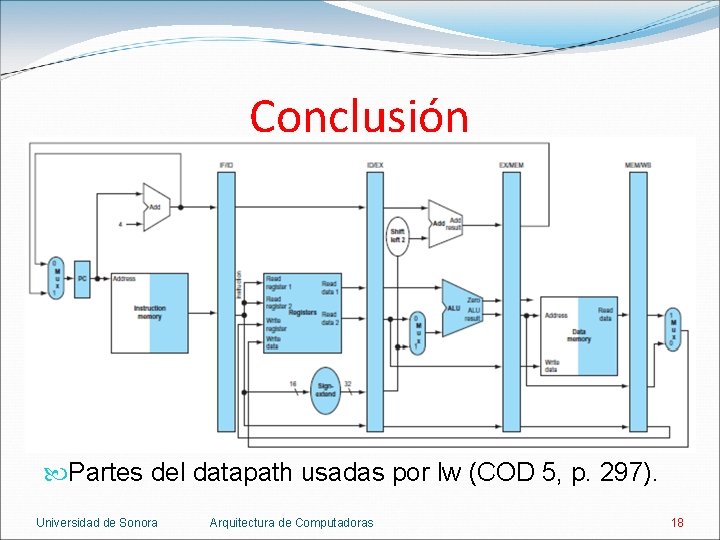

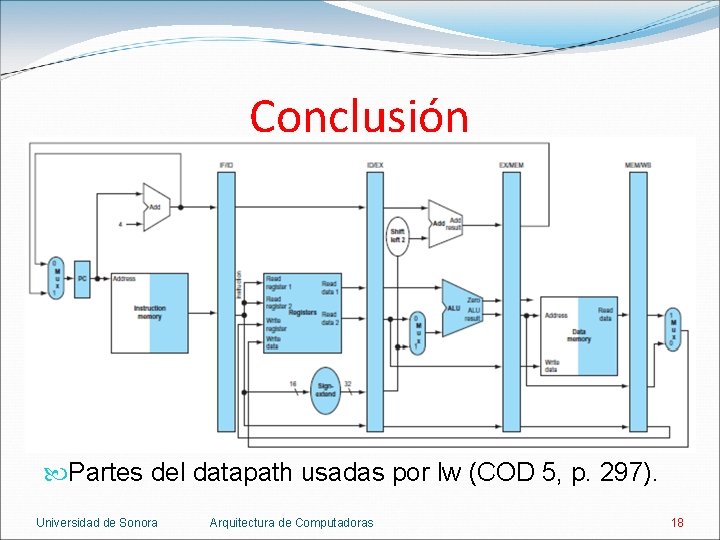

Conclusión Partes del datapath usadas por lw (COD 5, p. 297). Universidad de Sonora Arquitectura de Computadoras 18

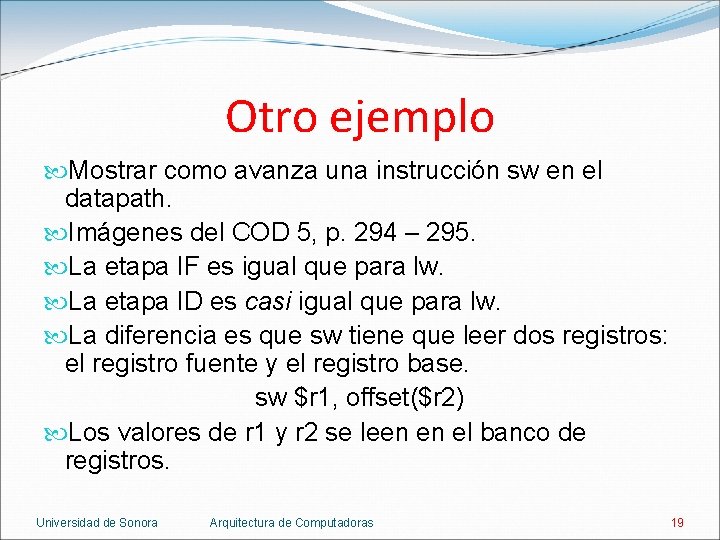

Otro ejemplo Mostrar como avanza una instrucción sw en el datapath. Imágenes del COD 5, p. 294 – 295. La etapa IF es igual que para lw. La etapa ID es casi igual que para lw. La diferencia es que sw tiene que leer dos registros: el registro fuente y el registro base. sw $r 1, offset($r 2) Los valores de r 1 y r 2 se leen en el banco de registros. Universidad de Sonora Arquitectura de Computadoras 19

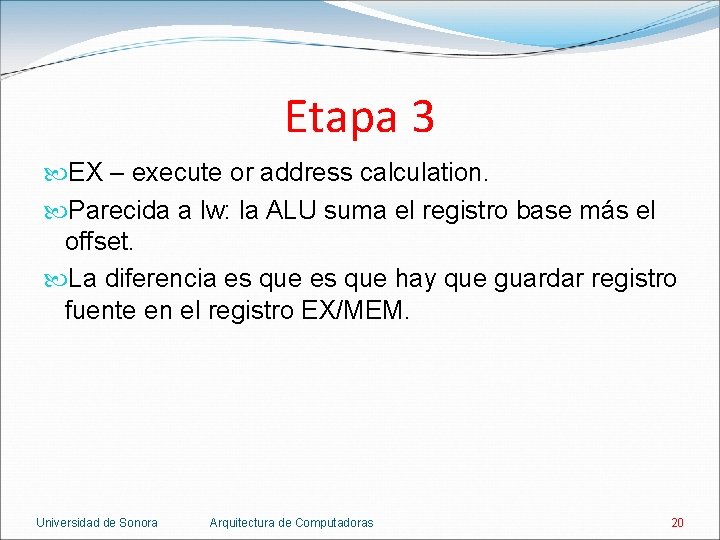

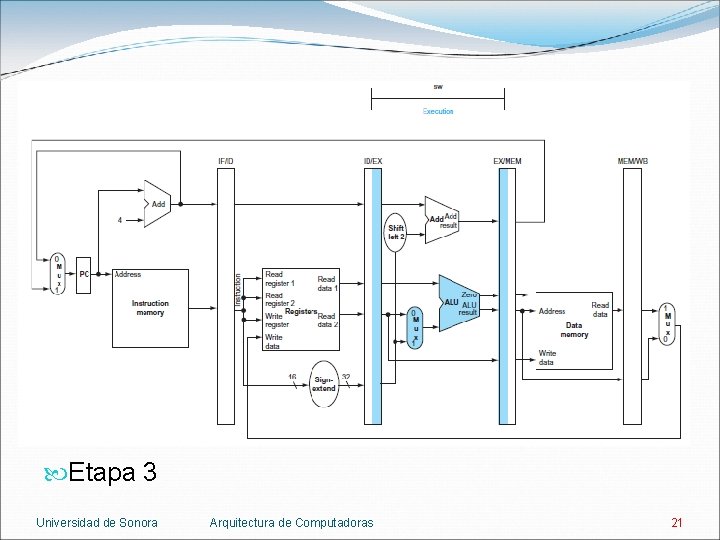

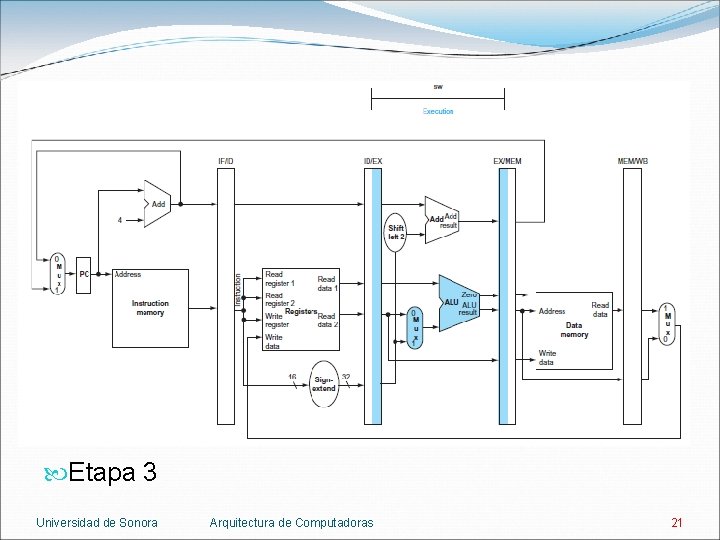

Etapa 3 EX – execute or address calculation. Parecida a lw: la ALU suma el registro base más el offset. La diferencia es que hay que guardar registro fuente en el registro EX/MEM. Universidad de Sonora Arquitectura de Computadoras 20

Otro ejemplo Etapa 3 Universidad de Sonora Arquitectura de Computadoras 21

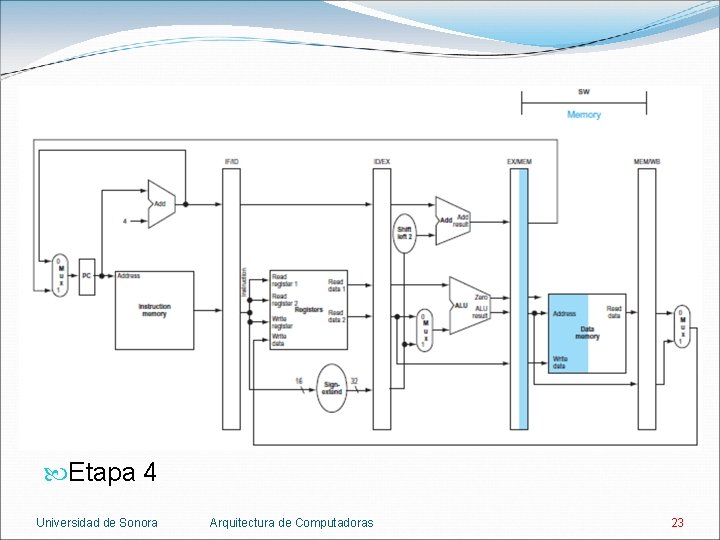

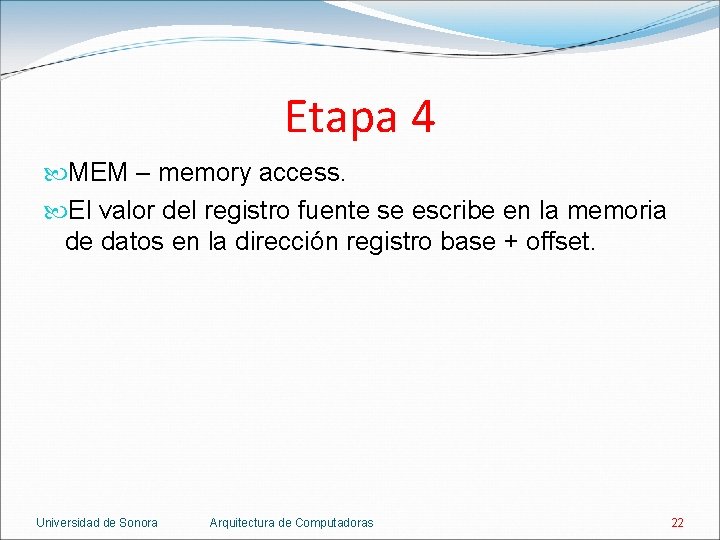

Etapa 4 MEM – memory access. El valor del registro fuente se escribe en la memoria de datos en la dirección registro base + offset. Universidad de Sonora Arquitectura de Computadoras 22

Otro ejemplo Etapa 4 Universidad de Sonora Arquitectura de Computadoras 23

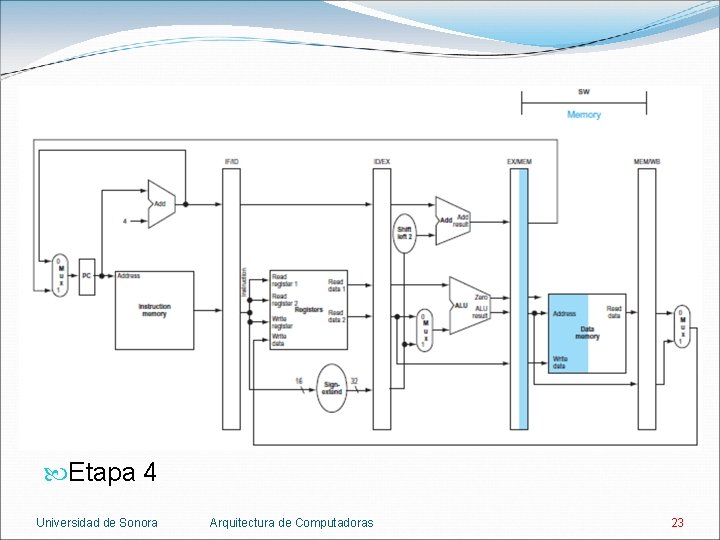

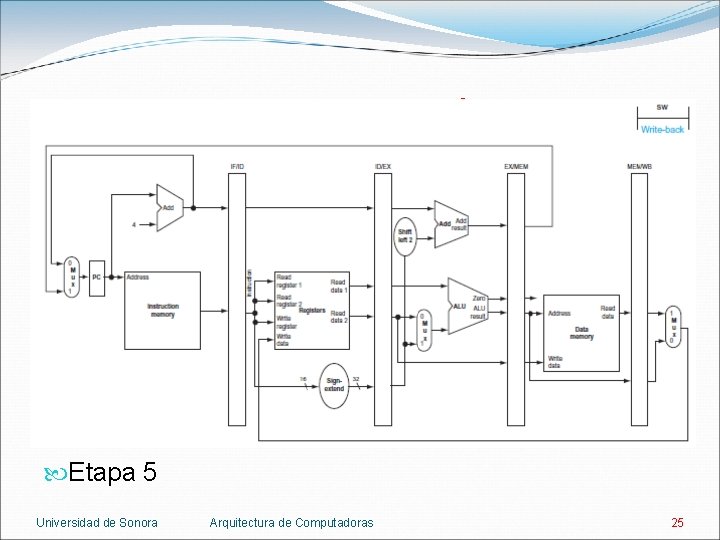

Etapa 5 WB – write back. El store no hace nada. Universidad de Sonora Arquitectura de Computadoras 24

Otro ejemplo Etapa 5 Universidad de Sonora Arquitectura de Computadoras 25

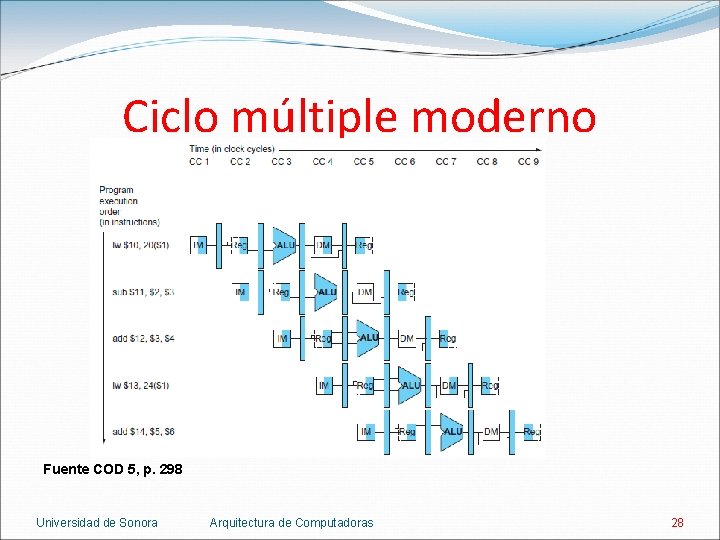

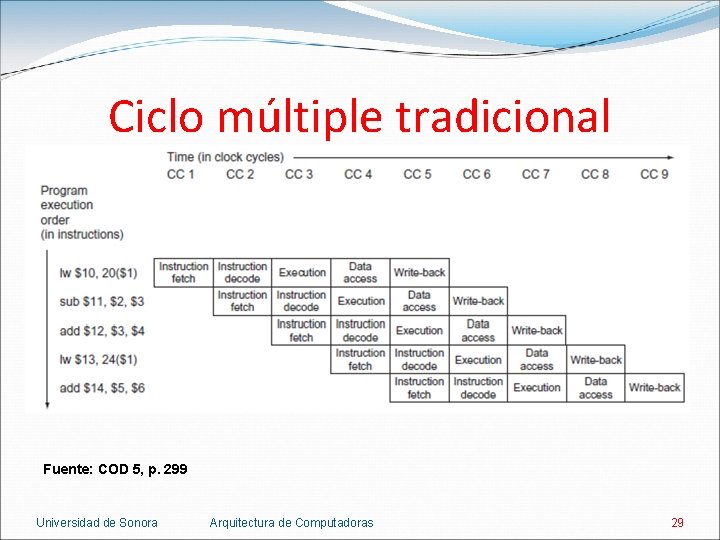

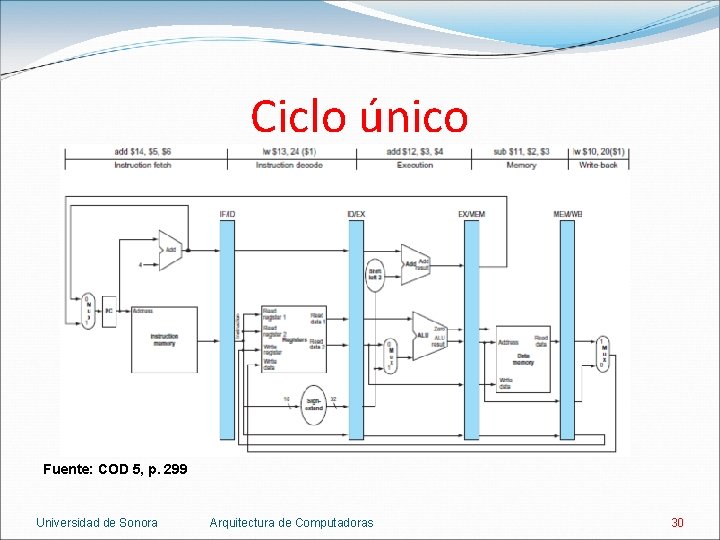

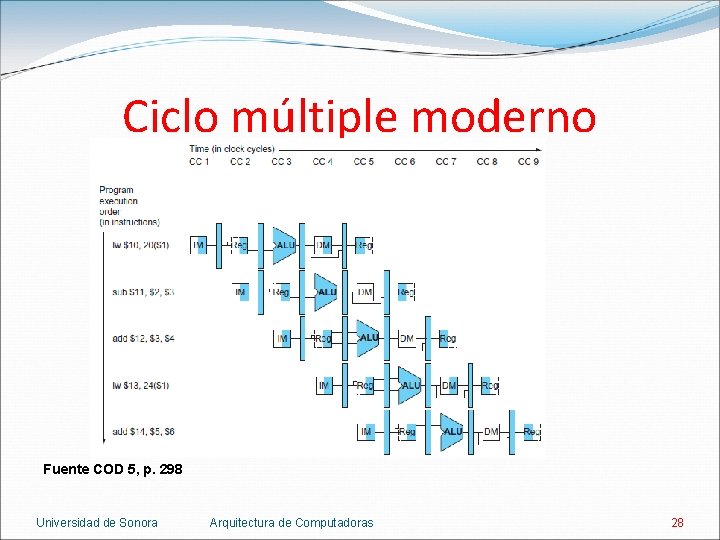

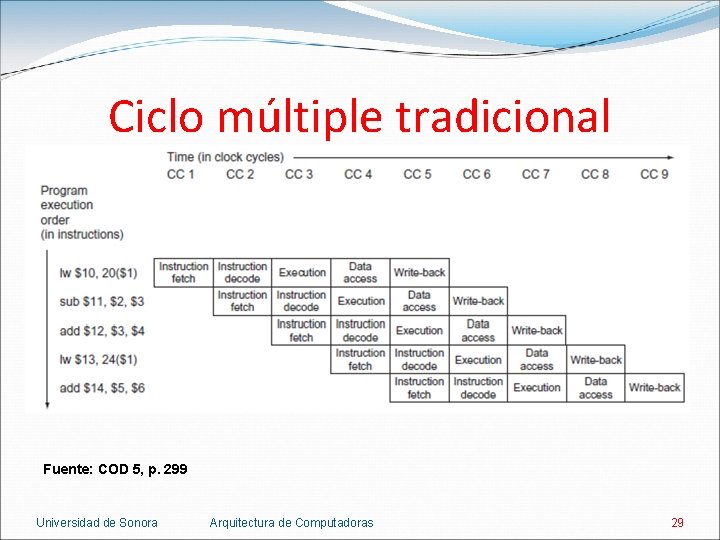

Representaciones gráficas Hay dos estilos de dibujos de pipelines: 1. Diagramas de pipeline de ciclos de reloj múltiple. 2. Diagramas de pipeline de ciclos de reloj único. Universidad de Sonora Arquitectura de Computadoras 26

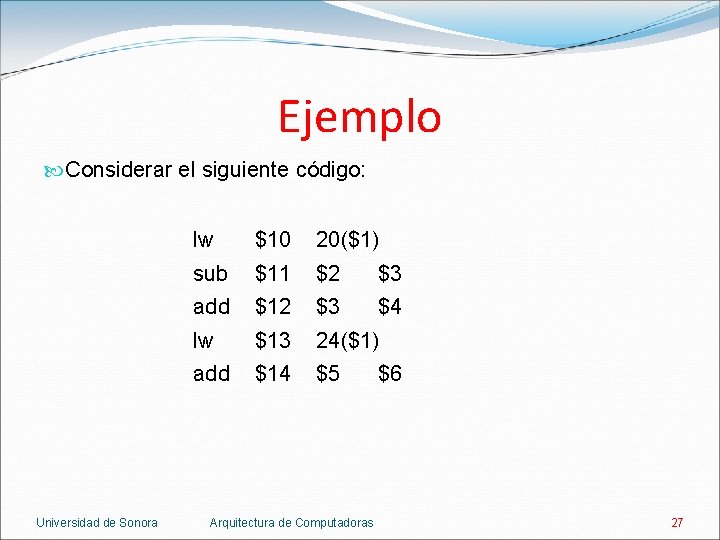

Ejemplo Considerar el siguiente código: Universidad de Sonora lw $10 20($1) sub $11 $2 $3 add $12 $3 $4 lw $13 24($1) add $14 $5 Arquitectura de Computadoras $6 27

Ciclo múltiple moderno Fuente COD 5, p. 298 Universidad de Sonora Arquitectura de Computadoras 28

Ciclo múltiple tradicional Fuente: COD 5, p. 299 Universidad de Sonora Arquitectura de Computadoras 29

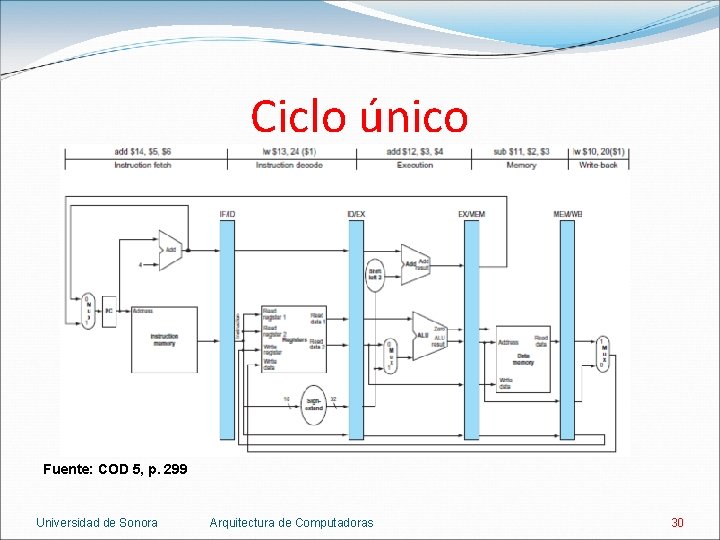

Ciclo único Fuente: COD 5, p. 299 Universidad de Sonora Arquitectura de Computadoras 30

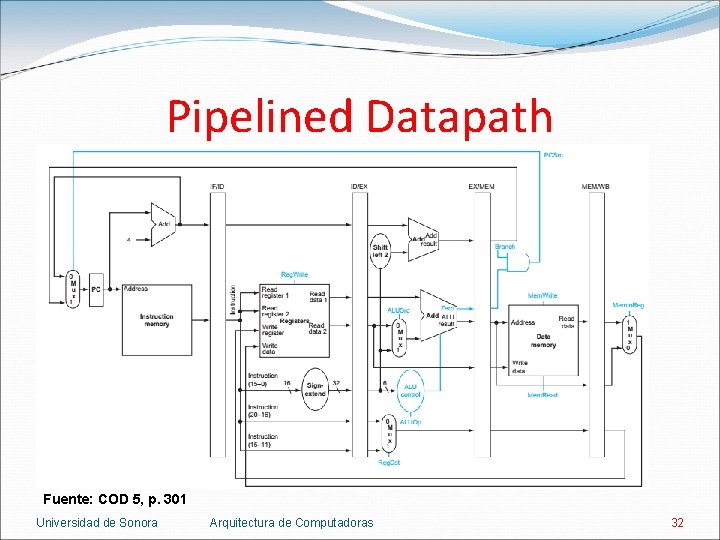

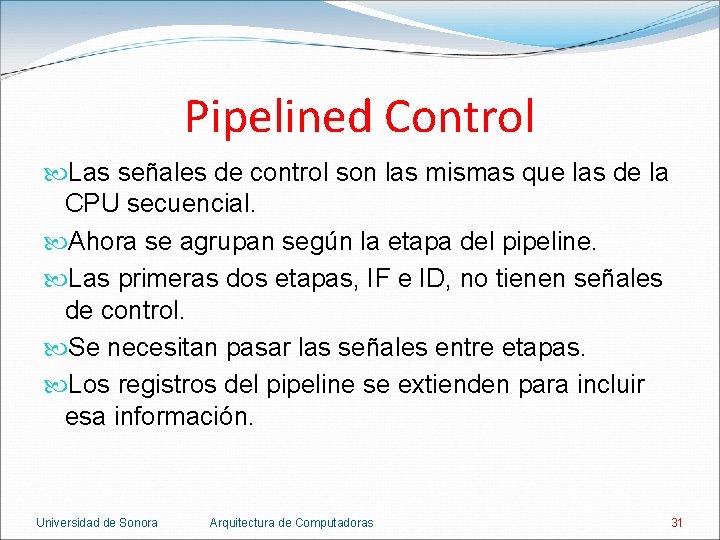

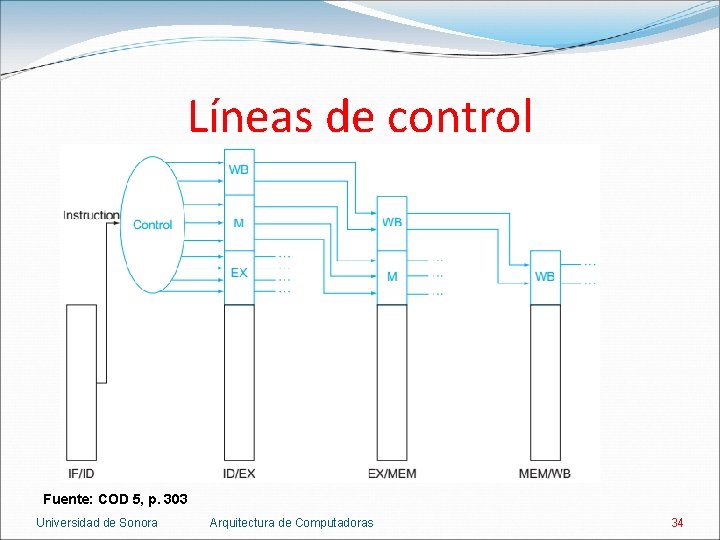

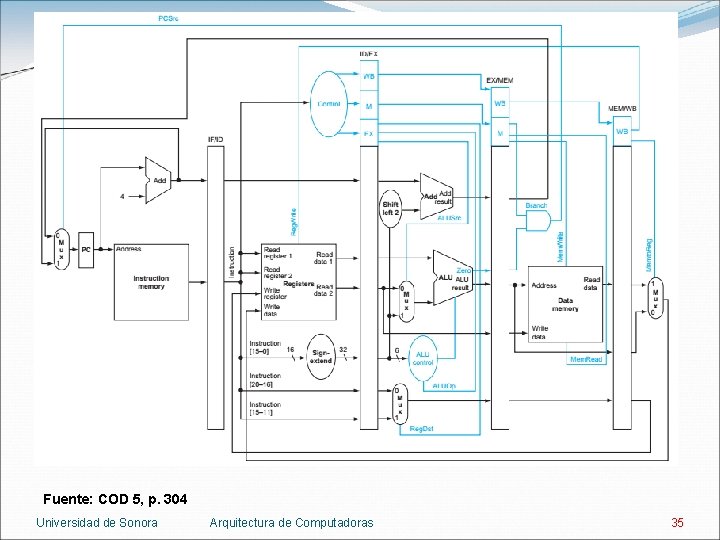

Pipelined Control Las señales de control son las mismas que las de la CPU secuencial. Ahora se agrupan según la etapa del pipeline. Las primeras dos etapas, IF e ID, no tienen señales de control. Se necesitan pasar las señales entre etapas. Los registros del pipeline se extienden para incluir esa información. Universidad de Sonora Arquitectura de Computadoras 31

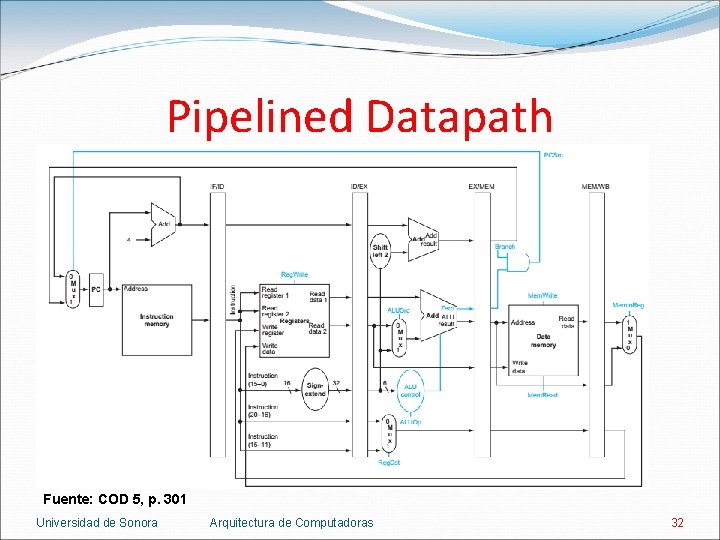

Pipelined Datapath Fuente: COD 5, p. 301 Universidad de Sonora Arquitectura de Computadoras 32

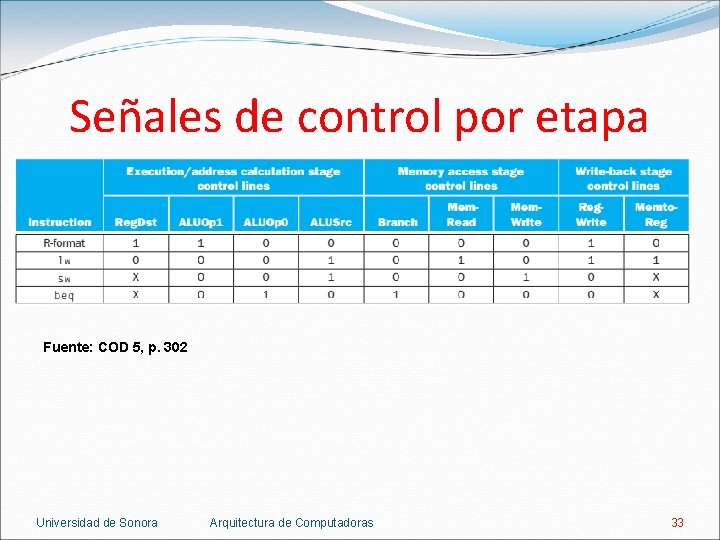

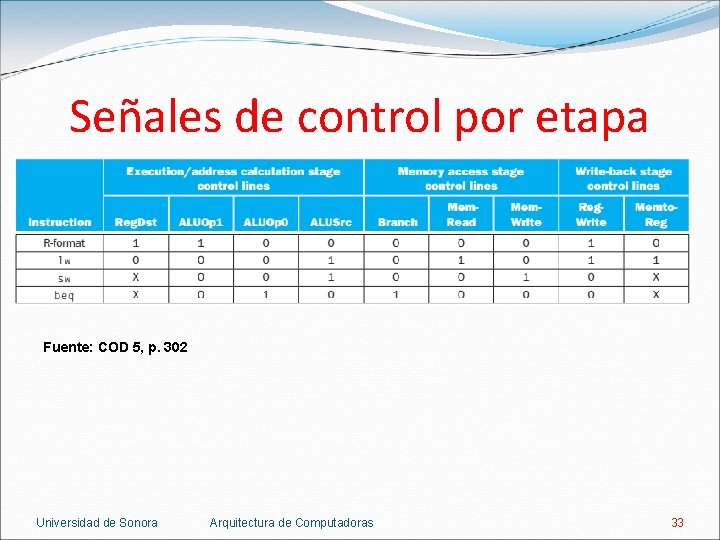

Señales de control por etapa Fuente: COD 5, p. 302 Universidad de Sonora Arquitectura de Computadoras 33

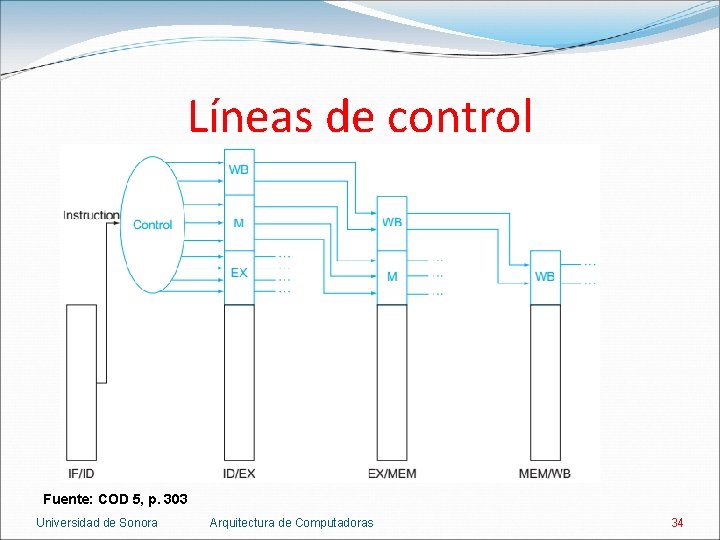

Líneas de control Fuente: COD 5, p. 303 Universidad de Sonora Arquitectura de Computadoras 34

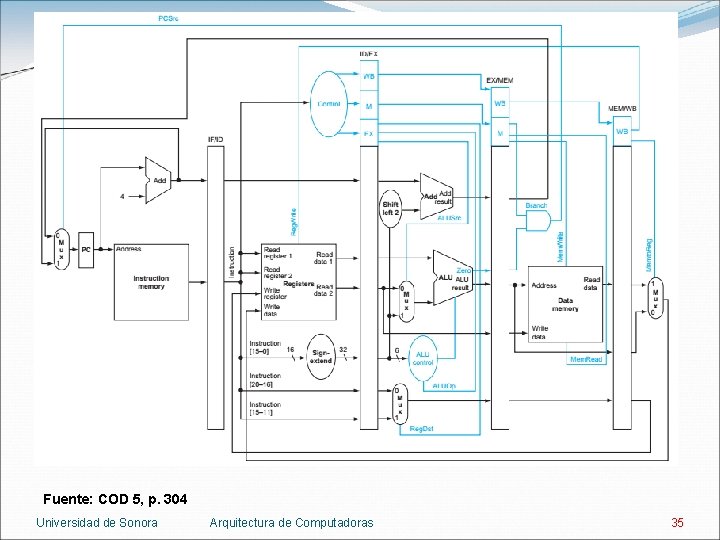

Pipelined datapath control Fuente: COD 5, p. 304 Universidad de Sonora Arquitectura de Computadoras 35