Pipelined Successive Approximation Conversion PSAC with Error Correction

- Slides: 25

Pipelined Successive Approximation Conversion (PSAC) with Error Correction for a CMOS Ophthalmic Sensor Frank Sill Torres and Davies W. de Lima Monteiro Department of Electrical Engineering, Universidade Federal de Minas Gerais Natal, 02. 09. 2009 1 / 20

Focus / Main ideas 1) Low power Analog Digital Converter (ADC) for ophthalmic applications 2) Error correction for ADC 2 / 20

Schedule § Motivation § Preliminaries § Pipelined Successive Approximation Converter (PSAC) § Error Correction Techniques § Results § Conclusion 3 / 20

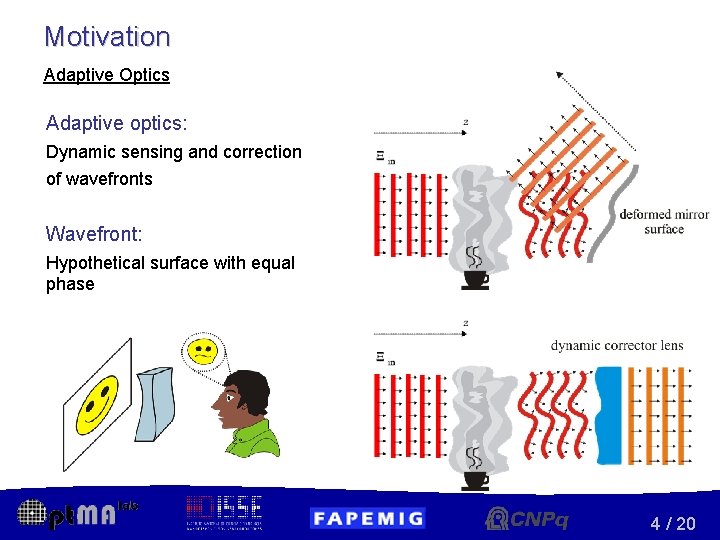

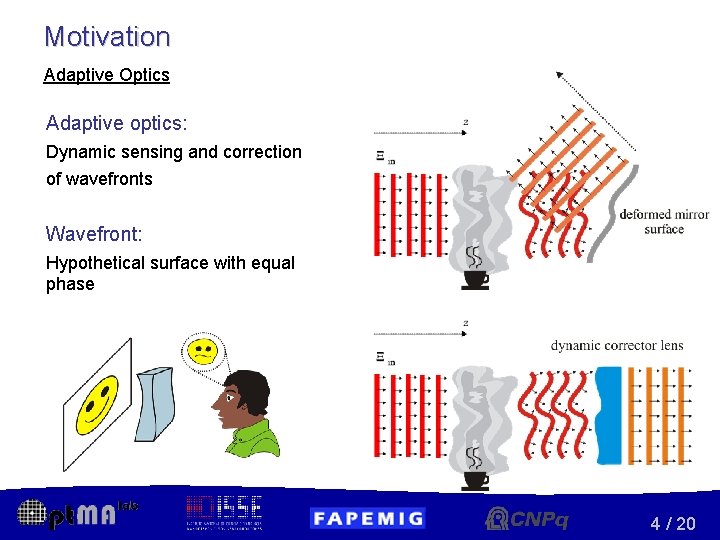

Motivation Adaptive Optics Adaptive optics: Dynamic sensing and correction of wavefronts Wavefront: Hypothetical surface with equal phase 4 / 20

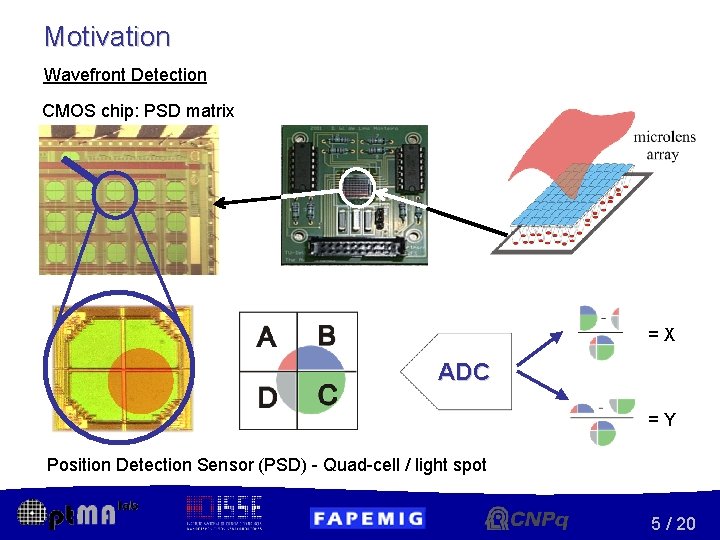

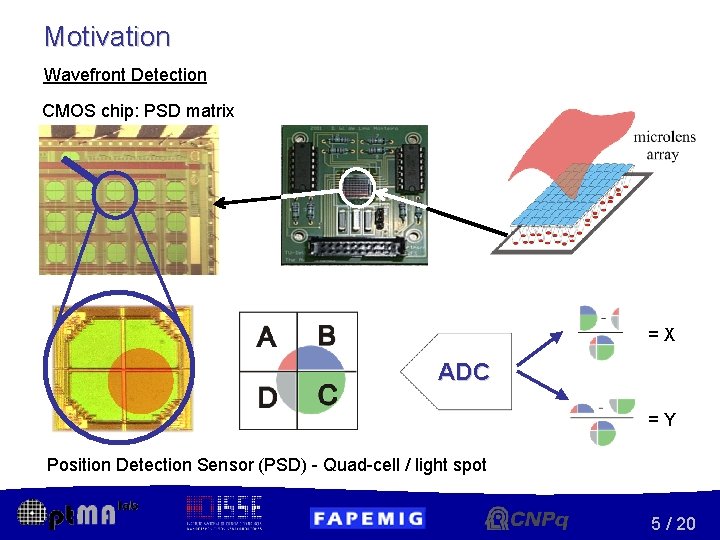

Motivation Wavefront Detection CMOS chip: PSD matrix = X ADC = Y Position Detection Sensor (PSD) - Quad-cell / light spot 5 / 20

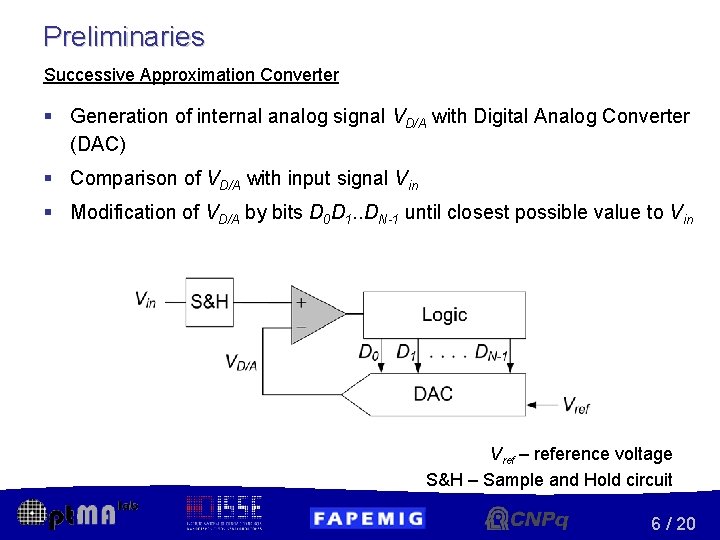

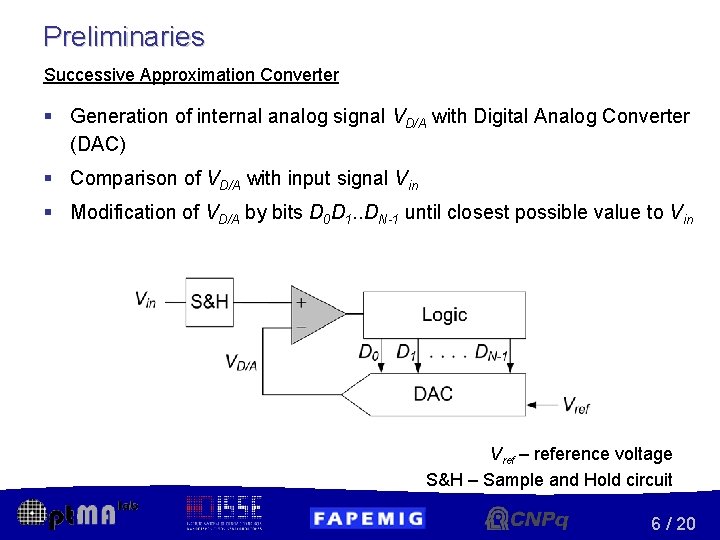

Preliminaries Successive Approximation Converter § Generation of internal analog signal VD/A with Digital Analog Converter (DAC) § Comparison of VD/A with input signal Vin § Modification of VD/A by bits D 0 D 1. . DN-1 until closest possible value to Vin Vref – reference voltage S&H – Sample and Hold circuit 6 / 20

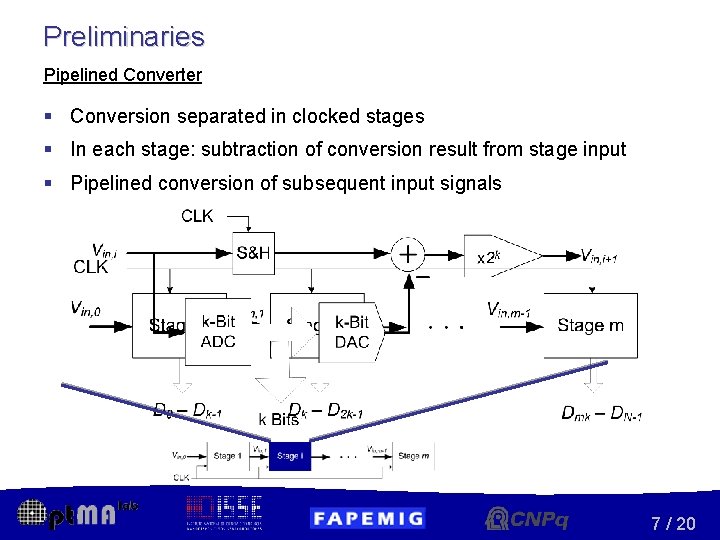

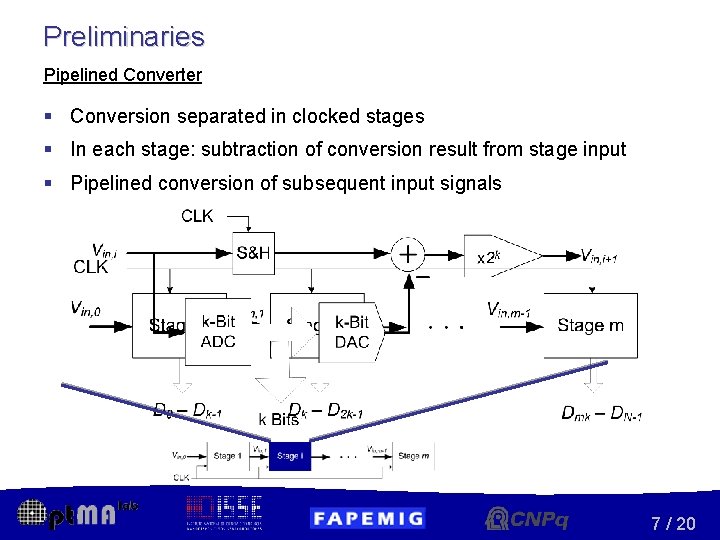

Preliminaries Pipelined Converter § Conversion separated in clocked stages § In each stage: subtraction of conversion result from stage input § Pipelined conversion of subsequent input signals 7 / 20

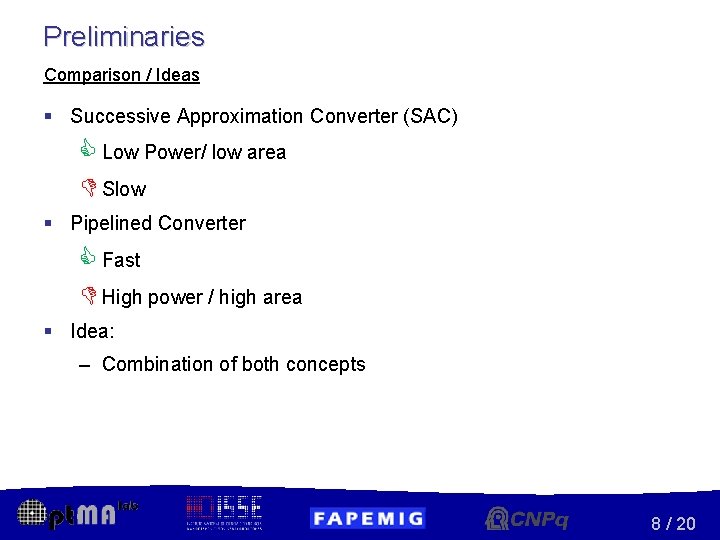

Preliminaries Comparison / Ideas § Successive Approximation Converter (SAC) Low Power/ low area Slow § Pipelined Converter Fast High power / high area § Idea: – Combination of both concepts 8 / 20

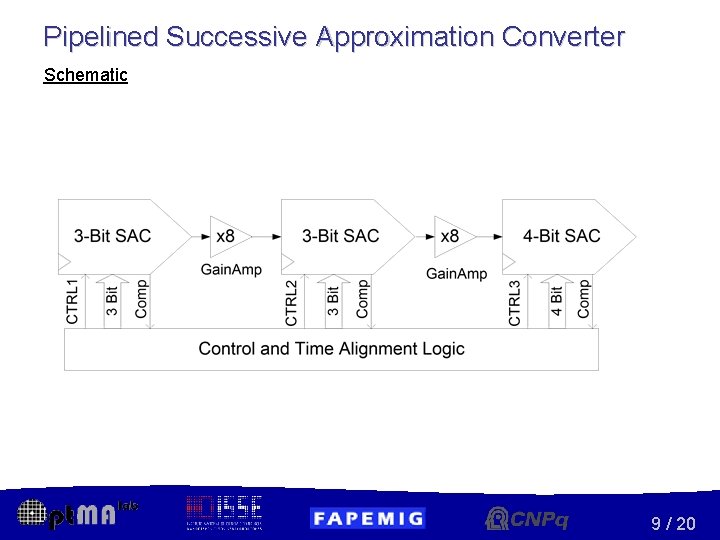

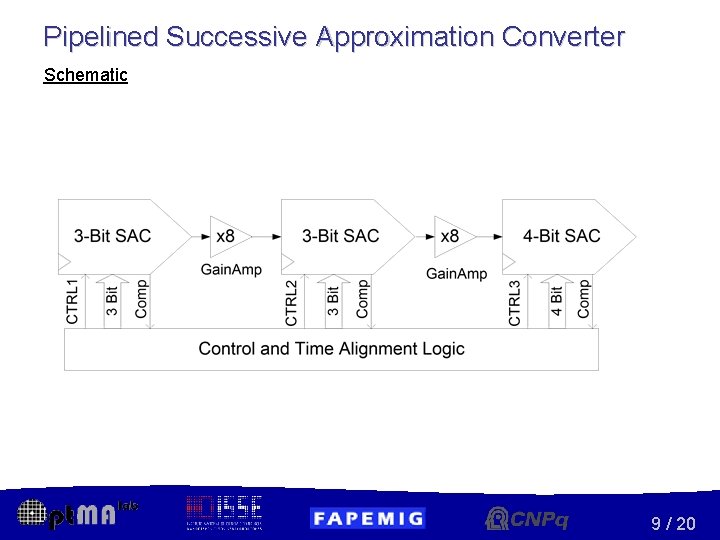

Pipelined Successive Approximation Converter Schematic 9 / 20

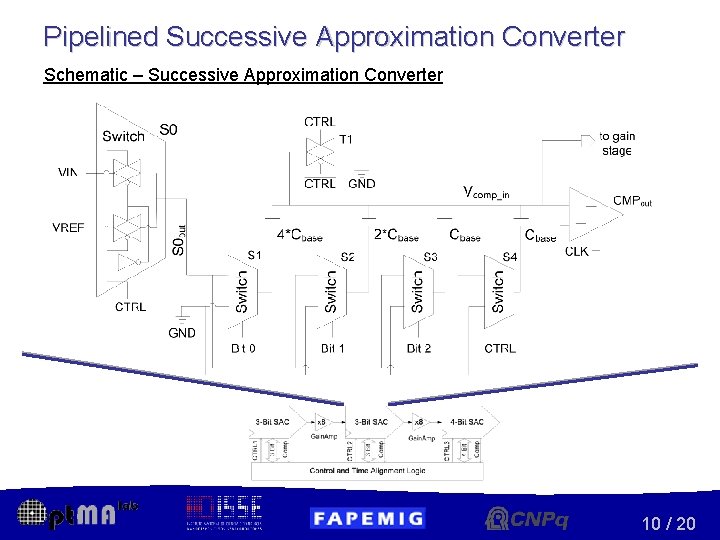

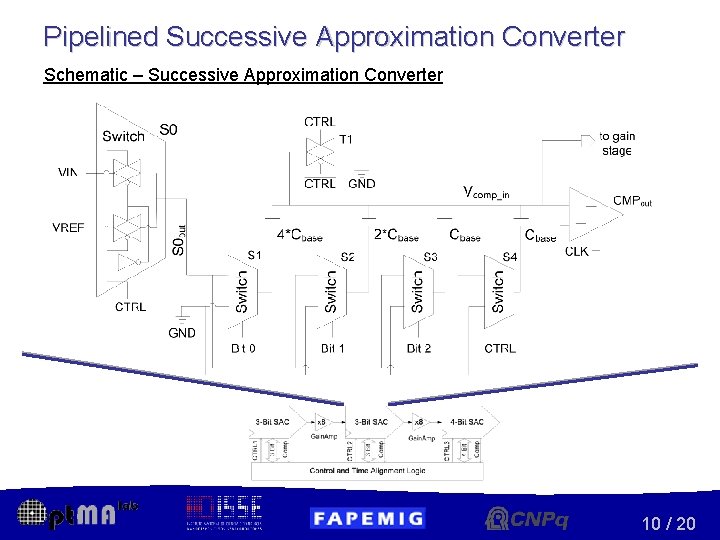

Pipelined Successive Approximation Converter Schematic – Successive Approximation Converter 10 / 20

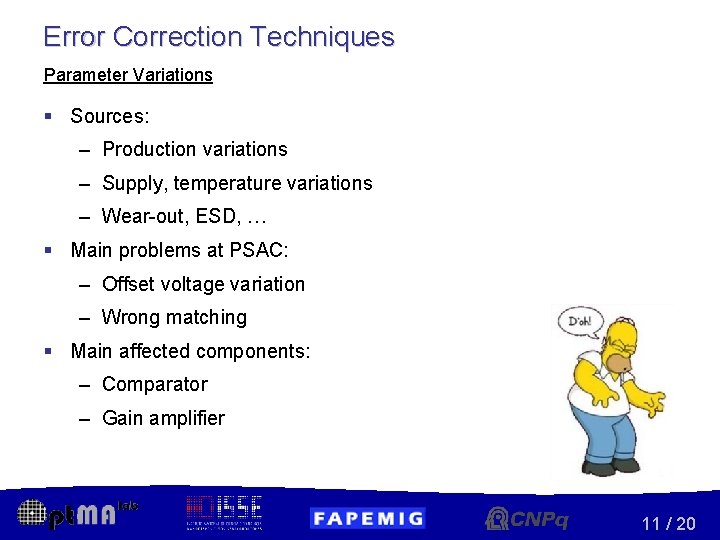

Error Correction Techniques Parameter Variations § Sources: – Production variations – Supply, temperature variations – Wear-out, ESD, … § Main problems at PSAC: – Offset voltage variation – Wrong matching § Main affected components: – Comparator – Gain amplifier 11 / 20

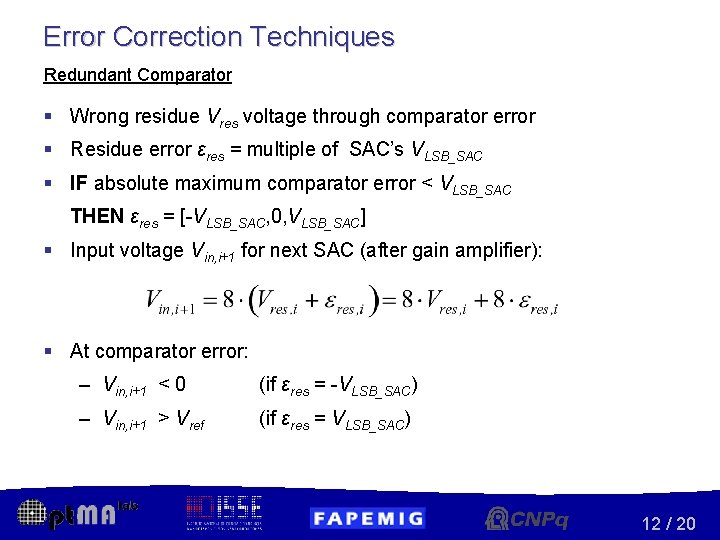

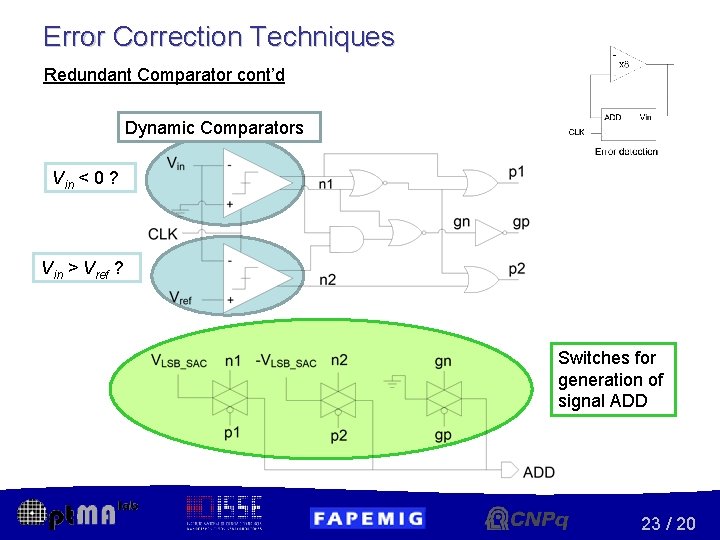

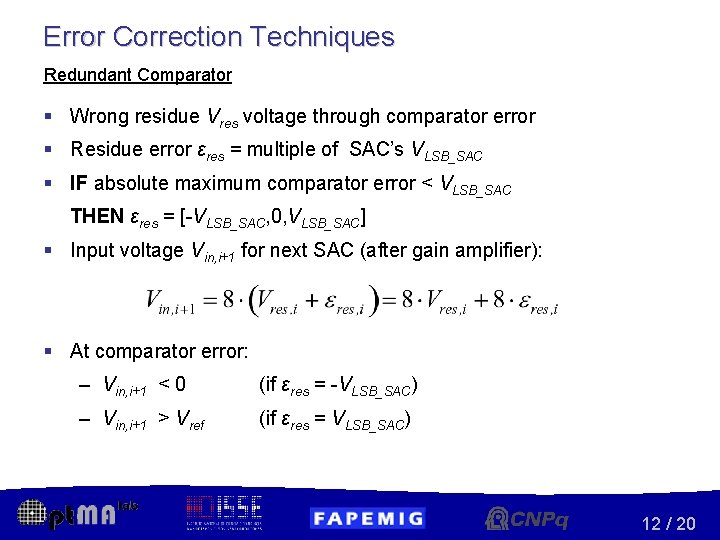

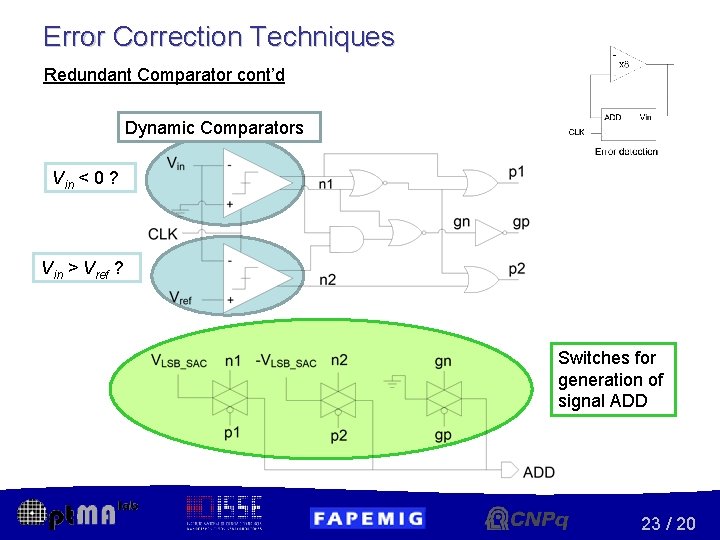

Error Correction Techniques Redundant Comparator § Wrong residue Vres voltage through comparator error § Residue error εres = multiple of SAC’s VLSB_SAC § IF absolute maximum comparator error < VLSB_SAC THEN εres = [-VLSB_SAC, 0, VLSB_SAC] § Input voltage Vin, i+1 for next SAC (after gain amplifier): § At comparator error: – Vin, i+1 < 0 (if εres = -VLSB_SAC) – Vin, i+1 > Vref (if εres = VLSB_SAC) 12 / 20

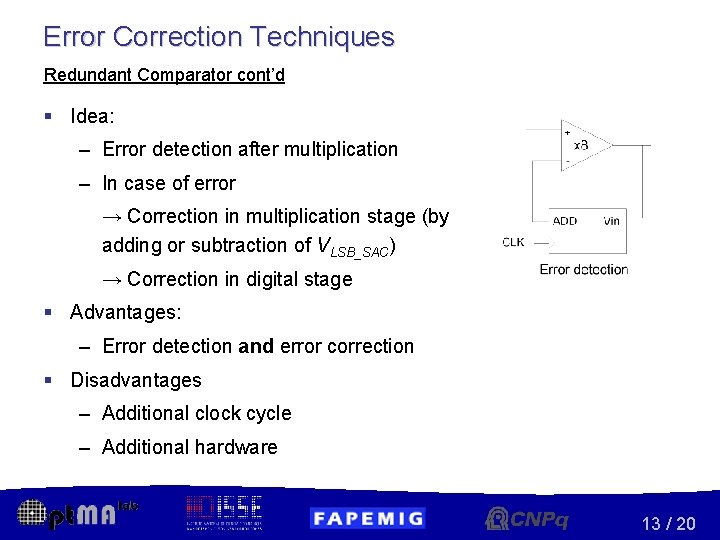

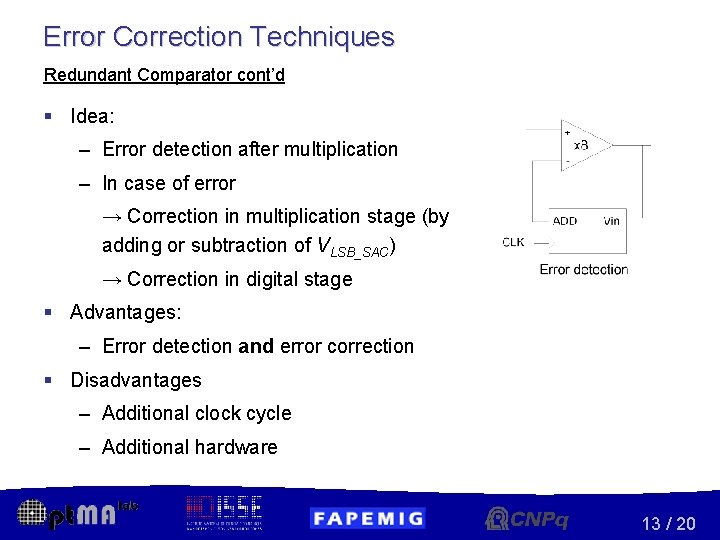

Error Correction Techniques Redundant Comparator cont’d § Idea: – Error detection after multiplication – In case of error → Correction in multiplication stage (by adding or subtraction of VLSB_SAC) → Correction in digital stage § Advantages: – Error detection and error correction § Disadvantages – Additional clock cycle – Additional hardware 13 / 20

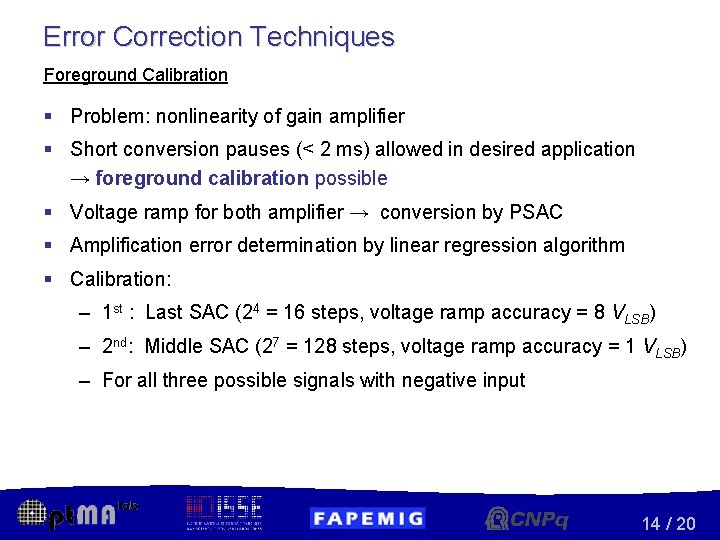

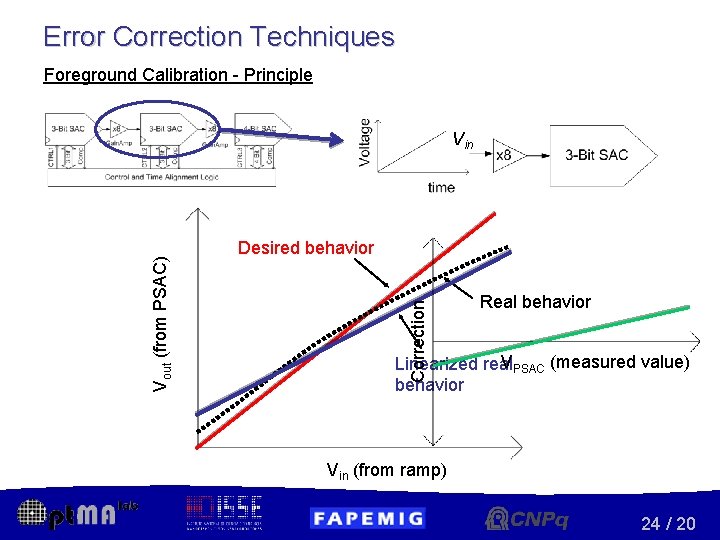

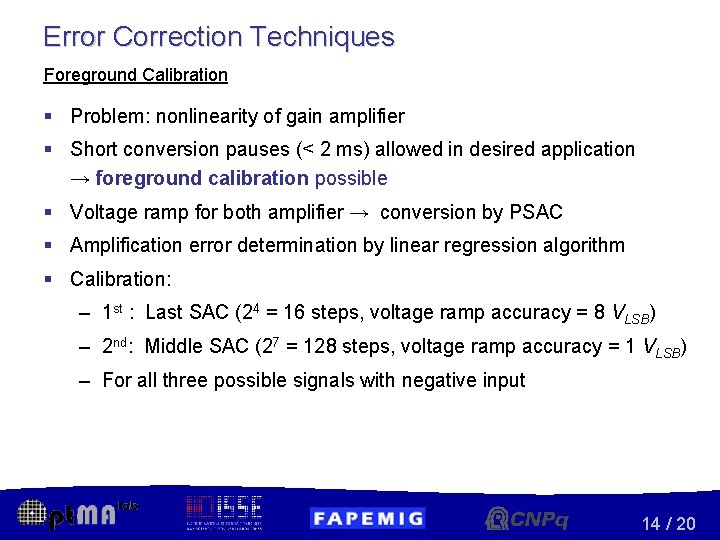

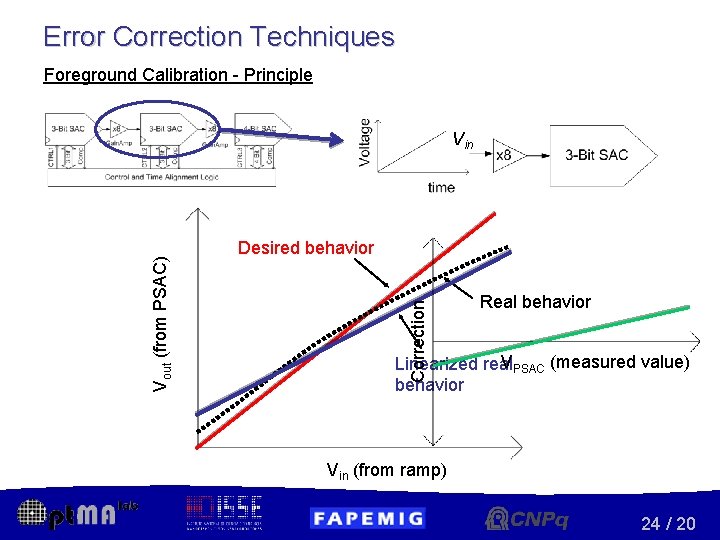

Error Correction Techniques Foreground Calibration § Problem: nonlinearity of gain amplifier § Short conversion pauses (< 2 ms) allowed in desired application → foreground calibration possible § Voltage ramp for both amplifier → conversion by PSAC § Amplification error determination by linear regression algorithm § Calibration: – 1 st : Last SAC (24 = 16 steps, voltage ramp accuracy = 8 VLSB) – 2 nd: Middle SAC (27 = 128 steps, voltage ramp accuracy = 1 VLSB) – For all three possible signals with negative input 14 / 20

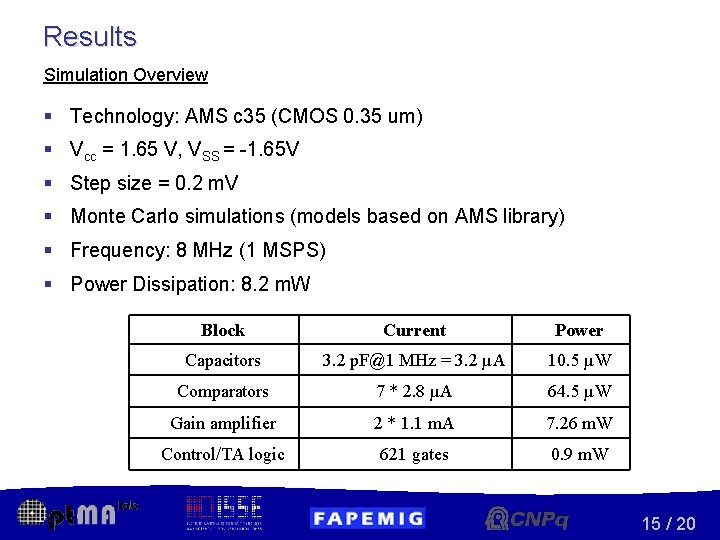

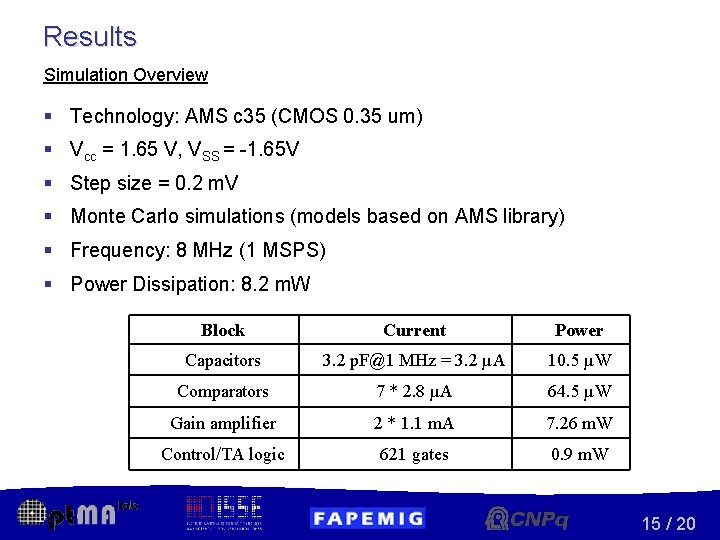

Results Simulation Overview § Technology: AMS c 35 (CMOS 0. 35 um) § Vcc = 1. 65 V, VSS = -1. 65 V § Step size = 0. 2 m. V § Monte Carlo simulations (models based on AMS library) § Frequency: 8 MHz (1 MSPS) § Power Dissipation: 8. 2 m. W Block Current Power Capacitors 3. 2 p. F@1 MHz = 3. 2 µA 10. 5 µW Comparators 7 * 2. 8 µA 64. 5 µW Gain amplifier 2 * 1. 1 m. A 7. 26 m. W Control/TA logic 621 gates 0. 9 m. W 15 / 20

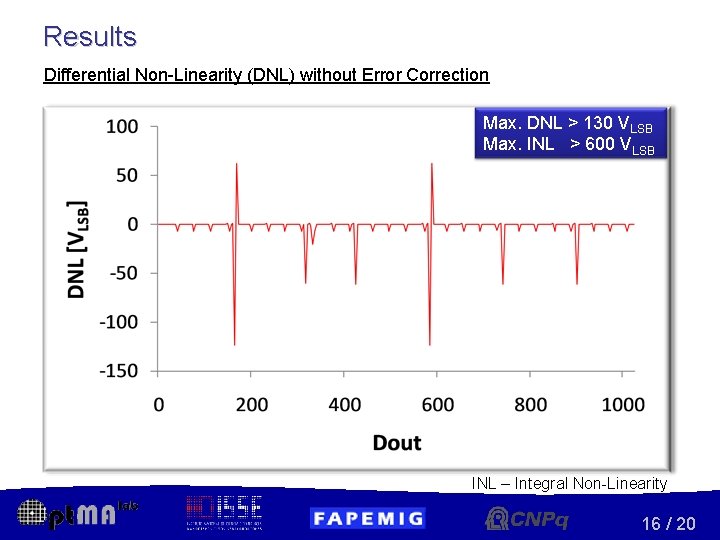

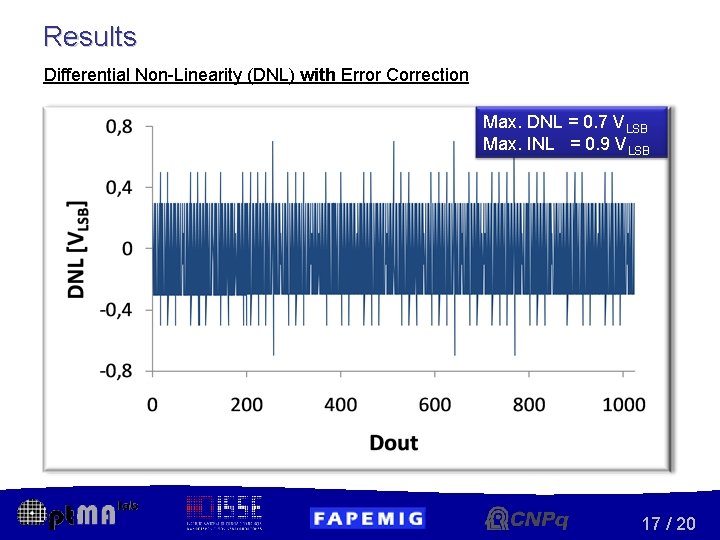

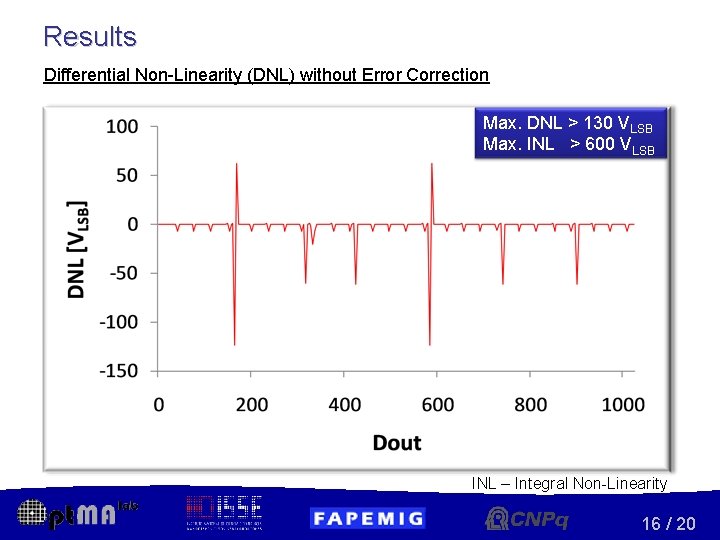

Results Differential Non-Linearity (DNL) without Error Correction Max. DNL > 130 VLSB Max. INL > 600 VLSB INL – Integral Non-Linearity 16 / 20

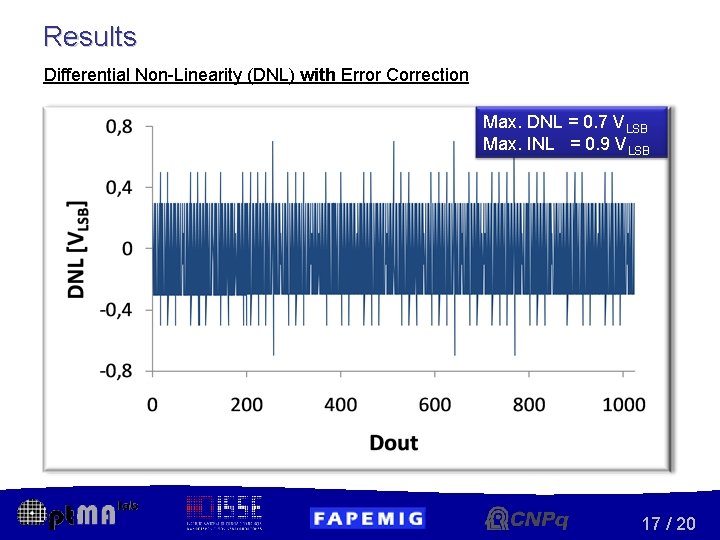

Results Differential Non-Linearity (DNL) with Error Correction Max. DNL = 0. 7 VLSB Max. INL = 0. 9 VLSB 17 / 20

Conclusion § Combination of two ADC concepts by Pipelined Successive Approximation Converter (PSAC) § Low power and moderate speed § Effective error correction through redundant comparator and foreground calibration § Future Work: – Improvement of the gain amplifier – Combination with ophthalmic sensor 18 / 20

Acknowledgements § This work was sponsored by: – CNPq – FAPEMIG – INCT-DISSE/CNPq § Thanks to: – Opt. MAlab crew – PPGEE / DEE / UFMG 19 / 20

THANK YOU! contacts: franksill@ufmg. br davies@ufmg. br 20 / 20

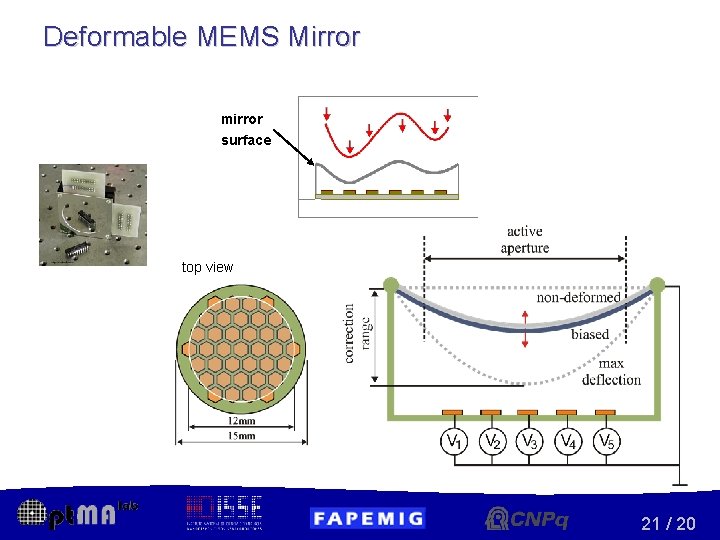

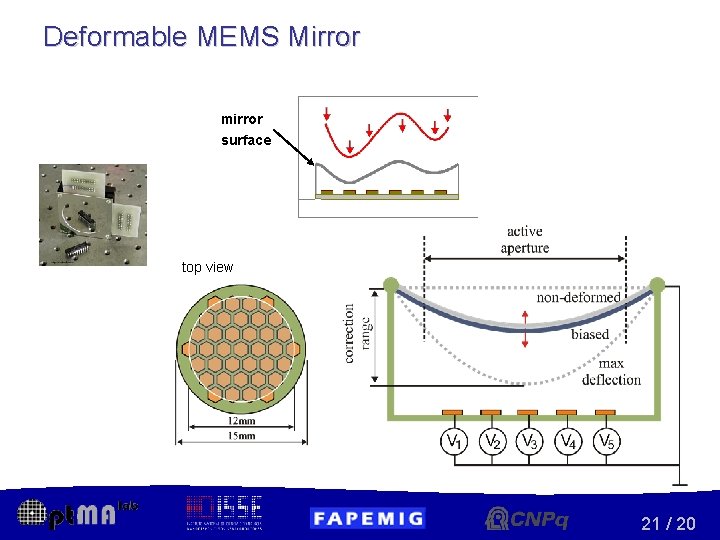

Deformable MEMS Mirror mirror surface top view 21 / 20

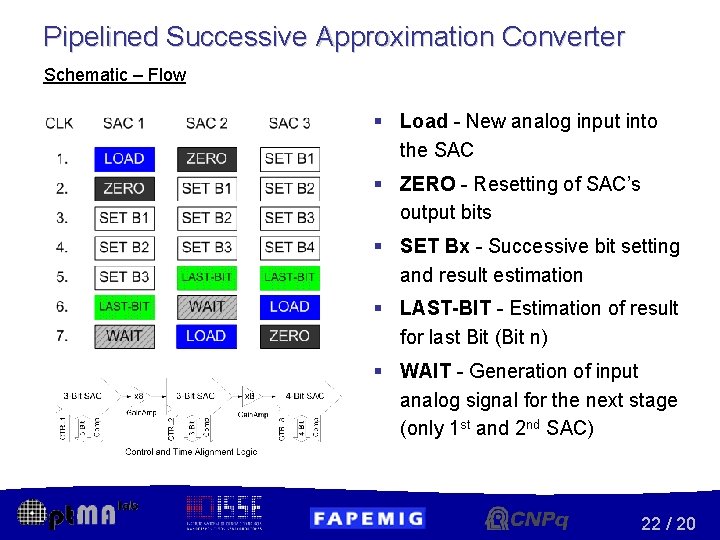

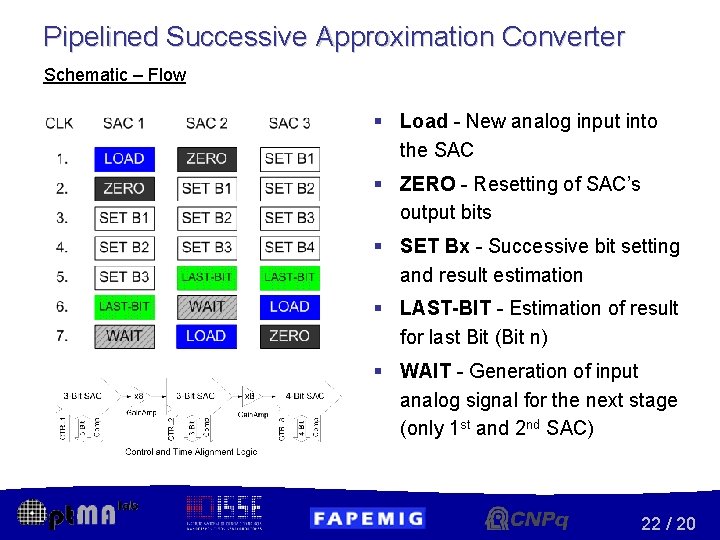

Pipelined Successive Approximation Converter Schematic – Flow § Load - New analog input into the SAC § ZERO - Resetting of SAC’s output bits § SET Bx - Successive bit setting and result estimation § LAST-BIT - Estimation of result for last Bit (Bit n) § WAIT - Generation of input analog signal for the next stage (only 1 st and 2 nd SAC) 22 / 20

Error Correction Techniques Redundant Comparator cont’d Dynamic Comparators Vin < 0 ? Vin > Vref ? Switches for generation of signal ADD 23 / 20

Error Correction Techniques Foreground Calibration - Principle Desired behavior Correction Vout (from PSAC) Vin Real behavior VPSAC (measured value) Linearized real behavior Vin (from ramp) 24 / 20

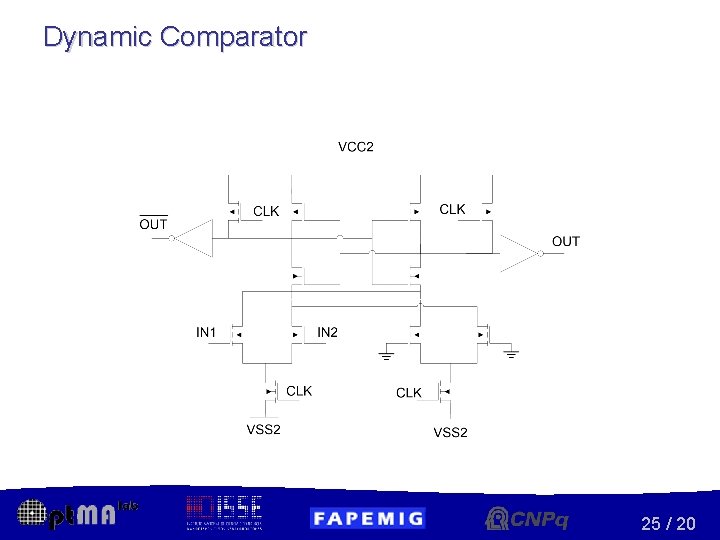

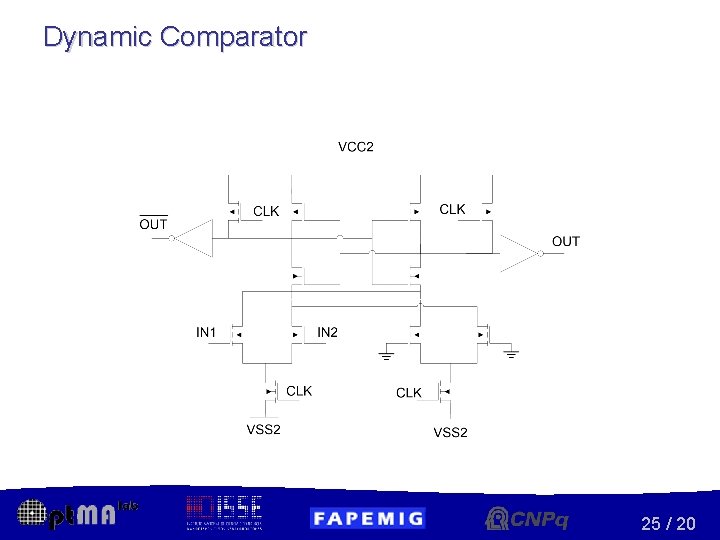

Dynamic Comparator 25 / 20