Pipeline transfer testing The purpose of pipeline transfer

- Slides: 21

Pipeline transfer testing

The purpose of pipeline transfer • increase the bandwidth for synchronous slave peripherals that require several cycles to return data for the first access, but can return data every cycle thereafter. • Only read is support in pipeline transfer.

The pipeline feature of AVALON • The bus transfer is splitting into two phase. Address phase and Data phase. • A master port initiates a transfer (i. e. fills the pipeline) by presenting the address during the address phase; a slave port fulfills the transfer by delivering the data during the data phase.

Wait state and pipeline latency • Wait state : determine the length of the address phase. slave issue the wait request by the WAITREQUEST signal. This will reduce throughput of the system. • Pipeline latency : determine the length of the data phase. This term means how many cycles can the slave return the data, although the slave can return one data per cycle thereafter.

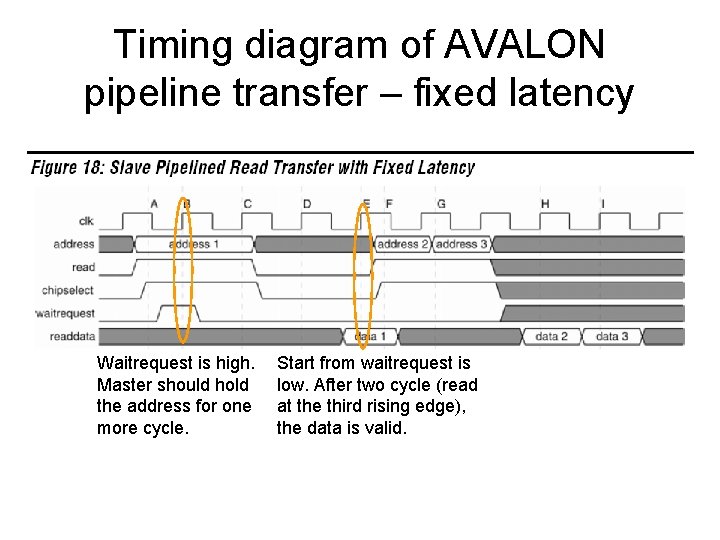

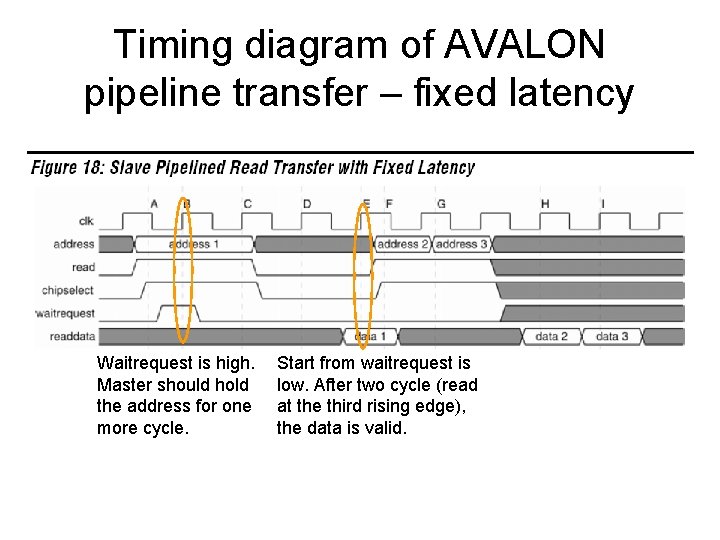

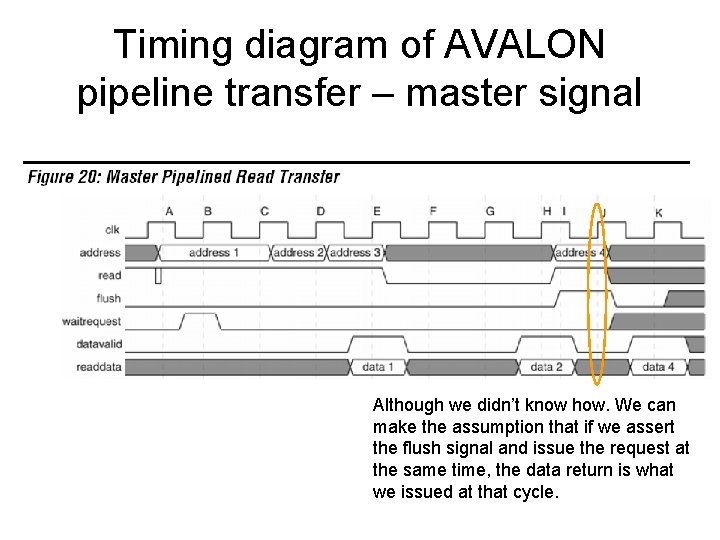

Timing diagram of AVALON pipeline transfer – fixed latency Waitrequest is high. Master should hold the address for one more cycle. Start from waitrequest is low. After two cycle (read at the third rising edge), the data is valid.

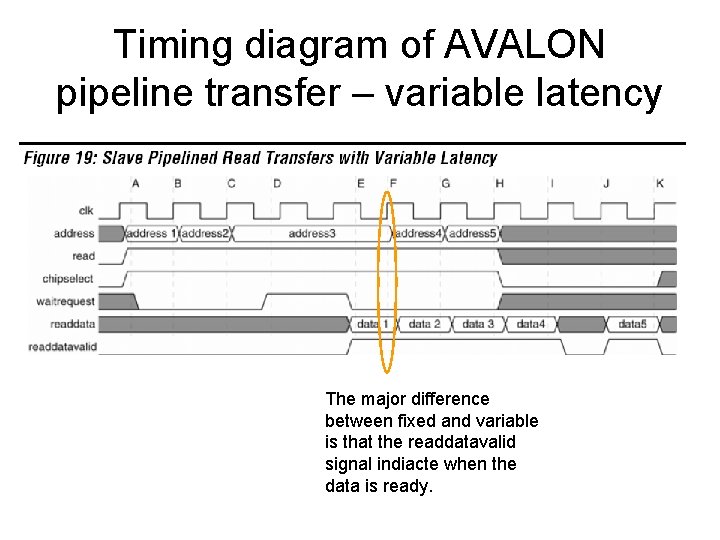

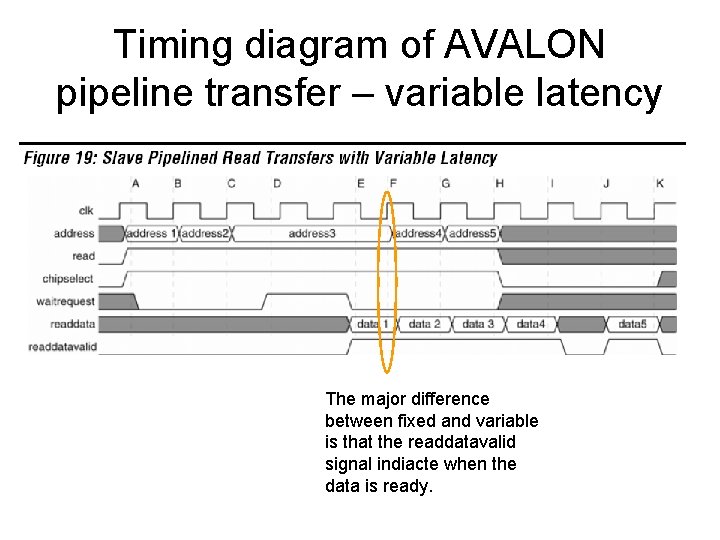

Timing diagram of AVALON pipeline transfer – variable latency The major difference between fixed and variable is that the readdatavalid signal indiacte when the data is ready.

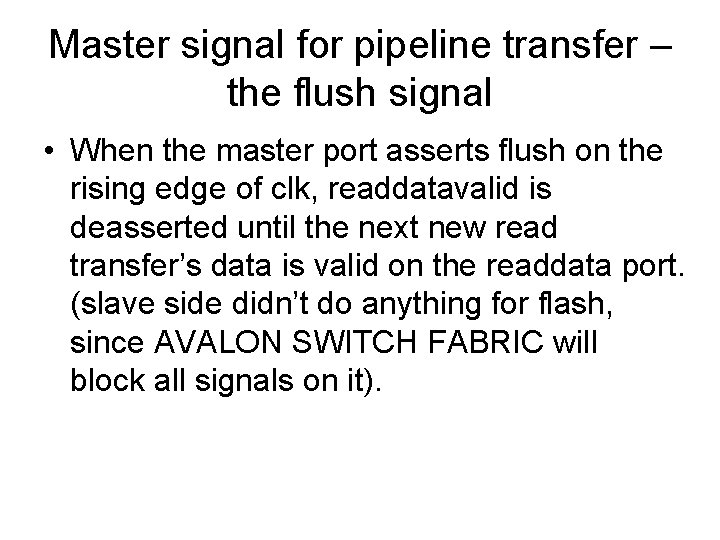

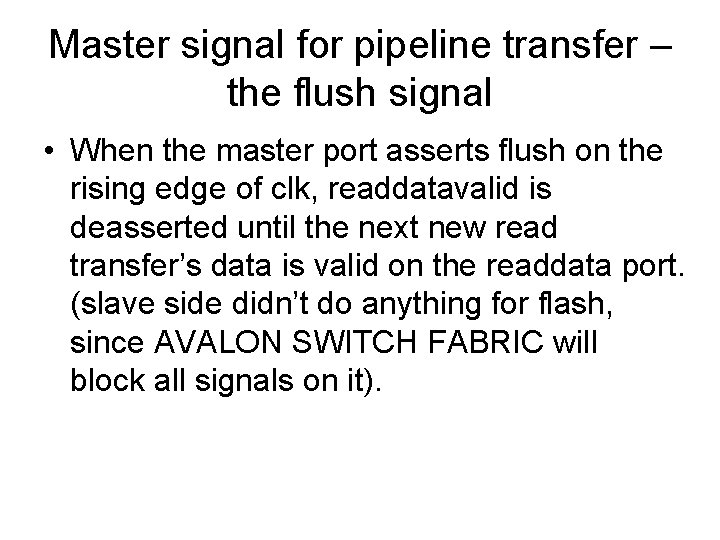

Master signal for pipeline transfer – the flush signal • When the master port asserts flush on the rising edge of clk, readdatavalid is deasserted until the next new read transfer’s data is valid on the readdata port. (slave side didn’t do anything for flash, since AVALON SWITCH FABRIC will block all signals on it).

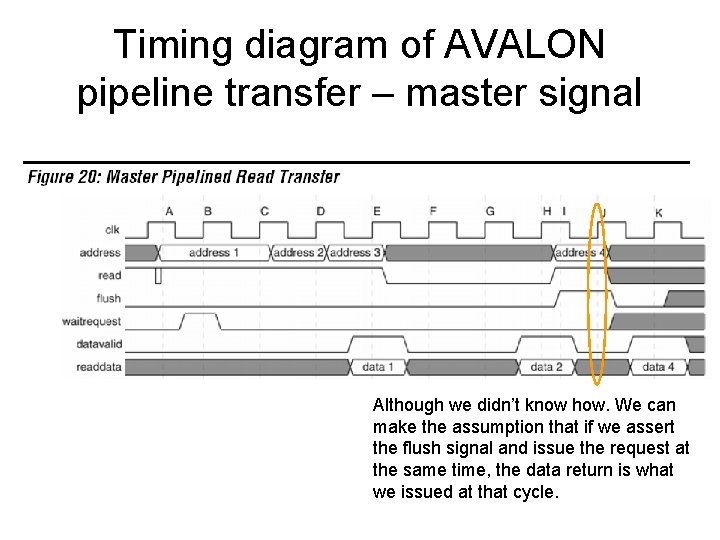

Timing diagram of AVALON pipeline transfer – master signal Although we didn’t know how. We can make the assumption that if we assert the flush signal and issue the request at the same time, the data return is what we issued at that cycle.

simple FIFO from software point of view

Data structure and signal required • An fifo_data_array (internal register arrays) • Read pointer and write pointer (internal register) • Read and readdata • Write and writedata • Empty and full signal

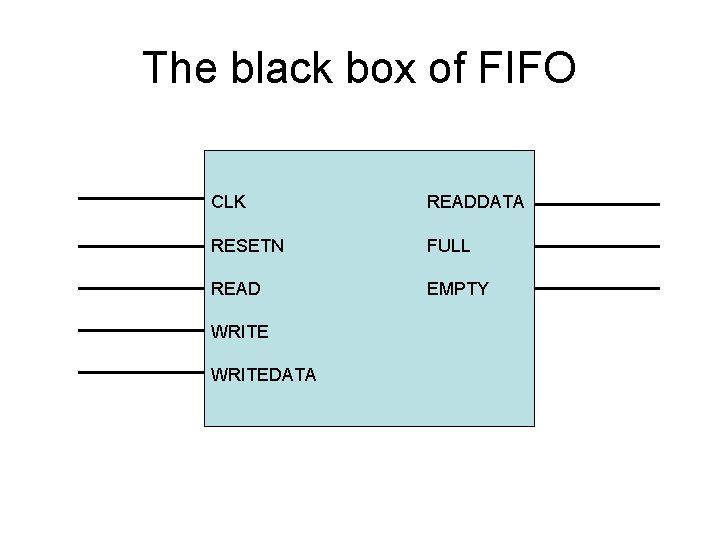

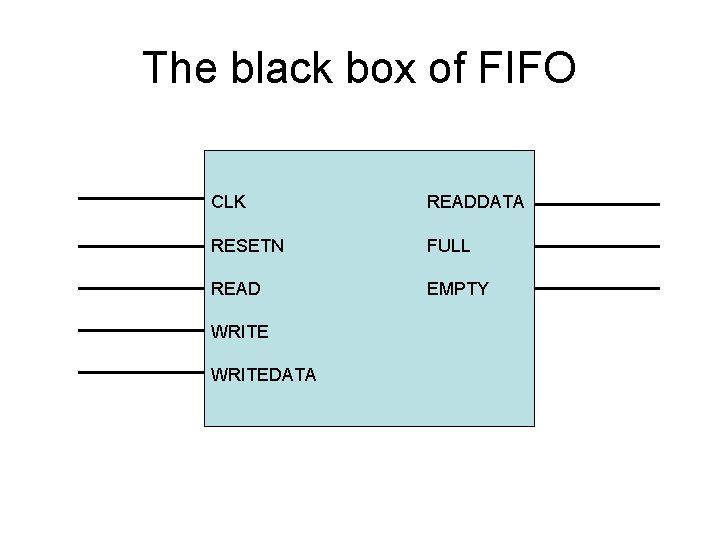

The black box of FIFO CLK READDATA RESETN FULL READ EMPTY WRITEDATA

Read and write operation • READ : once the read signals is assigned, the data which the rdptr point to is returned in the next positive edge. The rdptr is increased by 1. • WRITE : once the write signals and writedata is assigned, the data is write at the next positive edge. The wrptr is increased by 1.

Full and empty condition • After reset, the wrptr and rdptr = 0. • If wrptr == rdptr (which is the initial condition), empty is high. • If (wrptr + 1)%size == rdptr, then the fifo is full. • There is one entry that we can’t use.

Overflow protection • When the fifo is full, the write operation is ignored. • When the fifo is empty, the read operation is ignored. • The user of the fifo should detect the full and empty signal to decide whether a transaction should be issued or not.

Integration of pipeline and FIFO

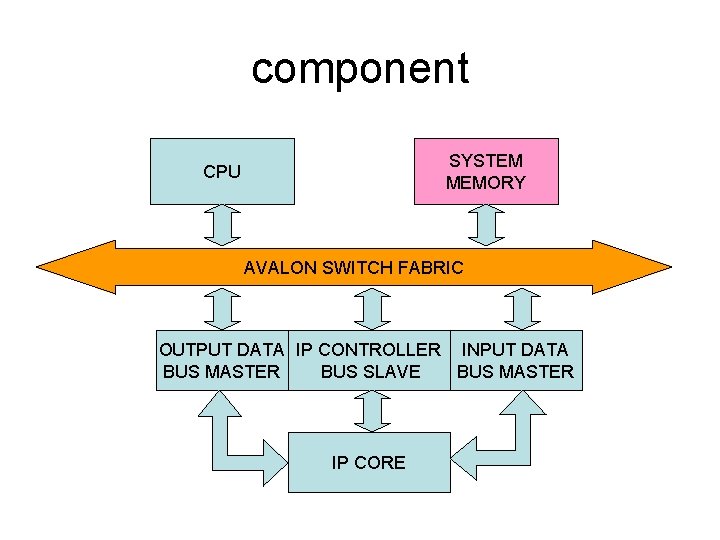

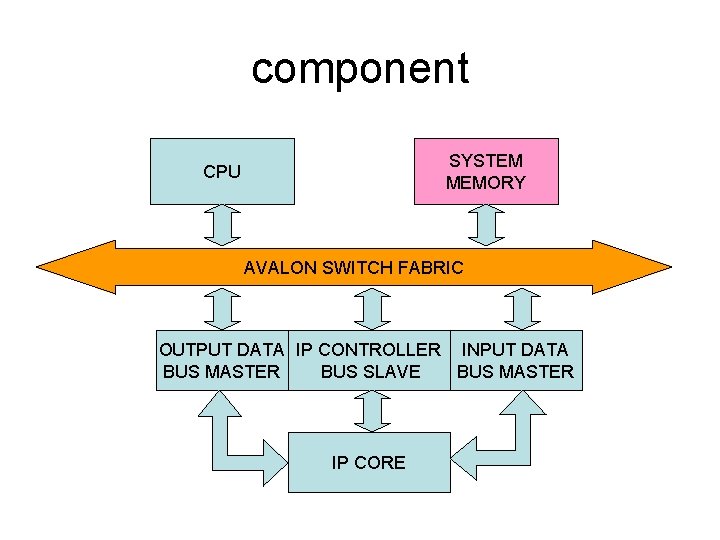

component SYSTEM MEMORY CPU AVALON SWITCH FABRIC OUTPUT DATA IP CONTROLLER INPUT DATA BUS MASTER BUS SLAVE BUS MASTER IP CORE

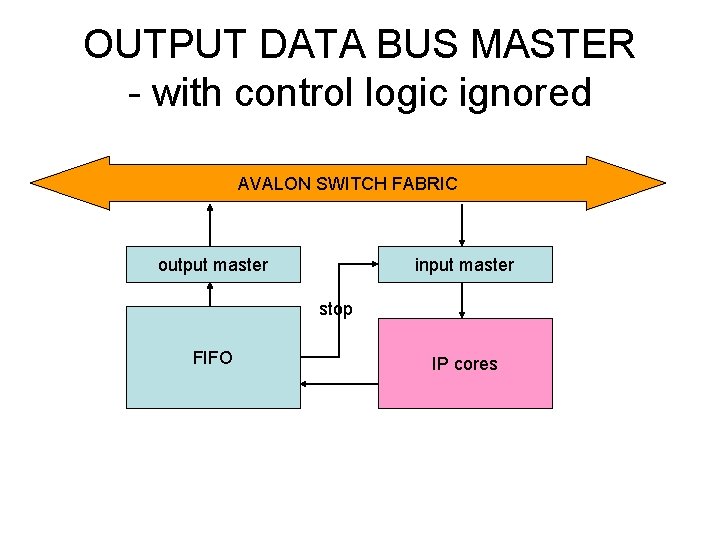

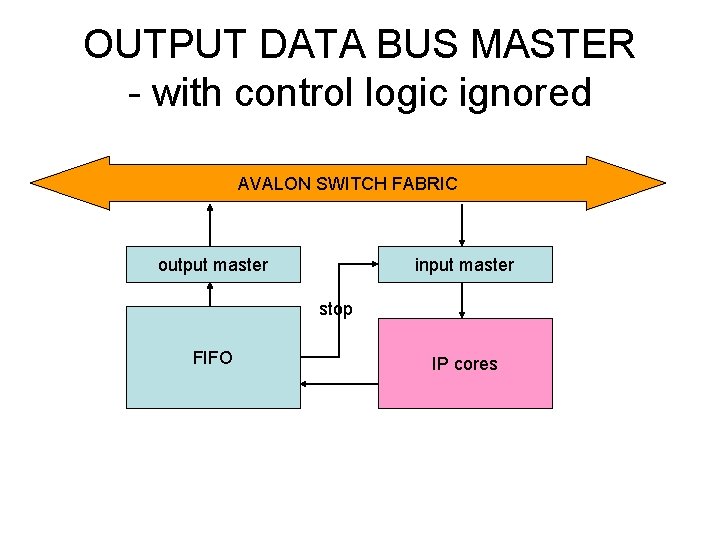

OUTPUT DATA BUS MASTER - with control logic ignored AVALON SWITCH FABRIC output master input master stop FIFO IP cores

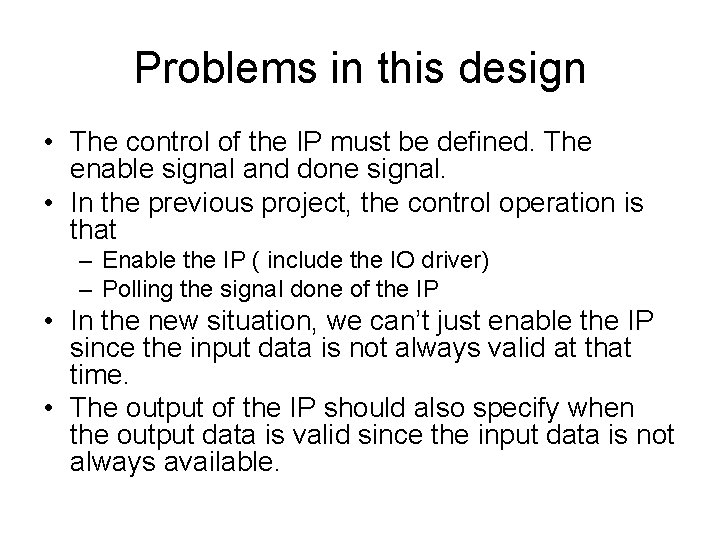

Problems in this design • The control of the IP must be defined. The enable signal and done signal. • In the previous project, the control operation is that – Enable the IP ( include the IO driver) – Polling the signal done of the IP • In the new situation, we can’t just enable the IP since the input data is not always valid at that time. • The output of the IP should also specify when the output data is valid since the input data is not always available.

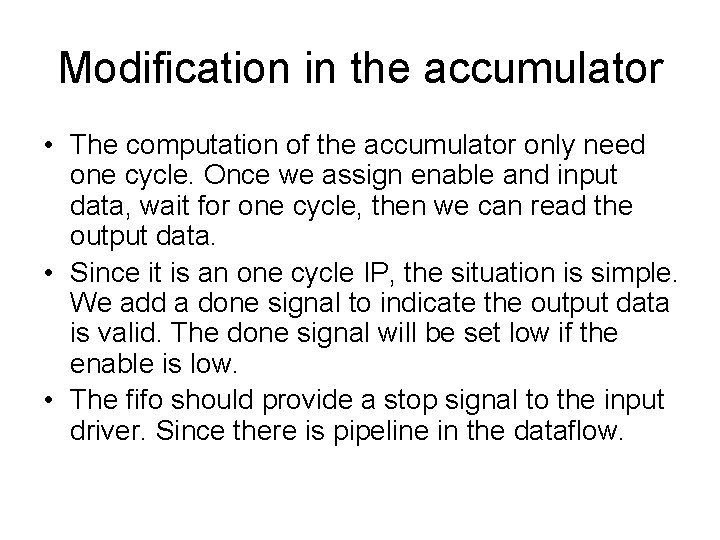

Modification in the accumulator • The computation of the accumulator only need one cycle. Once we assign enable and input data, wait for one cycle, then we can read the output data. • Since it is an one cycle IP, the situation is simple. We add a done signal to indicate the output data is valid. The done signal will be set low if the enable is low. • The fifo should provide a stop signal to the input driver. Since there is pipeline in the dataflow.

The difference between FIFO master with simple master • The old master must wait the write operation finish. • We solve this problem by using the FIFO at the write master side. • If the FIFO is full the input device of the IP must stop

Future work • This project didn’t use the concept of pipeline transfer. • If we want to use it one the read master, we have to add a FIFO in it. Also, the FIFO needs to provide the information of how many empty slots in this FIFO