Pipeline ADC CSE 598 A Project Proposal James

- Slides: 15

Pipeline ADC CSE 598 A Project Proposal James Yockey

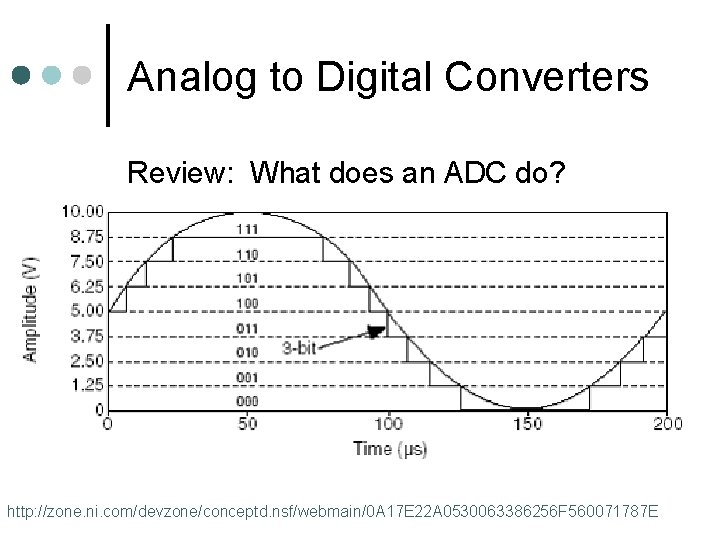

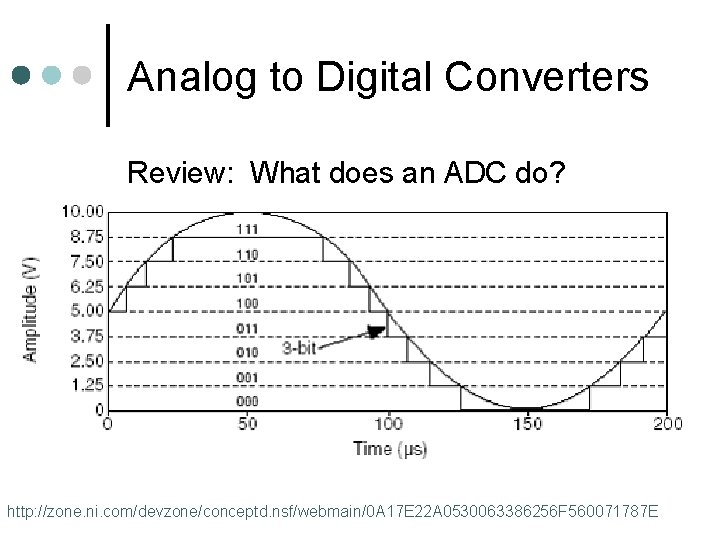

Analog to Digital Converters Review: What does an ADC do? http: //zone. ni. com/devzone/conceptd. nsf/webmain/0 A 17 E 22 A 0530063386256 F 560071787 E

Types of ADC Flash ¢ Pipeline ¢ Others… ¢

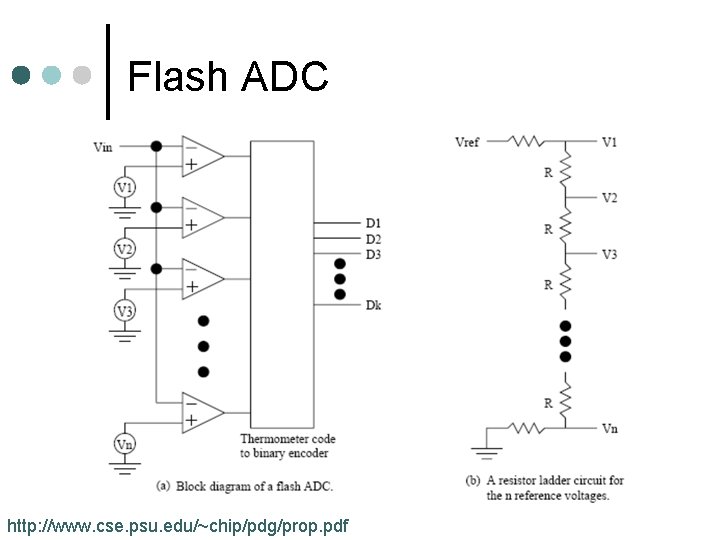

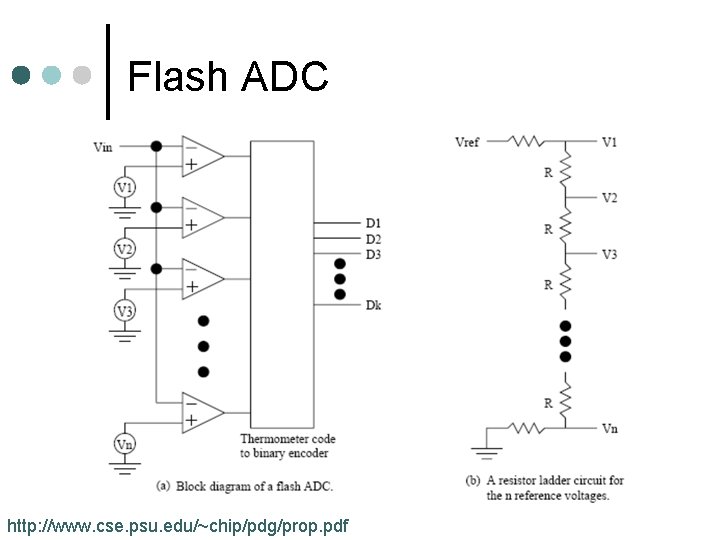

Flash ADC http: //www. cse. psu. edu/~chip/pdg/prop. pdf

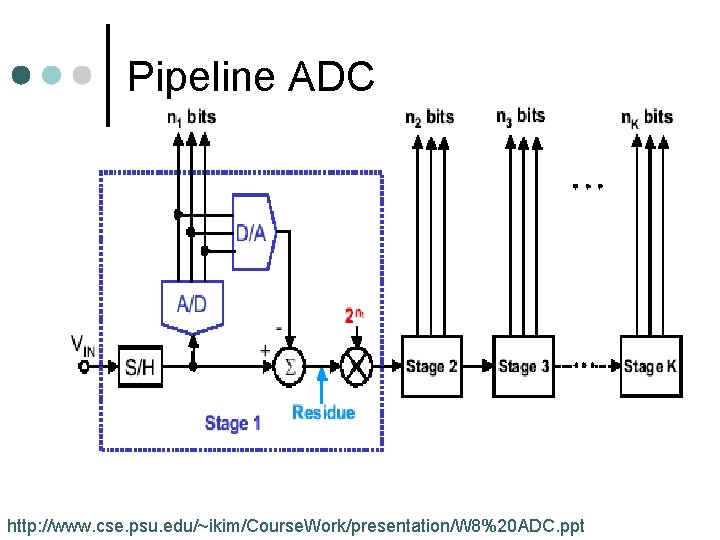

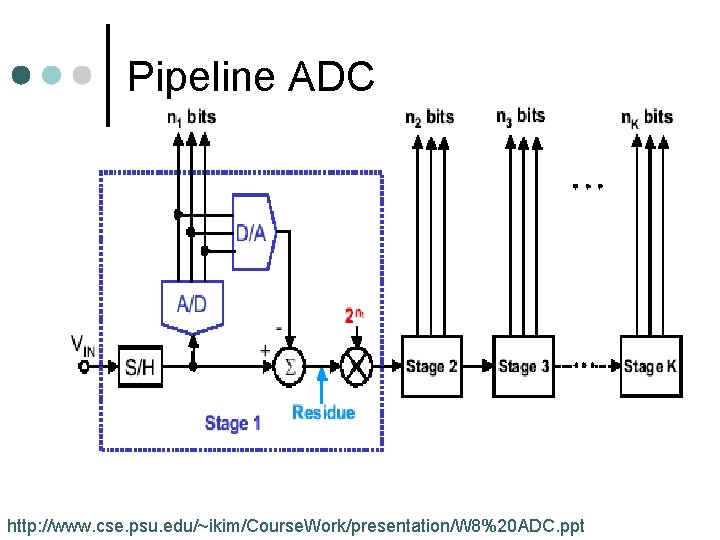

Pipeline ADC http: //www. cse. psu. edu/~ikim/Course. Work/presentation/W 8%20 ADC. ppt

Pipeline ADC (cont. ) Using two bits for a signal that can vary from 0 to 5 V, we can divide it into 4 regions. For example: 00 = 0 to 1. 25 01 = 1. 26 to 2. 5 10 = 2. 6 to 3. 75 11 = 3. 76 to 5. 0

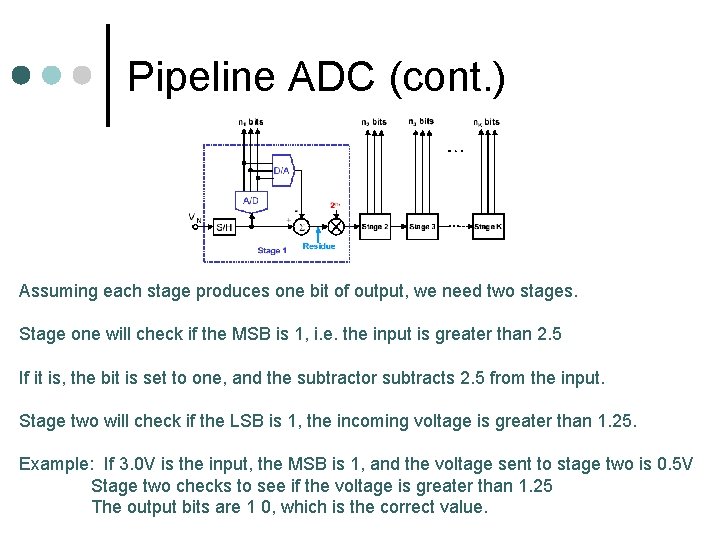

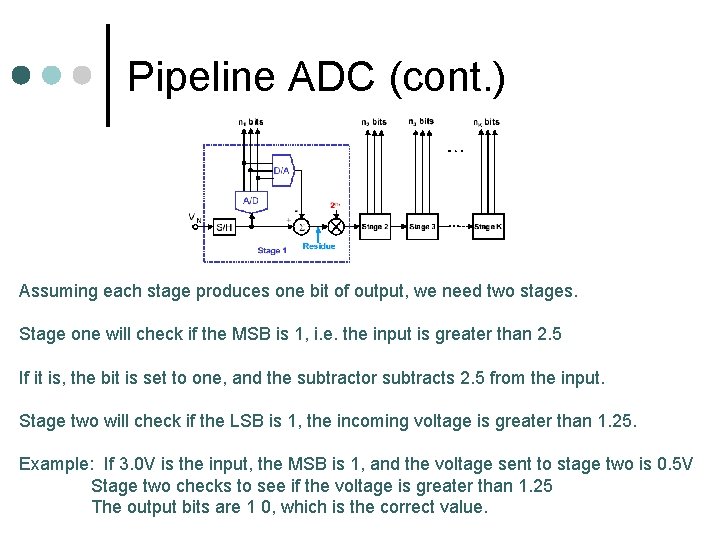

Pipeline ADC (cont. ) Assuming each stage produces one bit of output, we need two stages. Stage one will check if the MSB is 1, i. e. the input is greater than 2. 5 If it is, the bit is set to one, and the subtractor subtracts 2. 5 from the input. Stage two will check if the LSB is 1, the incoming voltage is greater than 1. 25. Example: If 3. 0 V is the input, the MSB is 1, and the voltage sent to stage two is 0. 5 V Stage two checks to see if the voltage is greater than 1. 25 The output bits are 1 0, which is the correct value.

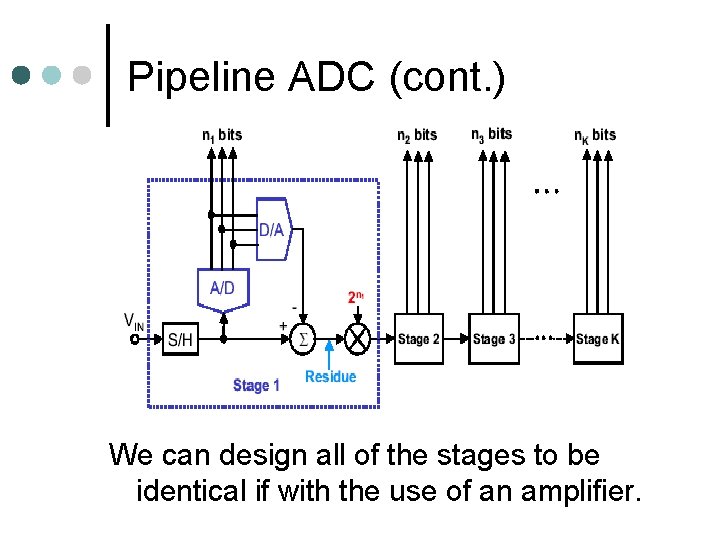

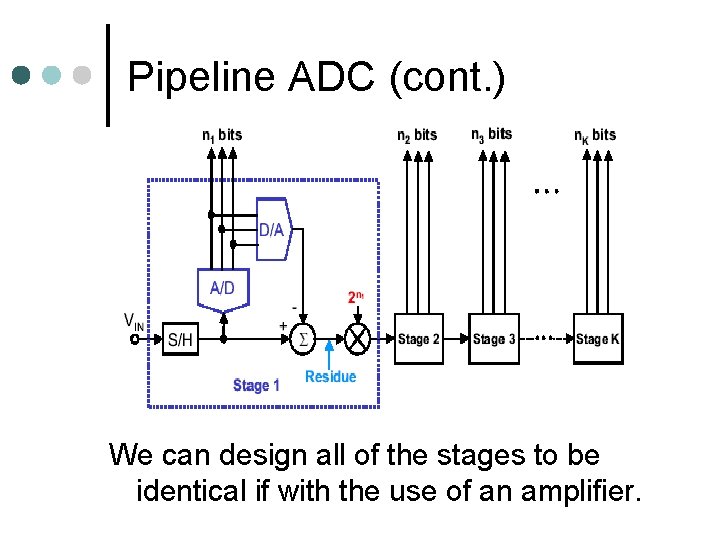

Pipeline ADC (cont. ) We can design all of the stages to be identical if with the use of an amplifier.

Other types of ADC Folding ¢ Time-interleaved ¢ Algorithmic ¢ Interpolating ¢ Integrating-type ¢ More information can be found at: http: //www. cse. psu. edu/~ikim/Course. Work/presentation/W 8%20 ADC. ppt

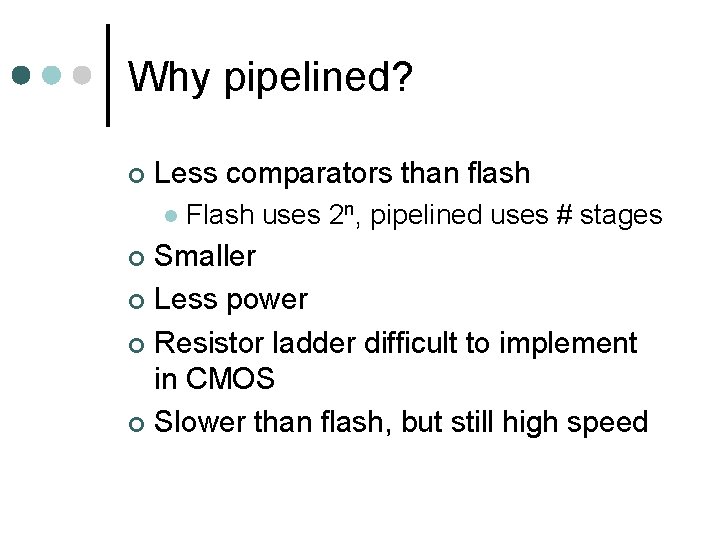

Why pipelined? ¢ Less comparators than flash l Flash uses 2 n, pipelined uses # stages Smaller ¢ Less power ¢ Resistor ladder difficult to implement in CMOS ¢ Slower than flash, but still high speed ¢

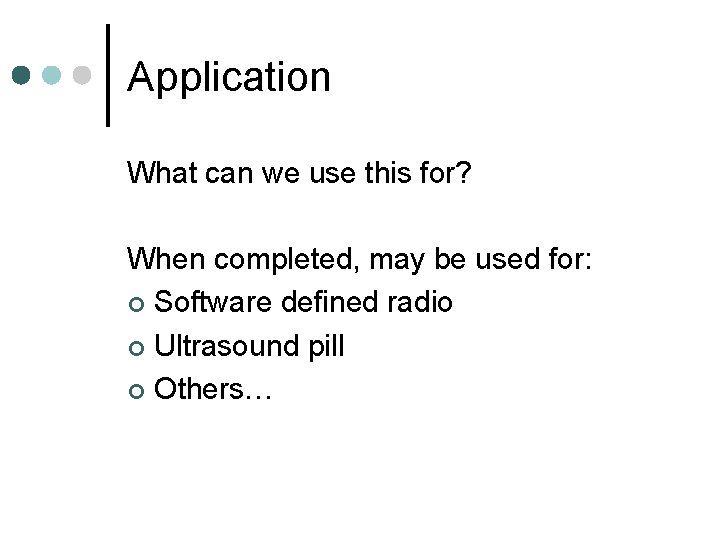

Application What can we use this for? When completed, may be used for: ¢ Software defined radio ¢ Ultrasound pill ¢ Others…

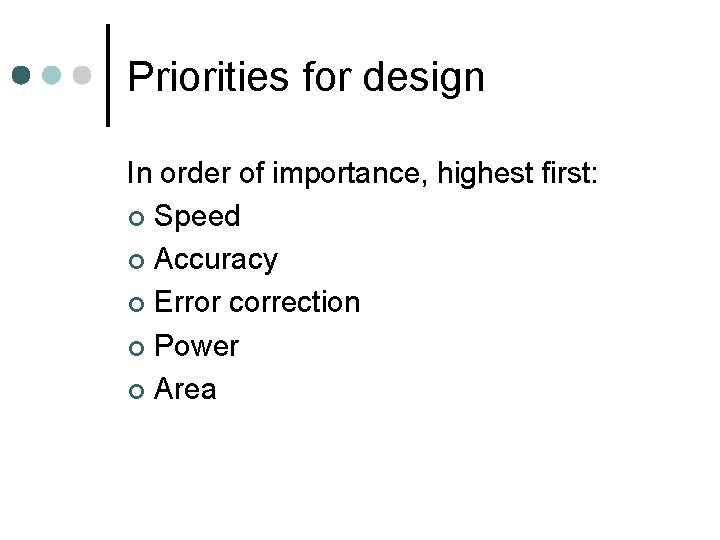

Priorities for design In order of importance, highest first: ¢ Speed ¢ Accuracy ¢ Error correction ¢ Power ¢ Area

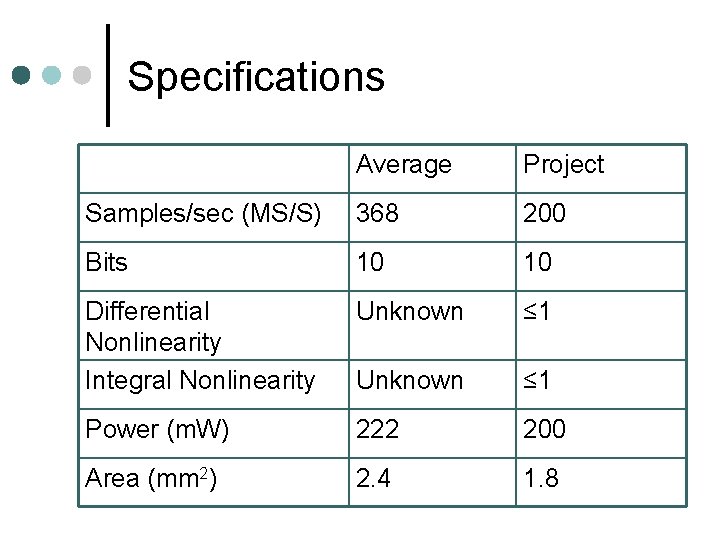

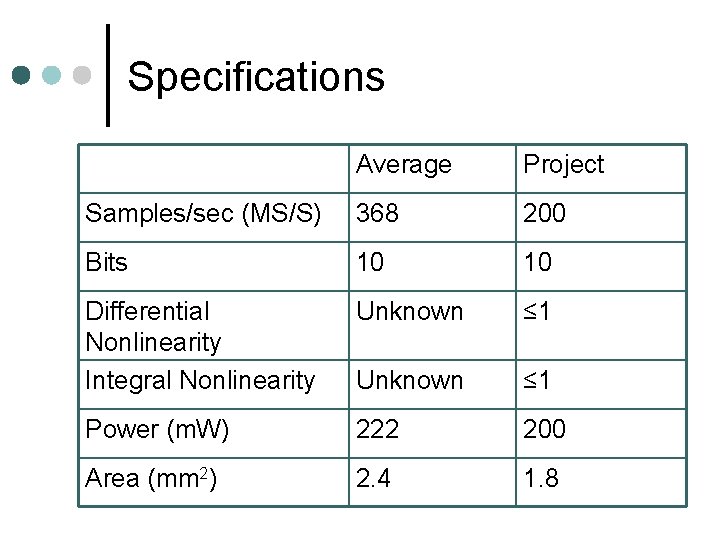

Specifications Average Project Samples/sec (MS/S) 368 200 Bits 10 10 Differential Nonlinearity Integral Nonlinearity Unknown ≤ 1 Power (m. W) 222 200 Area (mm 2) 2. 4 1. 8

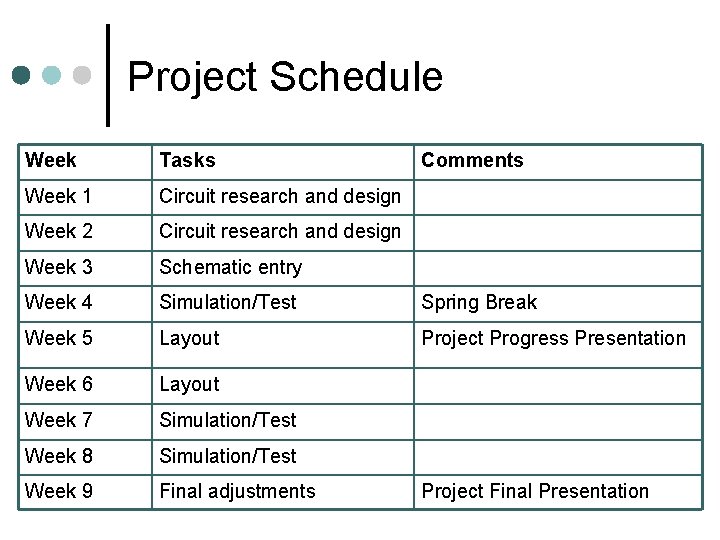

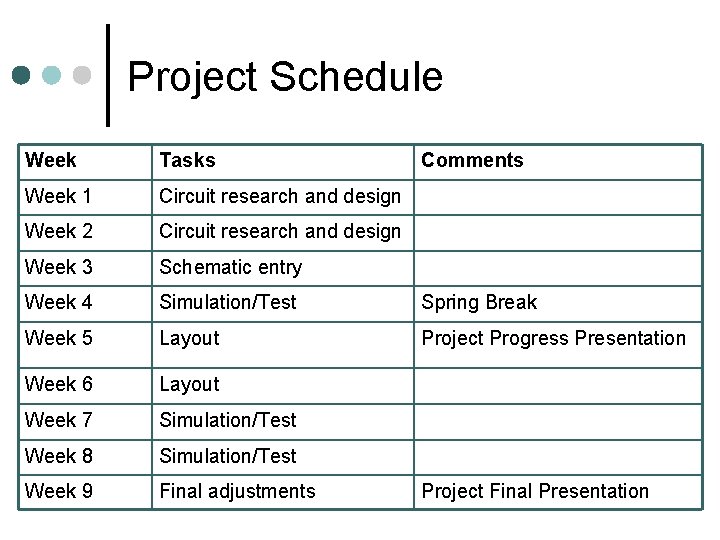

Project Schedule Week Tasks Comments Week 1 Circuit research and design Week 2 Circuit research and design Week 3 Schematic entry Week 4 Simulation/Test Spring Break Week 5 Layout Project Progress Presentation Week 6 Layout Week 7 Simulation/Test Week 8 Simulation/Test Week 9 Final adjustments Project Final Presentation

Conclusion Any comments or questions?