PICOBLAZE RESUMEN UNIDAD 5 Procesadores Embebidos de 8

PICOBLAZE RESUMEN

UNIDAD 5: Procesadores Embebidos de 8 bits 5. 1 Introducción 5. 2 Arquitectura Picoblaze 5. 3 Programación en ensamblador Picoblaze 5. 4 Manejo de interrupciones

Picoblaze � Microcontrolador 8 bits � Empotrado en un FPGA Xilinx � Soft core � Optimizado ocupa 200 celdas lógicas � Menos del 5% Spartan 3 s 200 Aplicaciones � Debido a que el desarrollo del software es usualmente mas fácil que crear hardware a la medida, la opción de un microcontrolador es preferida para aplicaciones no criticas en el tiempo. � Picoblaze requiere 2 ciclos para completar una instrucción � Si el reloj del sistema es de 50 MHz, Picoblaze ejecuta 25 millones de instrucciones por segundo

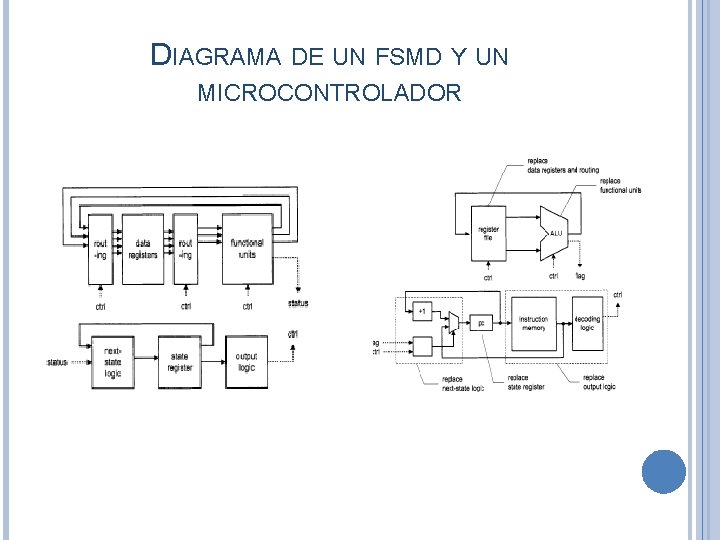

DIAGRAMA DE UN FSMD Y UN MICROCONTROLADOR

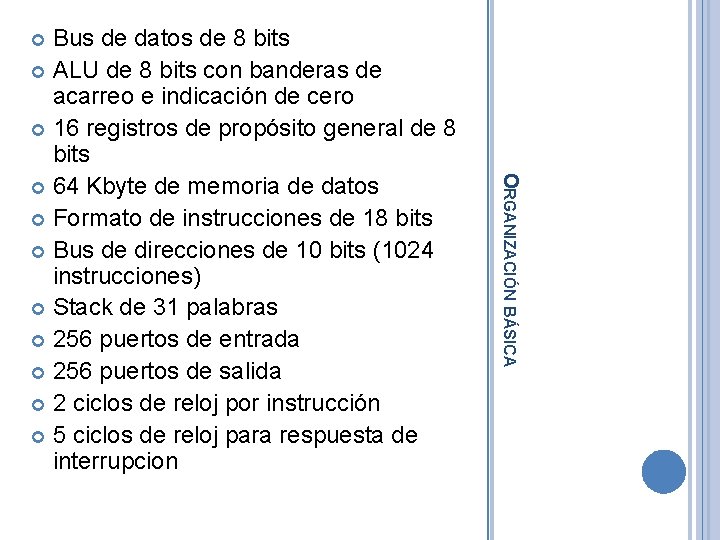

Bus de datos de 8 bits ALU de 8 bits con banderas de acarreo e indicación de cero 16 registros de propósito general de 8 bits 64 Kbyte de memoria de datos Formato de instrucciones de 18 bits Bus de direcciones de 10 bits (1024 instrucciones) Stack de 31 palabras 256 puertos de entrada 256 puertos de salida 2 ciclos de reloj por instrucción 5 ciclos de reloj para respuesta de interrupcion ORGANIZACIÓN BÁSICA

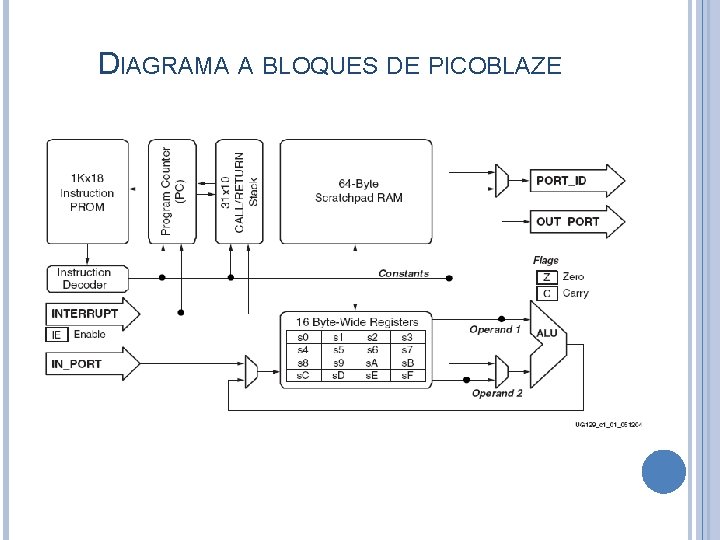

DIAGRAMA A BLOQUES DE PICOBLAZE

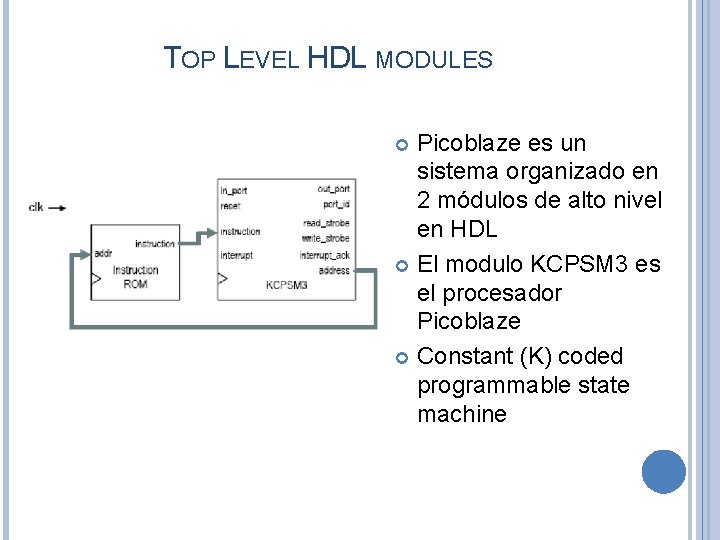

TOP LEVEL HDL MODULES Picoblaze es un sistema organizado en 2 módulos de alto nivel en HDL El modulo KCPSM 3 es el procesador Picoblaze Constant (K) coded programmable state machine

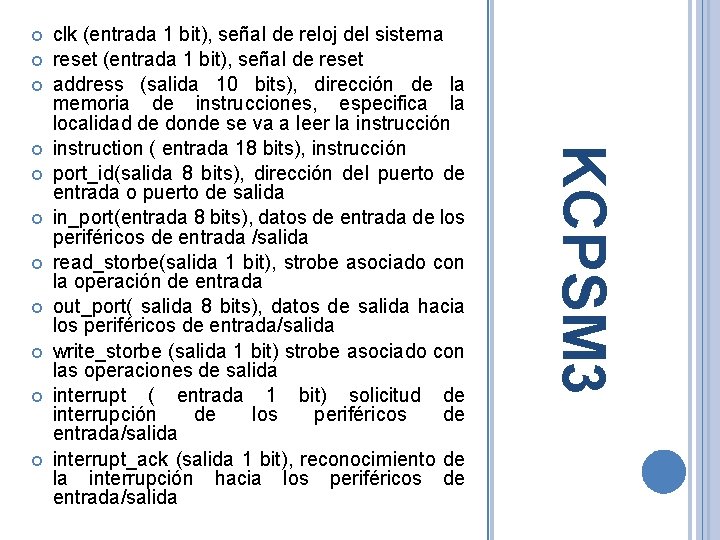

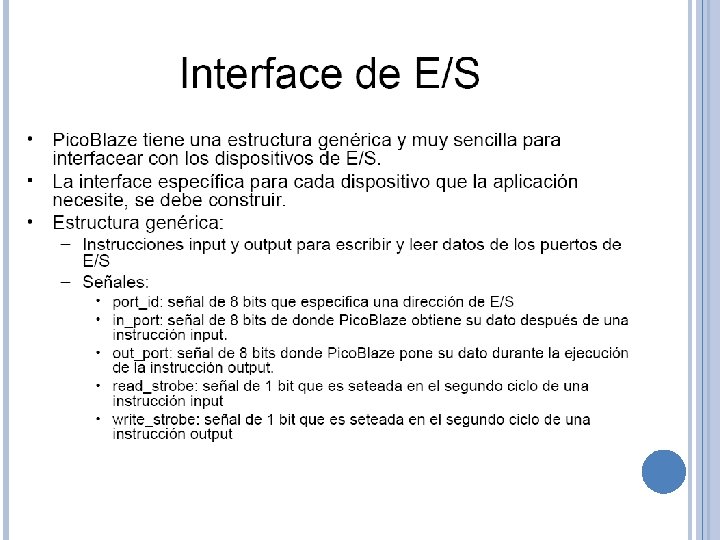

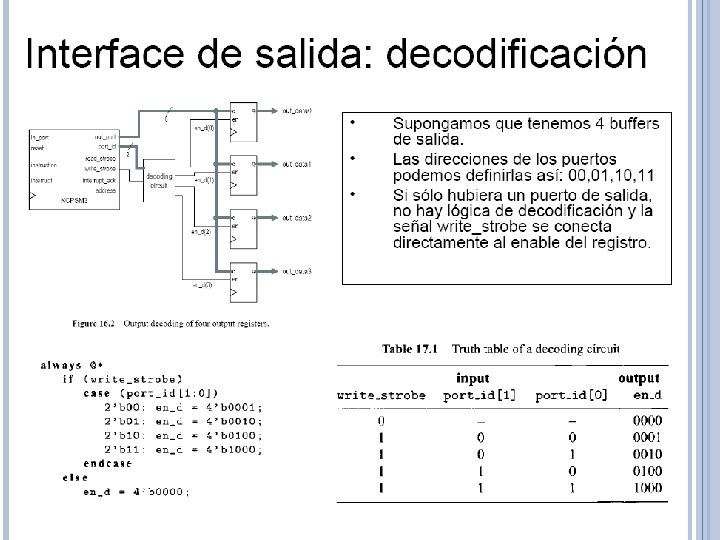

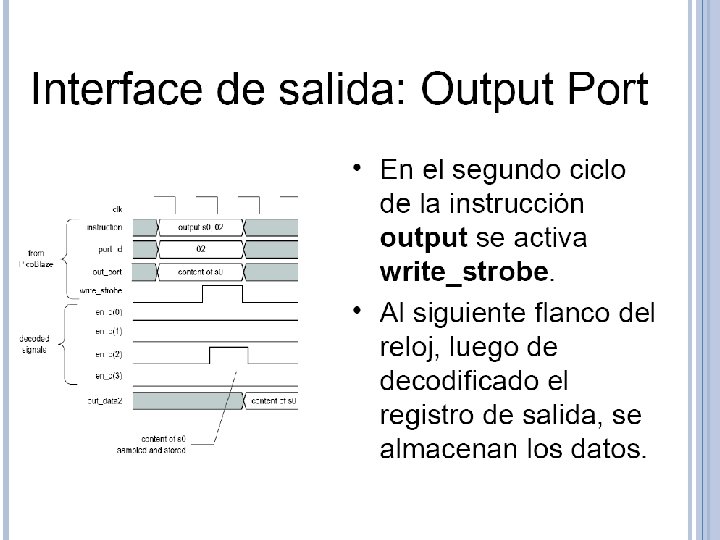

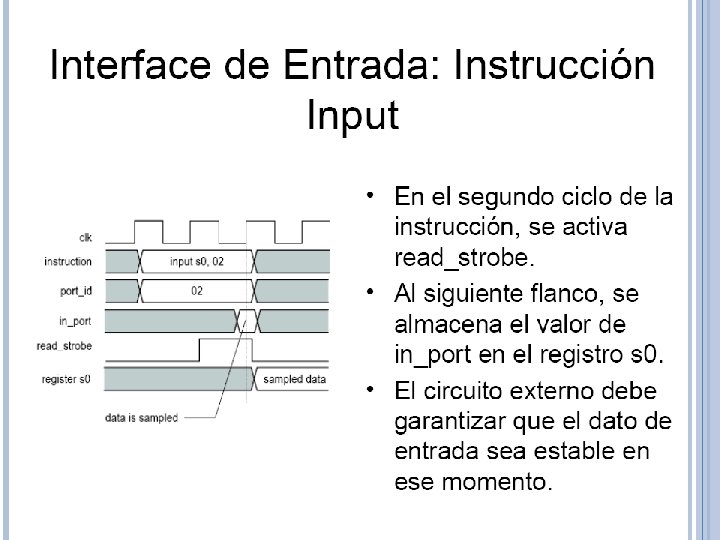

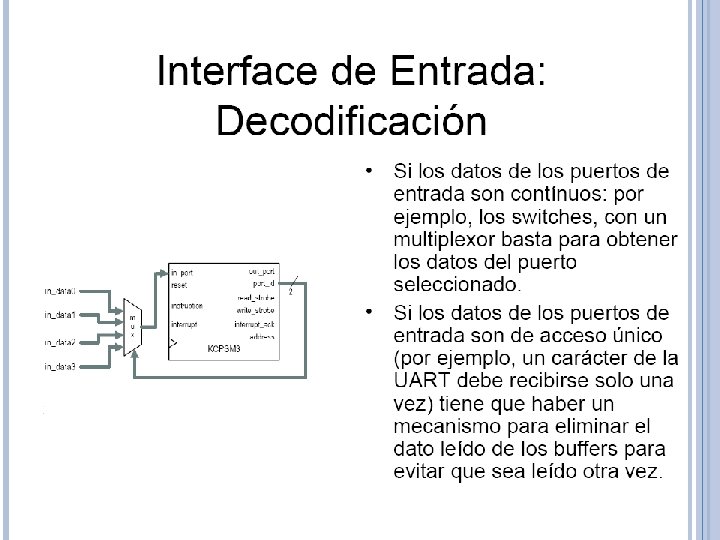

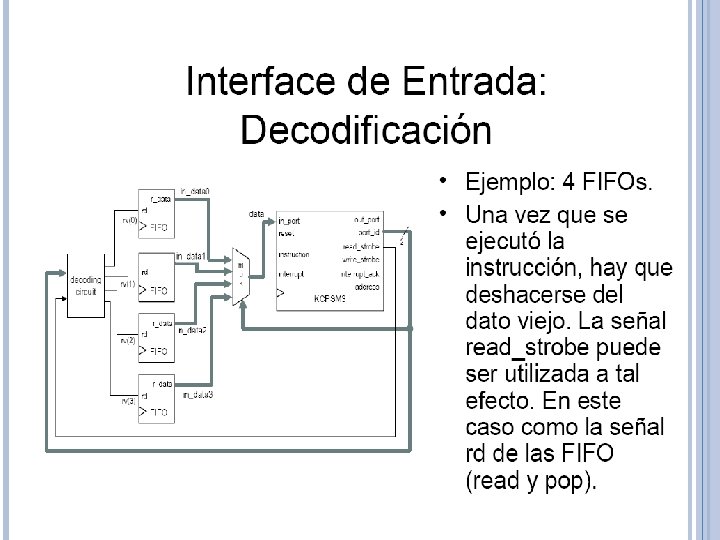

KCPSM 3 clk (entrada 1 bit), señal de reloj del sistema reset (entrada 1 bit), señal de reset address (salida 10 bits), dirección de la memoria de instrucciones, especifica la localidad de donde se va a leer la instrucción instruction ( entrada 18 bits), instrucción port_id(salida 8 bits), dirección del puerto de entrada o puerto de salida in_port(entrada 8 bits), datos de entrada de los periféricos de entrada /salida read_storbe(salida 1 bit), strobe asociado con la operación de entrada out_port( salida 8 bits), datos de salida hacia los periféricos de entrada/salida write_storbe (salida 1 bit) strobe asociado con las operaciones de salida interrupt ( entrada 1 bit) solicitud de interrupción de los periféricos de entrada/salida interrupt_ack (salida 1 bit), reconocimiento de la interrupción hacia los periféricos de entrada/salida

El segundo modulo es para la memoria de instrucciones Durante el desarrollo usualmente almacenamos el código ensamblado en la memoria y se configura como una ROM en el lenguaje de descripción de hardware.

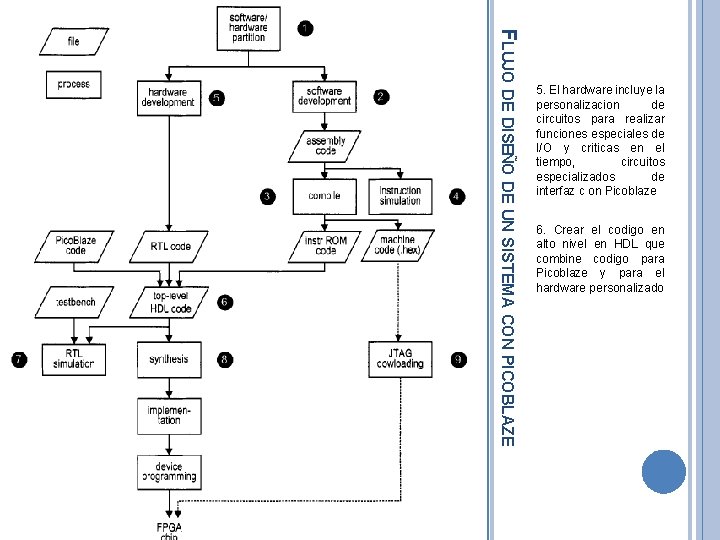

FLUJO DE DISEÑO DE UN SISTEMA CON PICOBLAZE 5. El hardware incluye la personalizacion de circuitos para realizar funciones especiales de I/O y criticas en el tiempo, circuitos especializados de interfaz c on Picoblaze 6. Crear el codigo en alto nivel en HDL que combine codigo para Picoblaze y para el hardware personalizado

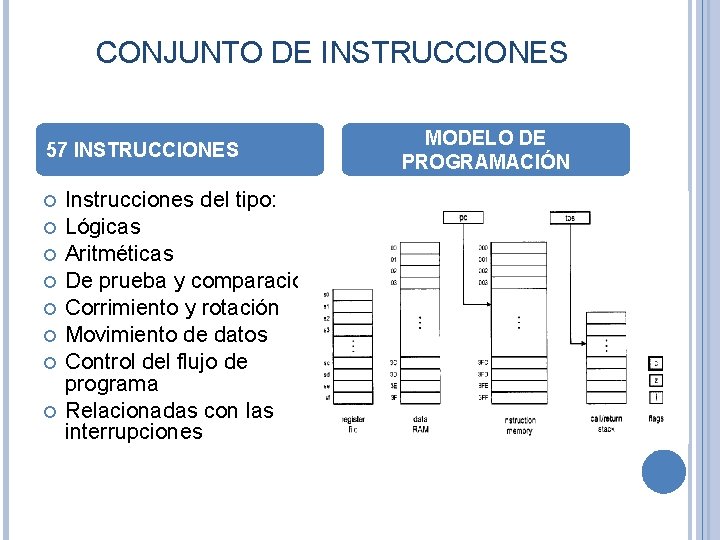

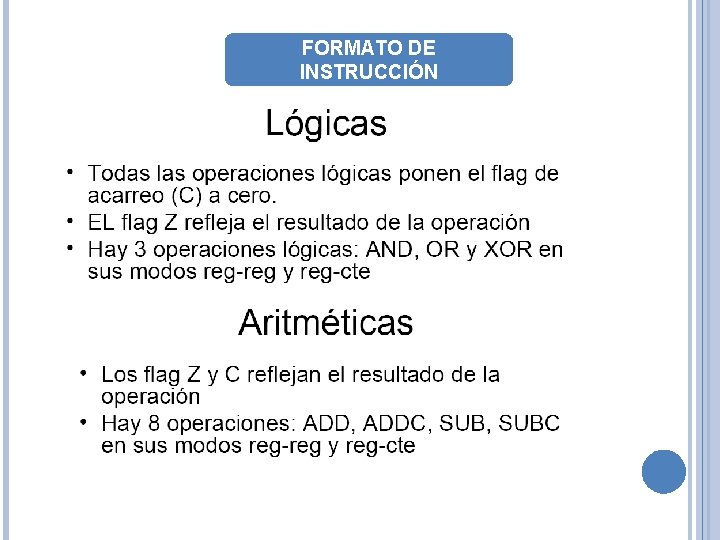

CONJUNTO DE INSTRUCCIONES 57 INSTRUCCIONES Instrucciones del tipo: Lógicas Aritméticas De prueba y comparación Corrimiento y rotación Movimiento de datos Control del flujo de programa Relacionadas con las interrupciones MODELO DE PROGRAMACIÓN

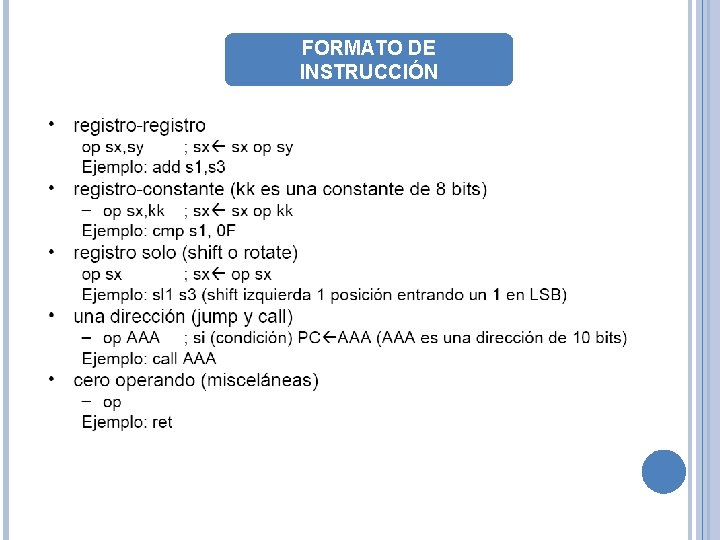

FORMATO DE INSTRUCCIÓN

FORMATO DE INSTRUCCIÓN

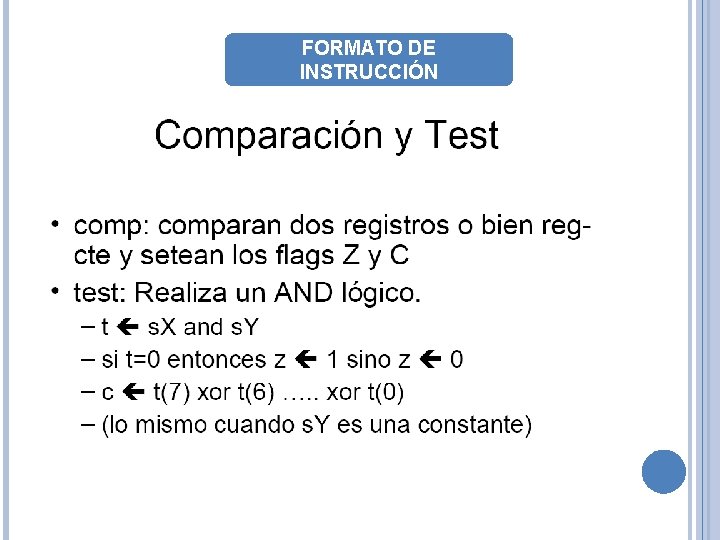

FORMATO DE INSTRUCCIÓN

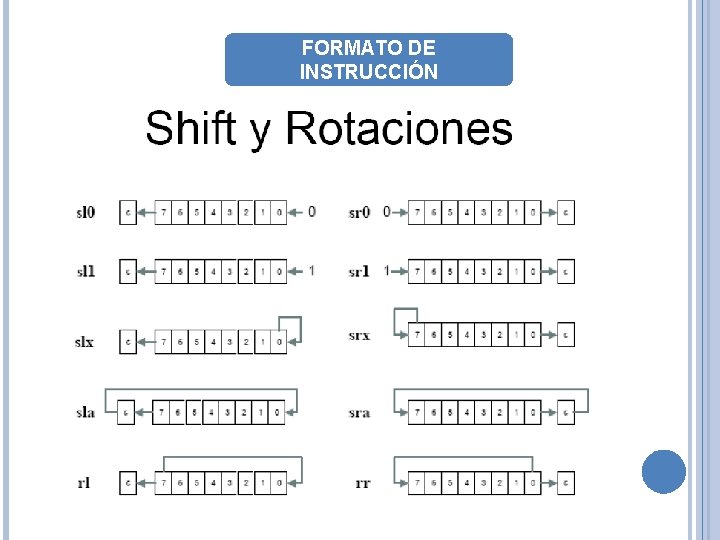

FORMATO DE INSTRUCCIÓN

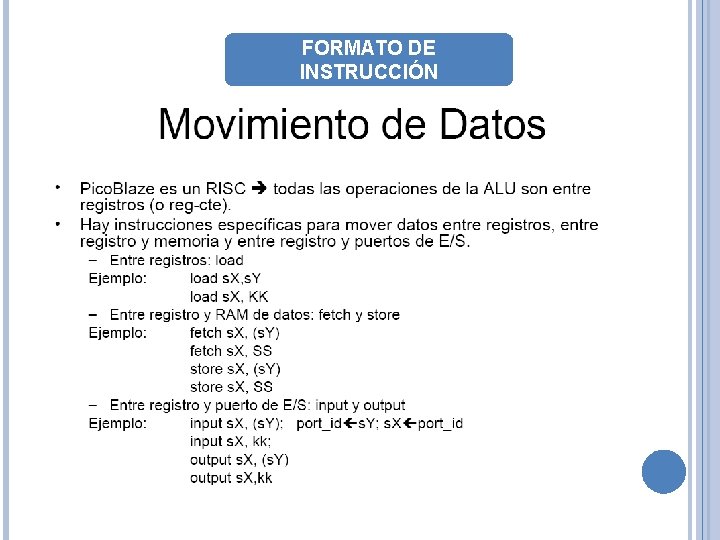

FORMATO DE INSTRUCCIÓN

FORMATO DE INSTRUCCIÓN

FORMATO DE INSTRUCCIÓN

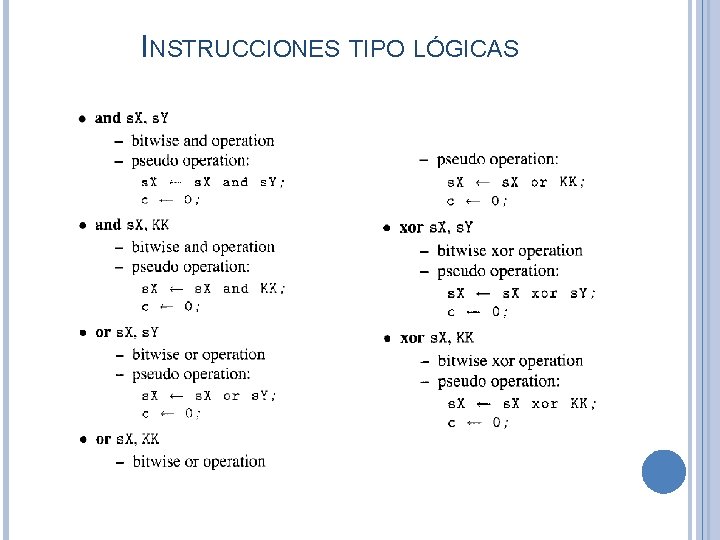

INSTRUCCIONES TIPO LÓGICAS

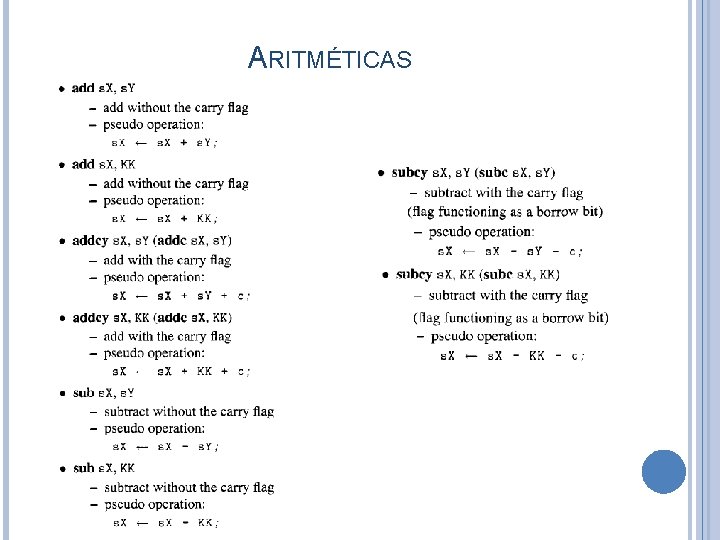

ARITMÉTICAS

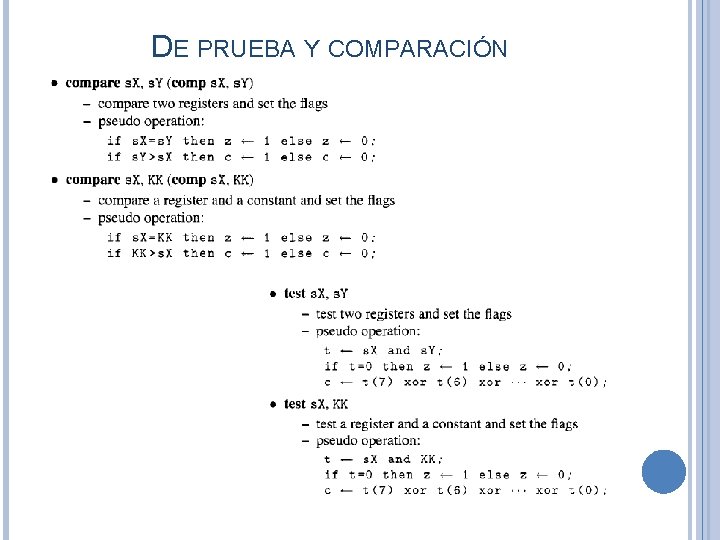

DE PRUEBA Y COMPARACIÓN

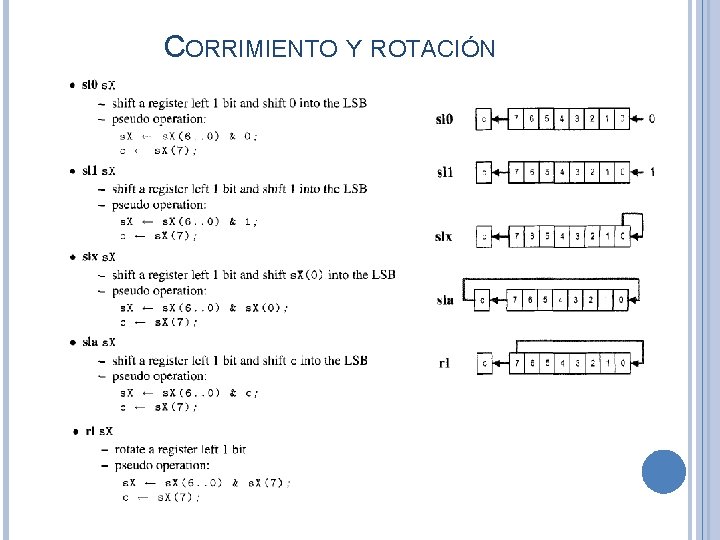

CORRIMIENTO Y ROTACIÓN

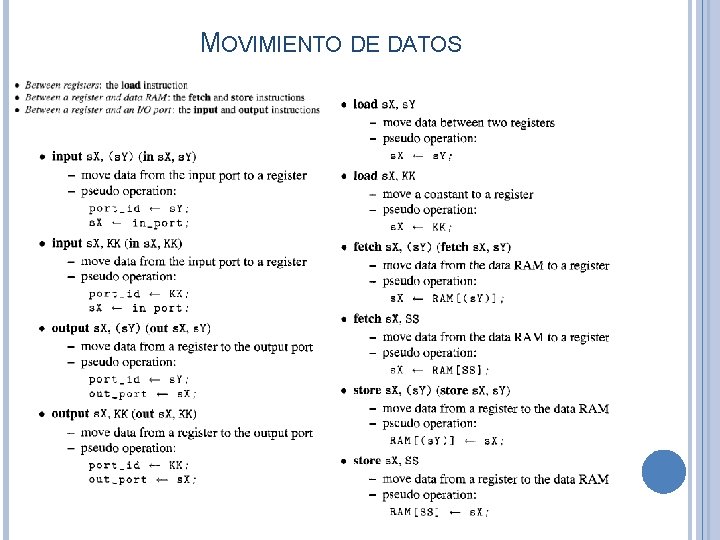

MOVIMIENTO DE DATOS

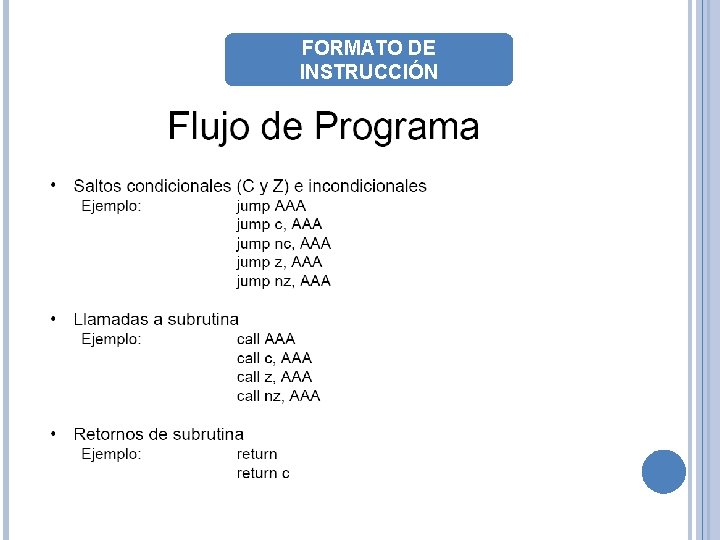

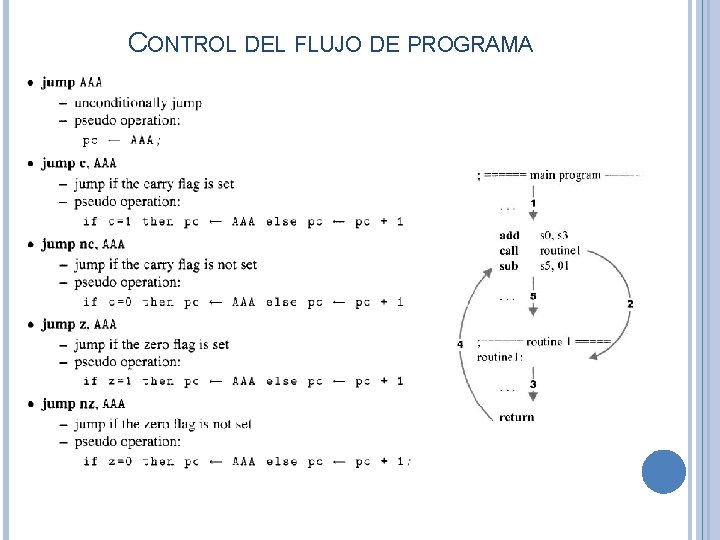

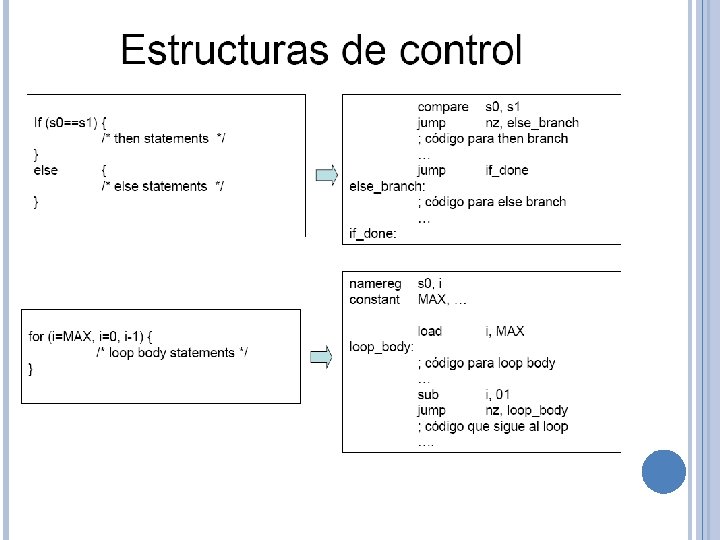

CONTROL DEL FLUJO DE PROGRAMA

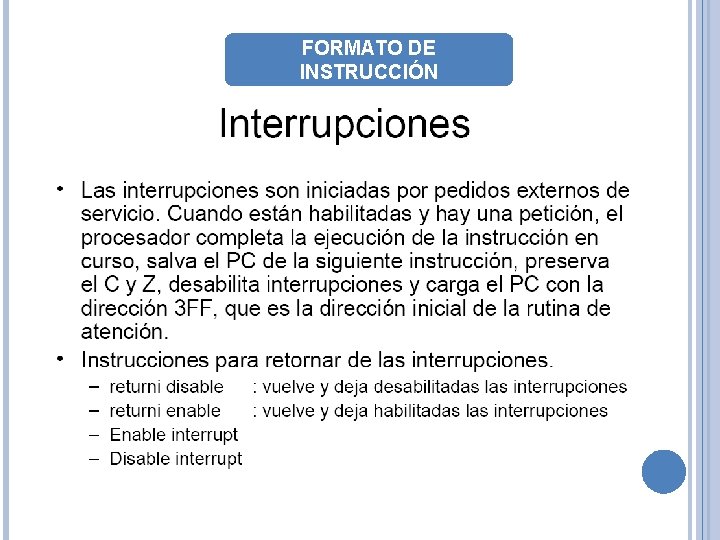

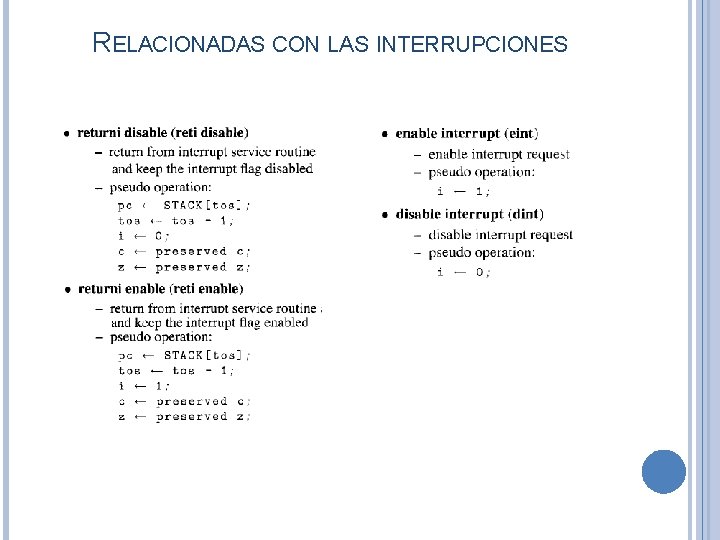

RELACIONADAS CON LAS INTERRUPCIONES

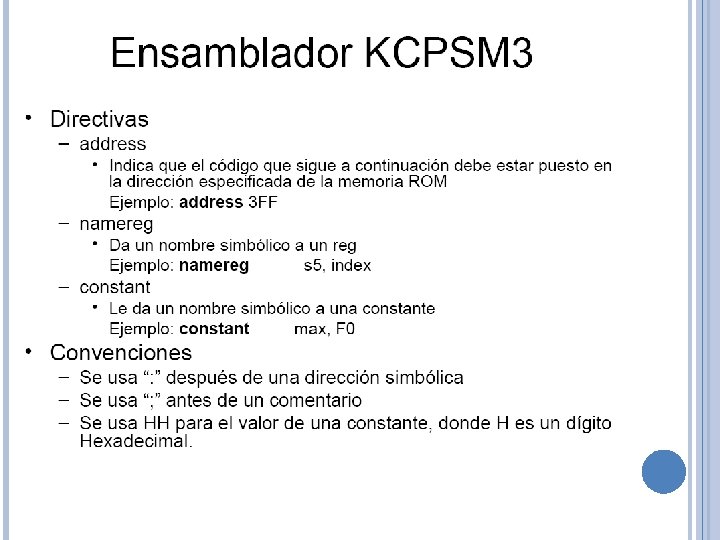

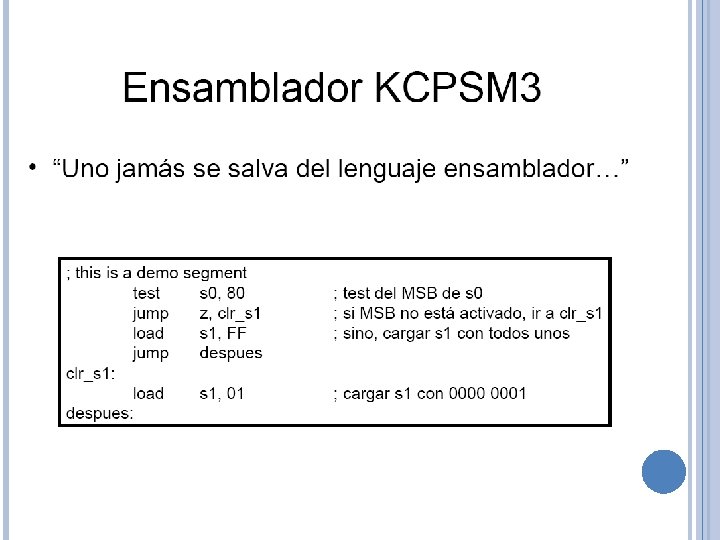

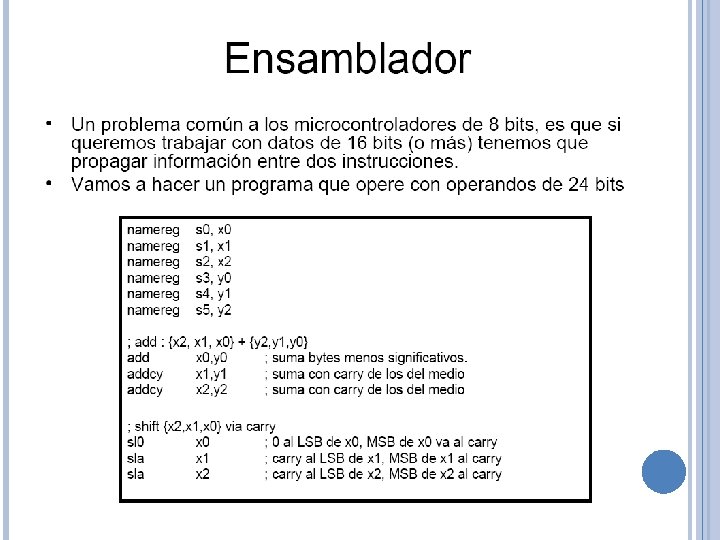

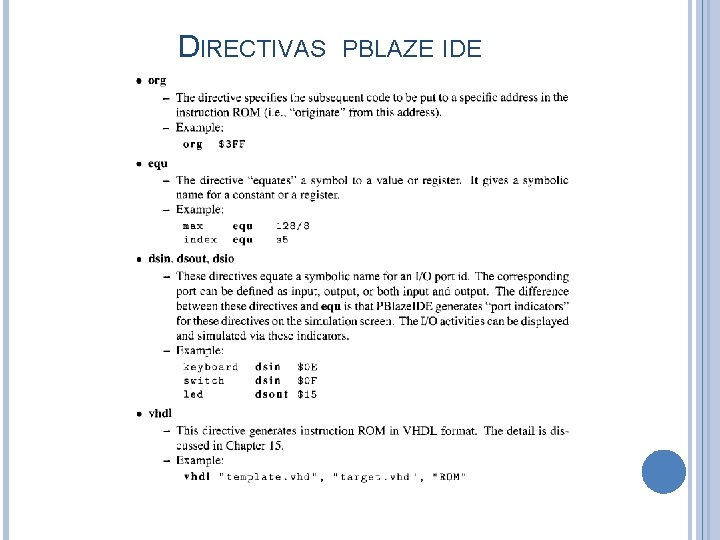

DIRECTIVAS PBLAZE IDE

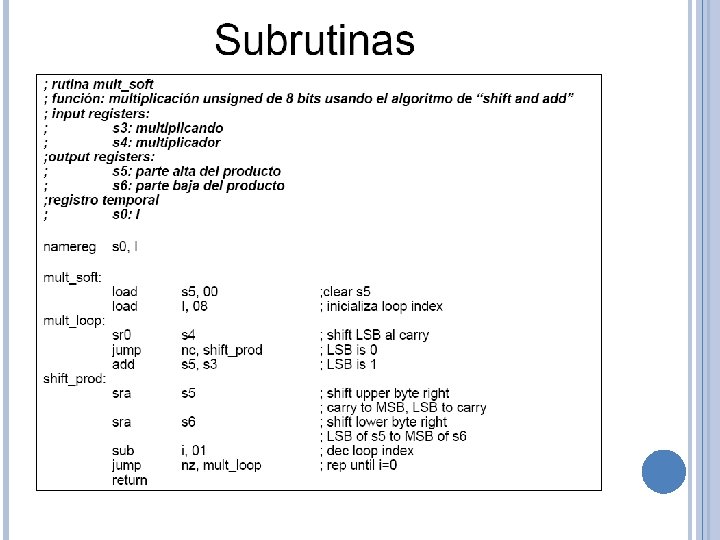

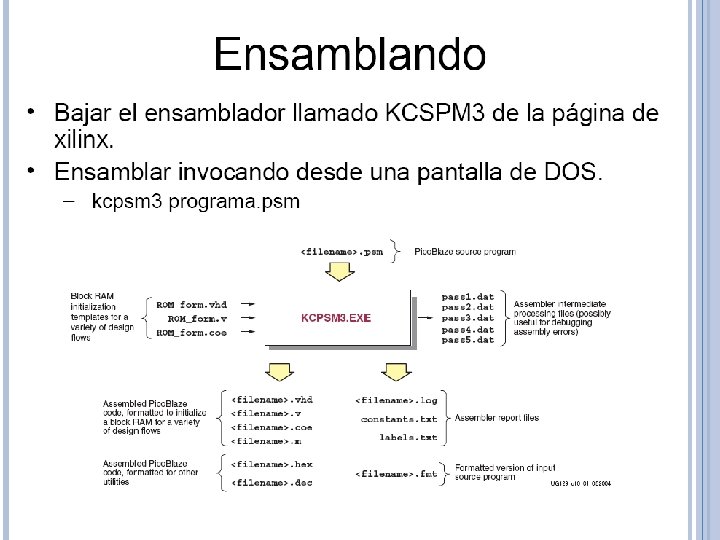

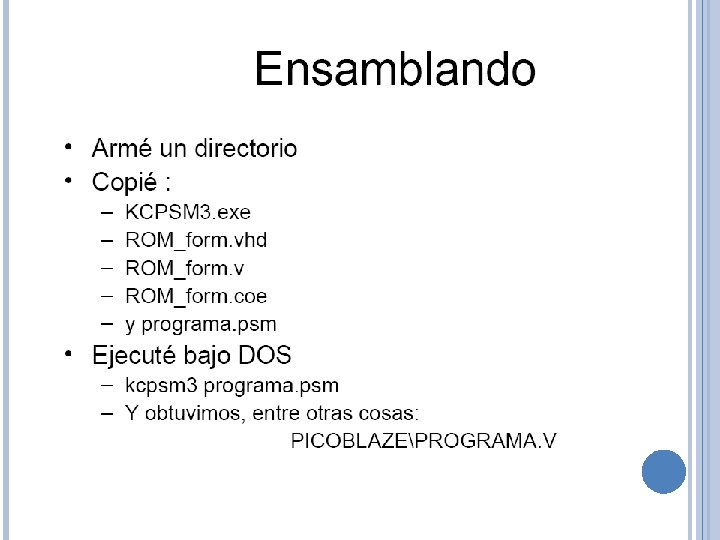

- Slides: 47