pico TDC ChipOnBoard and Package integration 7619 pico

pico. TDC - Chip-On-Board and Package integration 7/6/19 pico. TDC weekly meeting 1

Recent actions • One FPGA evaluation board is not working anymore >> New one recently ordered to Digi-key (US) >> I should try to diagnose the old one • 25 Test Boards PCBs just ordered (delay is 10 days instead of 5 days last time). I asked them to take more time to check better the PCB before delivery • 12 PCBs assemblies and wire-bonding of chips just ordered • Missing components for 12 -25 PCB assembly just ordered but in stock Farnell, should be delivered to CERN next Tuesday • I will send everything to Hybrid SA as soon as possible Probably the 24 th June • Expected new batch of completed boards – early-mid June 7/6/19 pico. TDC weekly meeting 2

Recent actions for packaging effort • For cost estimation I have contacted several possible sources for packaging: First through IMEC interface • Mr Paul Malisse replied me: Jerome – as to cost estimation, referring to previous projects and just indicative … I would expect the design + substrate tool manufacturing + ball mount kit + initial pre-series substrates to be in the range of 20 to 23 K. Units ~3 USD per pcs + ~3 K setup cost per assembly start. When starting the production the Mo. Q is the challenge along with limited lifetime of the substrates. These can only be used for one year ( max 18 months ) and the Min order qty can be pretty high and not known up front ( 20 K pcs, 30 Kpcs ? ) Substrates need to be pre-bought at 75% of the package price. Consequence : If you need to assemble only 10 K pcs and Mo. Q is 20 K : you need to prebuy 20 K*0. 75* 3 usd. The assy would cost 10 K*0. 25%3 usd. So some substrates are lost. If you need to assemble 40 K pcs and Mo. Q is 20 K : you need to prebuy 40 K*0. 75* 3 usd. The assy would cost 40 K*0. 25%3 usd. No loss here. • So if I understand correctly if we go to 1 K prototype + 40 K pcs: Total : 3 K USD for (IMEC feasility study (previous email from Paul) + 20 to 23 K USD (maybe 20 K if feasibility study is already done) + 1 K * 3 USD (for 1000 prototypes) + 3 K USD ( for the setup and assembly of prototypes) + 40 k * 3 USD + 3 K USD ( for the setup and assembly of production) = 152 K USD If min quantity to enter to the tender process is 30 K pcs, and if we order 1 K prototypes + 30 K pcs, total would be 122 K USD If min quantity is 30 K and if we order 1 K prototypes + 20 Kpcs = 114, 5 K USD ! If min quantity is 20 K and if we order 1 k prototypes + 20 Kpcs = 92 K USD ! 7/6/19 pico. TDC weekly meeting 3

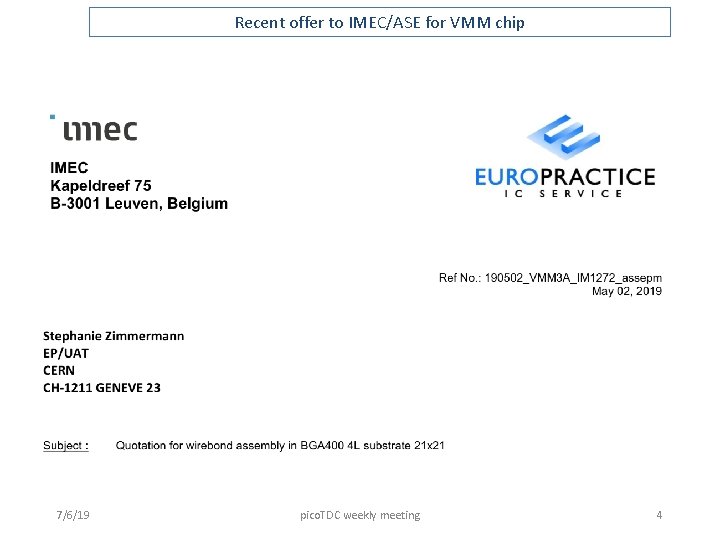

Recent offer to IMEC/ASE for VMM chip 7/6/19 pico. TDC weekly meeting 4

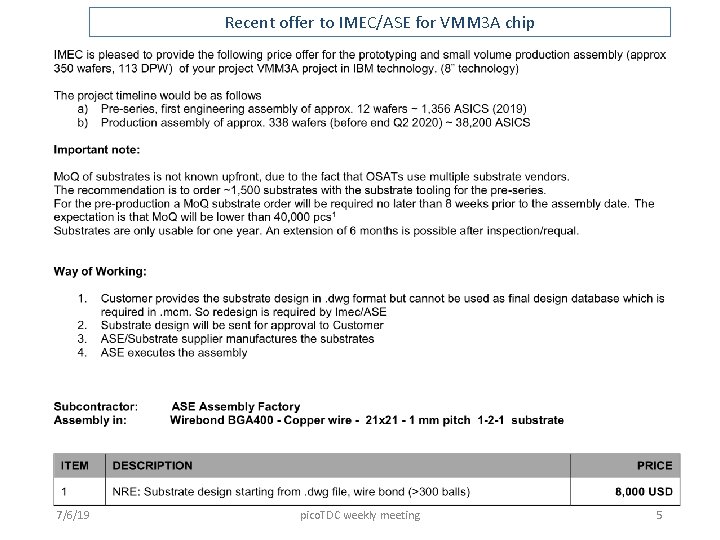

Recent offer to IMEC/ASE for VMM 3 A chip 7/6/19 pico. TDC weekly meeting 5

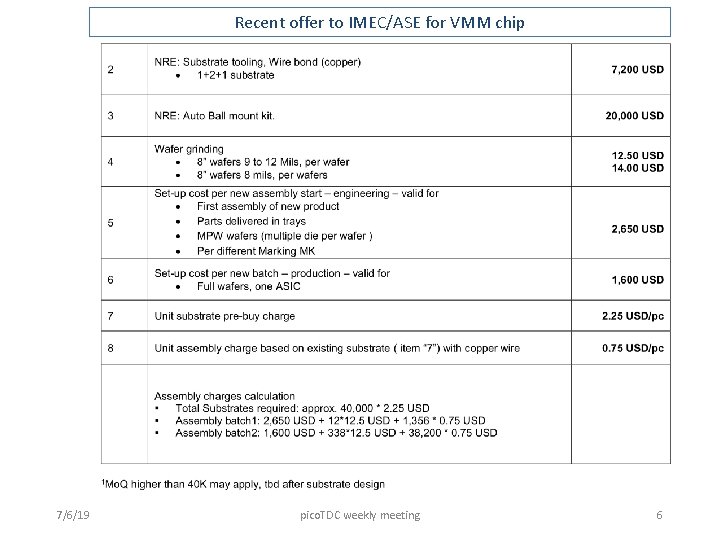

Recent offer to IMEC/ASE for VMM chip 7/6/19 pico. TDC weekly meeting 6

Recent order to IMEC/ASE for VMM chip 7/6/19 pico. TDC weekly meeting 7

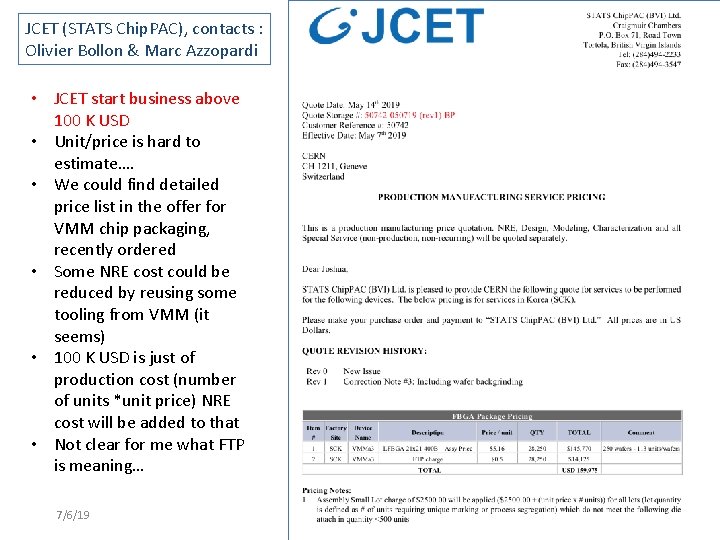

JCET (STATS Chip. PAC), contacts : Olivier Bollon & Marc Azzopardi • JCET start business above 100 K USD • Unit/price is hard to estimate…. • We could find detailed price list in the offer for VMM chip packaging, recently ordered • Some NRE cost could be reduced by reusing some tooling from VMM (it seems) • 100 K USD is just of production cost (number of units *unit price) NRE cost will be added to that • Not clear for me what FTP is meaning… 7/6/19 pico. TDC weekly meeting 8

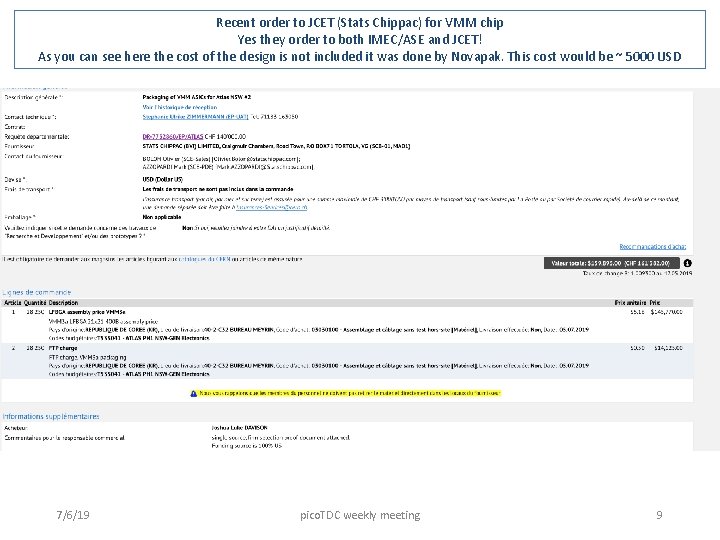

Recent order to JCET (Stats Chippac) for VMM chip Yes they order to both IMEC/ASE and JCET! As you can see here the cost of the design is not included it was done by Novapak. This cost would be ~ 5000 USD 7/6/19 pico. TDC weekly meeting 9

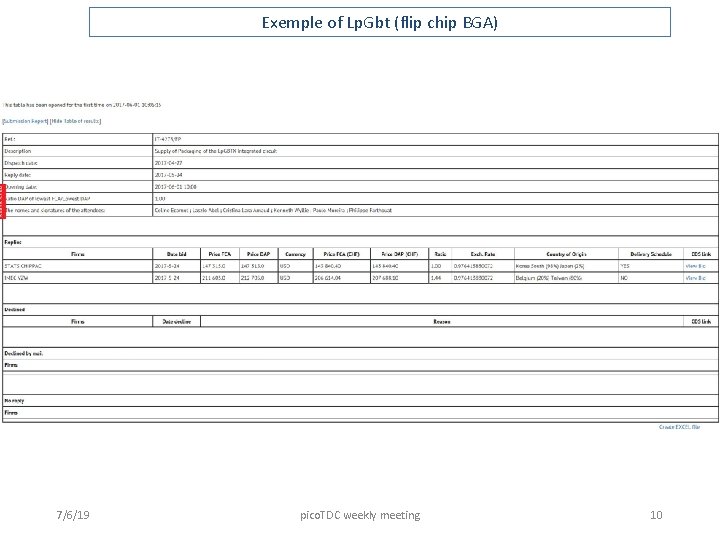

Exemple of Lp. Gbt (flip chip BGA) 7/6/19 pico. TDC weekly meeting 10

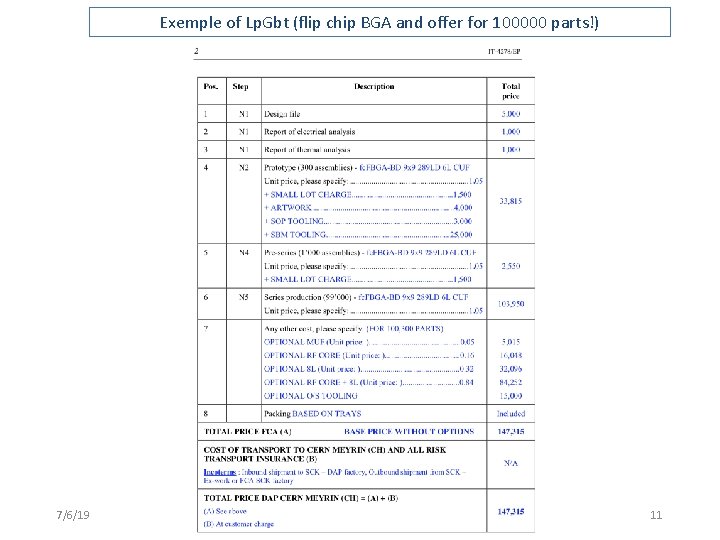

Exemple of Lp. Gbt (flip chip BGA and offer for 100000 parts!) 7/6/19 pico. TDC weekly meeting 11

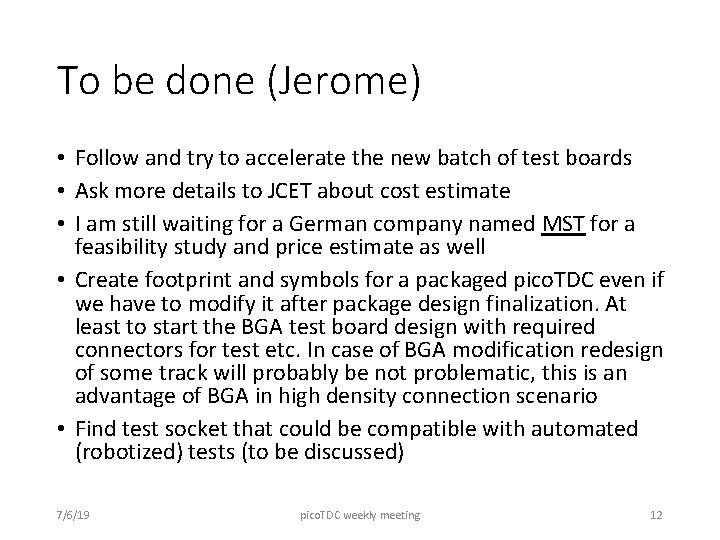

To be done (Jerome) • Follow and try to accelerate the new batch of test boards • Ask more details to JCET about cost estimate • I am still waiting for a German company named MST for a feasibility study and price estimate as well • Create footprint and symbols for a packaged pico. TDC even if we have to modify it after package design finalization. At least to start the BGA test board design with required connectors for test etc. In case of BGA modification redesign of some track will probably be not problematic, this is an advantage of BGA in high density connection scenario • Find test socket that could be compatible with automated (robotized) tests (to be discussed) 7/6/19 pico. TDC weekly meeting 12

- Slides: 12