PIC Microcontroller and Embedded Systems Muhammad Ali Mazidi

PIC Microcontroller and Embedded Systems Muhammad Ali Mazidi, Rolin Mc. Kinlay and Danny Causey Eng. Husam Alzaq The Islamic Uni. Of Gaza The PIC u. Cs 11 -1

Chapter 11: Interrupts programming in Assembly PIC Microcontroller and Embedded Systems Muhammad Ali Mazidi, Rolin Mc. Kinlay and Danny Causey, February 2007. The PIC u. Cs 11 -2

Objective The PIC u. Cs 11 -3

Introduction r Interrupts are mechanisms which enable instant response to events such as counter overflow, pin change, data received, etc. r In normal mode, microcontroller executes the main program as long as there are no occurrences that would cause an interrupt. r Upon interrupt, microcontroller stops the execution of main program and commences the special part of the program(ISR) which will analyze and handle the interrupt. The PIC u. Cs 11 -4

11. 1: PIC 18 interrupts r PIC can serve multiple devices using mechanisms of m Polling • PIC continuously monitors the status of each device • Each device get the attention of the CPU as the same level of priority • Wastes u-Controllers time by polling devices that do not need service. m Interrupt • Devices get the attention of the CPU only when it needs a service • Can service many devices with different level of priorities The PIC u. Cs 11 -5

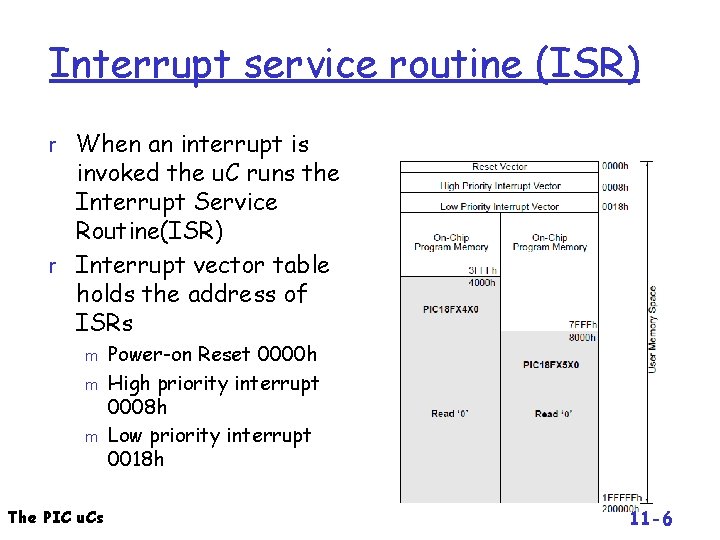

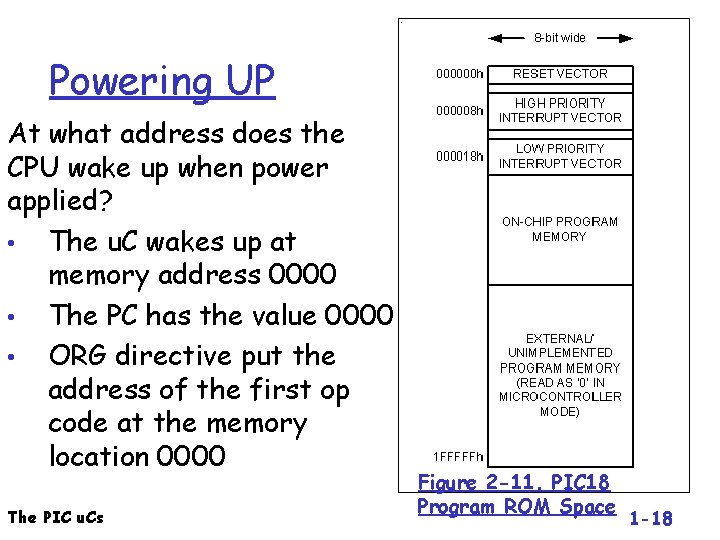

Interrupt service routine (ISR) r When an interrupt is invoked the u. C runs the Interrupt Service Routine(ISR) r Interrupt vector table holds the address of ISRs m m m The PIC u. Cs Power-on Reset 0000 h High priority interrupt 0008 h Low priority interrupt 0018 h 11 -6

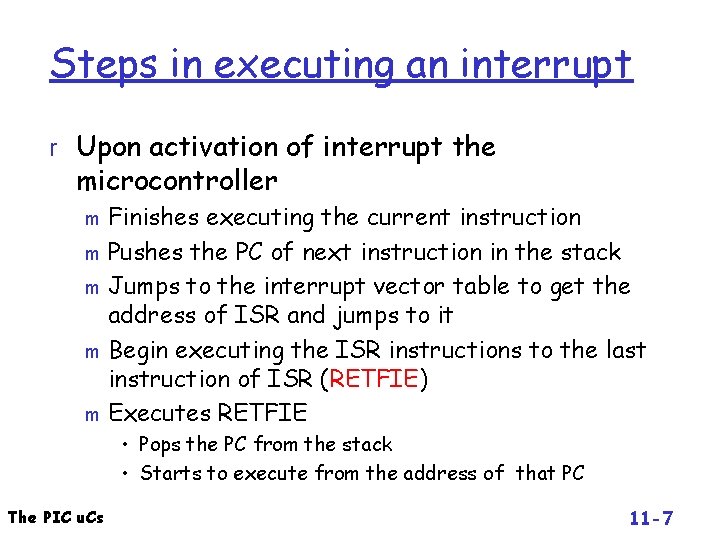

Steps in executing an interrupt r Upon activation of interrupt the microcontroller Finishes executing the current instruction m Pushes the PC of next instruction in the stack m Jumps to the interrupt vector table to get the address of ISR and jumps to it m Begin executing the ISR instructions to the last instruction of ISR (RETFIE) m Executes RETFIE m • Pops the PC from the stack • Starts to execute from the address of that PC The PIC u. Cs 11 -7

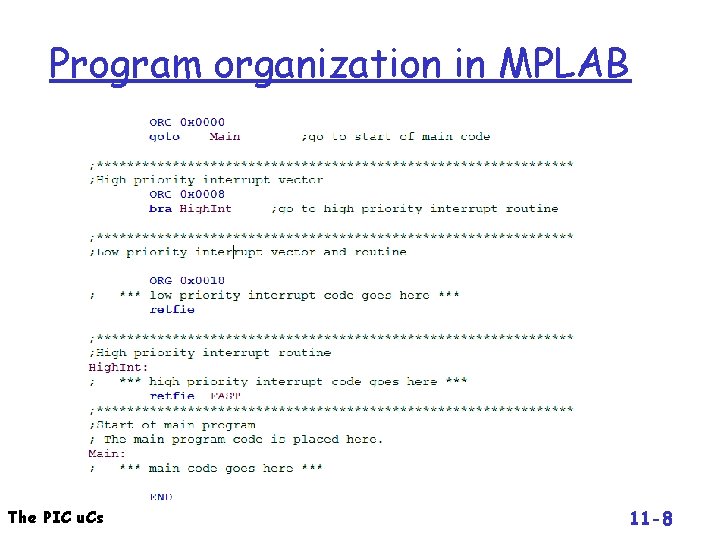

Program organization in MPLAB The PIC u. Cs 11 -8

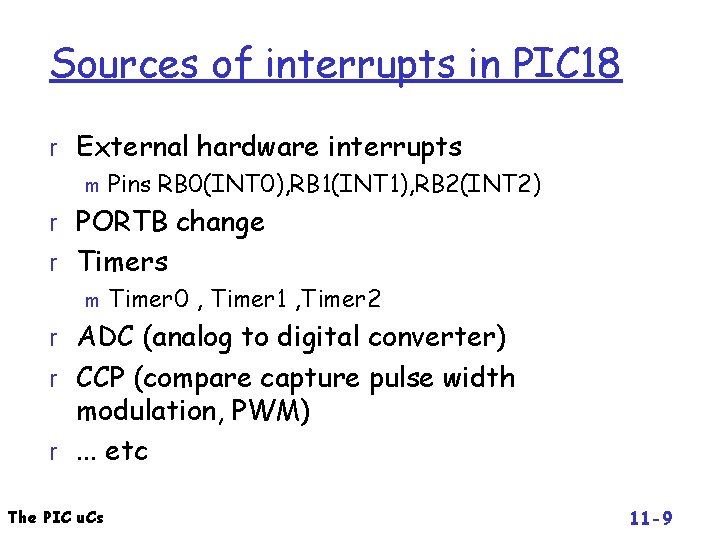

Sources of interrupts in PIC 18 r External hardware interrupts m Pins RB 0(INT 0), RB 1(INT 1), RB 2(INT 2) r PORTB change r Timers m Timer 0 , Timer 1 , Timer 2 r ADC (analog to digital converter) r CCP (compare capture pulse width modulation, PWM) r. . . etc The PIC u. Cs 11 -9

Enabling and disabling an interrupt r When the PIC is powered on (or resets) m All interrupts are masked (disabled) m The default ISR address is 0008 h • No interrupt priorities for interrupts The PIC u. Cs 11 -10

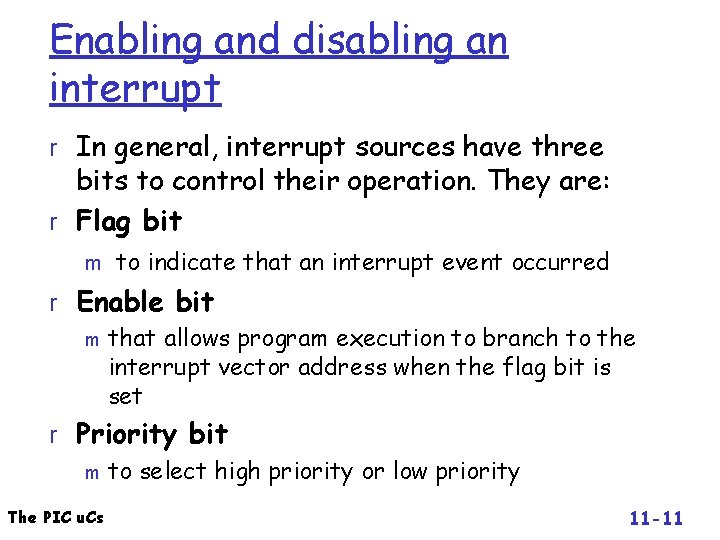

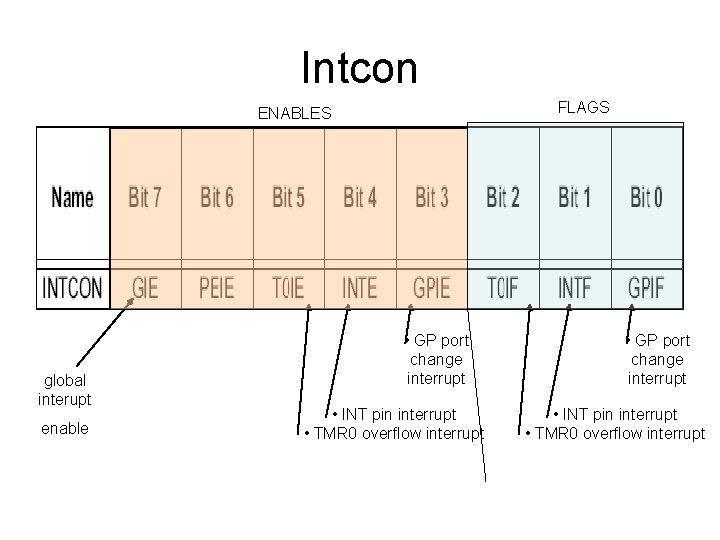

Enabling and disabling an interrupt r In general, interrupt sources have three bits to control their operation. They are: r Flag bit m to indicate that an interrupt event occurred r Enable bit m that allows program execution to branch to the interrupt vector address when the flag bit is set r Priority bit m to select high priority or low priority The PIC u. Cs 11 -11

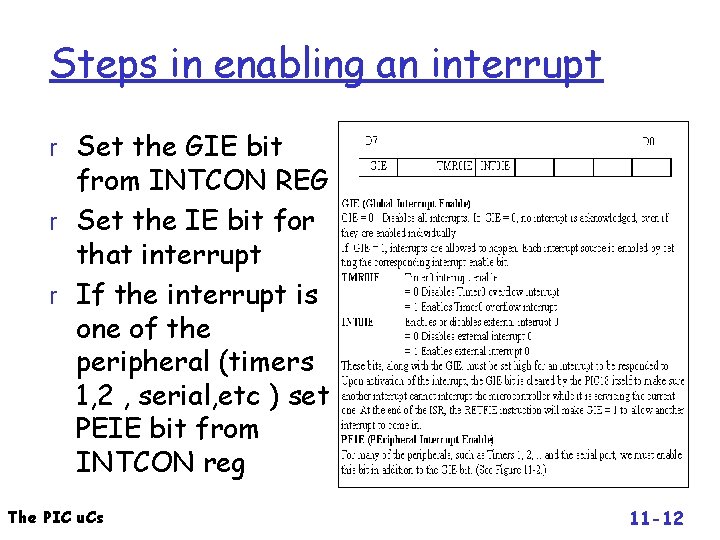

Steps in enabling an interrupt r Set the GIE bit from INTCON REG r Set the IE bit for that interrupt r If the interrupt is one of the peripheral (timers 1, 2 , serial, etc ) set PEIE bit from INTCON reg The PIC u. Cs 11 -12

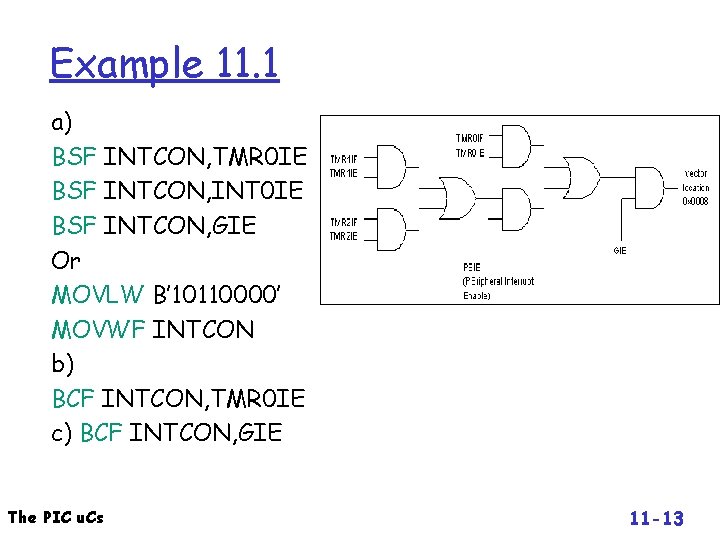

Example 11. 1 a) BSF INTCON, TMR 0 IE BSF INTCON, INT 0 IE BSF INTCON, GIE Or MOVLW B’ 10110000’ MOVWF INTCON b) BCF INTCON, TMR 0 IE c) BCF INTCON, GIE The PIC u. Cs 11 -13

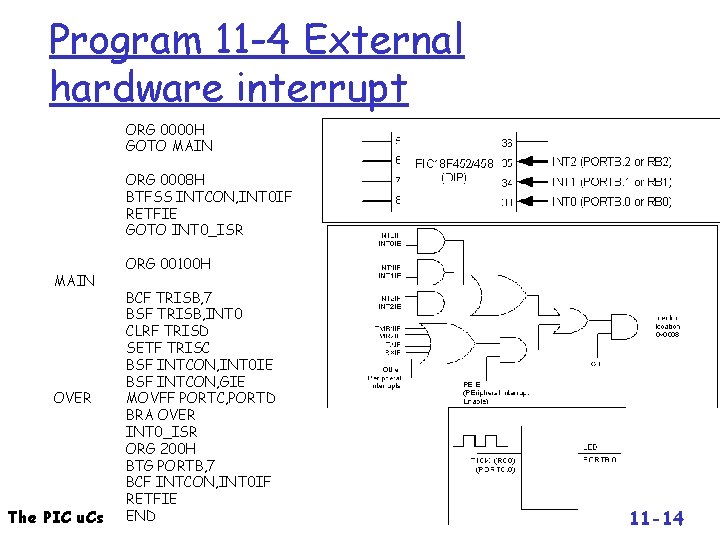

Program 11 -4 External hardware interrupt ORG 0000 H GOTO MAIN ORG 0008 H BTFSS INTCON, INT 0 IF RETFIE GOTO INT 0_ISR MAIN OVER The PIC u. Cs ORG 00100 H BCF TRISB, 7 BSF TRISB, INT 0 CLRF TRISD SETF TRISC BSF INTCON, INT 0 IE BSF INTCON, GIE MOVFF PORTC, PORTD BRA OVER INT 0_ISR ORG 200 H BTG PORTB, 7 BCF INTCON, INT 0 IF RETFIE END 11 -14

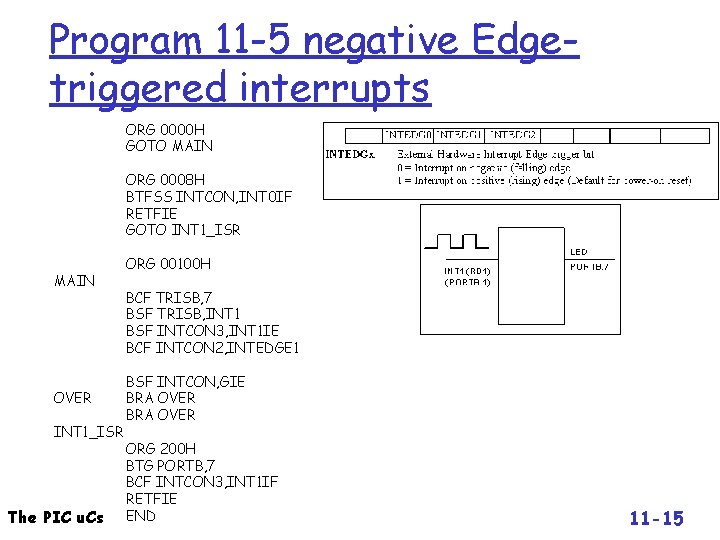

Program 11 -5 negative Edgetriggered interrupts ORG 0000 H GOTO MAIN ORG 0008 H BTFSS INTCON, INT 0 IF RETFIE GOTO INT 1_ISR MAIN OVER INT 1_ISR The PIC u. Cs ORG 00100 H BCF TRISB, 7 BSF TRISB, INT 1 BSF INTCON 3, INT 1 IE BCF INTCON 2, INTEDGE 1 BSF INTCON, GIE BRA OVER ORG 200 H BTG PORTB, 7 BCF INTCON 3, INT 1 IF RETFIE END 11 -15

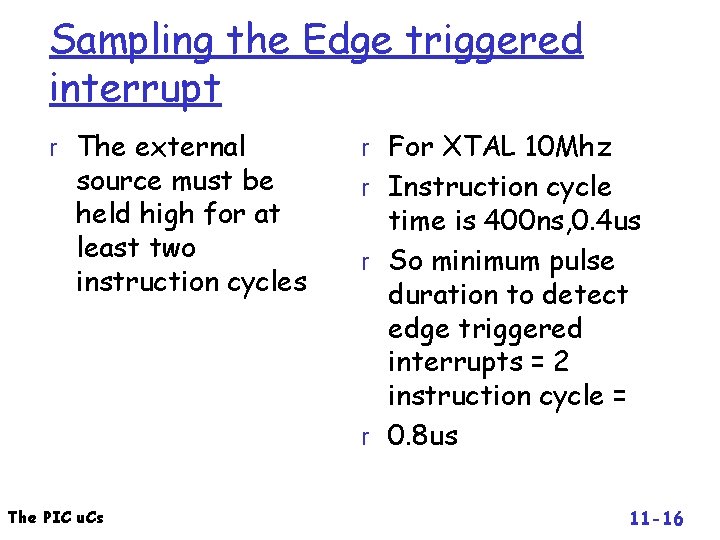

Sampling the Edge triggered interrupt r The external source must be held high for at least two instruction cycles The PIC u. Cs r For XTAL 10 Mhz r Instruction cycle time is 400 ns, 0. 4 us r So minimum pulse duration to detect edge triggered interrupts = 2 instruction cycle = r 0. 8 us 11 -16

The PIC u. Cs 11 -17

Powering UP At what address does the CPU wake up when power applied? • The u. C wakes up at memory address 0000 • The PC has the value 0000 • ORG directive put the address of the first op code at the memory location 0000 The PIC u. Cs Figure 2 -11. PIC 18 Program ROM Space 1 -18

Intcon FLAGS ENABLES global interupt enable • GP port change interrupt • INT pin interrupt • TMR 0 overflow interrupt

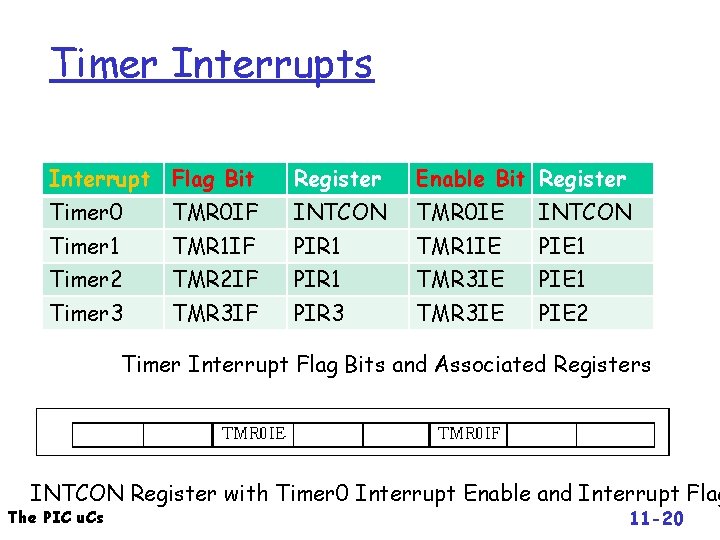

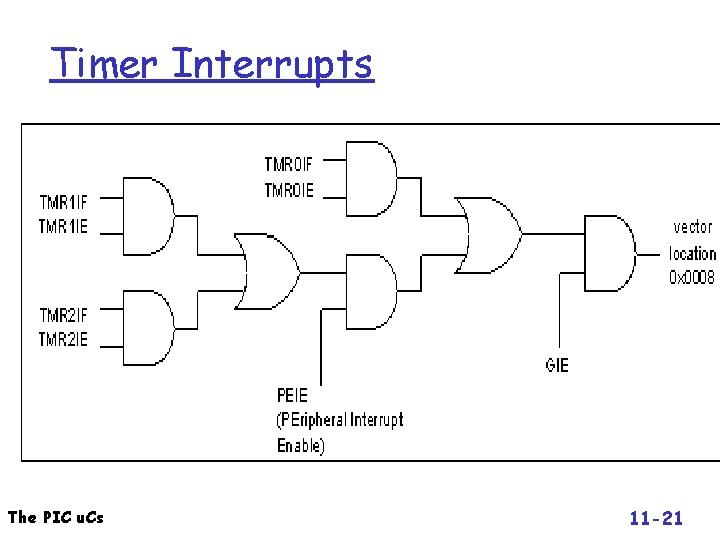

Timer Interrupts Interrupt Flag Bit Register Enable Bit Register Timer 0 TMR 0 IF INTCON TMR 0 IE INTCON Timer 1 TMR 1 IF PIR 1 TMR 1 IE PIE 1 Timer 2 TMR 2 IF PIR 1 TMR 3 IE PIE 1 Timer 3 TMR 3 IF PIR 3 TMR 3 IE PIE 2 Timer Interrupt Flag Bits and Associated Registers INTCON Register with Timer 0 Interrupt Enable and Interrupt Flag The PIC u. Cs 11 -20

Timer Interrupts The PIC u. Cs 11 -21

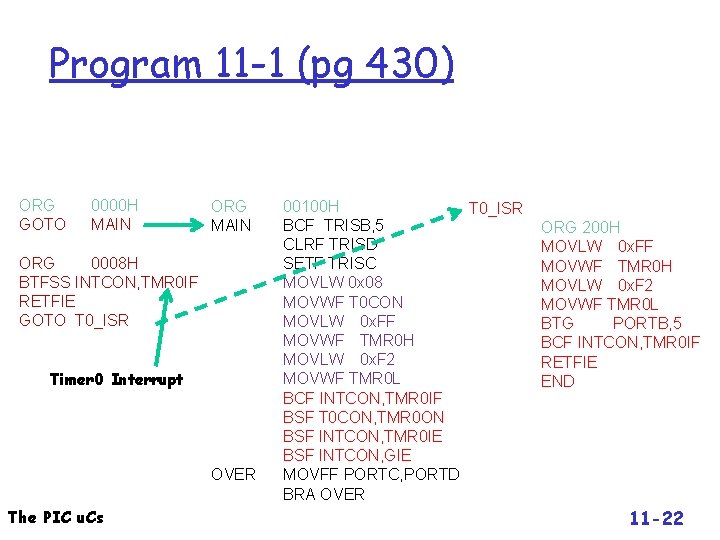

Program 11 -1 (pg 430) ORG GOTO 0000 H MAIN ORG 0008 H BTFSS INTCON, TMR 0 IF RETFIE GOTO T 0_ISR Timer 0 Interrupt OVER The PIC u. Cs 00100 H T 0_ISR BCF TRISB, 5 CLRF TRISD SETF TRISC MOVLW 0 x 08 MOVWF T 0 CON MOVLW 0 x. FF MOVWF TMR 0 H MOVLW 0 x. F 2 MOVWF TMR 0 L BCF INTCON, TMR 0 IF BSF T 0 CON, TMR 0 ON BSF INTCON, TMR 0 IE BSF INTCON, GIE MOVFF PORTC, PORTD BRA OVER ORG 200 H MOVLW 0 x. FF MOVWF TMR 0 H MOVLW 0 x. F 2 MOVWF TMR 0 L BTG PORTB, 5 BCF INTCON, TMR 0 IF RETFIE END 11 -22

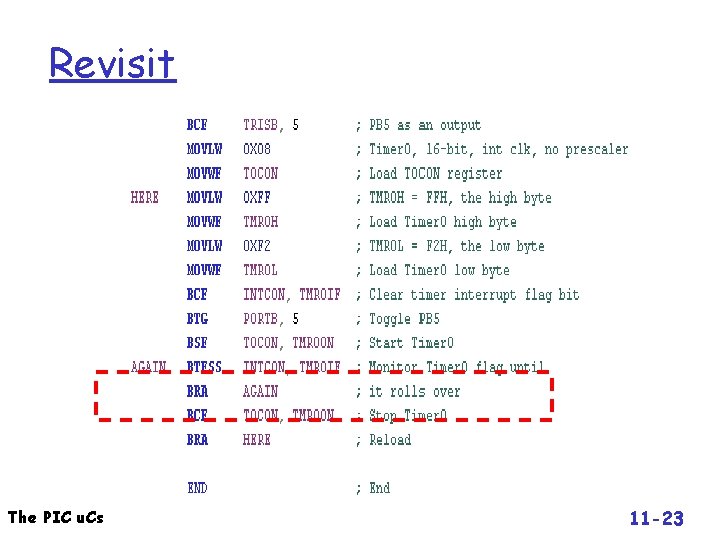

Revisit The PIC u. Cs 11 -23

Please see Program 11 -2 (pg 432) and Program 11 -3 (pg 433) The PIC u. Cs 11 -24

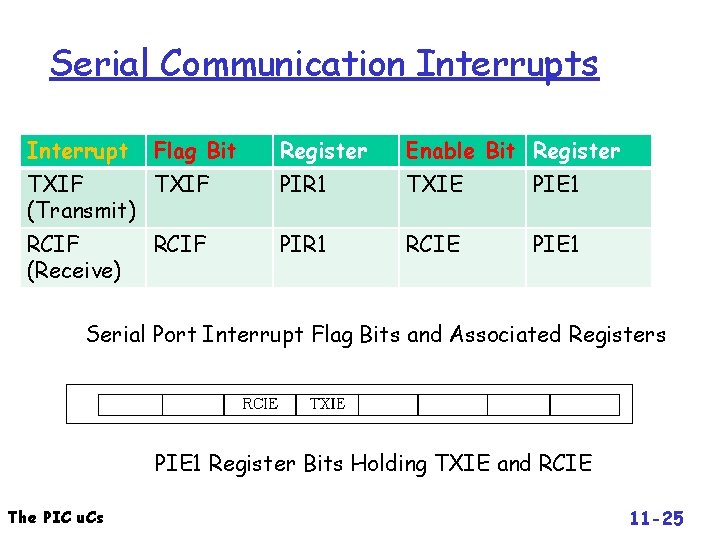

Serial Communication Interrupts Interrupt Flag Bit Register Enable Bit Register TXIF (Transmit) PIR 1 TXIE PIE 1 RCIF (Receive) PIR 1 RCIE PIE 1 RCIF Serial Port Interrupt Flag Bits and Associated Registers PIE 1 Register Bits Holding TXIE and RCIE The PIC u. Cs 11 -25

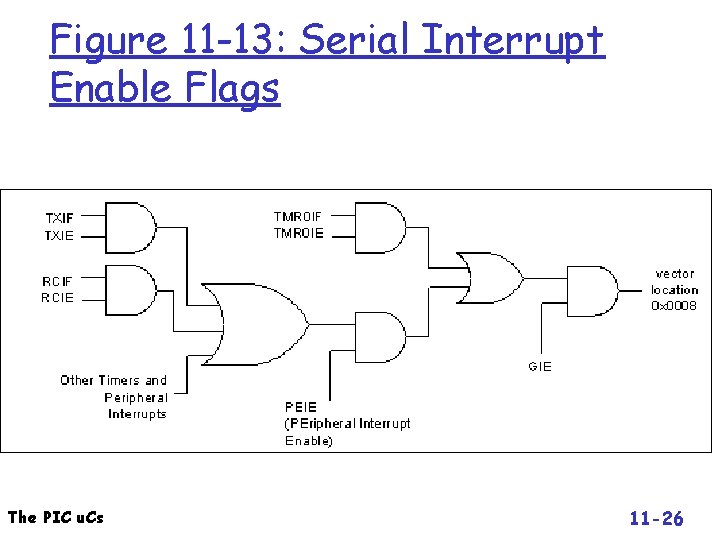

Figure 11 -13: Serial Interrupt Enable Flags The PIC u. Cs 11 -26

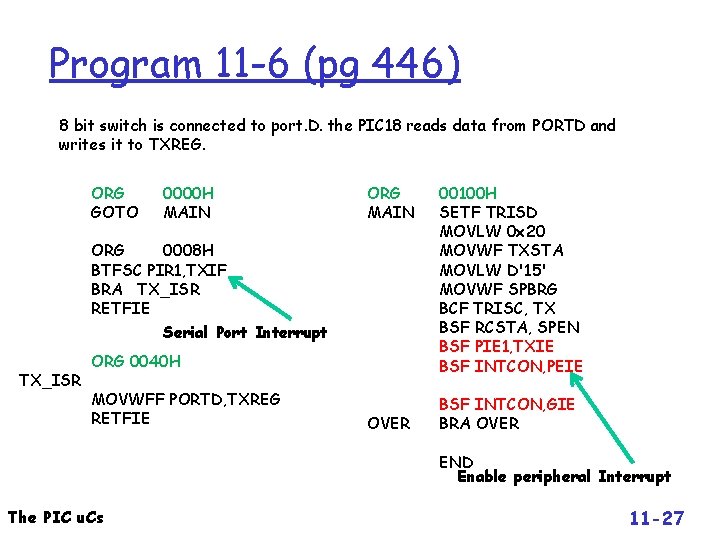

Program 11 -6 (pg 446) 8 bit switch is connected to port. D. the PIC 18 reads data from PORTD and writes it to TXREG. ORG GOTO 0000 H MAIN ORG 0040 H 00100 H SETF TRISD MOVLW 0 x 20 MOVWF TXSTA MOVLW D'15' MOVWF SPBRG BCF TRISC, TX BSF RCSTA, SPEN BSF PIE 1, TXIE BSF INTCON, PEIE MOVWFF PORTD, TXREG RETFIE BSF INTCON, GIE BRA OVER ORG 0008 H BTFSC PIR 1, TXIF BRA TX_ISR RETFIE Serial Port Interrupt TX_ISR OVER END Enable peripheral Interrupt The PIC u. Cs 11 -27

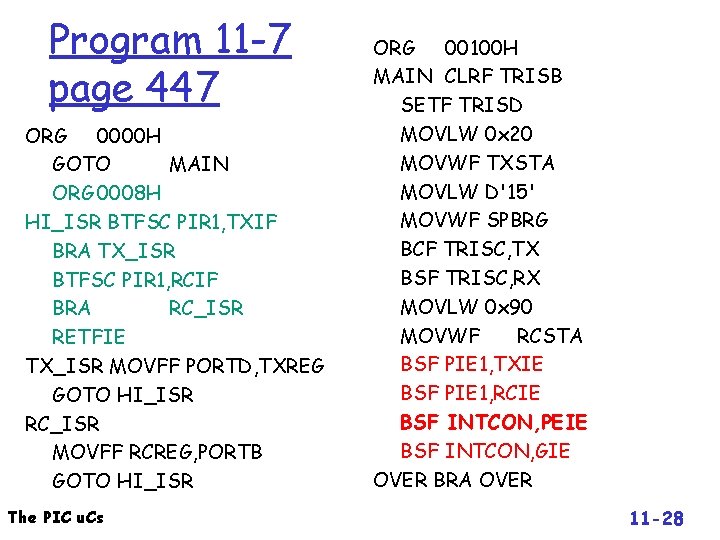

Program 11 -7 page 447 ORG 0000 H GOTO MAIN ORG 0008 H HI_ISR BTFSC PIR 1, TXIF BRA TX_ISR BTFSC PIR 1, RCIF BRA RC_ISR RETFIE TX_ISR MOVFF PORTD, TXREG GOTO HI_ISR RC_ISR MOVFF RCREG, PORTB GOTO HI_ISR The PIC u. Cs ORG 00100 H MAIN CLRF TRISB SETF TRISD MOVLW 0 x 20 MOVWF TXSTA MOVLW D'15' MOVWF SPBRG BCF TRISC, TX BSF TRISC, RX MOVLW 0 x 90 MOVWF RCSTA BSF PIE 1, TXIE BSF PIE 1, RCIE BSF INTCON, PEIE BSF INTCON, GIE OVER BRA OVER 11 -28

- Slides: 28