PIC 18 Interrupt Programming Explain the interrupts timer

- Slides: 21

PIC 18 Interrupt Programming “Explain the interrupts, timer interrupts, external hardware interrupts, serial communication interrupts and the interrupts priority”

Objectives Contra and compare interrupts versus pooling Explain the purpose of the ISR List all the major interrupts of the PIC 18 Explain the purpose of the IVT Enable and disable PIC 18 interrupts Program the PIC 18 interrupt using assembly language

Interrupt Whenever any device needs the microcontroller’s service the device notifies it by sending an interrupt signal. Upon receiving an interrupt signal, the microcontroller stops whatever it is doing and serve the device. The program associated with the interrupt is called ISR (interrupt service routine) or interrupt handler. Each device can get the attention of the microcontroller based on the priority assign to it. Can ignore a device request for service

Polling The microcontroller continuously monitors the status of a given device; when the status condition met, it performs the service. After that, it moves on to monitor the next device until each one is service. Cannot assign priority because it checks all devices in a round-robin fashion. Cannot ignore a devices for service

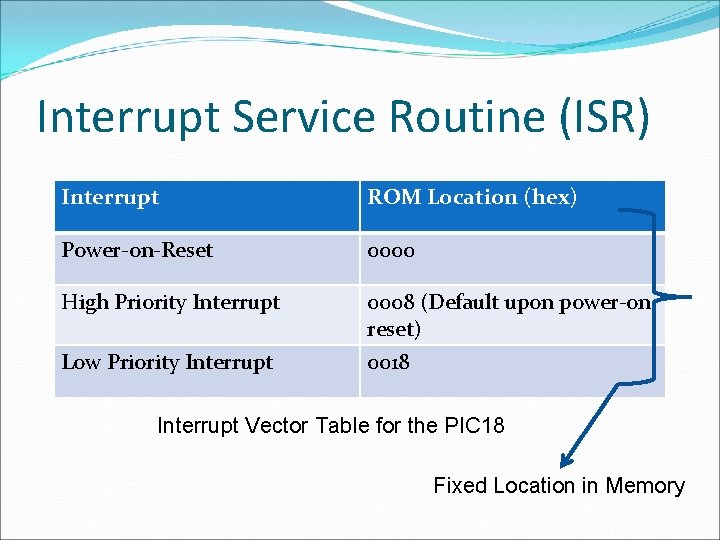

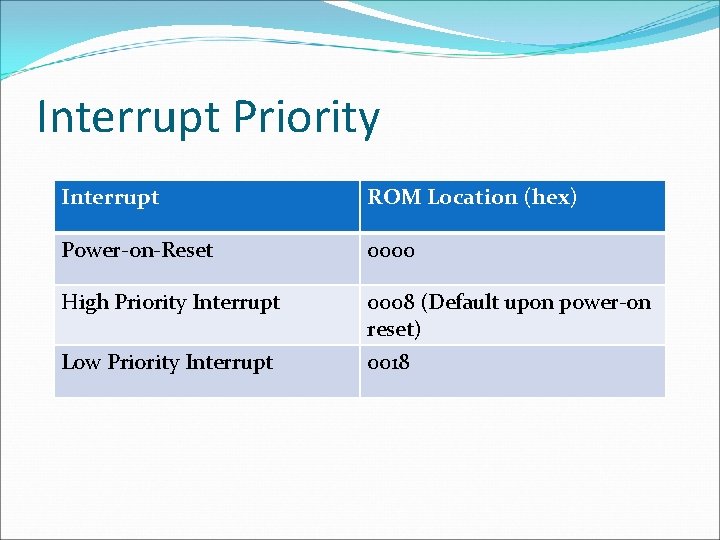

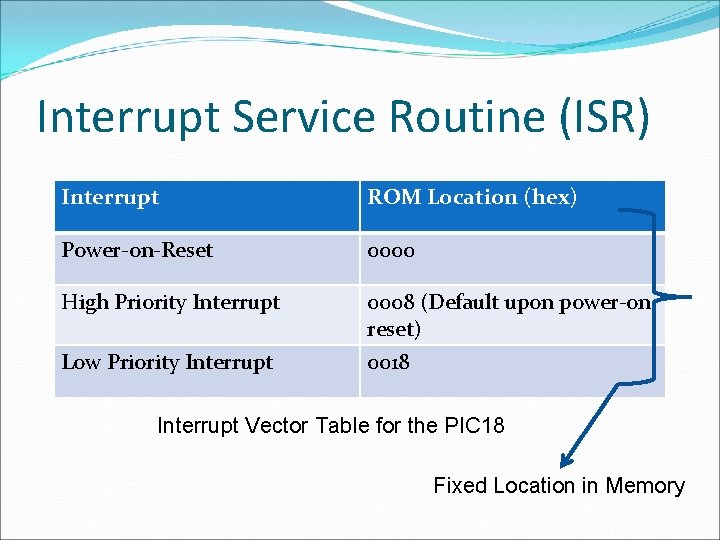

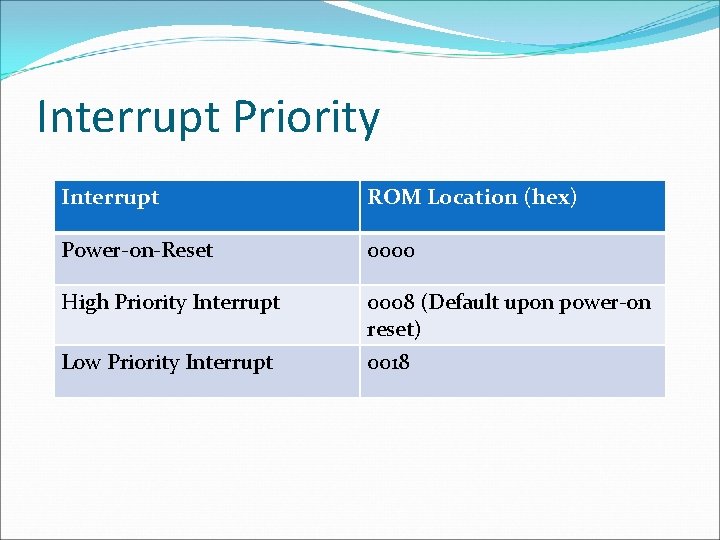

Interrupt Service Routine (ISR) Interrupt ROM Location (hex) Power-on-Reset 0000 High Priority Interrupt 0008 (Default upon power-on reset) Low Priority Interrupt 0018 Interrupt Vector Table for the PIC 18 Fixed Location in Memory

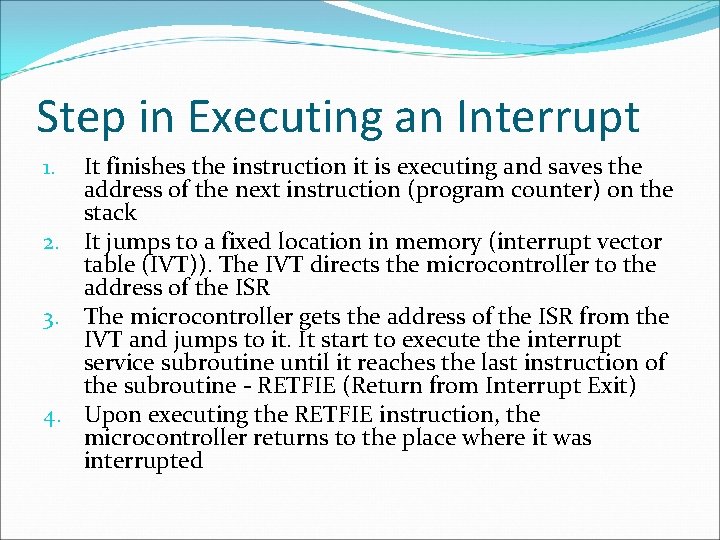

Step in Executing an Interrupt It finishes the instruction it is executing and saves the address of the next instruction (program counter) on the stack 2. It jumps to a fixed location in memory (interrupt vector table (IVT)). The IVT directs the microcontroller to the address of the ISR 3. The microcontroller gets the address of the ISR from the IVT and jumps to it. It start to execute the interrupt service subroutine until it reaches the last instruction of the subroutine - RETFIE (Return from Interrupt Exit) 4. Upon executing the RETFIE instruction, the microcontroller returns to the place where it was interrupted 1.

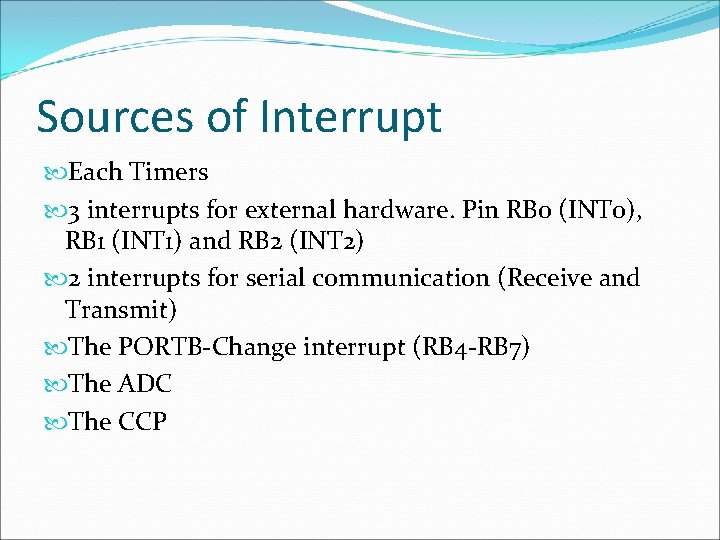

Sources of Interrupt Each Timers 3 interrupts for external hardware. Pin RB 0 (INT 0), RB 1 (INT 1) and RB 2 (INT 2) 2 interrupts for serial communication (Receive and Transmit) The PORTB-Change interrupt (RB 4 -RB 7) The ADC The CCP

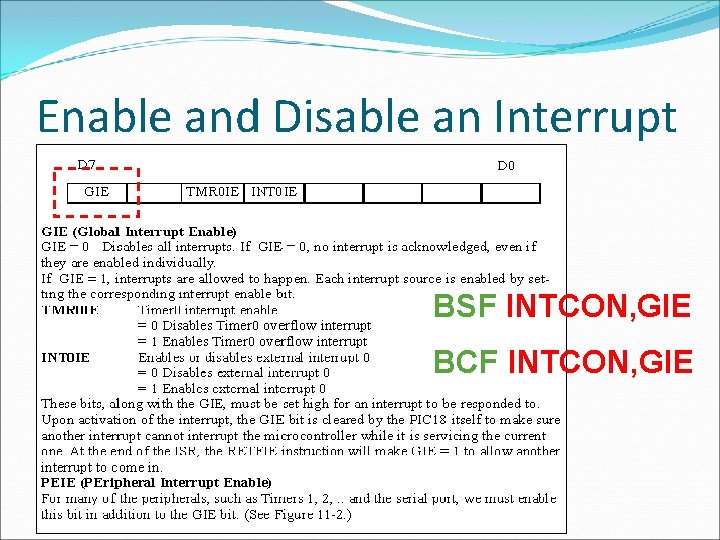

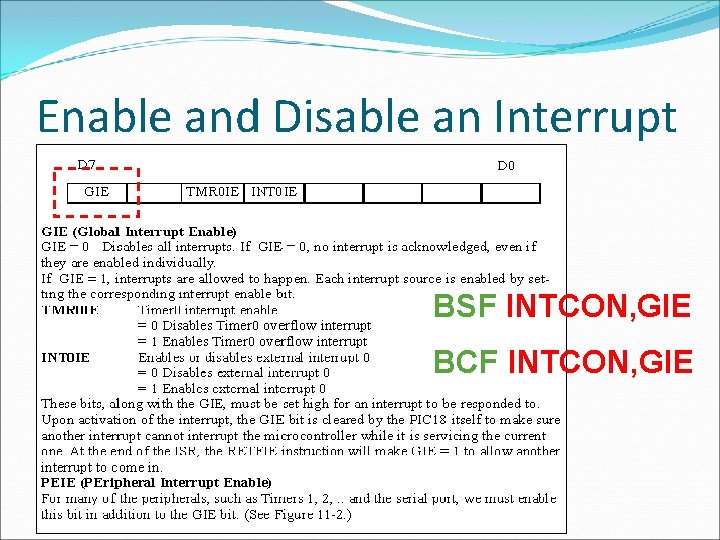

Enable and Disable an Interrupt BSF INTCON, GIE BCF INTCON, GIE

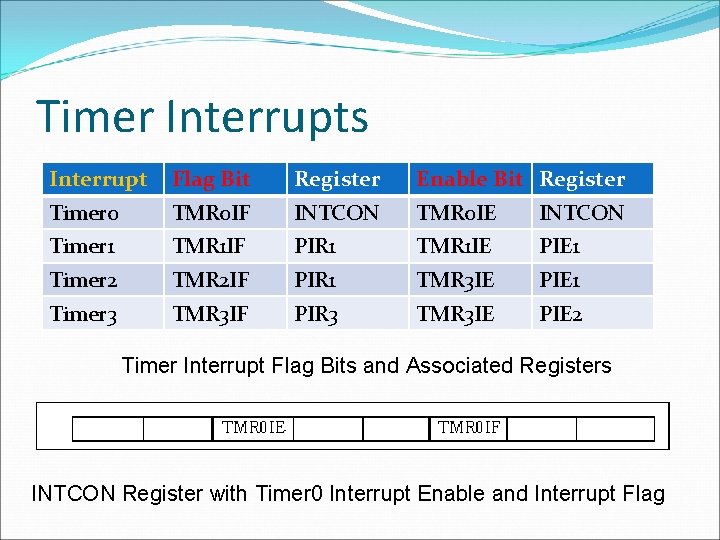

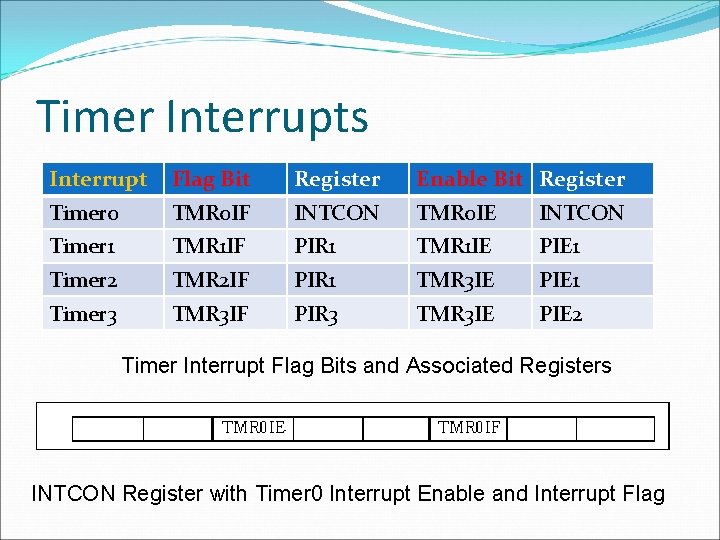

Timer Interrupts Interrupt Flag Bit Register Enable Bit Register Timer 0 TMR 0 IF INTCON TMR 0 IE INTCON Timer 1 TMR 1 IF PIR 1 TMR 1 IE PIE 1 Timer 2 TMR 2 IF PIR 1 TMR 3 IE PIE 1 Timer 3 TMR 3 IF PIR 3 TMR 3 IE PIE 2 Timer Interrupt Flag Bits and Associated Registers INTCON Register with Timer 0 Interrupt Enable and Interrupt Flag

Page 435

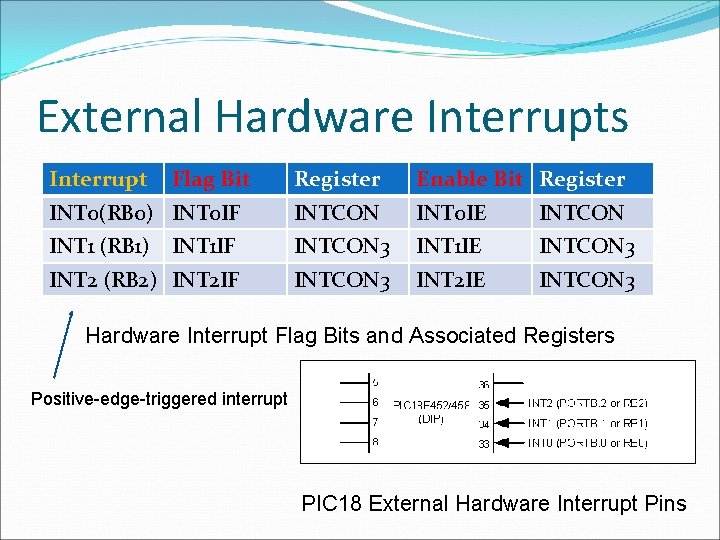

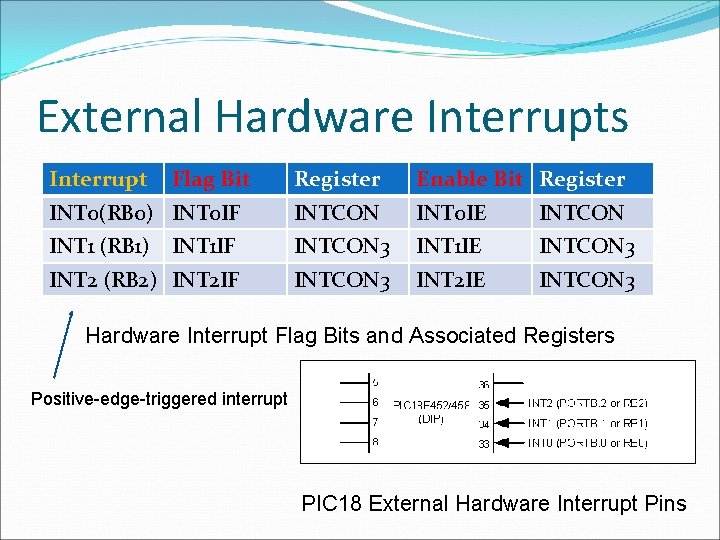

External Hardware Interrupts Interrupt Flag Bit Register Enable Bit Register INT 0(RB 0) INT 0 IF INTCON INT 0 IE INTCON INT 1 (RB 1) INT 1 IF INTCON 3 INT 1 IE INTCON 3 INT 2 (RB 2) INT 2 IF INTCON 3 INT 2 IE INTCON 3 Hardware Interrupt Flag Bits and Associated Registers Positive-edge-triggered interrupt PIC 18 External Hardware Interrupt Pins

Please see Program (pg 441)

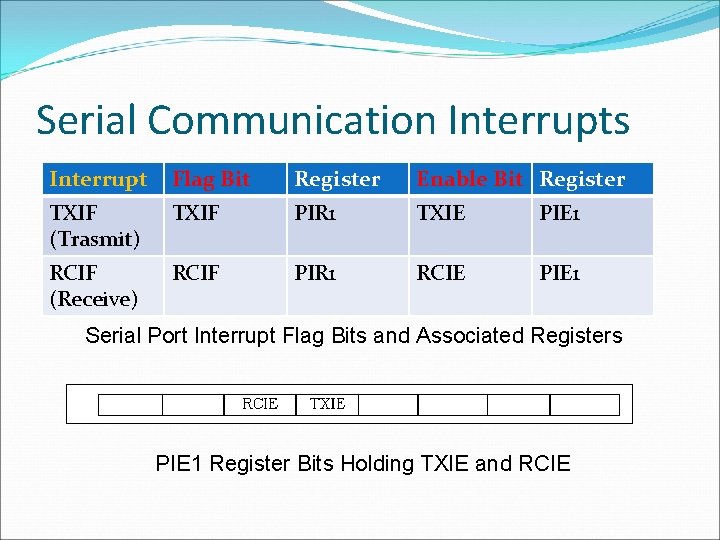

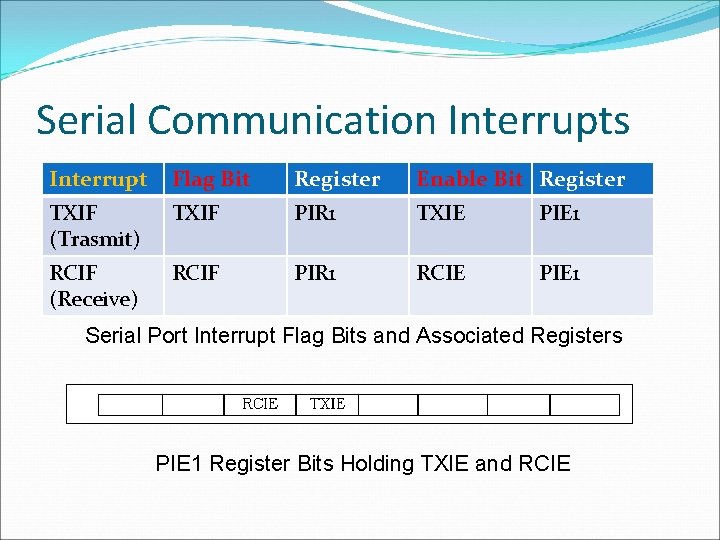

Serial Communication Interrupts Interrupt Flag Bit Register Enable Bit Register TXIF (Trasmit) TXIF PIR 1 TXIE PIE 1 RCIF (Receive) RCIF PIR 1 RCIE PIE 1 Serial Port Interrupt Flag Bits and Associated Registers PIE 1 Register Bits Holding TXIE and RCIE

Please see Program 11 -7 (pg 447)

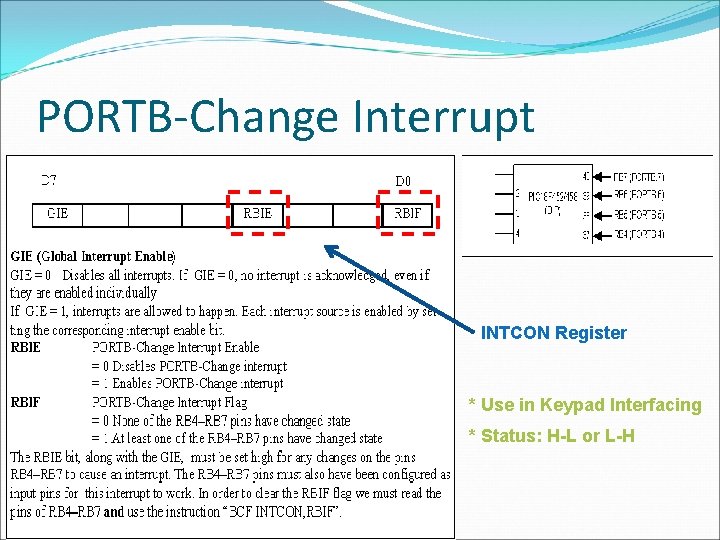

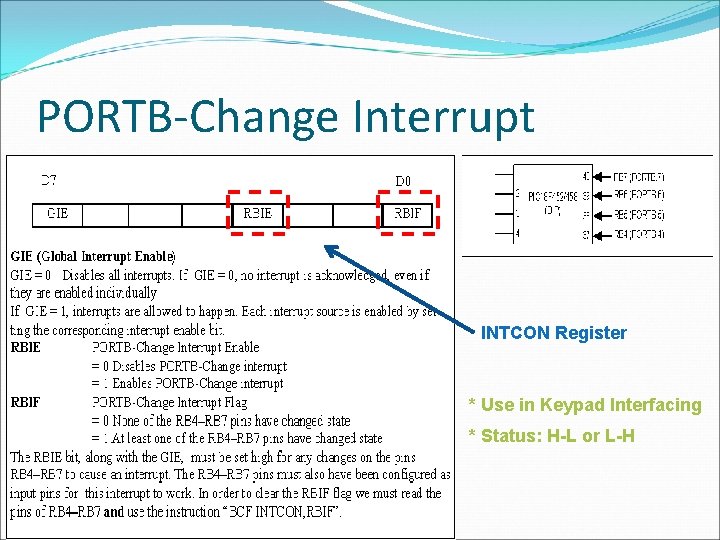

PORTB-Change Interrupt INTCON Register * Use in Keypad Interfacing * Status: H-L or L-H

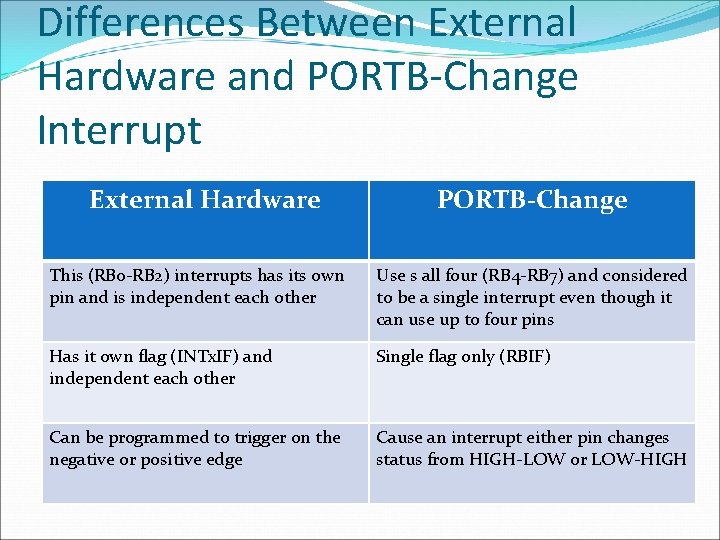

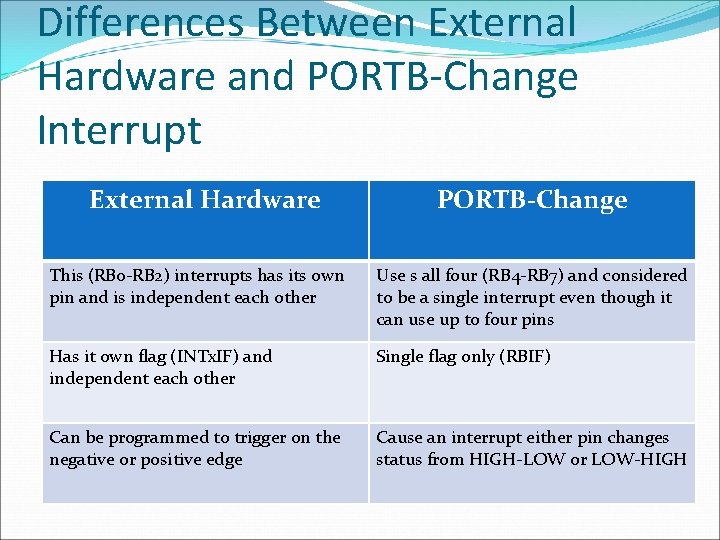

Differences Between External Hardware and PORTB-Change Interrupt External Hardware PORTB-Change This (RB 0 -RB 2) interrupts has its own pin and is independent each other Use s all four (RB 4 -RB 7) and considered to be a single interrupt even though it can use up to four pins Has it own flag (INTx. IF) and independent each other Single flag only (RBIF) Can be programmed to trigger on the negative or positive edge Cause an interrupt either pin changes status from HIGH-LOW or LOW-HIGH

Please see Program (pg 453)

Interrupt Priority Interrupt ROM Location (hex) Power-on-Reset 0000 High Priority Interrupt 0008 (Default upon power-on reset) Low Priority Interrupt 0018

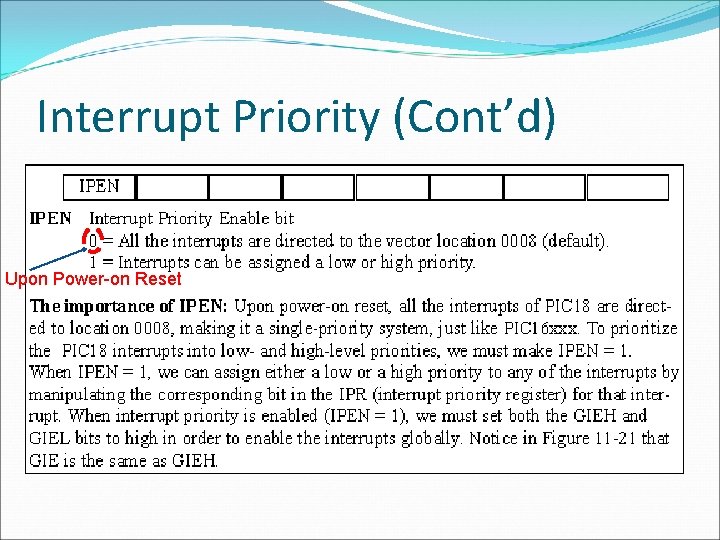

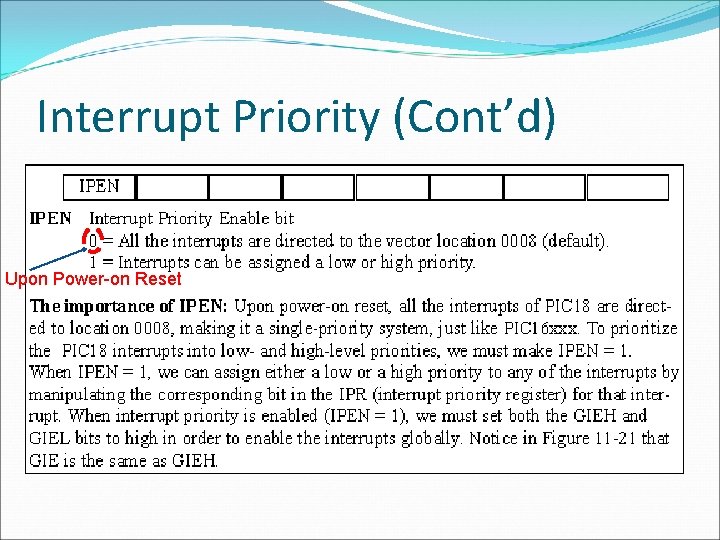

Interrupt Priority (Cont’d) Upon Power-on Reset

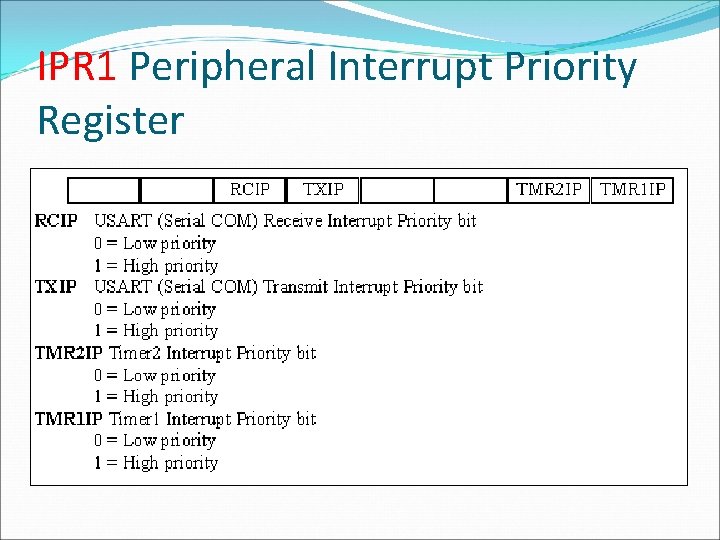

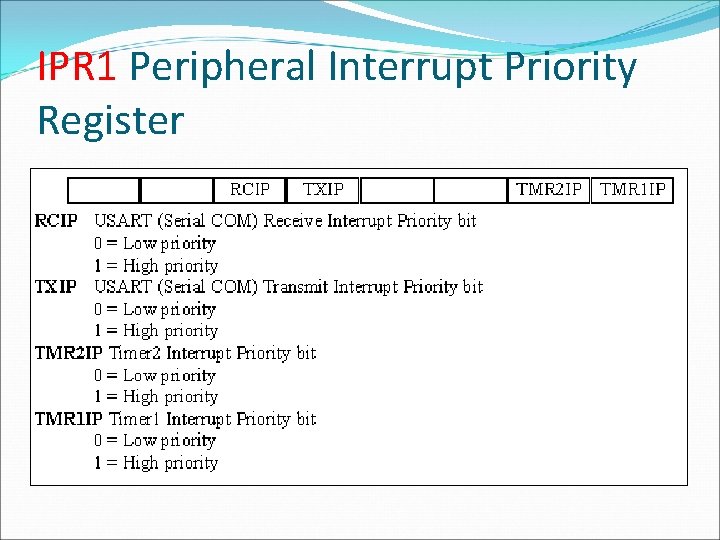

IPR 1 Peripheral Interrupt Priority Register

End Of Chapter “Never interrupt your enemy when he/she is making a mistake“