Physical Register File Management Renaming ECE 721 Spring

- Slides: 14

Physical Register File Management: Renaming ECE 721 Spring’ 20 Prof. Eric Rotenberg

Logical registers • Also called architectural registers • Registers defined in the instruction-set architecture (ISA) • Program registers (registers you see in the program binary) • Example: Alpha ISA • 32 logical integer registers (r 0 -r 31) • 32 logical floating-point registers ECE 721, Spring'20 Prof. Eric Rotenberg 2

Physical registers • Hardware registers • Example: Alpha 21264 microarchitecture • 80 physical integer registers (p 0 -p 79) • 72 physical floating-point registers ECE 721, Spring'20 Prof. Eric Rotenberg 3

Renaming • Assign a unique physical register to a logical register • Number of physical registers > number of logical registers • Multiple definitions of a logical register are each assigned a unique physical register ECE 721, Spring'20 Prof. Eric Rotenberg 4

Structures (required) • Physical register file • Rename map table • Free list • List of unused registers in physical register file • Active list • Active instruction: Instruction that has been dispatched but not yet retired • Active list: List of all active instructions in program order • Equivalent to the Reorder Buffer (ROB) ECE 721, Spring'20 Prof. Eric Rotenberg 5

Structures (optional) • Architectural map table • Recovery from exceptions and mispredictions (branch, load, etc. ) • Restore rename map table to committed state • Shadow map tables • Recovery from branch mispredictions • Restore rename map table to what it was just after the branch ECE 721, Spring'20 Prof. Eric Rotenberg 6

Side notes • Alternate names for map tables • Rename map table: frontend map table • Architectural map table: backend map table • Optional structures • Architectural map table is optional • Shadow map tables are optional • Whether or not these exist depends on recovery strategies. Active list alone can be used for recovery. Recovery strategies affect contents of active list and existence of the architectural and shadow map tables. More on this later… ECE 721, Spring'20 Prof. Eric Rotenberg 7

Renaming • Rename logical source registers • Obtain mappings from rename map table • Rename logical destination register • Pop a free physical register from the free list • Assign the physical register to the logical destination register • Update rename map table to reflect the new mapping ECE 721, Spring'20 Prof. Eric Rotenberg 8

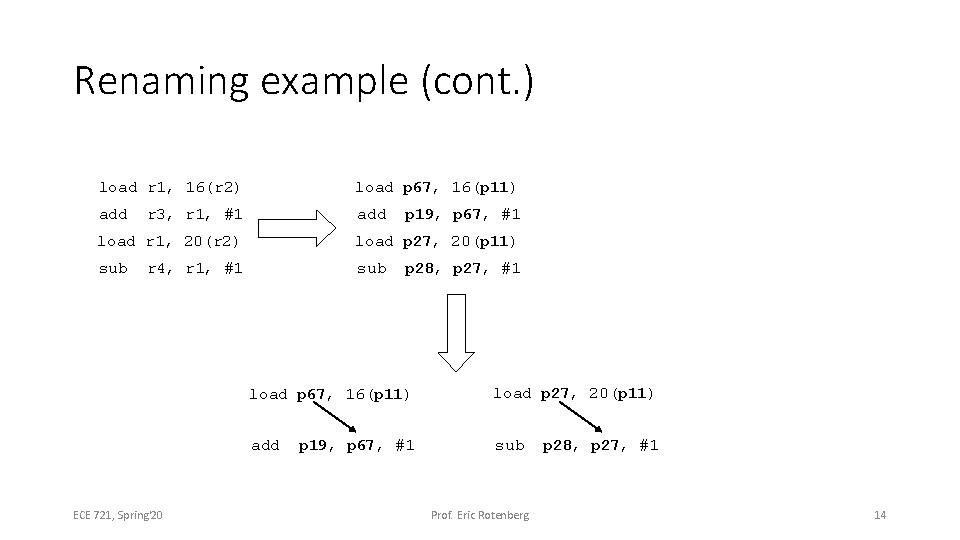

Renaming example load r 1, 16(r 2) add r 3, r 1, #1 load r 1, 20(r 2) sub r 4, r 1, #1 ECE 721, Spring'20 Prof. Eric Rotenberg 9

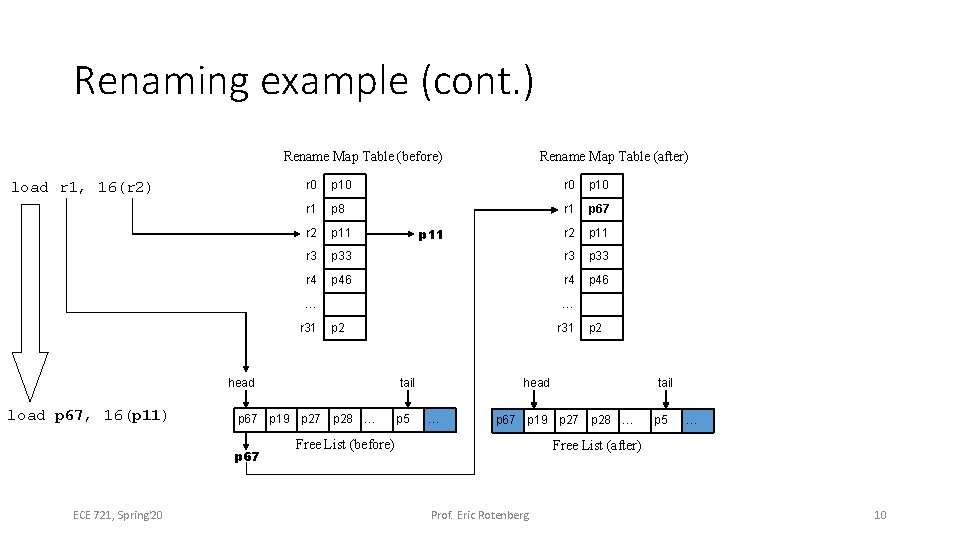

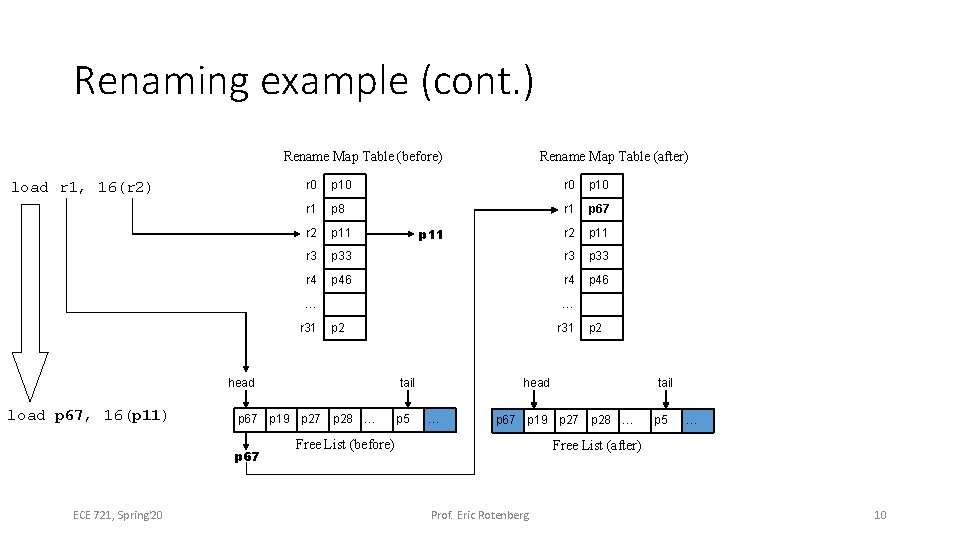

Renaming example (cont. ) Rename Map Table (before) load r 1, 16(r 2) Rename Map Table (after) r 0 p 10 r 1 p 8 r 1 p 67 r 2 p 11 r 3 p 33 r 4 p 46 p 11 … r 31 … p 2 head load p 67, 16(p 11) ECE 721, Spring'20 tail p 67 p 19 p 27 p 28 … p 67 r 31 p 5 p 2 head … tail p 67 p 19 p 27 p 28 … Free List (before) p 5 … Free List (after) Prof. Eric Rotenberg 10

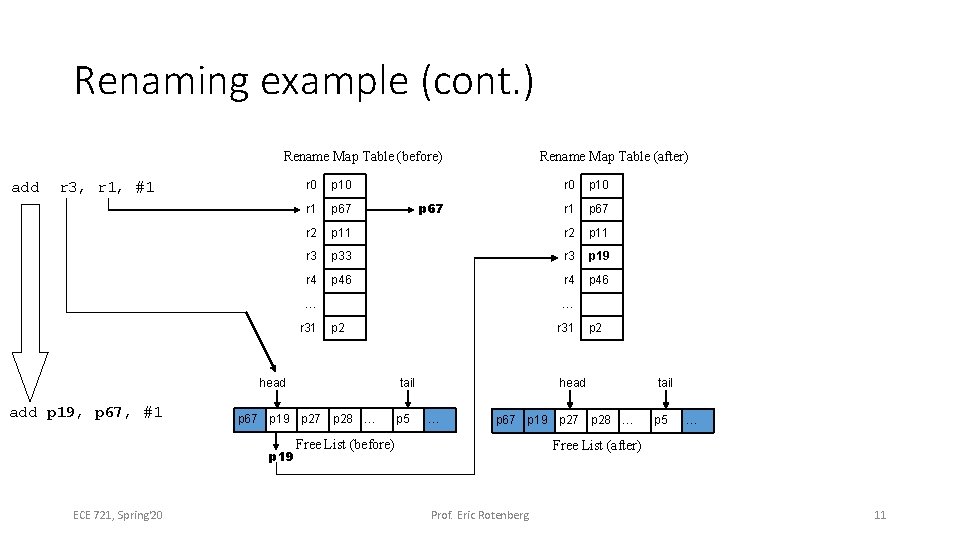

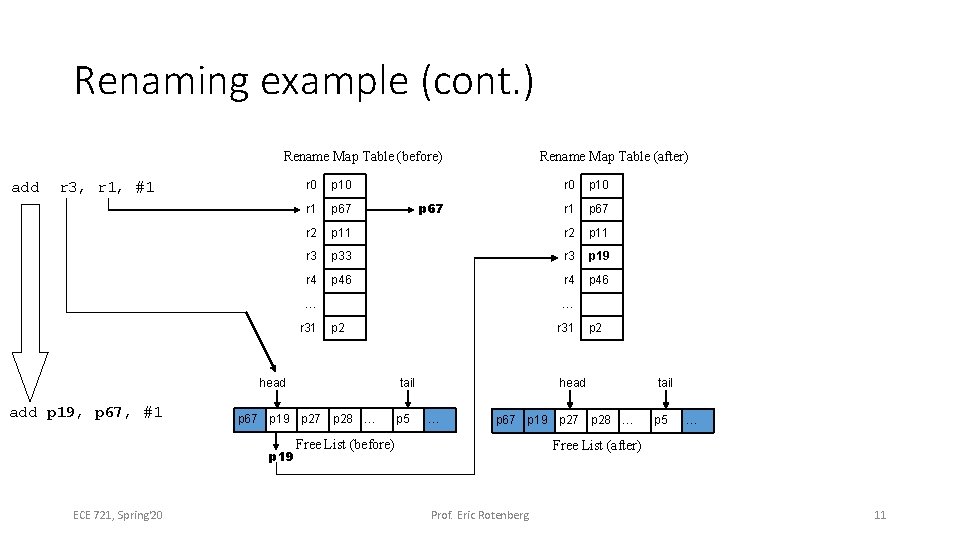

Renaming example (cont. ) Rename Map Table (before) add r 3, r 1, #1 r 0 p 10 r 1 p 67 r 2 Rename Map Table (after) r 0 p 10 r 1 p 67 p 11 r 2 p 11 r 3 p 33 r 3 p 19 r 4 p 46 p 67 … r 31 … p 2 head add p 19, p 67, #1 ECE 721, Spring'20 tail p 67 p 19 p 27 p 28 … p 19 r 31 p 5 p 2 head … p 67 p 19 p 27 p 28 … Free List (before) tail p 5 … Free List (after) Prof. Eric Rotenberg 11

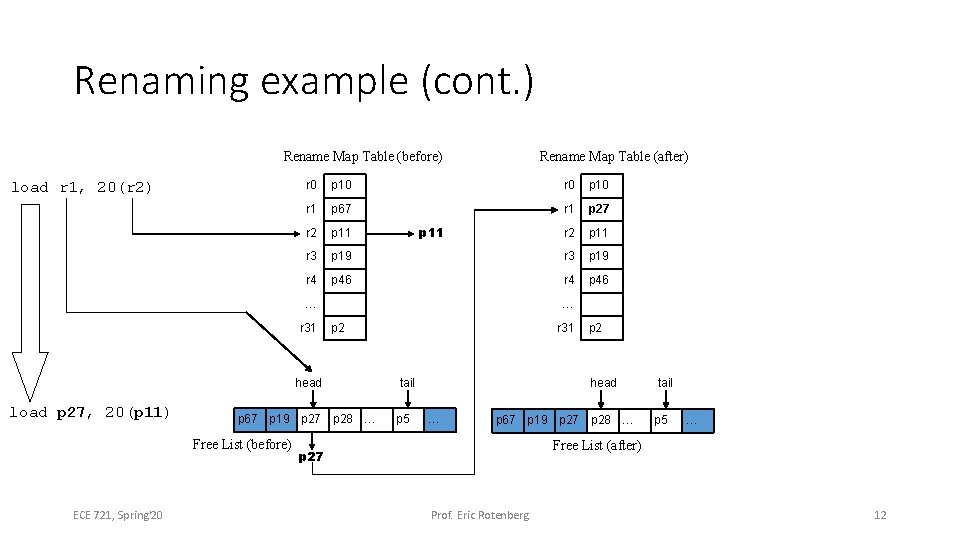

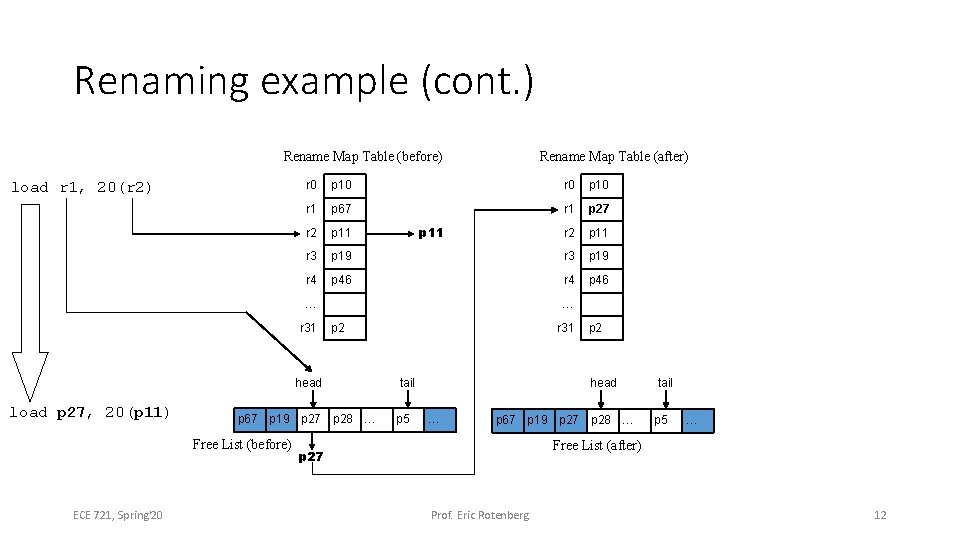

Renaming example (cont. ) Rename Map Table (before) load r 1, 20(r 2) Rename Map Table (after) r 0 p 10 r 1 p 67 r 1 p 27 r 2 p 11 r 3 p 19 r 4 p 46 p 11 … r 31 … p 2 head load p 27, 20(p 11) p 67 p 19 p 27 p 28 … Free List (before) ECE 721, Spring'20 r 31 tail p 5 p 2 head … p 67 p 19 p 27 p 28 … tail p 5 … Free List (after) p 27 Prof. Eric Rotenberg 12

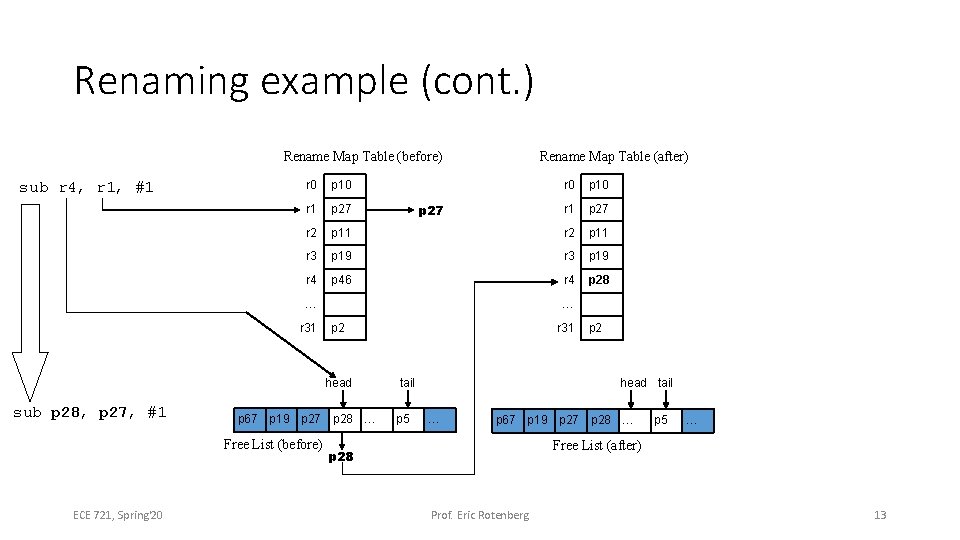

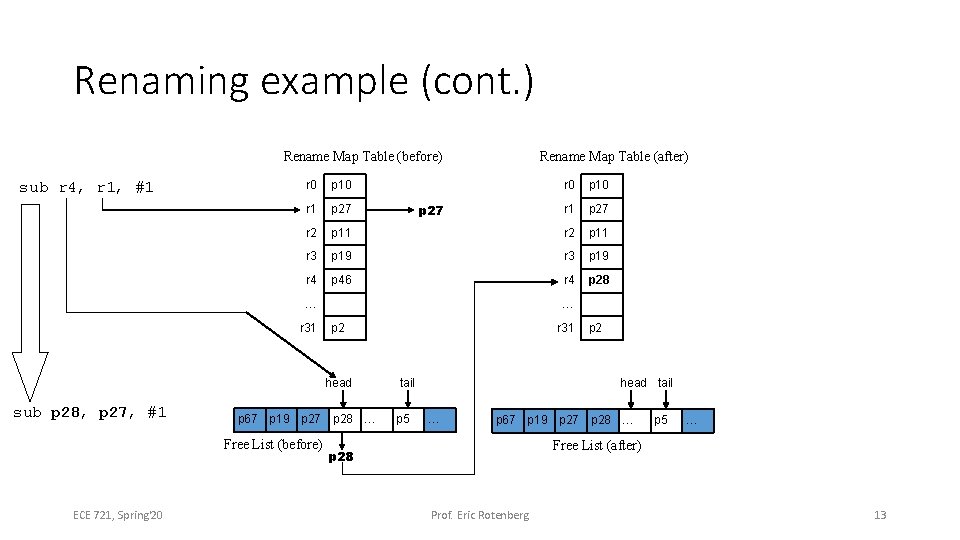

Renaming example (cont. ) Rename Map Table (before) sub r 4, r 1, #1 r 0 p 10 r 1 p 27 r 2 Rename Map Table (after) r 0 p 10 r 1 p 27 p 11 r 2 p 11 r 3 p 19 r 4 p 46 r 4 p 28 p 27 … r 31 … p 2 head sub p 28, p 27, #1 p 67 p 19 p 27 p 28 … Free List (before) ECE 721, Spring'20 r 31 tail p 5 p 2 head tail … p 67 p 19 p 27 p 28 … p 5 … Free List (after) p 28 Prof. Eric Rotenberg 13

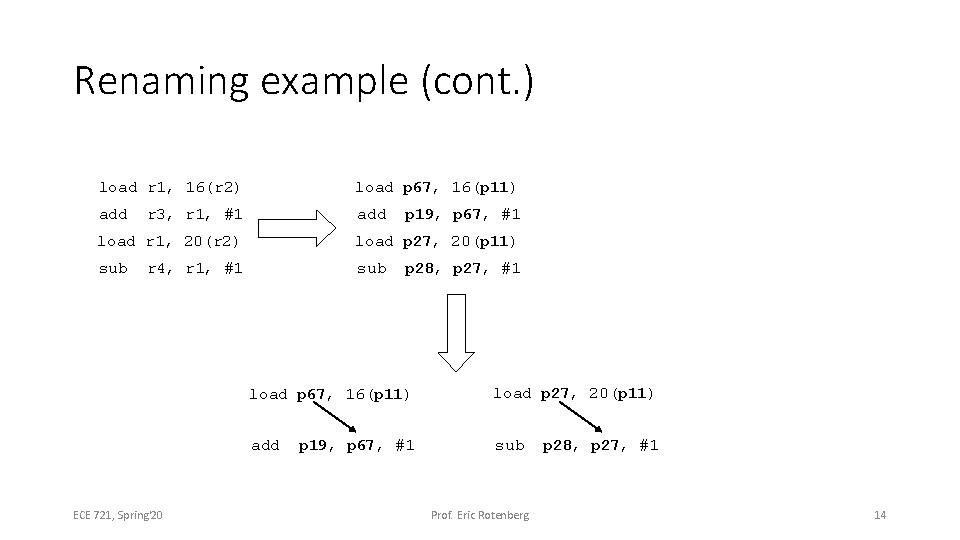

Renaming example (cont. ) load r 1, 16(r 2) load p 67, 16(p 11) add r 3, r 1, #1 p 19, p 67, #1 load r 1, 20(r 2) load p 27, 20(p 11) sub r 4, r 1, #1 ECE 721, Spring'20 p 28, p 27, #1 load p 67, 16(p 11) load p 27, 20(p 11) add sub p 19, p 67, #1 Prof. Eric Rotenberg p 28, p 27, #1 14