Physical Design of Fab Scalar Generated Superscalar Processors

Physical Design of Fab. Scalar Generated Superscalar Processors EE 6052 Class Project Wei Zhang

Outline � Heterogeneous Multi-Core Processors � Fab. Scalar � Physical design of Fab. Scalar generated cores � Things we can do � Conclusion 2 Wei

Heterogeneous Multi-Core Processors Heterogeneous multi-Core processor � Contains multiple, differently-designed superscalar core types that can streamline the execution of diverse programs. � The core types differ from each other and target at different applications. Superscalar processor � Utilizes instruction level parallelism. Executes more than one instruction during a clock-cycle. � Dispatch instructions to redundant functional units such as ALU, multiplier, bit shifter, etc on the processor. “Achilles’ heel” of heterogeneous multi-core processor design � Design and verification effort is multiplied by the number of different core types, which limits the amount of architectural diversity that can be practically implemented. 3 Wei

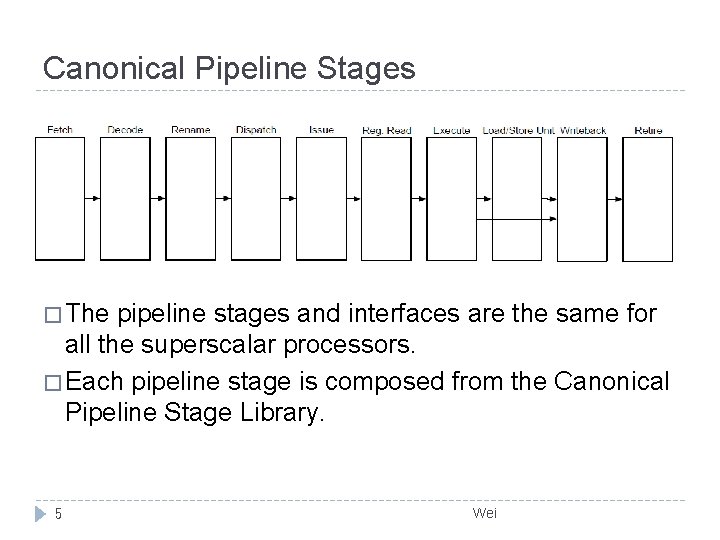

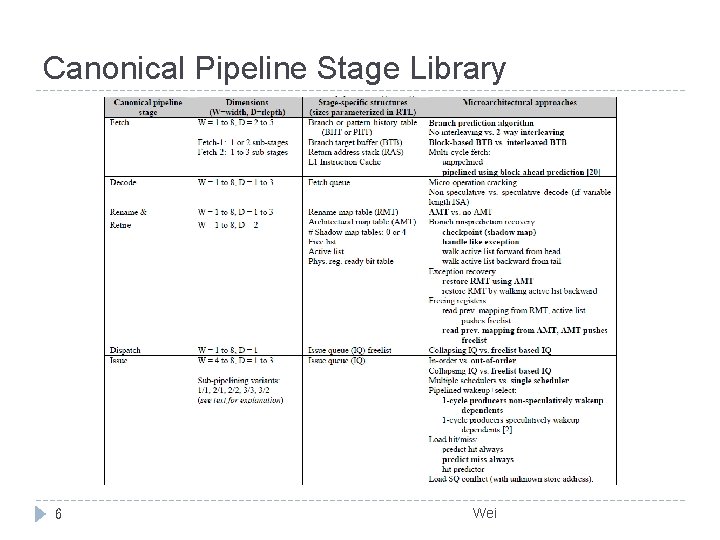

Fab. Scalar �A toolset developed to automatically compose RTL designs of arbitrary cores within a canonical superscalar template. � Frames superscalar processors in a canonical template which defines canonical pipeline stages and interfaces among them. � A Canonical Pipeline Stage Library (CPSL) provides many implementations of each canonical pipeline stage that differs in their superscalar dimensions. � An RTL generation tool uses the template and CPSL to automatically generate an overall core of desired configuration. 4 Wei

Canonical Pipeline Stages � The pipeline stages and interfaces are the same for all the superscalar processors. � Each pipeline stage is composed from the Canonical Pipeline Stage Library. 5 Wei

Canonical Pipeline Stage Library 6 Wei

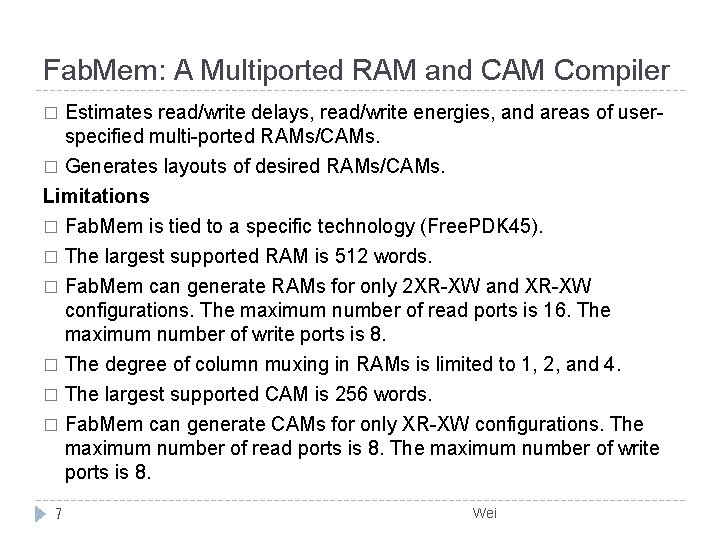

Fab. Mem: A Multiported RAM and CAM Compiler � Estimates read/write delays, read/write energies, and areas of userspecified multi-ported RAMs/CAMs. Generates layouts of desired RAMs/CAMs. Limitations � Fab. Mem is tied to a specific technology (Free. PDK 45). � The largest supported RAM is 512 words. � Fab. Mem can generate RAMs for only 2 XR-XW and XR-XW configurations. The maximum number of read ports is 16. The maximum number of write ports is 8. � The degree of column muxing in RAMs is limited to 1, 2, and 4. � The largest supported CAM is 256 words. � Fab. Mem can generate CAMs for only XR-XW configurations. The maximum number of read ports is 8. The maximum number of write ports is 8. � 7 Wei

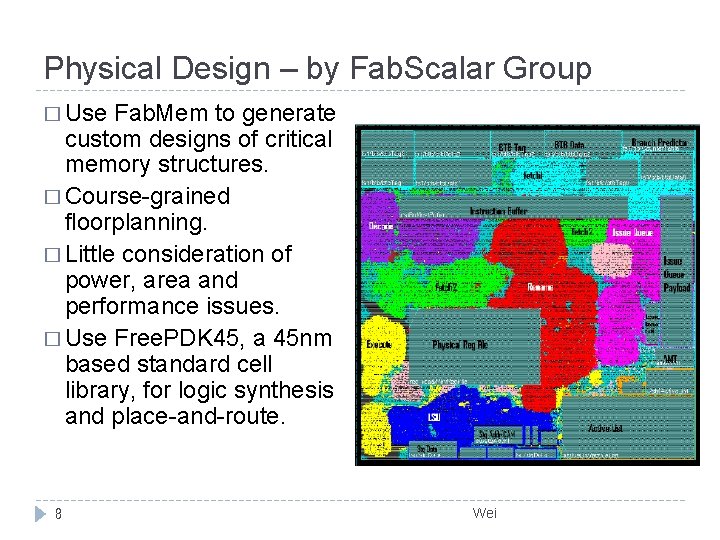

Physical Design – by Fab. Scalar Group � Use Fab. Mem to generate custom designs of critical memory structures. � Course-grained floorplanning. � Little consideration of power, area and performance issues. � Use Free. PDK 45, a 45 nm based standard cell library, for logic synthesis and place-and-route. 8 Wei

Physical Design – Things We Can Do � Floorplanning � Data path design � Memory design – comparison between Fab. Mem and other memory compilers � Cadence vs Synopsys � Power planning 9 Wei

Conclusion � Heterogeneous Multi-Core Processors have many advantages � Fab. Scalar uses canonical pipeline stages for superscalar processor generation. � Physical design of Fab. Scalar generated cores remains to be further investigated. 10 Wei

- Slides: 10