PG Katedra Systemw Mikroelektronicznych ZASTOSOWANIE PROCESORW SYGNAOWYCH Dr

- Slides: 25

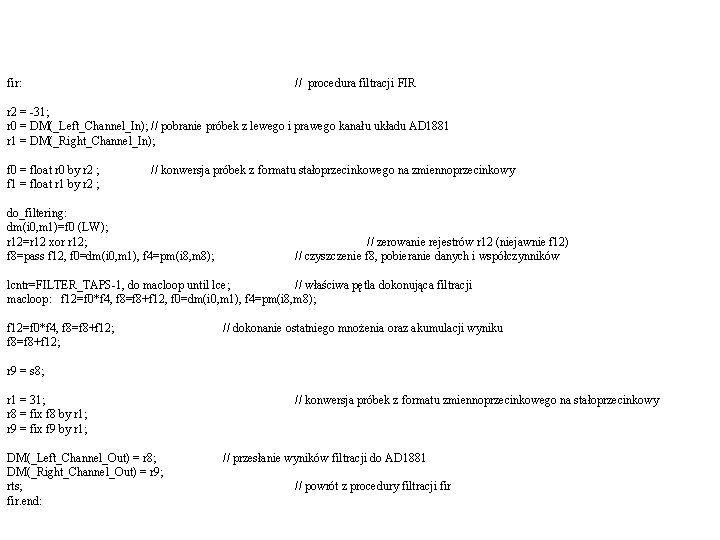

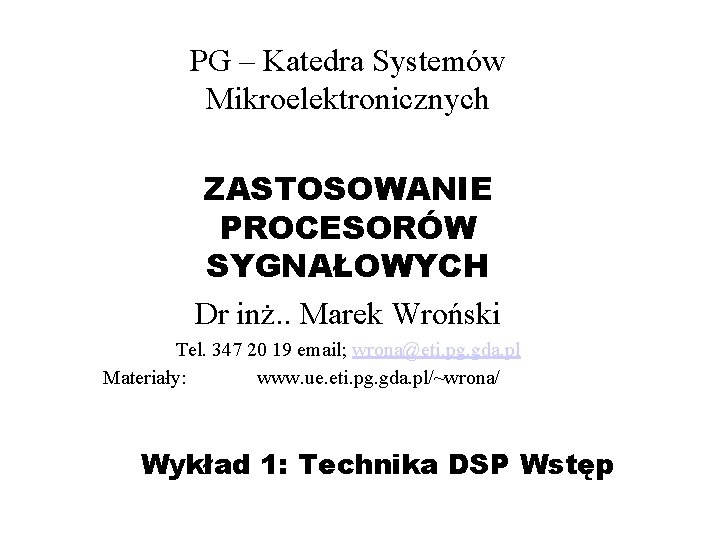

PG – Katedra Systemów Mikroelektronicznych ZASTOSOWANIE PROCESORÓW SYGNAŁOWYCH Dr inż. . Marek Wroński Tel. 347 20 19 email; wrona@eti. pg. gda. pl Materiały: www. ue. eti. pg. gda. pl/~wrona/ Wykład 1: Technika DSP Wstęp

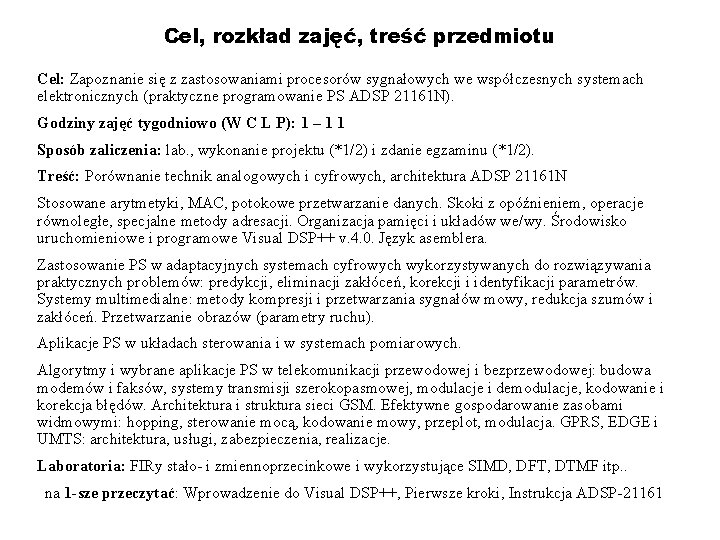

Cel, rozkład zajęć, treść przedmiotu Cel: Zapoznanie się z zastosowaniami procesorów sygnałowych we współczesnych systemach elektronicznych (praktyczne programowanie PS ADSP 21161 N). Godziny zajęć tygodniowo (W C L P): 1 – 1 1 Sposób zaliczenia: lab. , wykonanie projektu (*1/2) i zdanie egzaminu (*1/2). Treść: Porównanie technik analogowych i cyfrowych, architektura ADSP 21161 N Stosowane arytmetyki, MAC, potokowe przetwarzanie danych. Skoki z opóźnieniem, operacje równoległe, specjalne metody adresacji. Organizacja pamięci i układów we/wy. Środowisko uruchomieniowe i programowe Visual DSP++ v. 4. 0. Język asemblera. Zastosowanie PS w adaptacyjnych systemach cyfrowych wykorzystywanych do rozwiązywania praktycznych problemów: predykcji, eliminacji zakłóceń, korekcji i identyfikacji parametrów. Systemy multimedialne: metody kompresji i przetwarzania sygnałów mowy, redukcja szumów i zakłóceń. Przetwarzanie obrazów (parametry ruchu). Aplikacje PS w układach sterowania i w systemach pomiarowych. Algorytmy i wybrane aplikacje PS w telekomunikacji przewodowej i bezprzewodowej: budowa modemów i faksów, systemy transmisji szerokopasmowej, modulacje i demodulacje, kodowanie i korekcja błędów. Architektura i struktura sieci GSM. Efektywne gospodarowanie zasobami widmowymi: hopping, sterowanie mocą, kodowanie mowy, przeplot, modulacja. GPRS, EDGE i UMTS: architektura, usługi, zabezpieczenia, realizacje. Laboratoria: FIRy stało- i zmiennoprzecinkowe i wykorzystujące SIMD, DFT, DTMF itp. . na 1 -sze przeczytać: Wprowadzenie do Visual DSP++, Pierwsze kroki, Instrukcja ADSP-21161

Zalety i ograniczenia techniki DSP Zalety przetwarzania sygnałów w sposób cyfrowy: § precyzja i przewidywalność • stabilność (brak zjawiska dryftu temperaturowego i starzenia się elementów) • reprogramowalność • prostsza konstrukcja sprzętowa projektu • koszt projektu w niewielkim stopniu zależy od złożoności algorytmu przetwarzania • skrócenie czasu „od projektu do gotowego wyrobu” (prostsza procedura testowania) • kontrola nad poziomem szumu wprowadzanym w trakcie przetwarzania sygnału Ograniczenia: • ograniczone pasmo (szybkość próbkowania) • ograniczony zakres dynamiczny • szum kwantyzacji • błędy zaokrągleń

Różnice pomiędzy DSP a standardowym procesorem • Równoległe mnożenie z akumulacją wykonywane w jednym cyklu, • Generatory adresu ze specjalnymi trybami, • Wydajny zestaw instrukcji z jedno-cyklowymi równoległymi operacjami matematycznymi i przestrzenią w pamięci oraz sprawną realizacją pętli, • Zintegrowany wewnętrzny koprocesor DMA i RAM dla jednoczesnych operacji wykonywanych przez CPU i układy we/wy • • Podział procesorów DSP Stałoprzecinkowe (szybsze , tańsze i pobierają mniej mocy) Zmiennoprzecinkowe (większa dynamika i stosunek sygnał/szum) 16, 32, 64 bitowe (wg wymaganej precyzji obliczeń) Różne formaty liczb

DSP - Zastosowania • • Telekomunikacja: kompresja dźwięku i obrazu, redukcja pogłosu, komutacja, filtrowanie (telefonia komórkowa – generacje 2. 5 G, 3 G – UMTS, CDMA 2000, 4 G) Wojsko: radary i sonary, szyfrowanie, nawigacja, GPS – Global Positioning Satellite Medycyna: analiza i przetwarzanie obrazów EKG, rezonansu jądrowego MRI i tomografii PET. . , składanie danych medycznych – kompresja Przemysł kosmiczny: wyostrzanie zdjęć, kompresja danych, analiza sygnałów z czujników Przemysł: poszukiwania złóż ropy i minerałów, monitoring i sterowanie procesami, przeprowadzanie testów, projektowanie – CAD Zastosowania komercyjne: multimedia, wizualne efekty specjalne, wideo konferencje, GPS Nauka: nagrywanie i analiza wstrząsów ziemi, gromadzenie danych, analiza spekteralna, symulacje i modelowanie, sterowanie w czasie rzeczywistym

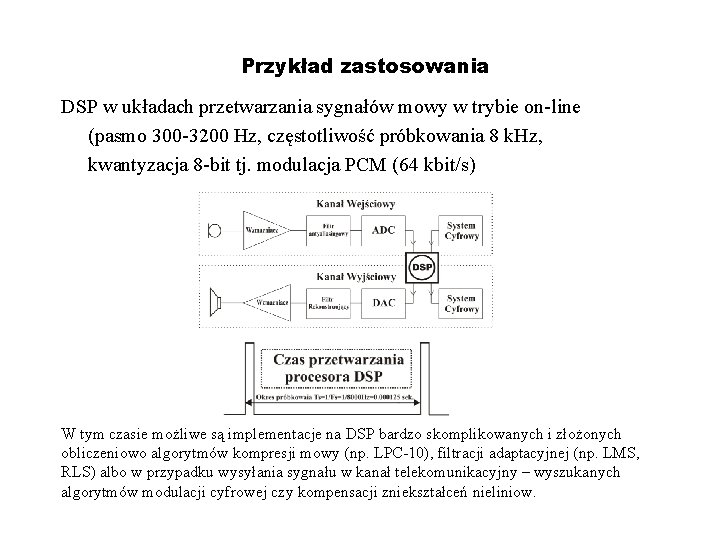

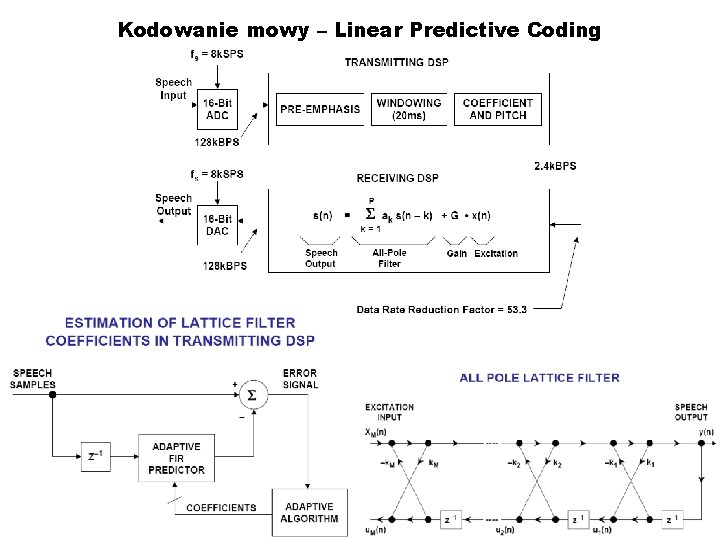

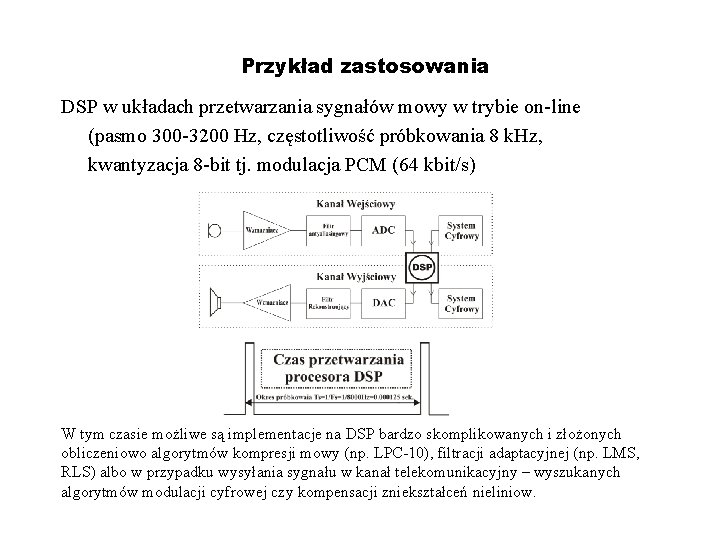

Przykład zastosowania DSP w układach przetwarzania sygnałów mowy w trybie on-line (pasmo 300 -3200 Hz, częstotliwość próbkowania 8 k. Hz, kwantyzacja 8 -bit tj. modulacja PCM (64 kbit/s) W tym czasie możliwe są implementacje na DSP bardzo skomplikowanych i złożonych obliczeniowo algorytmów kompresji mowy (np. LPC-10), filtracji adaptacyjnej (np. LMS, RLS) albo w przypadku wysyłania sygnału w kanał telekomunikacyjny – wyszukanych algorytmów modulacji cyfrowej czy kompensacji zniekształceń nieliniow.

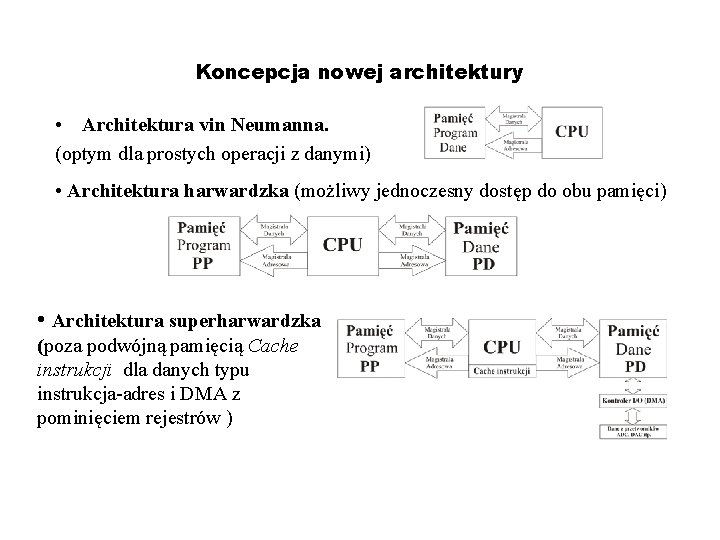

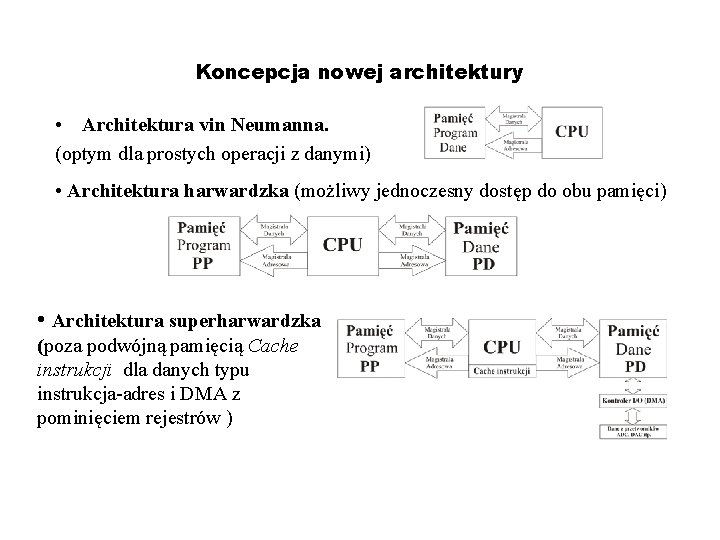

Koncepcja nowej architektury • Architektura vin Neumanna. (optym dla prostych operacji z danymi) • Architektura harwardzka (możliwy jednoczesny dostęp do obu pamięci) • Architektura superharwardzka (poza podwójną pamięcią Cache instrukcji dla danych typu instrukcja-adres i DMA z pominięciem rejestrów )

Konfiguracja DSP • Oprócz wersji „okrojonych”, wersje procesorów z dodatkowymi elementy dla różnorodnych zastosowań, a także niezbędne narzędzia

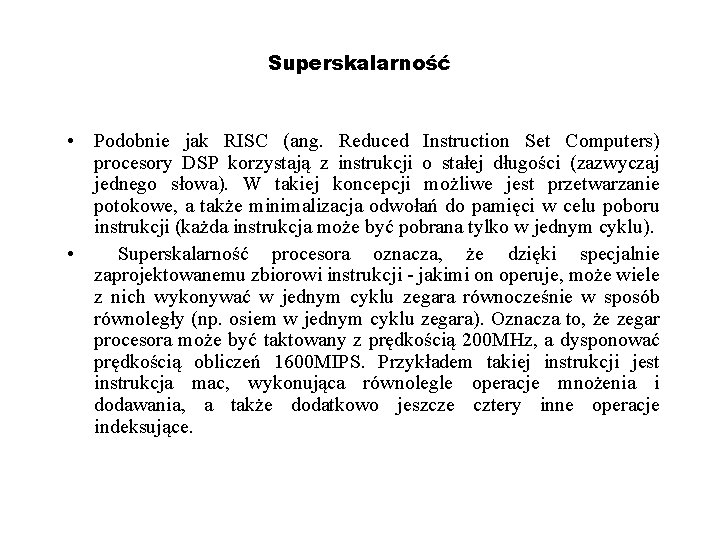

Superskalarność • Podobnie jak RISC (ang. Reduced Instruction Set Computers) procesory DSP korzystają z instrukcji o stałej długości (zazwyczaj jednego słowa). W takiej koncepcji możliwe jest przetwarzanie potokowe, a także minimalizacja odwołań do pamięci w celu poboru instrukcji (każda instrukcja może być pobrana tylko w jednym cyklu). • Superskalarność procesora oznacza, że dzięki specjalnie zaprojektowanemu zbiorowi instrukcji - jakimi on operuje, może wiele z nich wykonywać w jednym cyklu zegara równocześnie w sposób równoległy (np. osiem w jednym cyklu zegara). Oznacza to, że zegar procesora może być taktowany z prędkością 200 MHz, a dysponować prędkością obliczeń 1600 MIPS. Przykładem takiej instrukcji jest instrukcja mac, wykonująca równolegle operacje mnożenia i dodawania, a także dodatkowo jeszcze cztery inne operacje indeksujące.

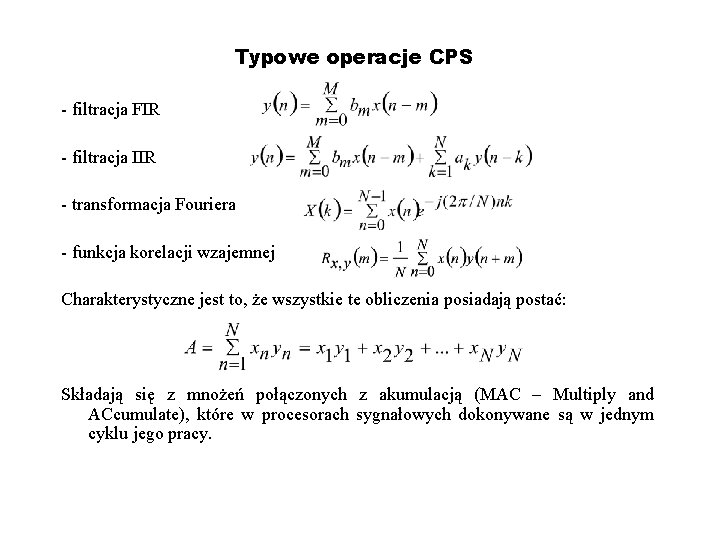

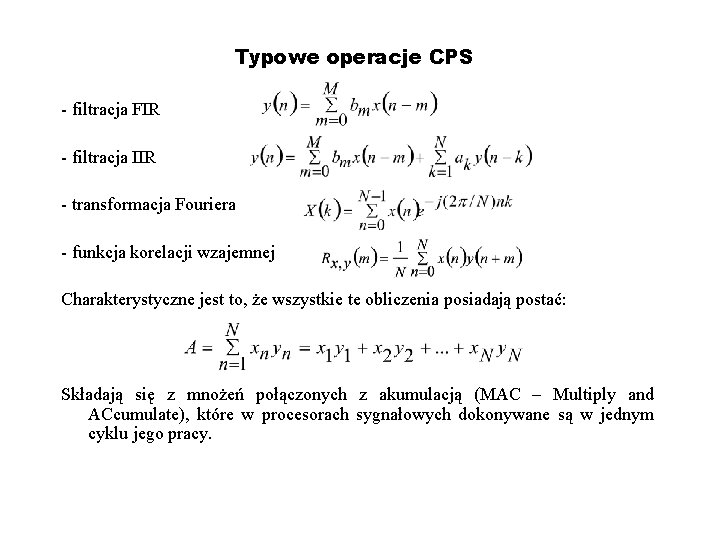

Typowe operacje CPS - filtracja FIR - filtracja IIR - transformacja Fouriera - funkcja korelacji wzajemnej Charakterystyczne jest to, że wszystkie te obliczenia posiadają postać: Składają się z mnożeń połączonych z akumulacją (MAC – Multiply and ACcumulate), które w procesorach sygnałowych dokonywane są w jednym cyklu jego pracy.

Bufory cyrkularne Zasada działania operacji MAC opiera się na sprzętowych rozwiązaniach gwarantujących optymalizację wykonywanych przez nie zadań (tzn. mnożenia i jednoczesnej akumulacji) poprzez specjalnie zaprojektowane układy adresujące pamięć DAGs (ang. Data Address Generatorors) oraz odpowiednie towarzyszące im zbiory rejestrów indeksujących. Wykorzystują one tryb pracy polegający na organizowaniu pamięci w bufory adresowanie w sposób cykliczny. „Przesunięcie” dokonywane jest tylko poprzez modyfikację stosownych rejestrów wskazujących ich odpowiednią kolejność. Dodatkowo układy DAGs posiadają możliwość adresowania polegającą na bitowym odwracaniu adresów (ang. Bit Reverse Addressing). Własność ta jest szczególnie przydatna w przypadku obliczeń korzystających z algorytmów szybkiej transformacji Fouriera (FFT).

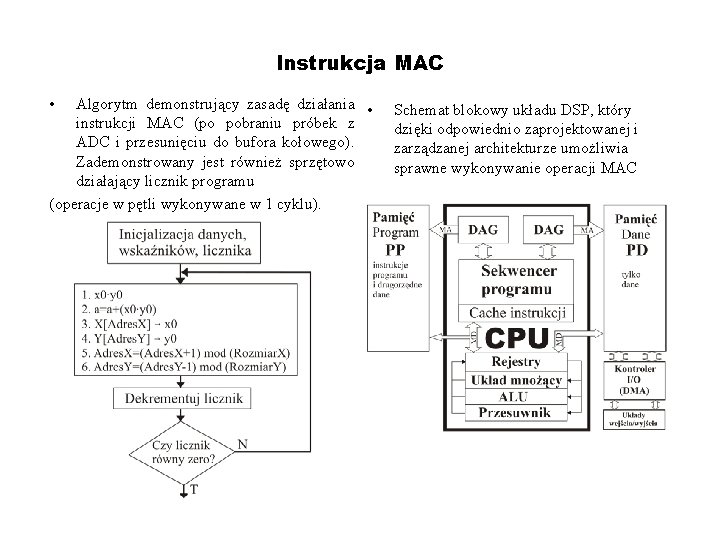

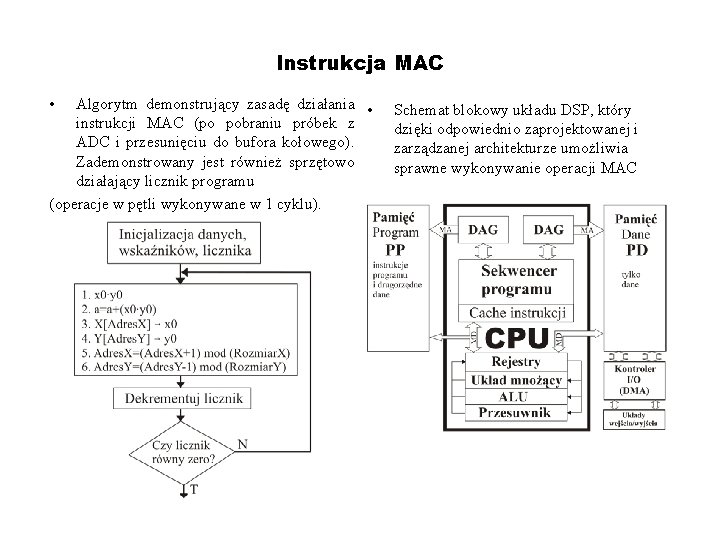

Instrukcja MAC • Algorytm demonstrujący zasadę działania • instrukcji MAC (po pobraniu próbek z ADC i przesunięciu do bufora kołowego). Zademonstrowany jest również sprzętowo działający licznik programu (operacje w pętli wykonywane w 1 cyklu). Schemat blokowy układu DSP, który dzięki odpowiednio zaprojektowanej i zarządzanej architekturze umożliwia sprawne wykonywanie operacji MAC

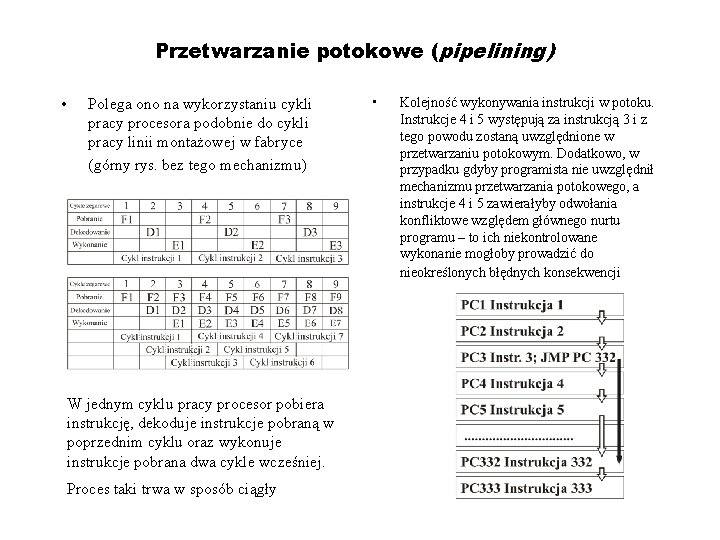

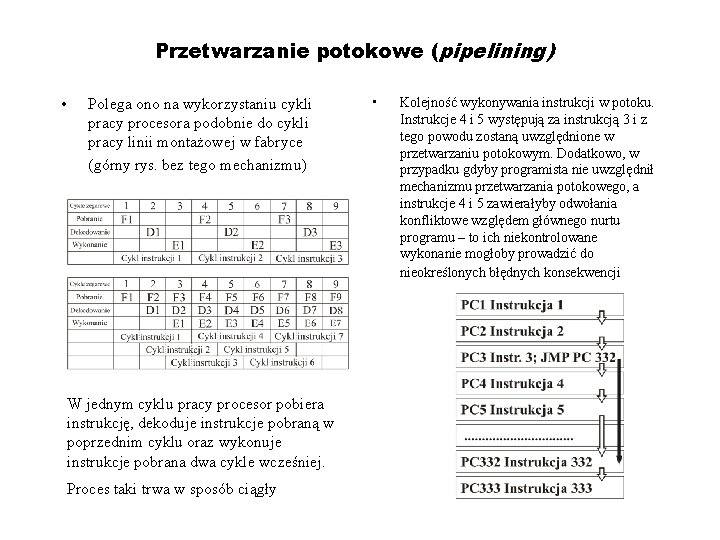

Przetwarzanie potokowe (pipelining) • Polega ono na wykorzystaniu cykli pracy procesora podobnie do cykli pracy linii montażowej w fabryce (górny rys. bez tego mechanizmu) W jednym cyklu pracy procesor pobiera instrukcję, dekoduje instrukcje pobraną w poprzednim cyklu oraz wykonuje instrukcje pobrana dwa cykle wcześniej. Proces taki trwa w sposób ciągły • Kolejność wykonywania instrukcji w potoku. Instrukcje 4 i 5 występują za instrukcją 3 i z tego powodu zostaną uwzględnione w przetwarzaniu potokowym. Dodatkowo, w przypadku gdyby programista nie uwzględnił mechanizmu przetwarzania potokowego, a instrukcje 4 i 5 zawierałyby odwołania konfliktowe względem głównego nurtu programu – to ich niekontrolowane wykonanie mogłoby prowadzić do nieokreślonych błędnych konsekwencji

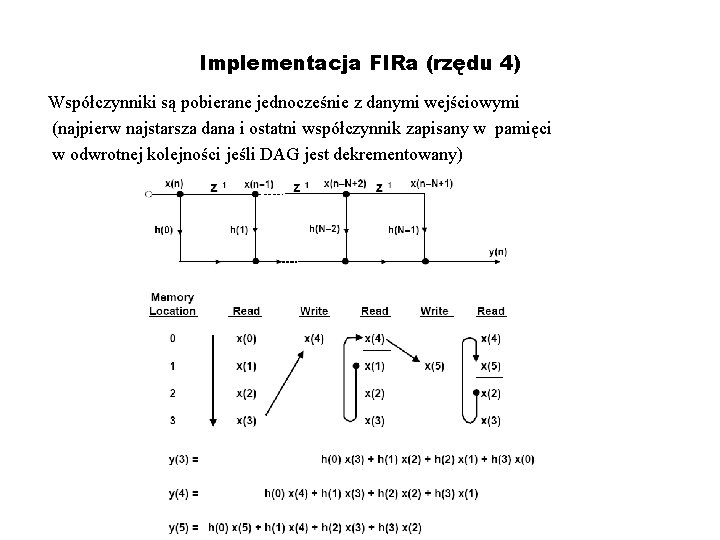

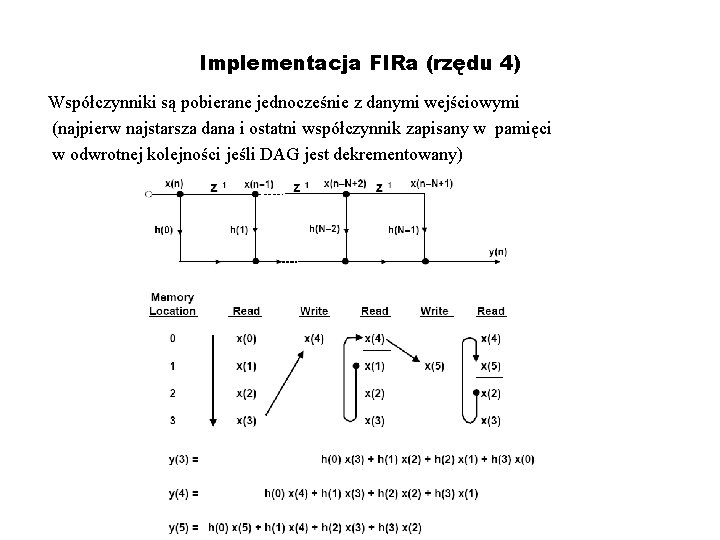

Implementacja FIRa (rzędu 4) Współczynniki są pobierane jednocześnie z danymi wejściowymi (najpierw najstarsza dana i ostatni współczynnik zapisany w pamięci w odwrotnej kolejności jeśli DAG jest dekrementowany)

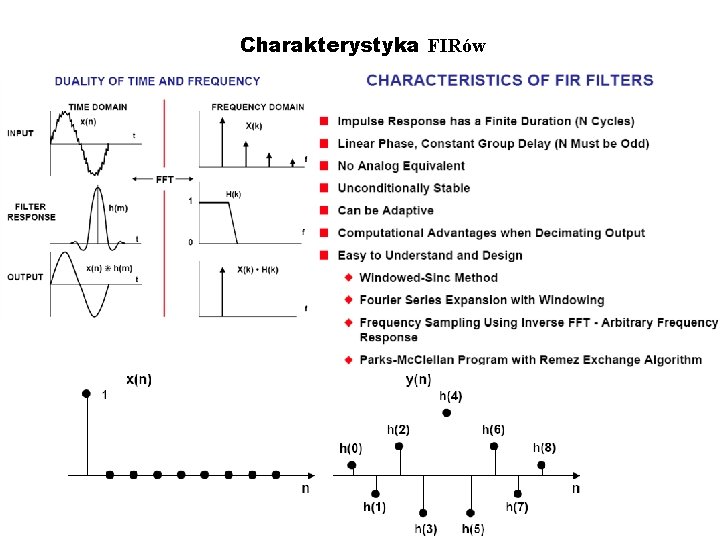

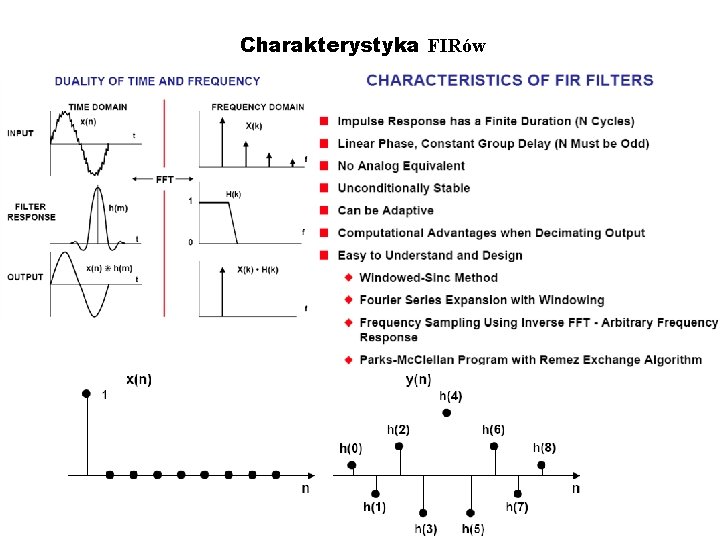

Charakterystyka FIRów

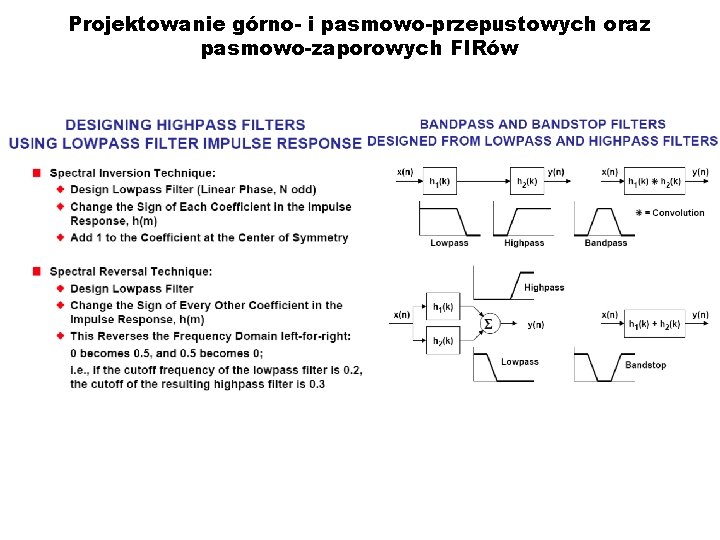

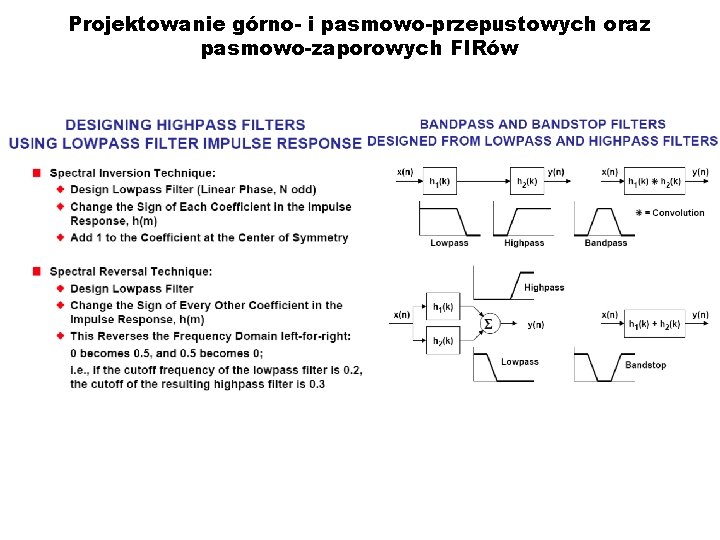

Projektowanie górno- i pasmowo-przepustowych oraz pasmowo-zaporowych FIRów

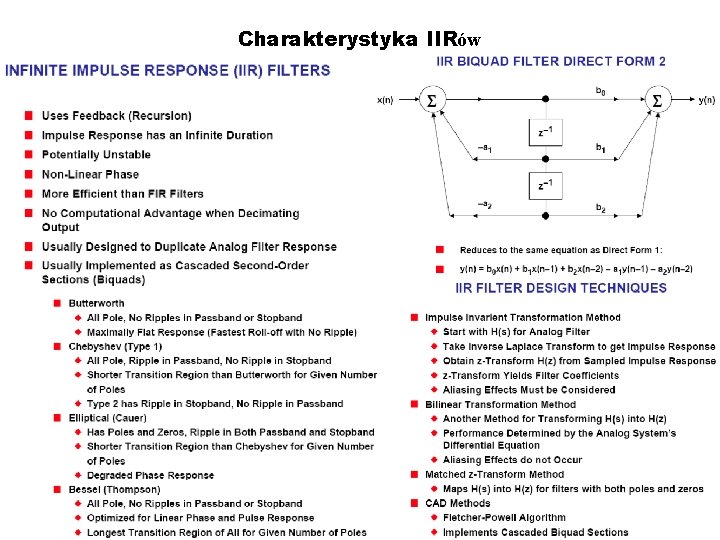

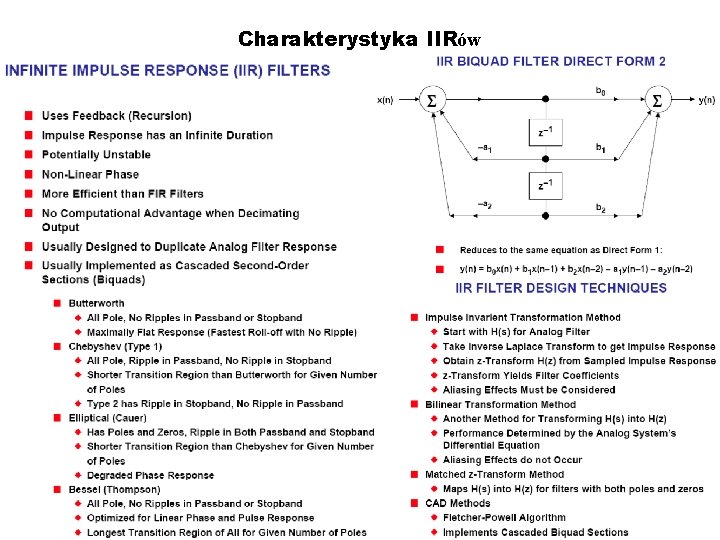

Charakterystyka IIRów

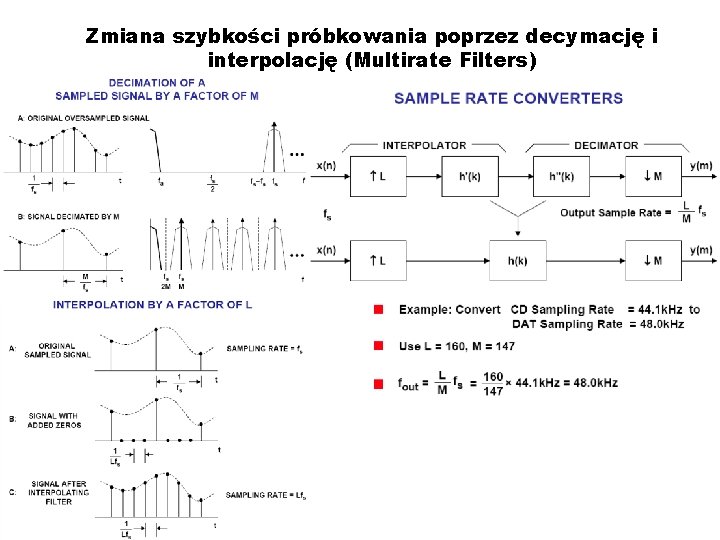

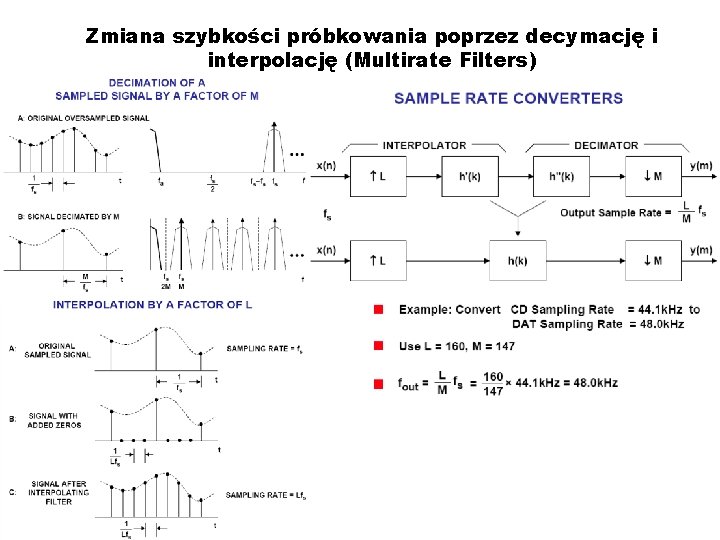

Zmiana szybkości próbkowania poprzez decymację i interpolację (Multirate Filters)

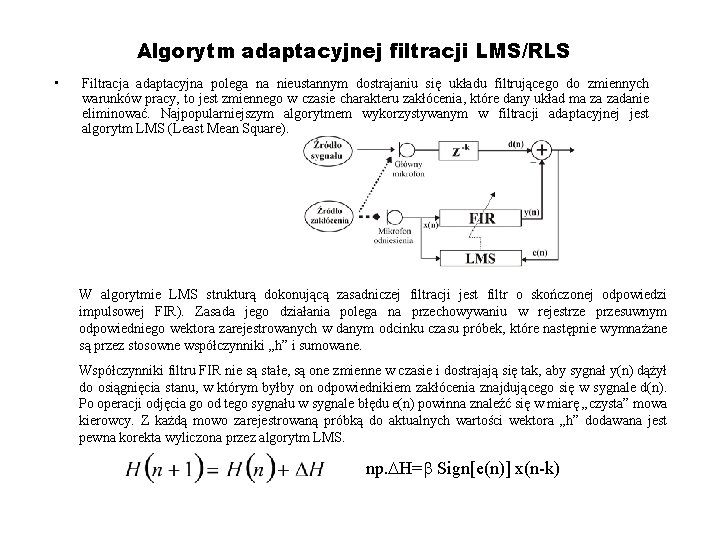

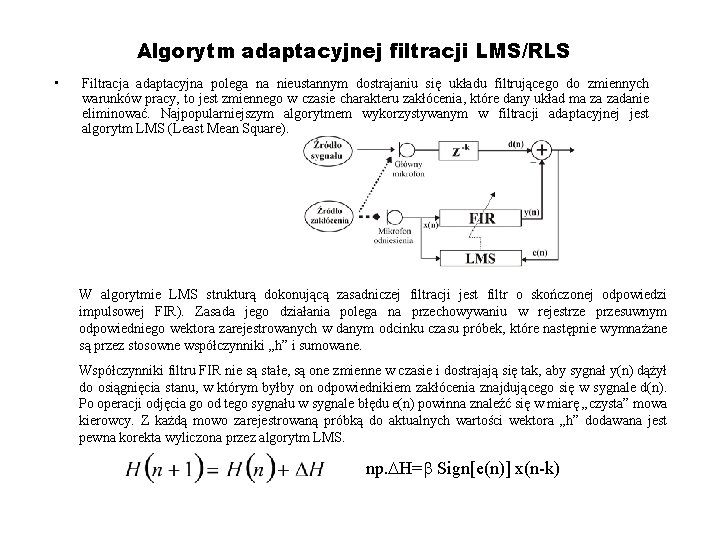

Algorytm adaptacyjnej filtracji LMS/RLS • Filtracja adaptacyjna polega na nieustannym dostrajaniu się układu filtrującego do zmiennych warunków pracy, to jest zmiennego w czasie charakteru zakłócenia, które dany układ ma za zadanie eliminować. Najpopularniejszym algorytmem wykorzystywanym w filtracji adaptacyjnej jest algorytm LMS (Least Mean Square). W algorytmie LMS strukturą dokonującą zasadniczej filtracji jest filtr o skończonej odpowiedzi impulsowej FIR). Zasada jego działania polega na przechowywaniu w rejestrze przesuwnym odpowiedniego wektora zarejestrowanych w danym odcinku czasu próbek, które następnie wymnażane są przez stosowne współczynniki „h” i sumowane. Współczynniki filtru FIR nie są stałe, są one zmienne w czasie i dostrajają się tak, aby sygnał y(n) dążył do osiągnięcia stanu, w którym byłby on odpowiednikiem zakłócenia znajdującego się w sygnale d(n). Po operacji odjęcia go od tego sygnału w sygnale błędu e(n) powinna znaleźć się w miarę „czysta” mowa kierowcy. Z każdą mowo zarejestrowaną próbką do aktualnych wartości wektora „h” dodawana jest pewna korekta wyliczona przez algorytm LMS. np. DH=b Sign[e(n)] x(n-k)

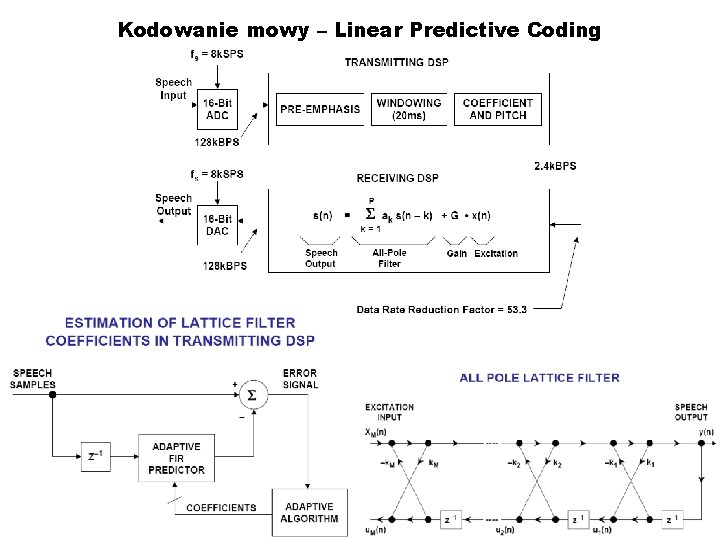

Kodowanie mowy – Linear Predictive Coding

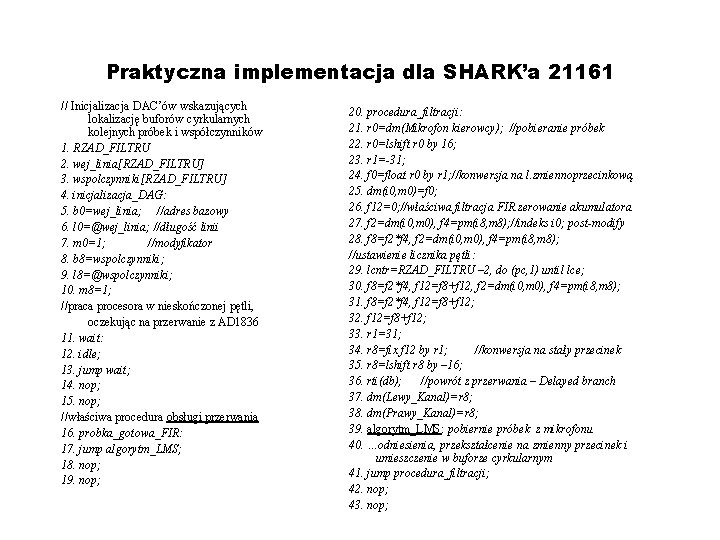

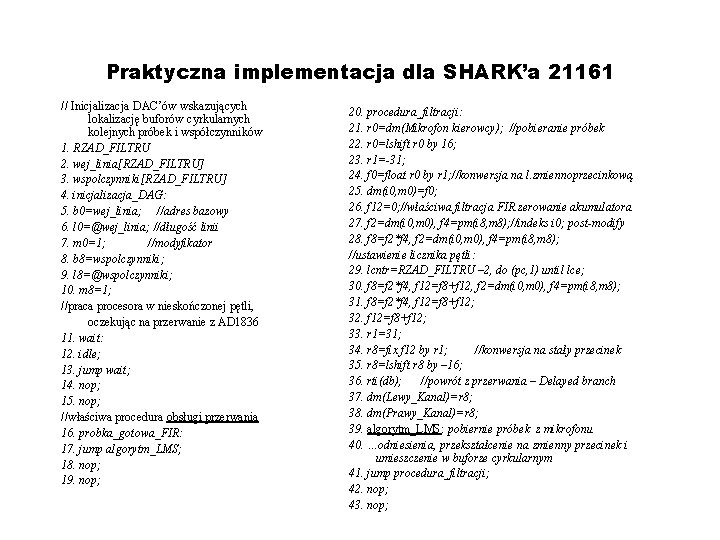

Praktyczna implementacja dla SHARK’a 21161 // Inicjalizacja DAC’ów wskazujących lokalizację buforów cyrkularnych kolejnych próbek i współczynników 1. RZAD_FILTRU 2. wej_linia[RZAD_FILTRU] 3. wspolczynniki[RZAD_FILTRU] 4. inicjalizacja_DAG: 5. b 0=wej_linia; //adres bazowy 6. l 0=@wej_linia; //długość linii 7. m 0=1; //modyfikator 8. b 8=wspolczynniki; 9. l 8=@wspolczynniki; 10. m 8=1; //praca procesora w nieskończonej pętli, oczekując na przerwanie z AD 1836 11. wait: 12. idle; 13. jump wait; 14. nop; 15. nop; //właściwa procedura obsługi przerwania 16. probka_gotowa_FIR: 17. jump algorytm_LMS; 18. nop; 19. nop; 20. procedura_filtracji: 21. r 0=dm(Mikrofon kierowcy); //pobieranie próbek 22. r 0=lshift r 0 by 16; 23. r 1=-31; 24. f 0=float r 0 by r 1; //konwersja na l. zmiennoprzecinkową 25. dm(i 0, m 0)=f 0; 26. f 12=0; //właściwa filtracja FIR. zerowanie akumulatora 27. f 2=dm(i 0, m 0), f 4=pm(i 8, m 8); //indeks i 0; post-modify 28. f 8=f 2*f 4, f 2=dm(i 0, m 0), f 4=pm(i 8, m 8); //ustawienie licznika pętli: 29. lcntr=RZAD_FILTRU – 2, do (pc, 1) until lce; 30. f 8=f 2*f 4, f 12=f 8+f 12, f 2=dm(i 0, m 0), f 4=pm(i 8, m 8); 31. f 8=f 2*f 4, f 12=f 8+f 12; 32. f 12=f 8+f 12; 33. r 1=31; 34. r 8=fix f 12 by r 1; //konwersja na stały przecinek 35. r 8=lshift r 8 by – 16; 36. rti(db); //powrót z przerwania – Delayed branch 37. dm(Lewy_Kanal)=r 8; 38. dm(Prawy_Kanal)=r 8; 39. algorytm_LMS: pobiernie próbek z mikrofonu 40. …odniesienia, przekształcenie na zmienny przecinek i umieszczenie w buforze cyrkularnym 41. jump procedura_filtracji; 42. nop; 43. nop;

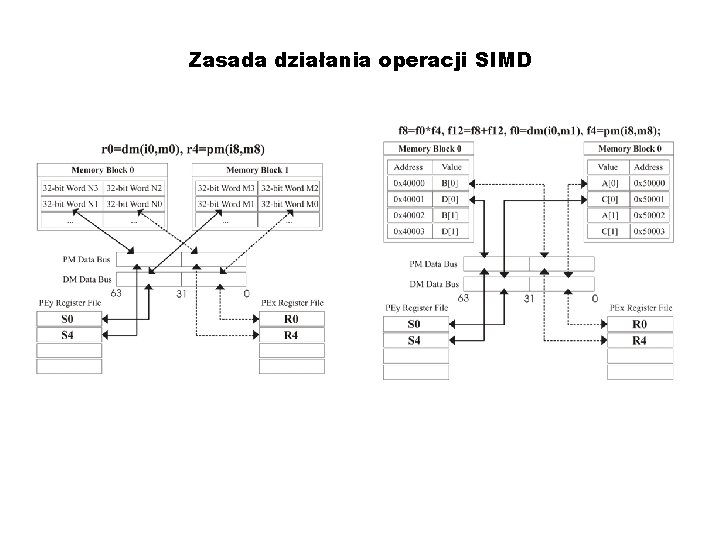

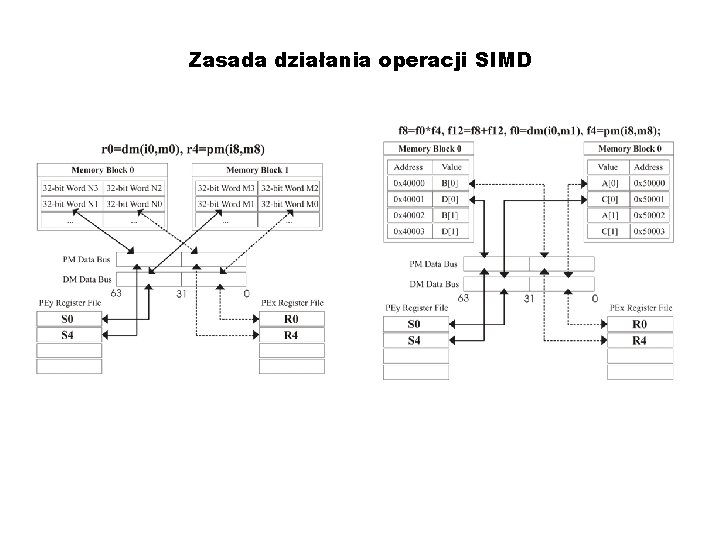

Idea operacji SIMD • Operacje SIMD (Single-Instruction Multiple-Data) poprawiają wydajność procesora przy przetwarzaniu danych poprzez “rozbicie” dużych danych (zajmujących cały rejestr) znajdujących się w specjalnych rejestrach, na ich mniejsze odpowiedniki (zajmujące dwie połówki rejestru). Dzięki temu możliwe jest zwielokrotnienie działania tej samej operacji na równoległe przetwarzanie dwóch danych znajdujących się w tym samym rejestrze. Szczególną zaletą tej techniki jest możliwość zwielokrotnienia działania tych samych algorytmów na dwa równoległe kanały przetwarzania danych.

Zasada działania operacji SIMD

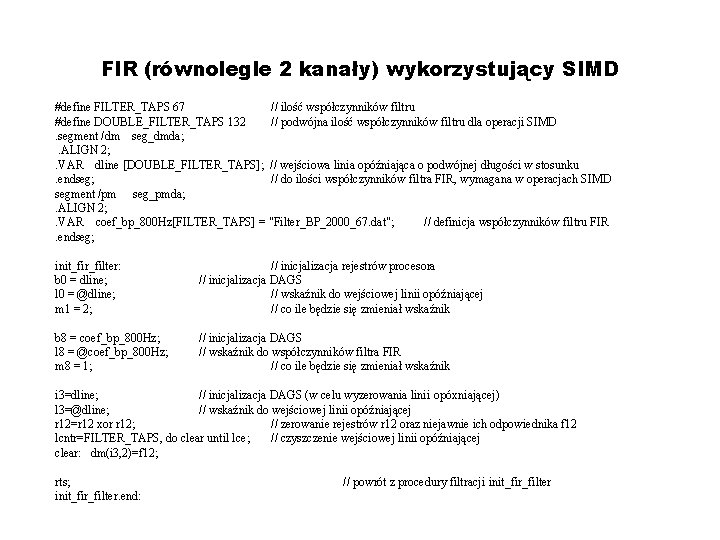

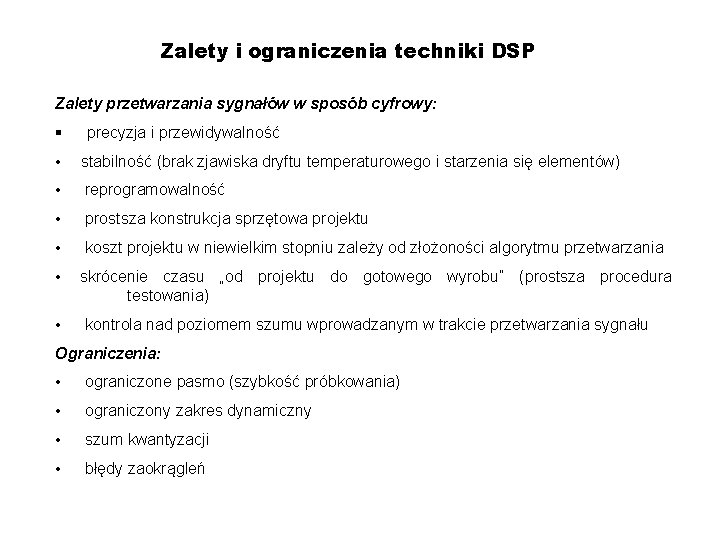

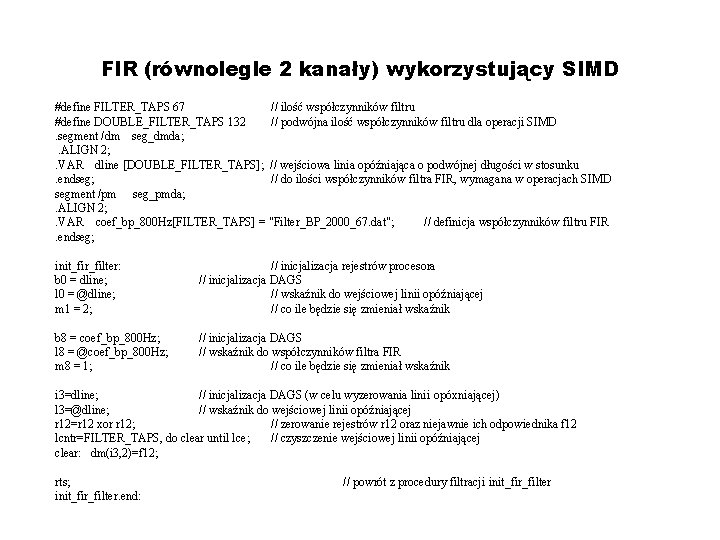

FIR (równolegle 2 kanały) wykorzystujący SIMD #define FILTER_TAPS 67 // ilość współczynników filtru #define DOUBLE_FILTER_TAPS 132 // podwójna ilość współczynników filtru dla operacji SIMD. segment /dm seg_dmda; . ALIGN 2; . VAR dline [DOUBLE_FILTER_TAPS]; // wejściowa linia opóźniająca o podwójnej długości w stosunku. endseg; // do ilości współczynników filtra FIR, wymagana w operacjach SIMD segment /pm seg_pmda; . ALIGN 2; . VAR coef_bp_800 Hz[FILTER_TAPS] = "Filter_BP_2000_67. dat"; // definicja współczynników filtru FIR. endseg; init_fir_filter: b 0 = dline; l 0 = @dline; m 1 = 2; // inicjalizacja rejestrów procesora // inicjalizacja DAGS // wskaźnik do wejściowej linii opóźniającej // co ile będzie się zmieniał wskaźnik b 8 = coef_bp_800 Hz; l 8 = @coef_bp_800 Hz; m 8 = 1; // inicjalizacja DAGS // wskaźnik do współczynników filtra FIR // co ile będzie się zmieniał wskaźnik i 3=dline; // inicjalizacja DAGS (w celu wyzerowania linii opóxniającej) l 3=@dline; // wskaźnik do wejściowej linii opóźniającej r 12=r 12 xor r 12; // zerowanie rejestrów r 12 oraz niejawnie ich odpowiednika f 12 lcntr=FILTER_TAPS, do clear until lce; // czyszczenie wejściowej linii opóźniającej clear: dm(i 3, 2)=f 12; rts; init_fir_filter. end: // powrót z procedury filtracji init_fir_filter

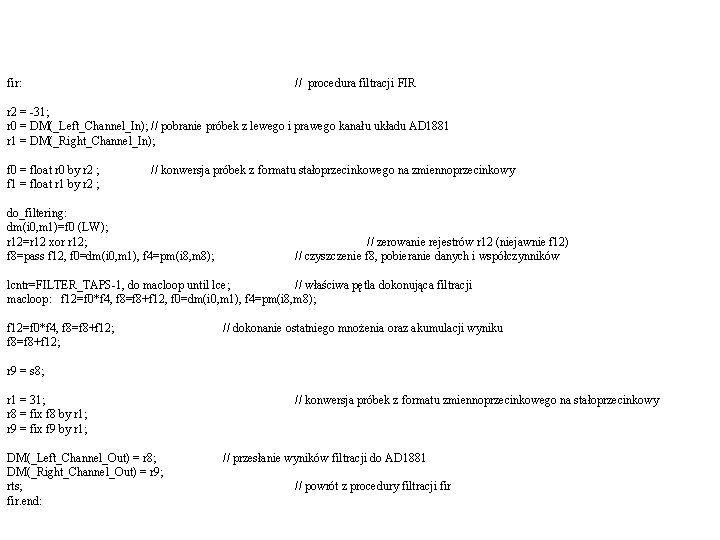

fir: // procedura filtracji FIR r 2 = -31; r 0 = DM(_Left_Channel_In); // pobranie próbek z lewego i prawego kanału układu AD 1881 r 1 = DM(_Right_Channel_In); f 0 = float r 0 by r 2 ; f 1 = float r 1 by r 2 ; // konwersja próbek z formatu stałoprzecinkowego na zmiennoprzecinkowy do_filtering: dm(i 0, m 1)=f 0 (LW); r 12=r 12 xor r 12; f 8=pass f 12, f 0=dm(i 0, m 1), f 4=pm(i 8, m 8); // zerowanie rejestrów r 12 (niejawnie f 12) // czyszczenie f 8, pobieranie danych i współczynników lcntr=FILTER_TAPS-1, do macloop until lce; // właściwa pętla dokonująca filtracji macloop: f 12=f 0*f 4, f 8=f 8+f 12, f 0=dm(i 0, m 1), f 4=pm(i 8, m 8); f 12=f 0*f 4, f 8=f 8+f 12; // dokonanie ostatniego mnożenia oraz akumulacji wyniku r 9 = s 8; r 1 = 31; r 8 = fix f 8 by r 1; r 9 = fix f 9 by r 1; DM(_Left_Channel_Out) = r 8; DM(_Right_Channel_Out) = r 9; rts; fir. end: // konwersja próbek z formatu zmiennoprzecinkowego na stałoprzecinkowy // przesłanie wyników filtracji do AD 1881 // powrót z procedury filtracji fir