PERKALIAN Operasi Aritmatika 1 PENGALIAN Operasi pengalian lebih

PERKALIAN Operasi Aritmatika 1

PENGALIAN Operasi pengalian lebih rumit dibandingkan operasi penjumlahan atau pengurangan, baik dalam hardware maupun software Ada beberapa jenis algoritma yang digunakan dalam bermacam-macam komputer 2

PENGALIAN – UNSIGNED INTEGER 1 0 1 1 x 1 1 0 1 Multiplicand (11) Mutiplier (13) 1 0 1 1 0 0 1 0 1 1 Partial Product 1 0 1 1 1 0 0 0 1 1 Product (143) 3

PENGALIAN – UNSIGNED INTEGER Pengalian meliputi pembentukan beberapa perkalian parsial untuk setiap digit dalam multiplier. Perkalian parsial ini kemudian dijumlahkan untuk mendapatkan hasil pengalian akhir Bila bit multiplier sama dengan 0, maka hasil pengaliannya 0. Bila bit multiplier 1, maka hasil pengaliannya sama dengan mutiplier Hasil pengalian akhir diperoleh dengan menjumlahkan perkalian parsial tersebut. Setiap hasil perkalian parsial yang berurutan digeser satu posisi ke kiri relatif terhadap hasil perkalian sebelumnya. Pengalian dua buah integer biner n-bit menghasilkan hasil perkalian sampai 2 n-bit 4

PENGALIAN – UNSIGNED INTEGER Control Logic membaca bit-bit multiplier satu persatu Bila Q 0 = 1, multiplicand ditambahkan ke register A; hasilnya disimpan ke register A; setelah itu seluruh bit di register C, A dan Q digeser ke kanan 1 bit. Bila Q 0 = 0, tidak terjadi penambahan; seluruh bit di register C, A dan Q digeser ke kanan 1 bit. Proses tersebut dilakukan secara berulang untuk setiap bit multiplier Hasil perkalian akhir tersimpan di register A dan Q. 5

PENGALIAN – UNSIGNED INTEGER 6

PENGALIAN – UNSIGNED INTEGER yg diambil selalu Q 0 M=1011 7

PENGALIAN KOMPLEMEN-2 Dengan algoritma pengalian di atas 1011 * 1101 = 1000 1111 Perkalian unsigned integer : 11 * 13 = 143 Perkalian komplemen-2 : -5 * -3 = -113 perkalian tidak berfungsi jika multiplicand dan/atau multiplier-nya negatif 8

PERKALIAN UNSIGN & KOMPLEMEN-2 Ada beberapa cara untuk menangani hal tersebut: konversi multiplier dan multicand jadi positif, dikalikan; cari komplemen-2 dari hasilnya jika tanda multiplier dan multiplicand berbeda Menggunakan algoritma lain yang tidak memerlukan transformasi, misalnya Algoritma Booth 9

ALGORITMA BOOTH memiliki kelebihan kecepatan proses perkaliannya, relatif terhadap pendekatan langsung terdapat register Q(multiplier), M(multiplicand), A(accumulator), dan register 1 -bit di kanan Q yg ditandai dengan Q-1 hasil perkalian tersimpan di A dan Q 10

ALGORITMA BOOTH A dan Q-1 diinisialisasi 0 control logic memeriksa bit-bit multiplier satu -persatu beserta bit di kanannya Jika kedua bit sama (1 -1 atau 0 -0), maka seluruh bit di A, Q dan Q-1 digeser 1 -bit ke kanan jika kedua bit berbeda, multiplicand ditambahkan (0 -1) atau dikurangkan (1 -0) ke register A, kemudian digeser ke kanan pergeseran menggunakan Arithmetic Shift contoh : 1011 0101 1101 1010 11

ALGORITMA BOOTH 12

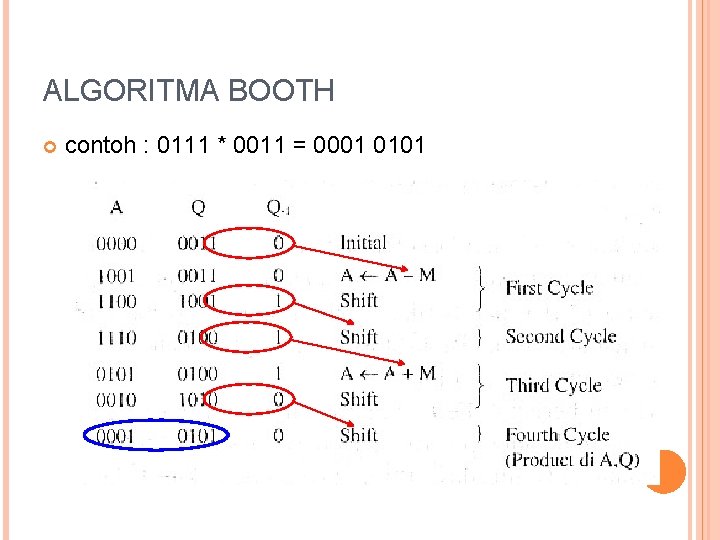

ALGORITMA BOOTH contoh : 0111 * 0011 = 0001 0101 13

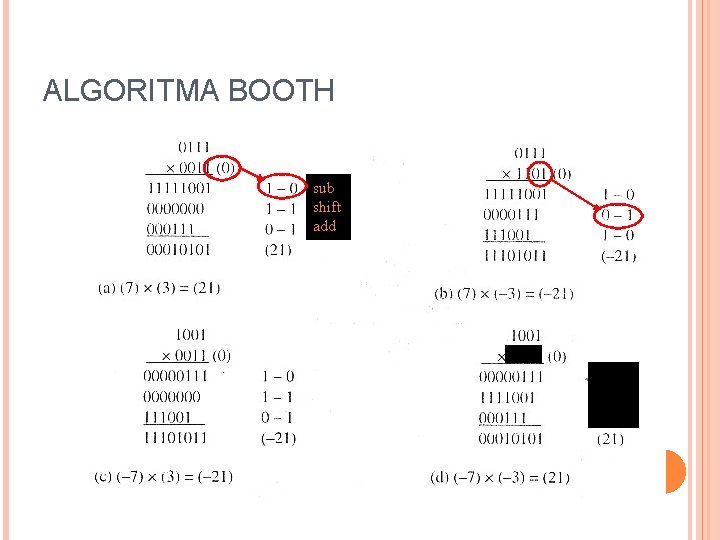

ALGORITMA BOOTH sub shift add 1101 1– 0 0– 1 1 -0 14

PEMBAGIAN Operasi Aritmatika 15

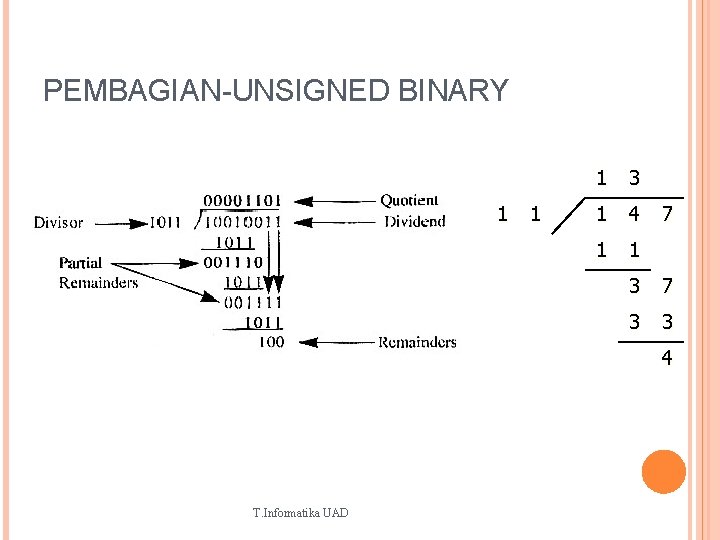

PEMBAGIAN-UNSIGNED BINARY 1 1 1 3 1 4 1 1 7 3 3 4 T. Informatika UAD 16

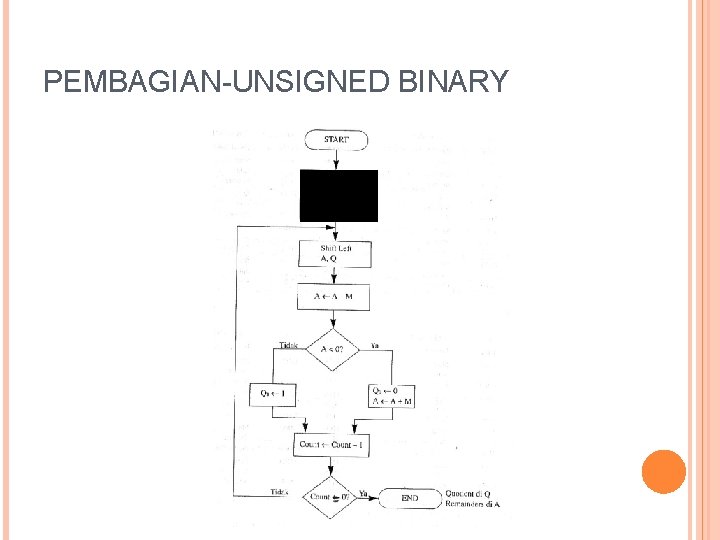

PEMBAGIAN-UNSIGNED BINARY E 0 M divisor A, Q dividend Count n 17

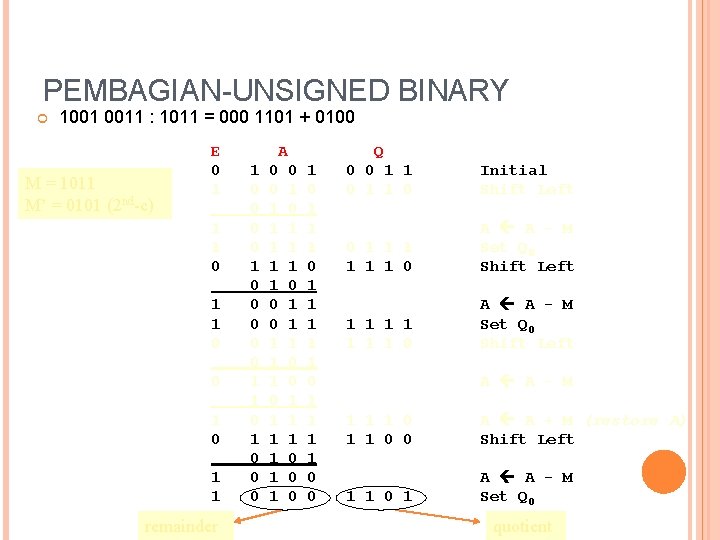

PEMBAGIAN-UNSIGNED BINARY 1001 0011 : 1011 = 000 1101 + 0100 M = 1011 M’ = 0101 (2 nd-c) E 0 1 1 1 0 0 1 1 remainder 1 0 0 0 0 0 1 1 0 0 0 A 0 0 0 1 1 1 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 Q 0 0 1 1 0 Initial Shift Left 0 1 1 1 0 A A - M Set Q 0 Shift Left 1 1 1 1 0 A A - M Set Q 0 Shift Left A A - M 1 1 1 0 0 A A + M (restore A) Shift Left 1 1 0 1 A A - M Set Q 0 quotient 18

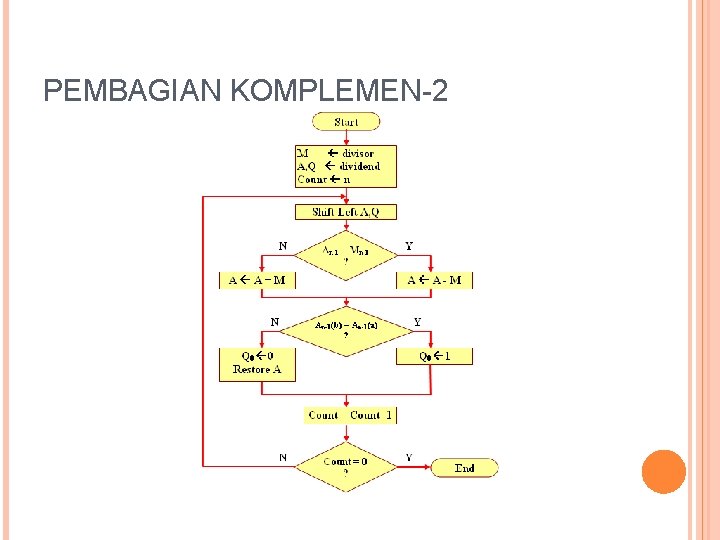

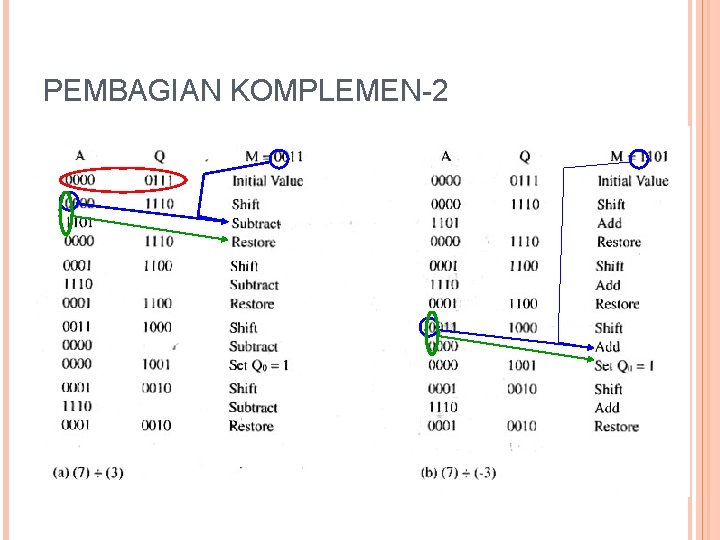

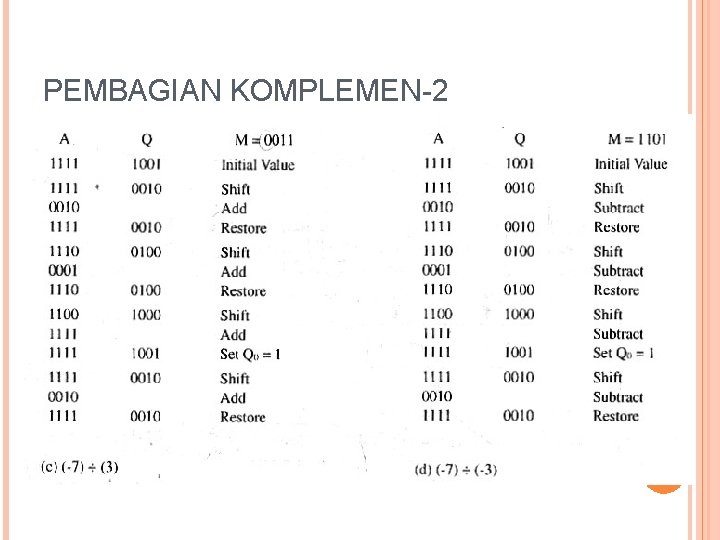

PEMBAGIAN KOMPLEMEN-2 Muatkan divisor ke M, dividend ke A dan Q. dividend diekspresikan sbg komplemen-2 2 n-bit. Geser A dan Q 1 -bit ke kiri Bila M dan A memiliki tanda yg sama, lakukan A A – M; bila tandanya beda, A A + M Operasi tsb akan berhasil bila tanda A sesudah dan sebelum operasi sama bila berhasil (A dan Q = 0), set Q 0 1 bila gagal (A dan Q <> 0), reset Q 0 0 dan simpan A sebelumnya Ulangi langkah 2 sampai 4 utk setiap posisi bit di Q Bila tanda divisor dan dividend sama maka quotient ada di Q, jika tidak quotient adalah komplemen-2 dari Q. Remainder ada di A. 19

PEMBAGIAN KOMPLEMEN-2 20

PEMBAGIAN KOMPLEMEN-2 21

PEMBAGIAN KOMPLEMEN-2 22

PEMBAGIAN KOMPLEMEN-2 (-7)/(3) dan (7)/(-3) akan menghasilkan remainder yang berbeda. Hal ini disebabkan operasi pembagian didefinisikan sebagai D=Q*V+R dengan D = dividend Q = quotient V = divisor R = remainder 23

Daftar Pustaka: 1. William Stallings, Computer and Architecture 2. E. Haodudin Nurkifli, Universitas Ahmad Dahlan

- Slides: 24