Performance analysis outline 1 2 3 4 5

![SPARK – minsort brief introduction • Input function int a[8]; // array must be SPARK – minsort brief introduction • Input function int a[8]; // array must be](https://slidetodoc.com/presentation_image_h2/5c1e9c7bb788a8b4e2f57aba11272183/image-32.jpg)

- Slides: 35

Performance analysis

outline 1. 2. 3. 4. 5. 6. IP introduction Compare between different kinds of interface Compare between direction and non-direction Compare between different memory hierarchy Using FIFO full-cycles to improve the system SPARK survey

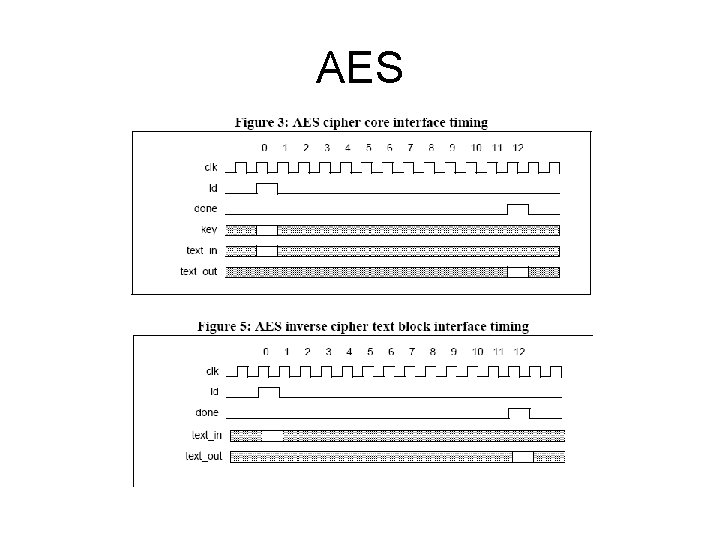

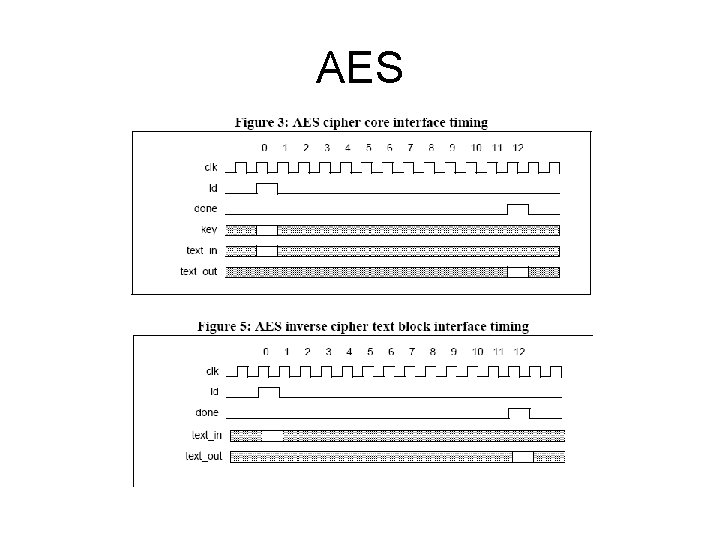

AES

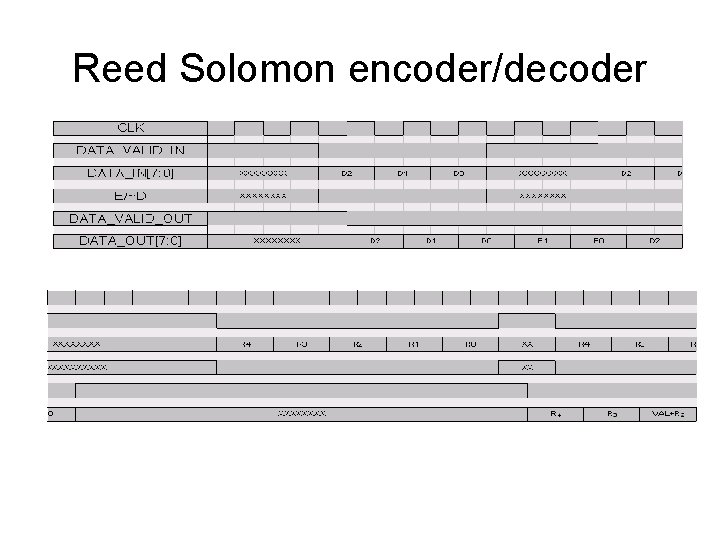

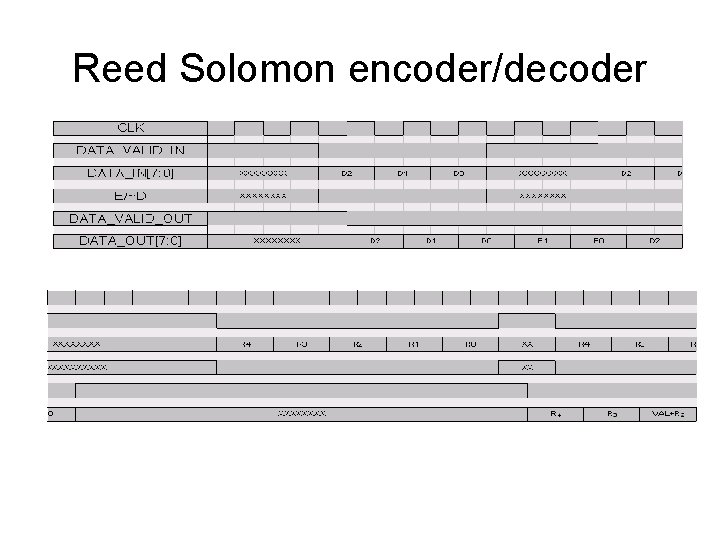

Reed Solomon encoder/decoder

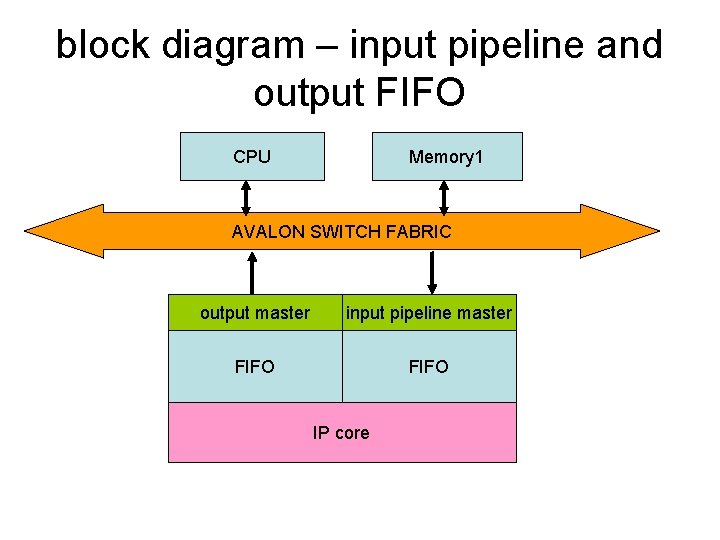

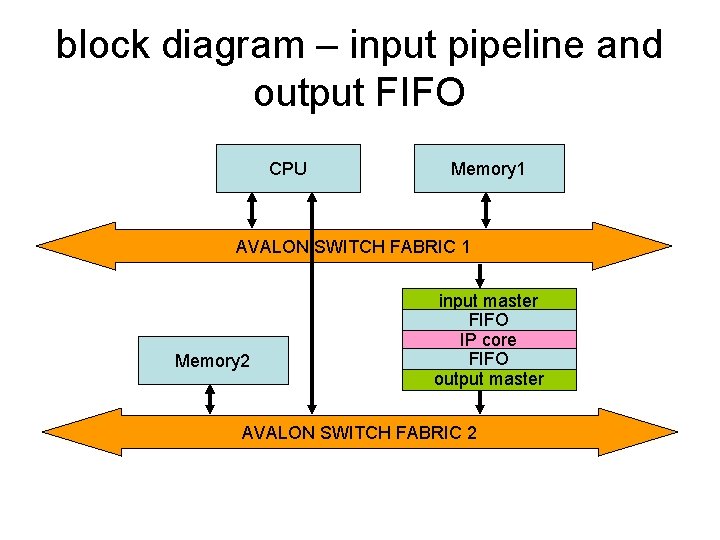

The compare between input master

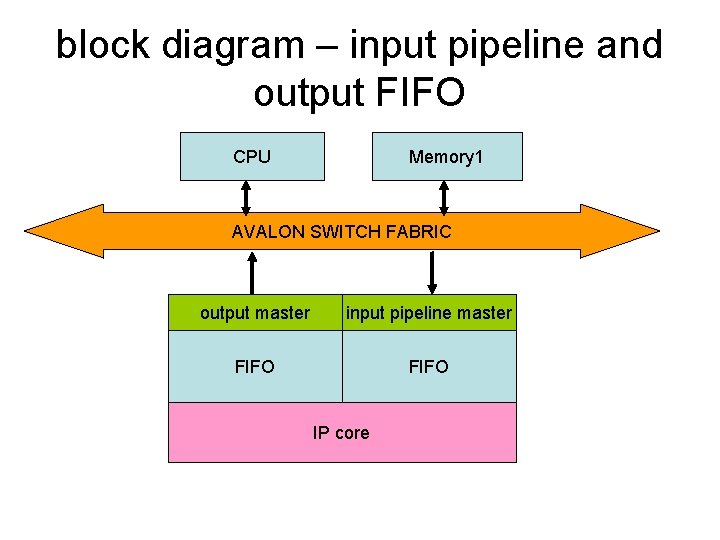

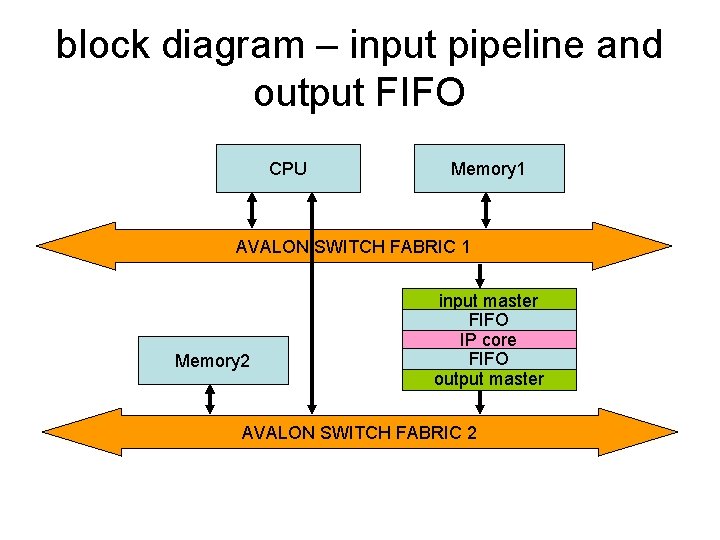

block diagram – input pipeline and output FIFO CPU Memory 1 AVALON SWITCH FABRIC output master input pipeline master FIFO IP core

block diagram – input pipeline and output FIFO CPU Memory 1 AVALON SWITCH FABRIC 1 Memory 2 input master FIFO IP core FIFO output master AVALON SWITCH FABRIC 2

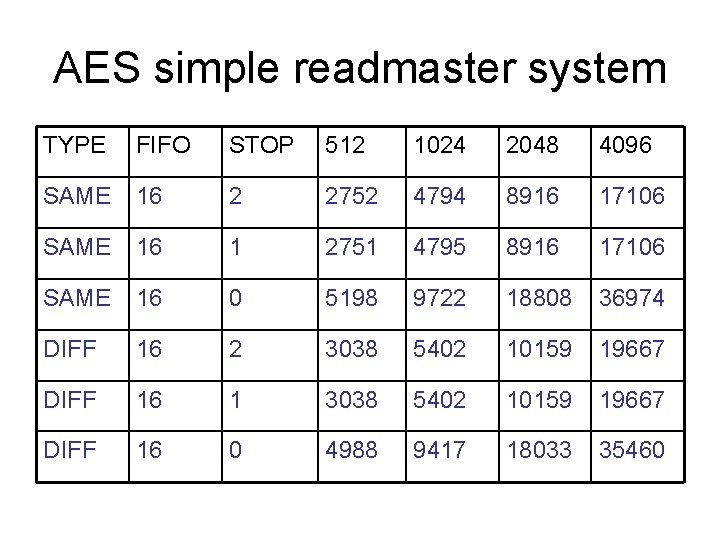

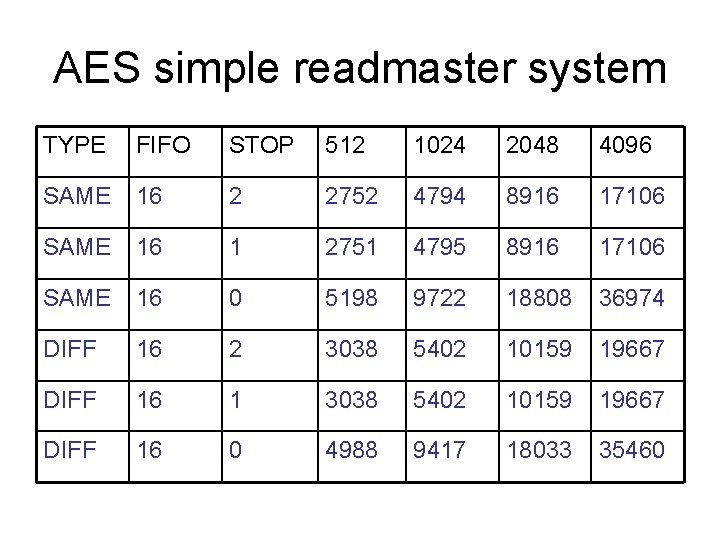

AES simple readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 2752 4794 8916 17106 SAME 16 1 2751 4795 8916 17106 SAME 16 0 5198 9722 18808 36974 DIFF 16 2 3038 5402 10159 19667 DIFF 16 1 3038 5402 10159 19667 DIFF 16 0 4988 9417 18033 35460

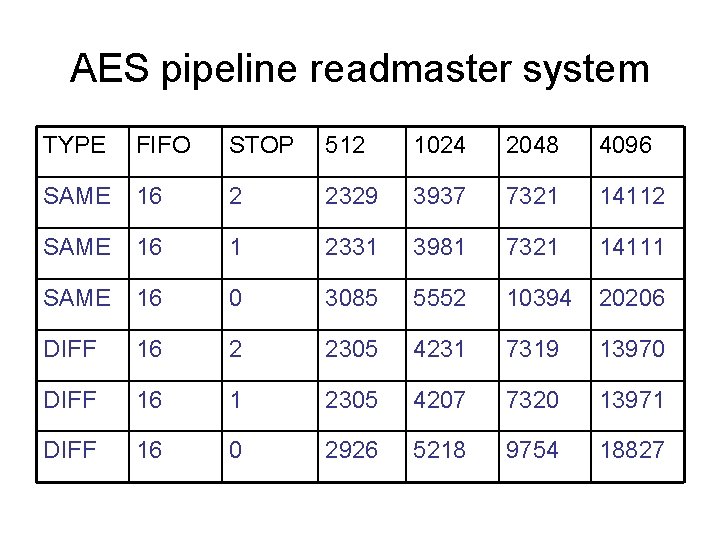

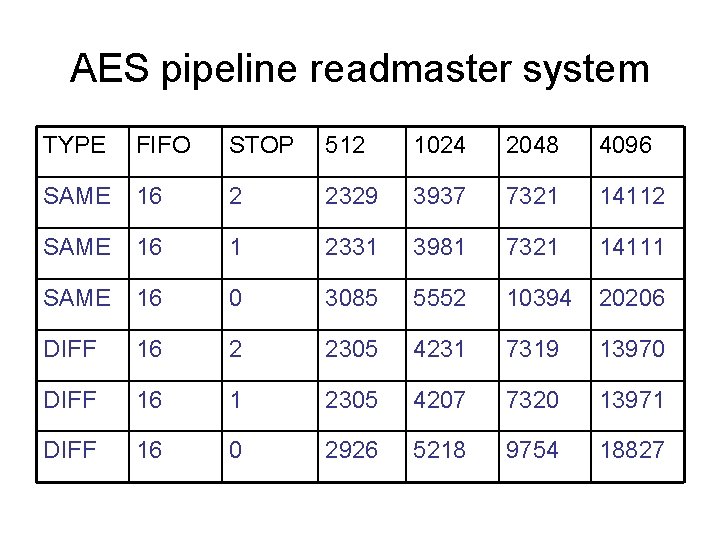

AES pipeline readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 2329 3937 7321 14112 SAME 16 1 2331 3981 7321 14111 SAME 16 0 3085 5552 10394 20206 DIFF 16 2 2305 4231 7319 13970 DIFF 16 1 2305 4207 7320 13971 DIFF 16 0 2926 5218 9754 18827

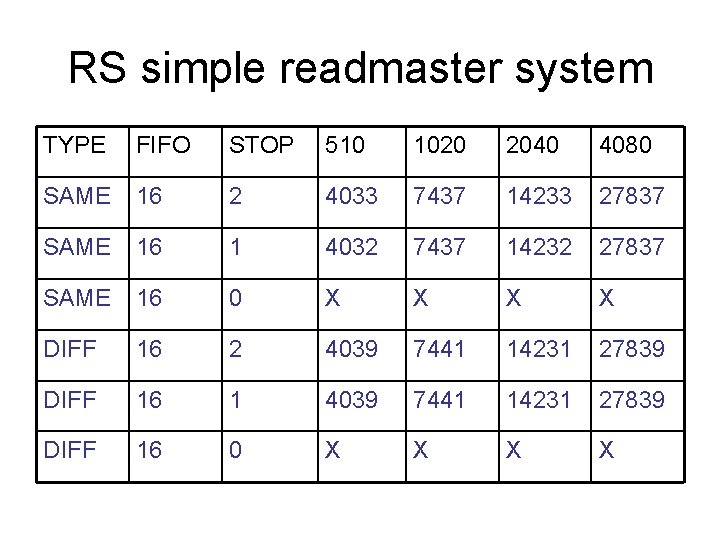

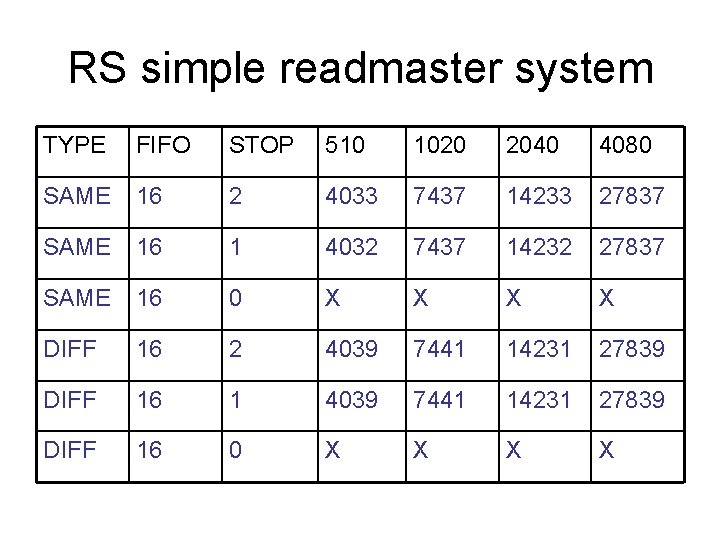

RS simple readmaster system TYPE FIFO STOP 510 1020 2040 4080 SAME 16 2 4033 7437 14233 27837 SAME 16 1 4032 7437 14232 27837 SAME 16 0 X X DIFF 16 2 4039 7441 14231 27839 DIFF 16 1 4039 7441 14231 27839 DIFF 16 0 X X

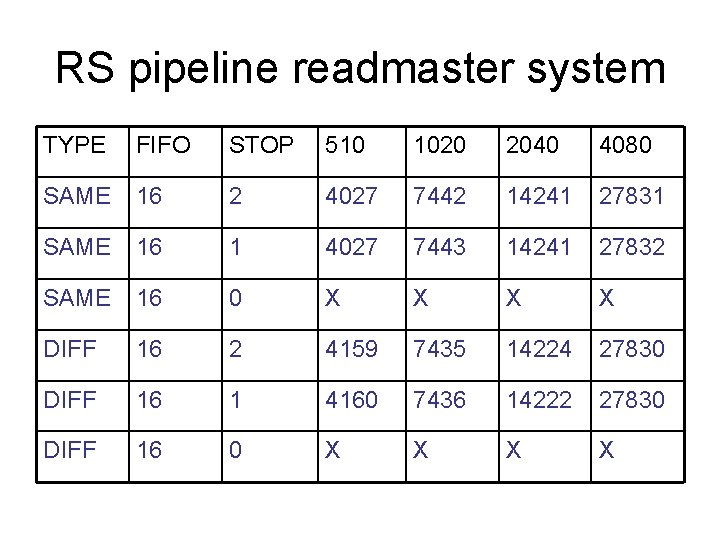

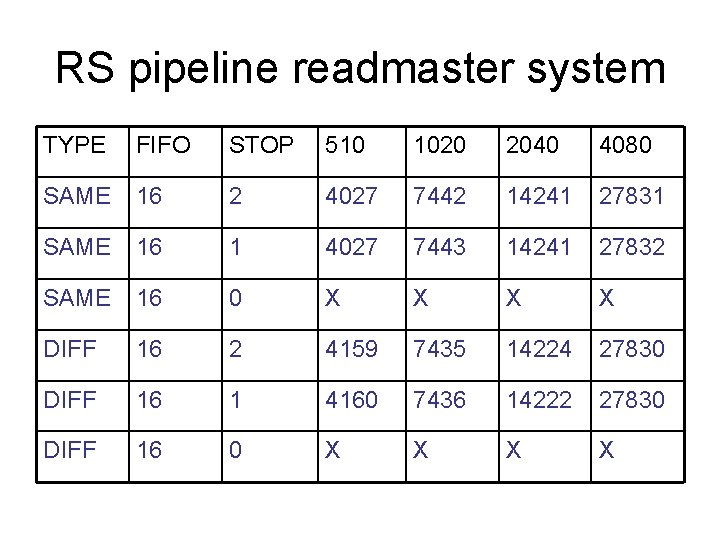

RS pipeline readmaster system TYPE FIFO STOP 510 1020 2040 4080 SAME 16 2 4027 7442 14241 27831 SAME 16 1 4027 7443 14241 27832 SAME 16 0 X X DIFF 16 2 4159 7435 14224 27830 DIFF 16 1 4160 7436 14222 27830 DIFF 16 0 X X

The compare between direct connection and non-direct connection

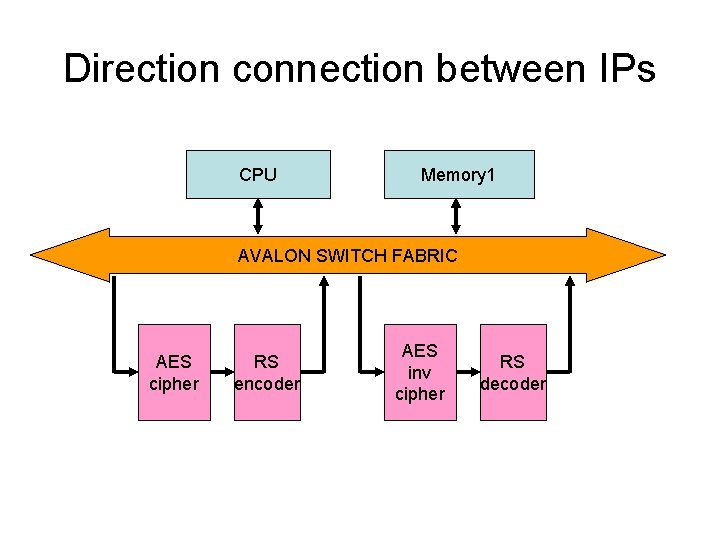

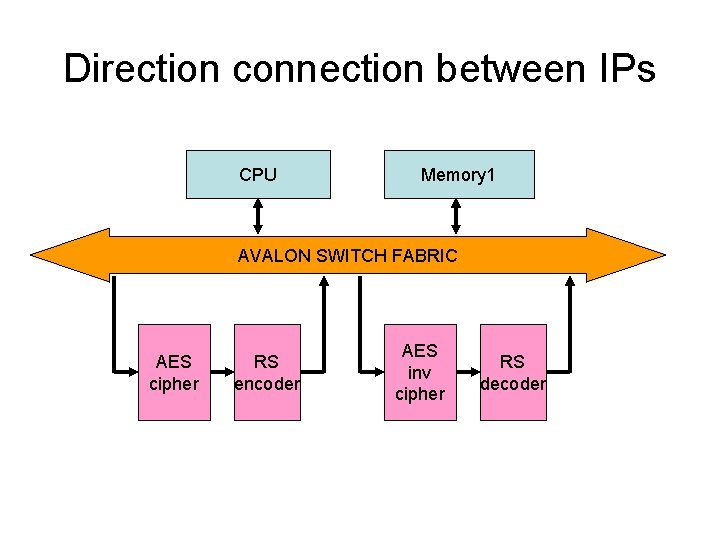

Direction connection between IPs CPU Memory 1 AVALON SWITCH FABRIC AES cipher RS encoder AES inv cipher RS decoder

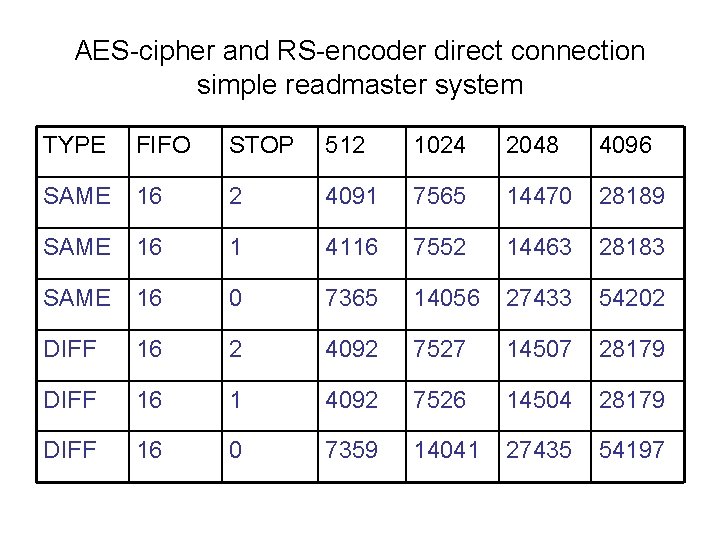

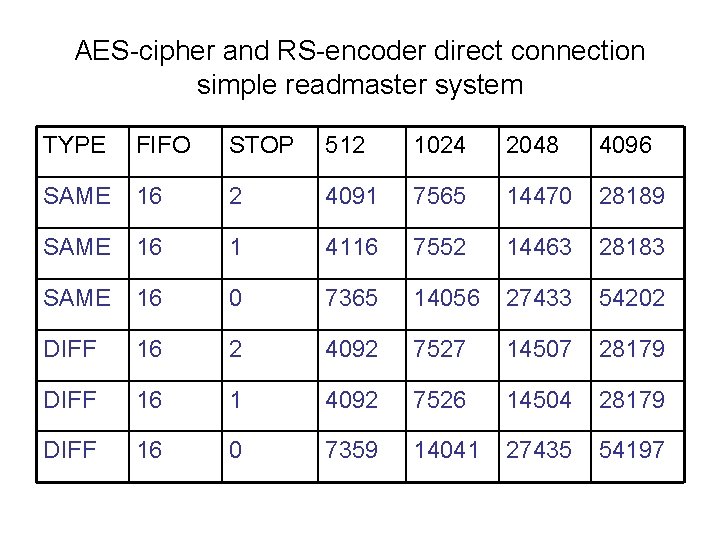

AES-cipher and RS-encoder direct connection simple readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 4091 7565 14470 28189 SAME 16 1 4116 7552 14463 28183 SAME 16 0 7365 14056 27433 54202 DIFF 16 2 4092 7527 14507 28179 DIFF 16 1 4092 7526 14504 28179 DIFF 16 0 7359 14041 27435 54197

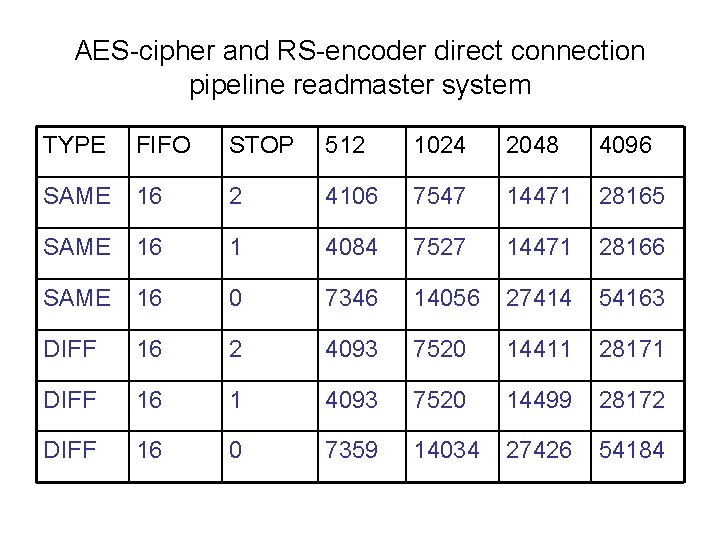

AES-cipher and RS-encoder direct connection pipeline readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 4106 7547 14471 28165 SAME 16 1 4084 7527 14471 28166 SAME 16 0 7346 14056 27414 54163 DIFF 16 2 4093 7520 14411 28171 DIFF 16 1 4093 7520 14499 28172 DIFF 16 0 7359 14034 27426 54184

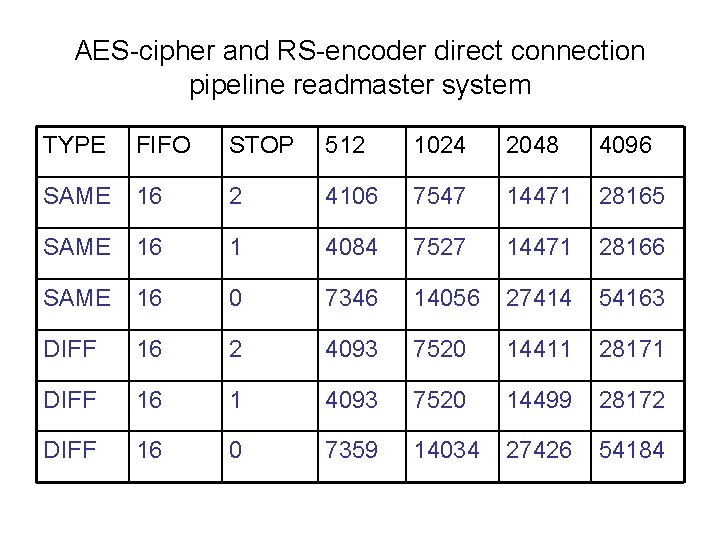

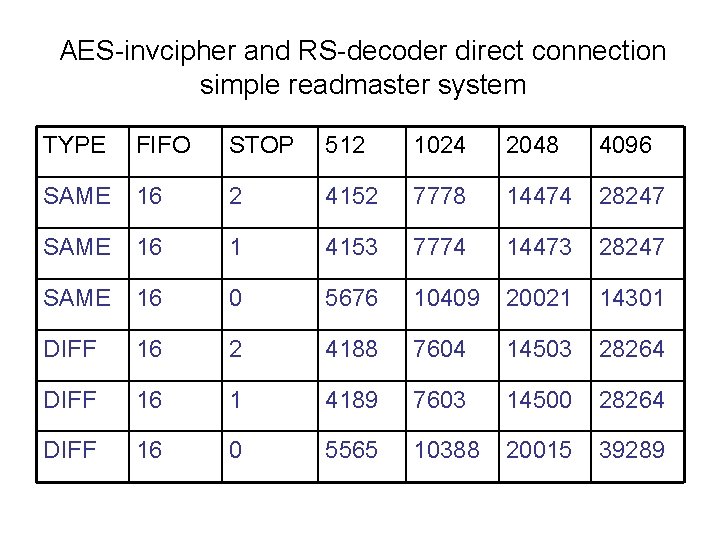

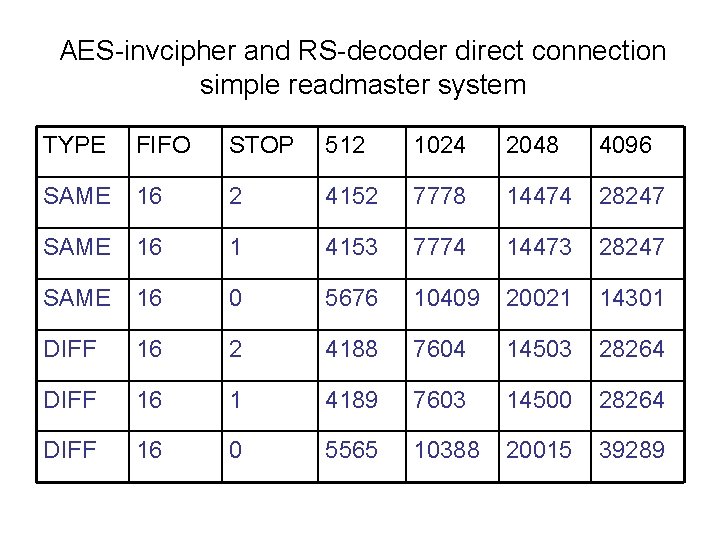

AES-invcipher and RS-decoder direct connection simple readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 4152 7778 14474 28247 SAME 16 1 4153 7774 14473 28247 SAME 16 0 5676 10409 20021 14301 DIFF 16 2 4188 7604 14503 28264 DIFF 16 1 4189 7603 14500 28264 DIFF 16 0 5565 10388 20015 39289

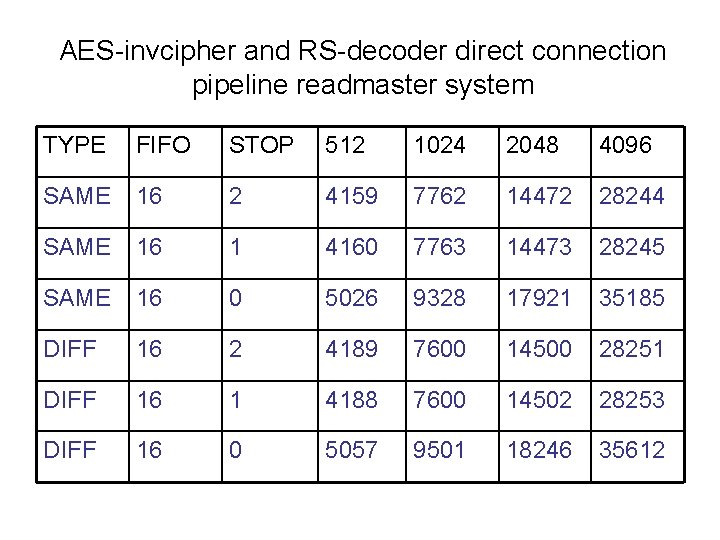

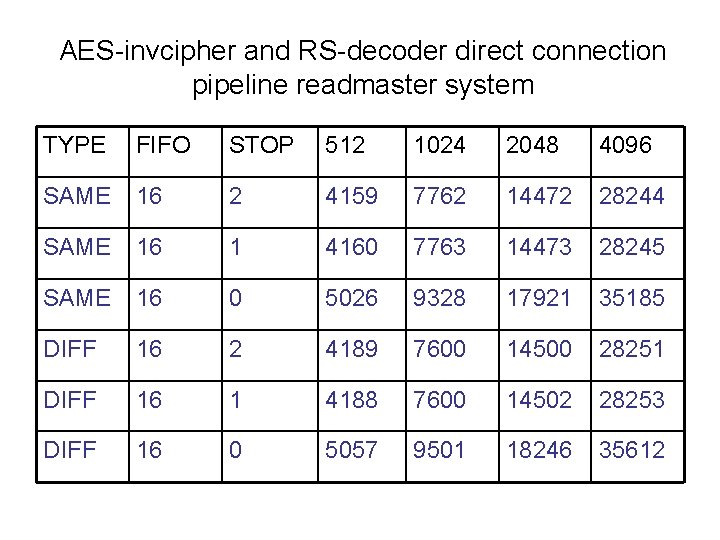

AES-invcipher and RS-decoder direct connection pipeline readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 4159 7762 14472 28244 SAME 16 1 4160 7763 14473 28245 SAME 16 0 5026 9328 17921 35185 DIFF 16 2 4189 7600 14500 28251 DIFF 16 1 4188 7600 14502 28253 DIFF 16 0 5057 9501 18246 35612

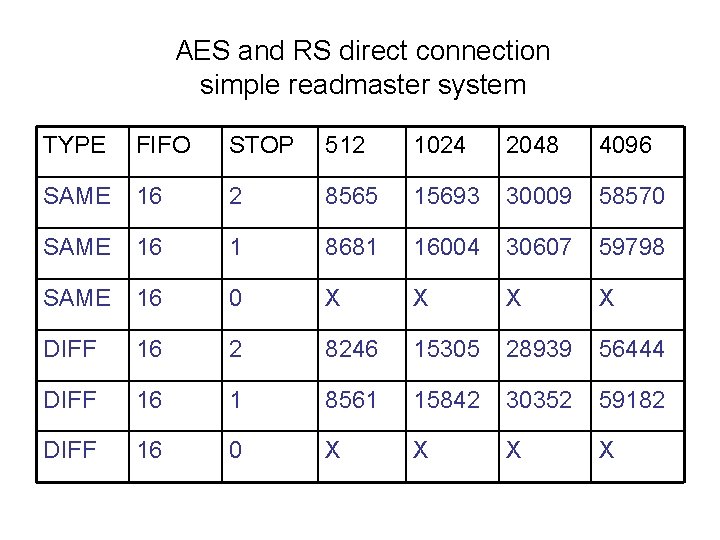

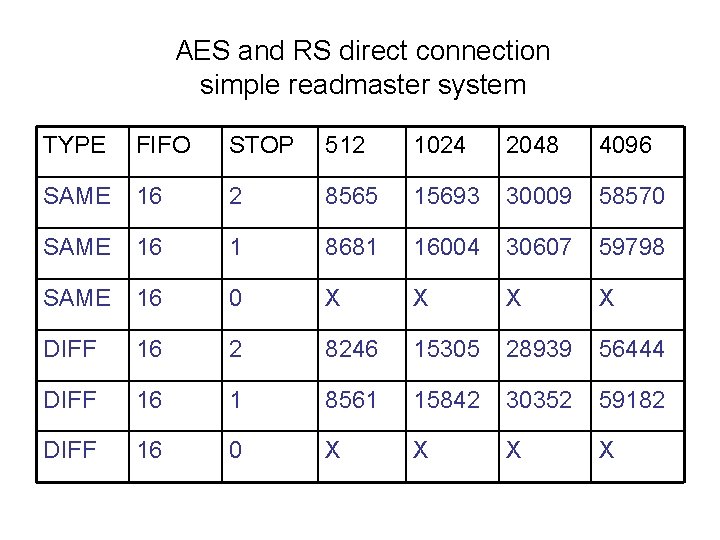

AES and RS direct connection simple readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 8565 15693 30009 58570 SAME 16 1 8681 16004 30607 59798 SAME 16 0 X X DIFF 16 2 8246 15305 28939 56444 DIFF 16 1 8561 15842 30352 59182 DIFF 16 0 X X

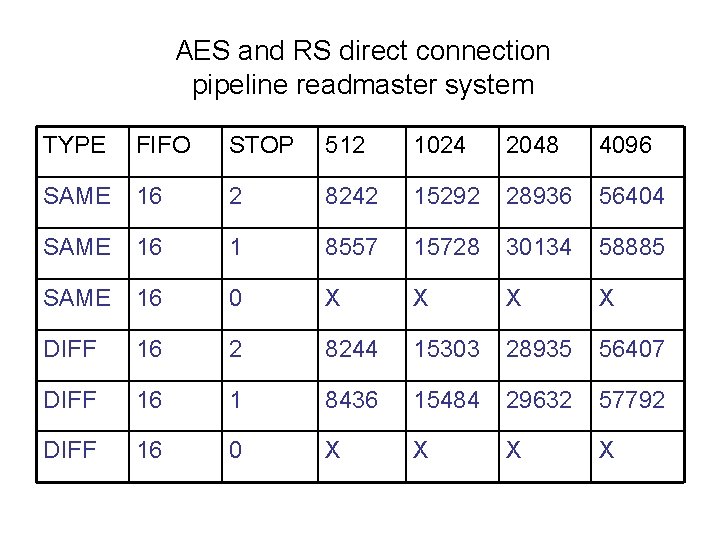

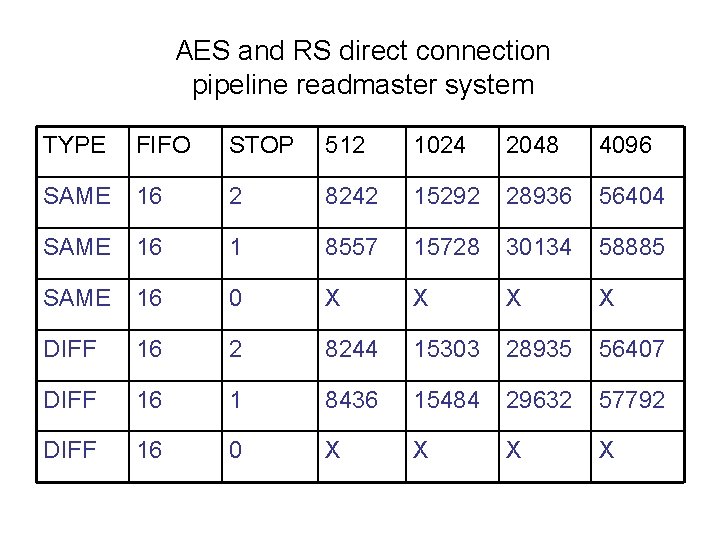

AES and RS direct connection pipeline readmaster system TYPE FIFO STOP 512 1024 2048 4096 SAME 16 2 8242 15292 28936 56404 SAME 16 1 8557 15728 30134 58885 SAME 16 0 X X DIFF 16 2 8244 15303 28935 56407 DIFF 16 1 8436 15484 29632 57792 DIFF 16 0 X X

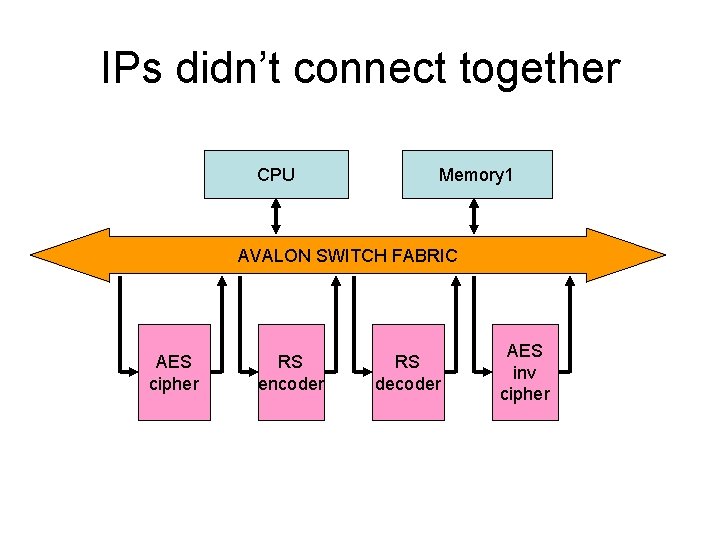

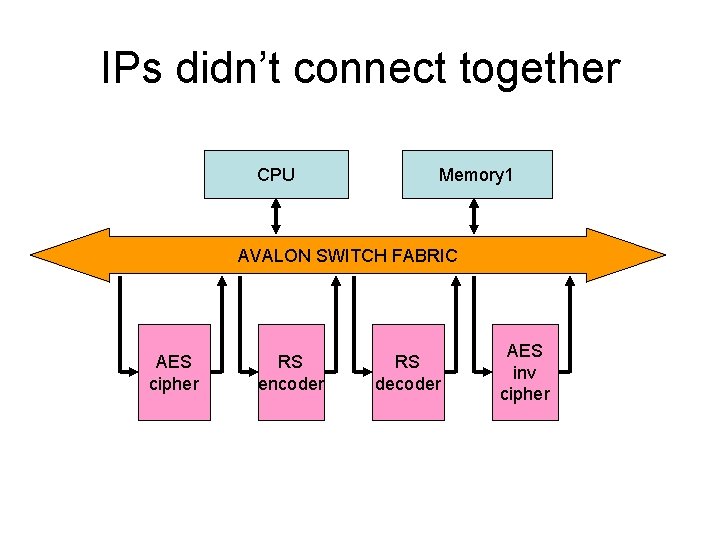

IPs didn’t connect together CPU Memory 1 AVALON SWITCH FABRIC AES cipher RS encoder RS decoder AES inv cipher

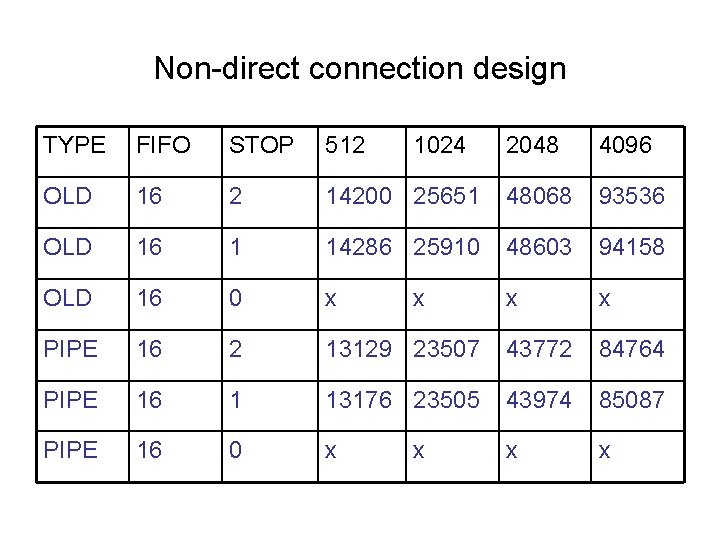

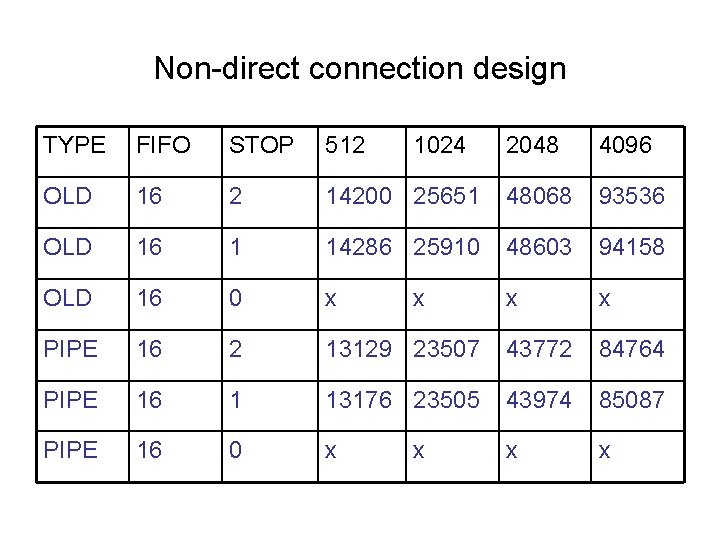

Non-direct connection design TYPE FIFO STOP 512 OLD 16 OLD 1024 2048 4096 14200 25651 48068 93536 1 14286 25910 48603 94158 16 0 x x x PIPE 16 2 13129 23507 43772 84764 PIPE 16 1 13176 23505 43974 85087 PIPE 16 0 x x x

The compare between one memory or two memory

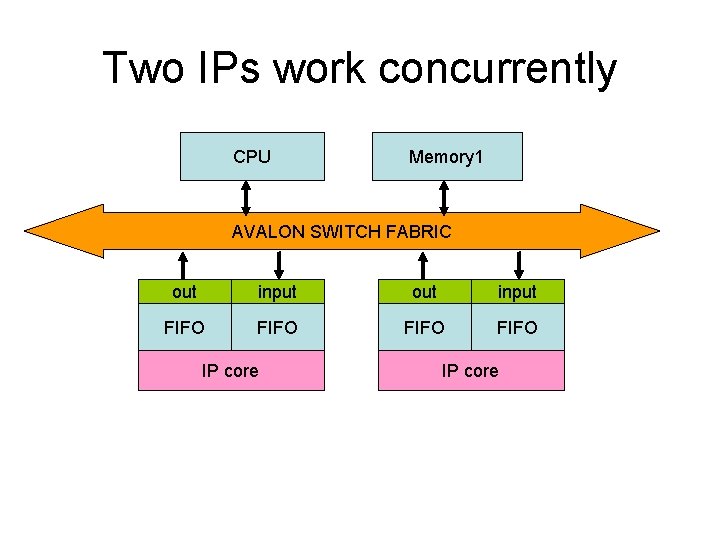

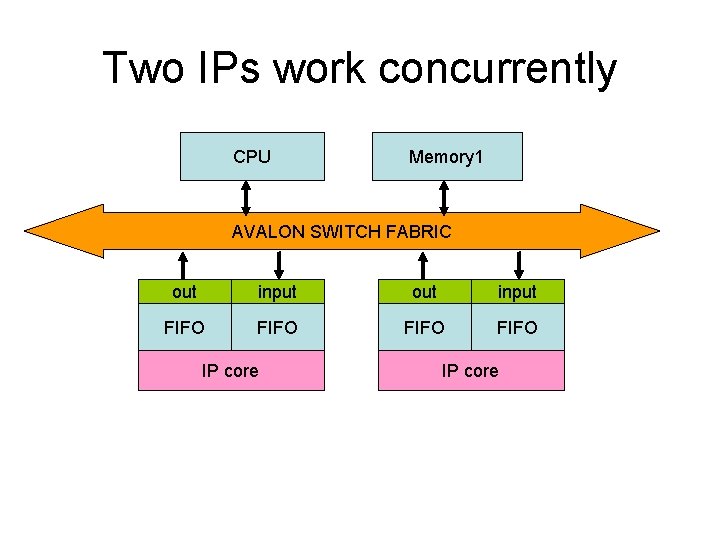

Two IPs work concurrently CPU Memory 1 AVALON SWITCH FABRIC out input FIFO IP core

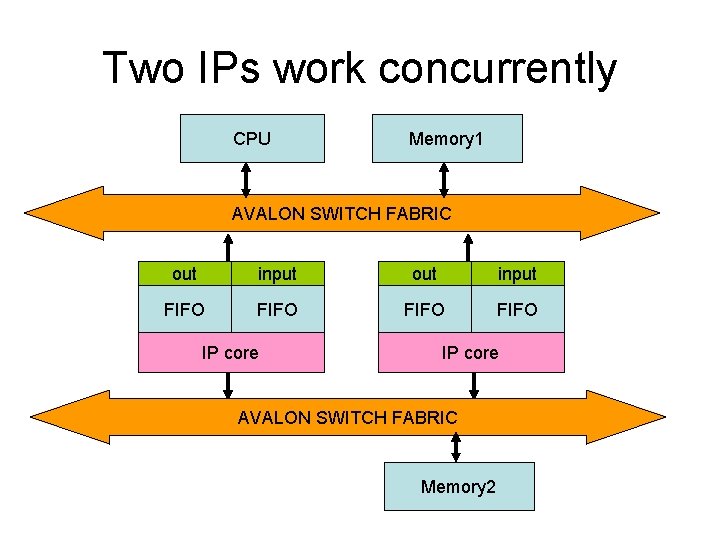

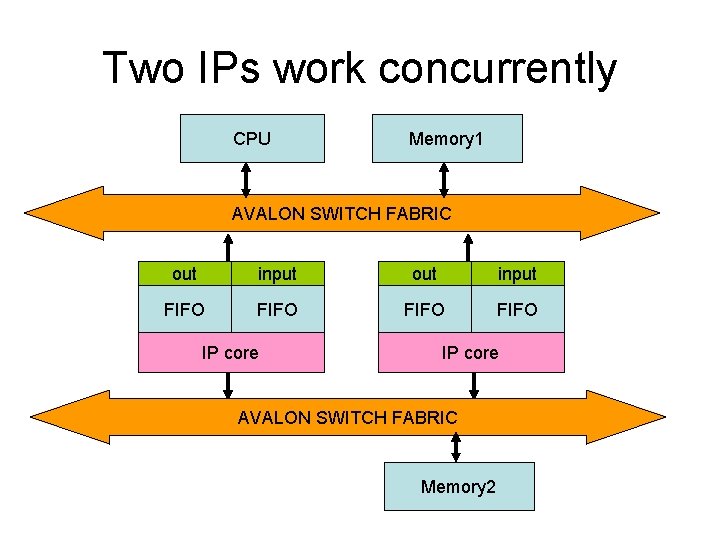

Two IPs work concurrently CPU Memory 1 AVALON SWITCH FABRIC out input FIFO IP core AVALON SWITCH FABRIC Memory 2

The FIFO full-cycles analysis

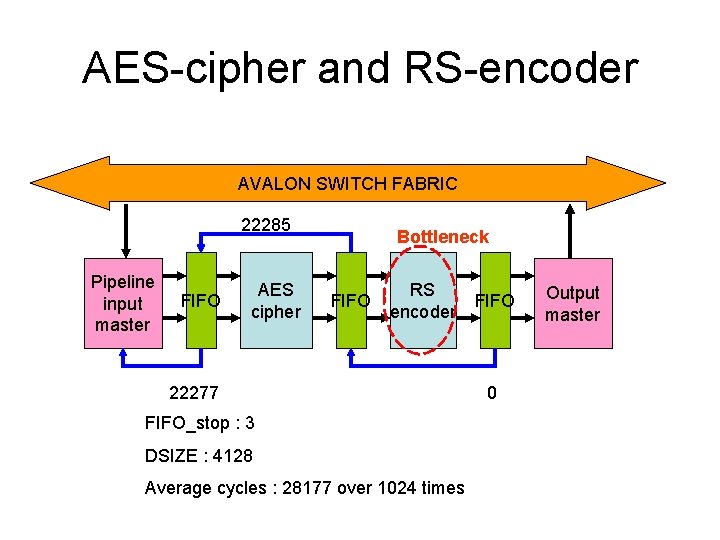

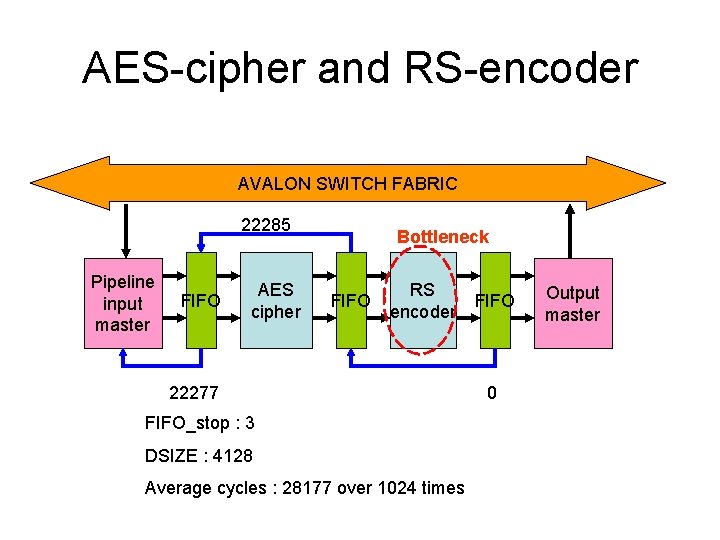

AES-cipher and RS-encoder AVALON SWITCH FABRIC 22285 Pipeline input master FIFO AES cipher Bottleneck FIFO RS encoder 22277 FIFO_stop : 3 DSIZE : 4128 Average cycles : 28177 over 1024 times FIFO 0 Output master

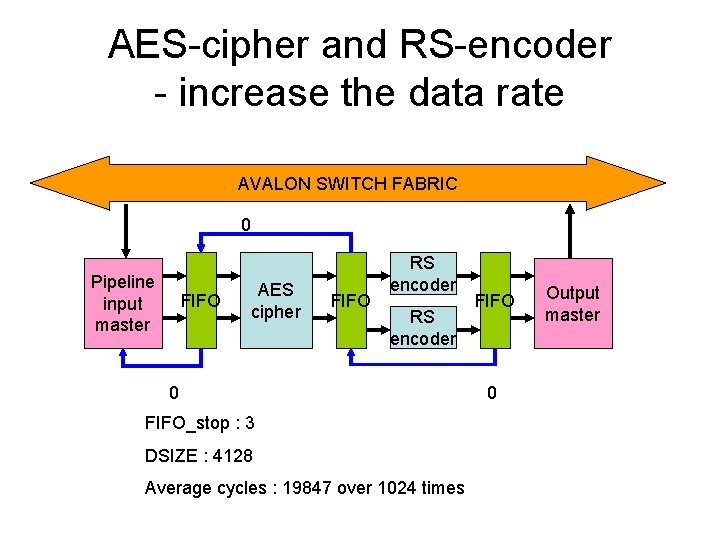

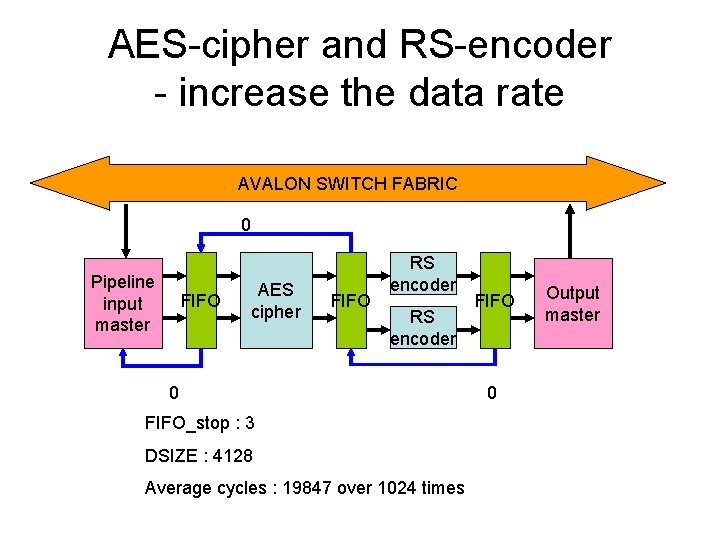

AES-cipher and RS-encoder - increase the data rate AVALON SWITCH FABRIC 0 Pipeline input master FIFO AES cipher FIFO RS encoder 0 FIFO_stop : 3 DSIZE : 4128 Average cycles : 19847 over 1024 times FIFO 0 Output master

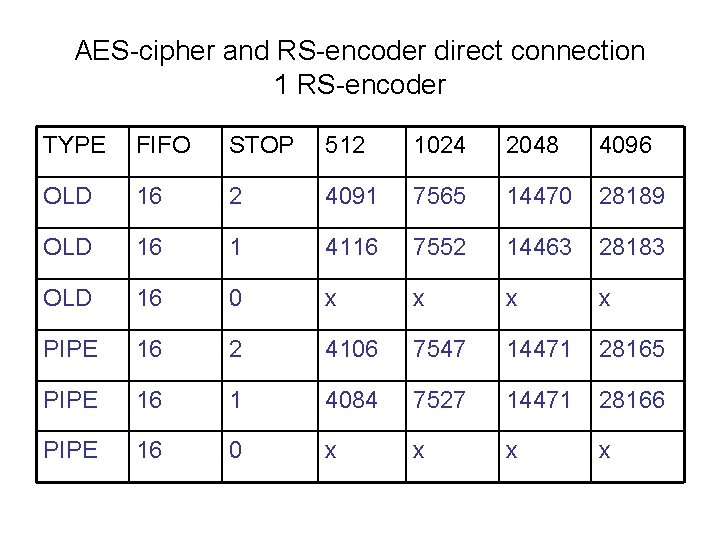

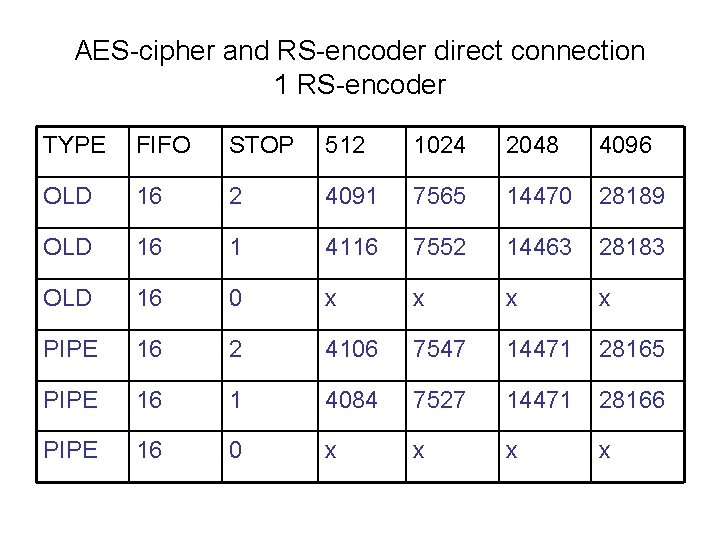

AES-cipher and RS-encoder direct connection 1 RS-encoder TYPE FIFO STOP 512 1024 2048 4096 OLD 16 2 4091 7565 14470 28189 OLD 16 1 4116 7552 14463 28183 OLD 16 0 x x PIPE 16 2 4106 7547 14471 28165 PIPE 16 1 4084 7527 14471 28166 PIPE 16 0 x x

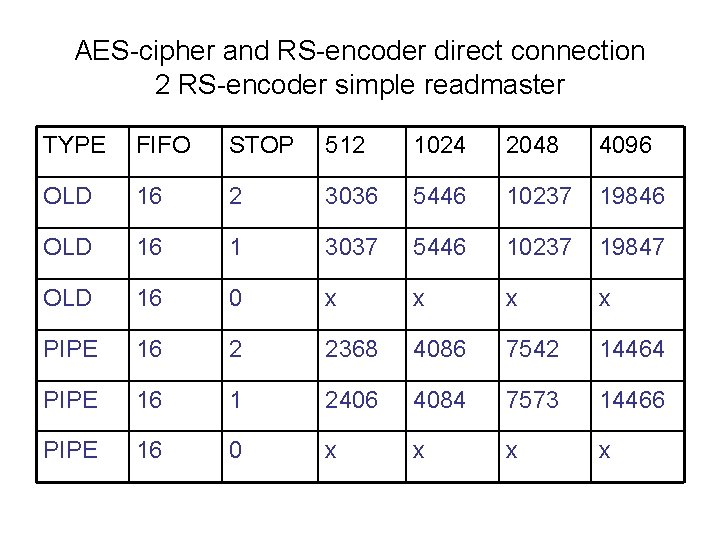

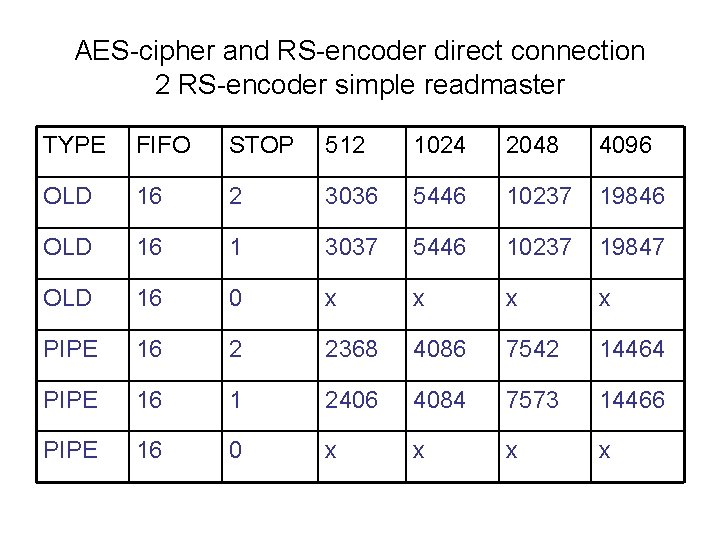

AES-cipher and RS-encoder direct connection 2 RS-encoder simple readmaster TYPE FIFO STOP 512 1024 2048 4096 OLD 16 2 3036 5446 10237 19846 OLD 16 1 3037 5446 10237 19847 OLD 16 0 x x PIPE 16 2 2368 4086 7542 14464 PIPE 16 1 2406 4084 7573 14466 PIPE 16 0 x x

SPARK survey

SPARK • I want to prove that the interface is suitable for HLS tool’s result. • SPARK has released their version v 1. 3. It contains more examples to illustrate how to use the tool. • There is an example min-sort illustrate the usage of array.

![SPARK minsort brief introduction Input function int a8 array must be SPARK – minsort brief introduction • Input function int a[8]; // array must be](https://slidetodoc.com/presentation_image_h2/5c1e9c7bb788a8b4e2f57aba11272183/image-32.jpg)

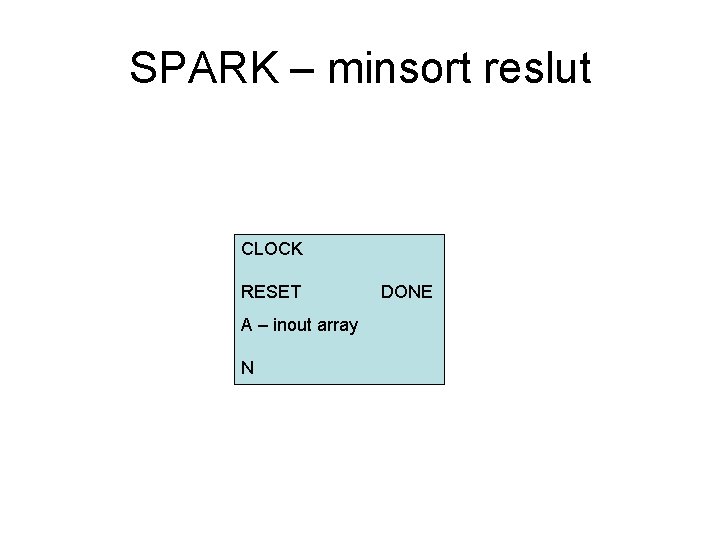

SPARK – minsort brief introduction • Input function int a[8]; // array must be declared as an array void sort(int n) {. . . } • Output module port CLOCK RESET N – an 32 bit data, in port A – an 8 -element array of 32 -bit data, inout port DONE

SPARK - signal • RESET is positive edge triggered. After reset the module, the IP start to work. • Once it finish the computation. It will raise the done signal. • The done signal is de-asserted by another reset.

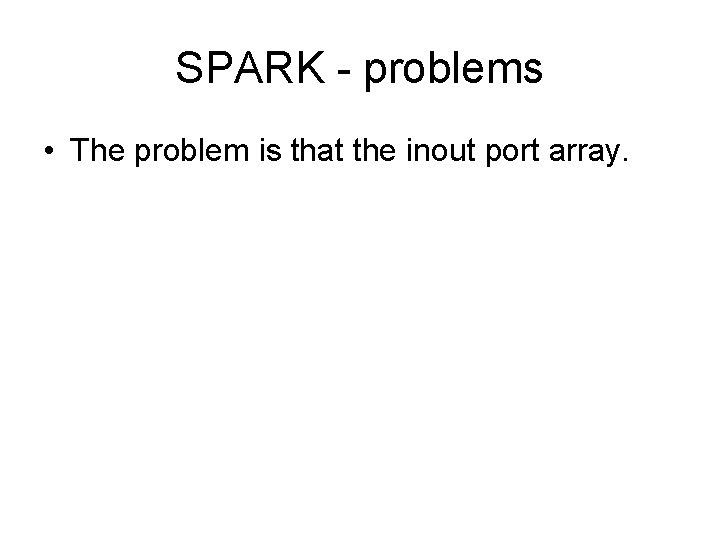

SPARK – minsort reslut CLOCK RESET A – inout array N DONE

SPARK - problems • The problem is that the inout port array.