Perancangan rangkaian logika ada uraian verbal tentang apa

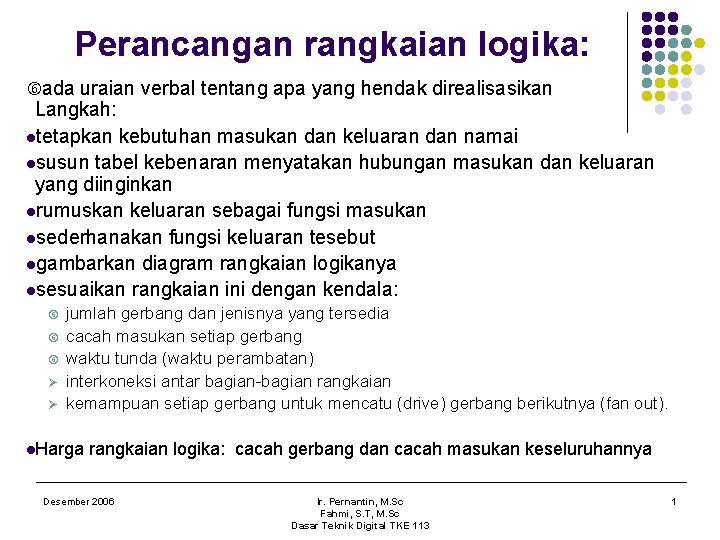

Perancangan rangkaian logika: ada uraian verbal tentang apa yang hendak direalisasikan Langkah: ltetapkan kebutuhan masukan dan keluaran dan namai lsusun tabel kebenaran menyatakan hubungan masukan dan keluaran yang diinginkan lrumuskan keluaran sebagai fungsi masukan lsederhanakan fungsi keluaran tesebut lgambarkan diagram rangkaian logikanya lsesuaikan rangkaian ini dengan kendala: Ø Ø jumlah gerbang dan jenisnya yang tersedia cacah masukan setiap gerbang waktu tunda (waktu perambatan) interkoneksi antar bagian-bagian rangkaian kemampuan setiap gerbang untuk mencatu (drive) gerbang berikutnya (fan out). l. Harga rangkaian logika: cacah gerbang dan cacah masukan keseluruhannya Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 1

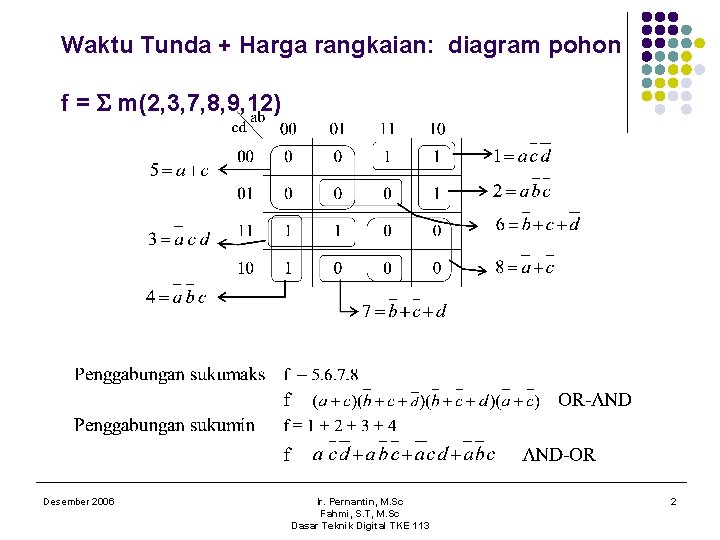

Waktu Tunda + Harga rangkaian: diagram pohon f = m(2, 3, 7, 8, 9, 12) Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 2

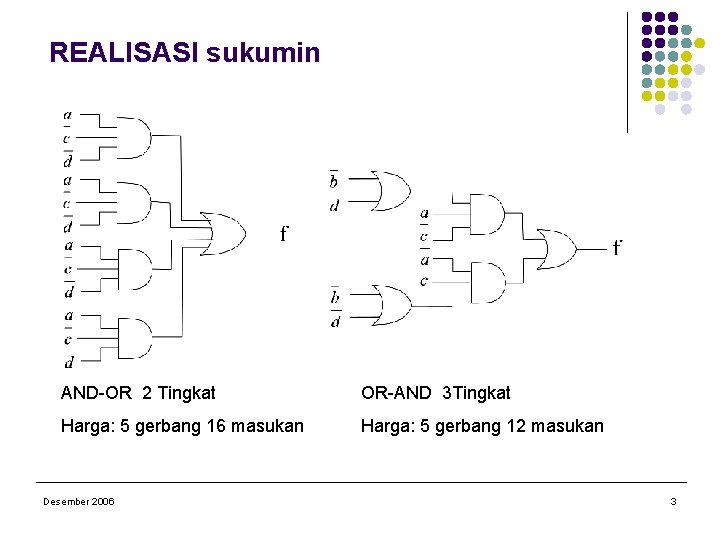

REALISASI sukumin AND-OR 2 Tingkat OR-AND 3 Tingkat Harga: 5 gerbang 16 masukan Harga: 5 gerbang 12 masukan Desember 2006 3

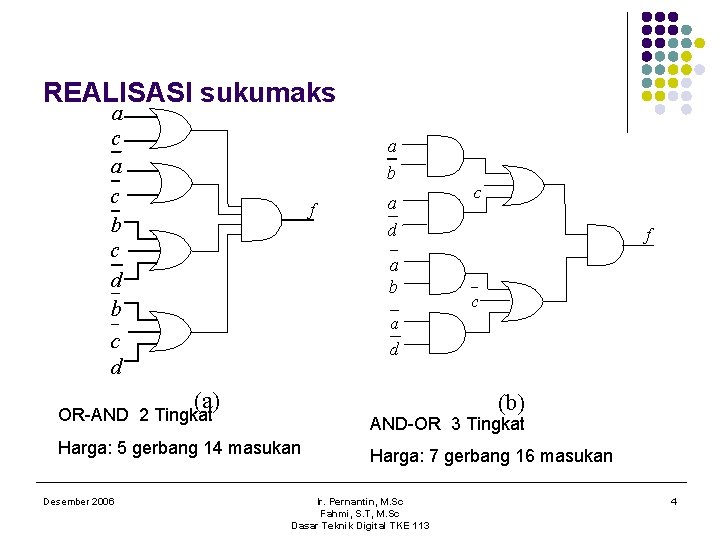

REALISASI sukumaks a c b c d a b f a d a b a d c f c (a) (b) 3 Tingkat OR-AND 2 Tingkat AND-OR Harga: 5 gerbang 14 masukan Harga: 7 gerbang 16 masukan Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 4

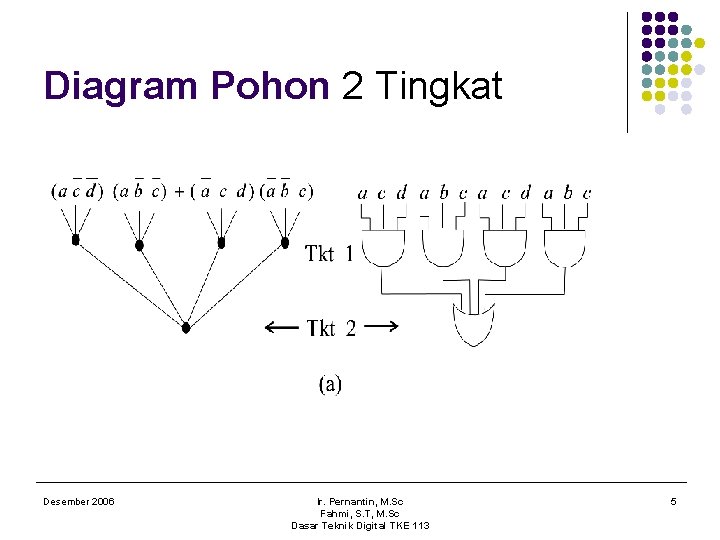

Diagram Pohon 2 Tingkat Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 5

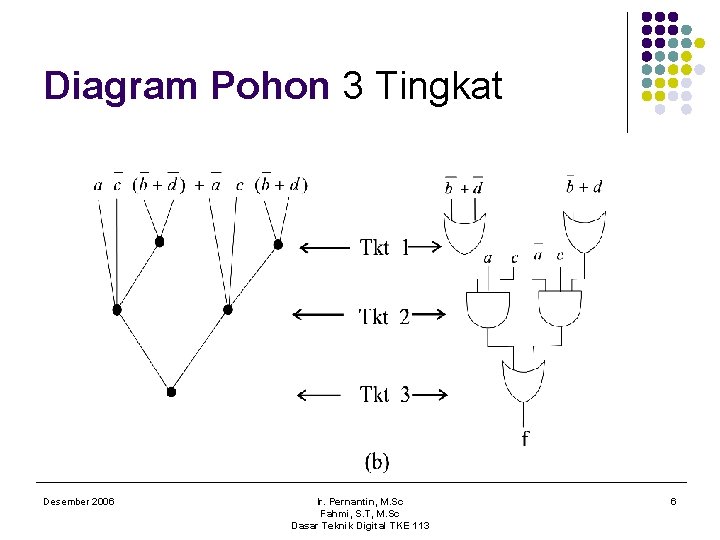

Diagram Pohon 3 Tingkat Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 6

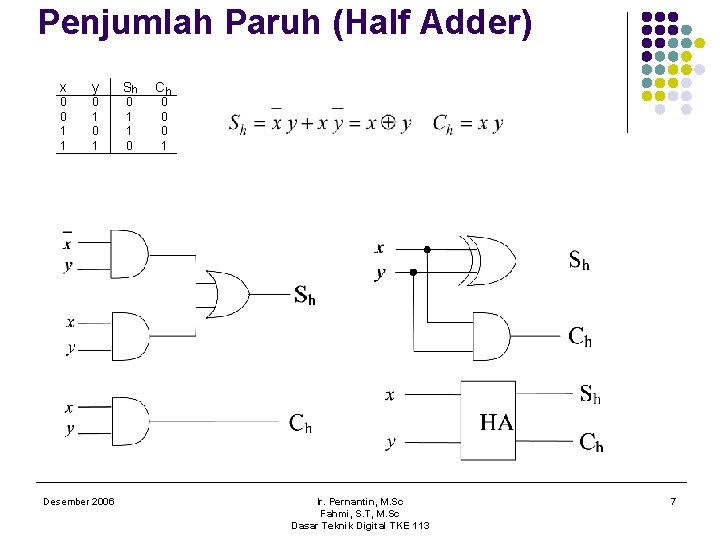

Penjumlah Paruh (Half Adder) x y Sh 0 0 1 1 0 1 0 1 1 0 Desember 2006 Ch 0 0 0 1 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 7

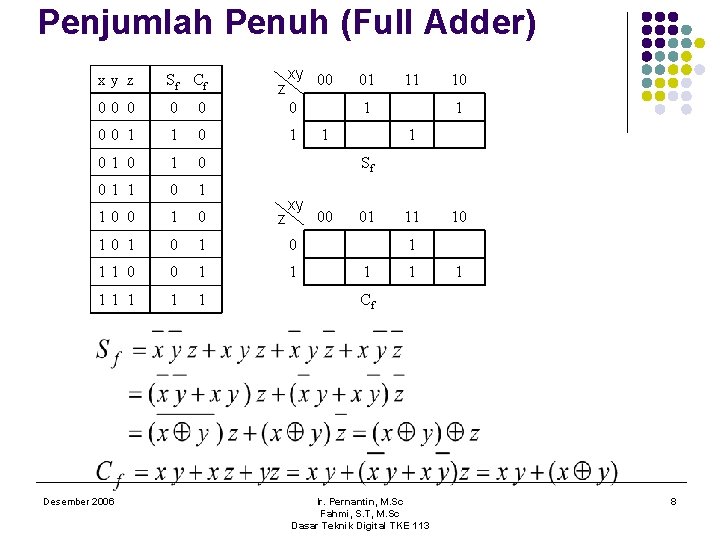

Penjumlah Penuh (Full Adder) xy 00 01 0 0 1 1 01 0 01 1 0 1 10 0 10 1 0 11 0 0 1 1 1 1 xy z Sf C f 00 0 0 00 1 Desember 2006 z 1 11 10 1 1 Sf z xy 00 01 11 10 1 1 Cf Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 8

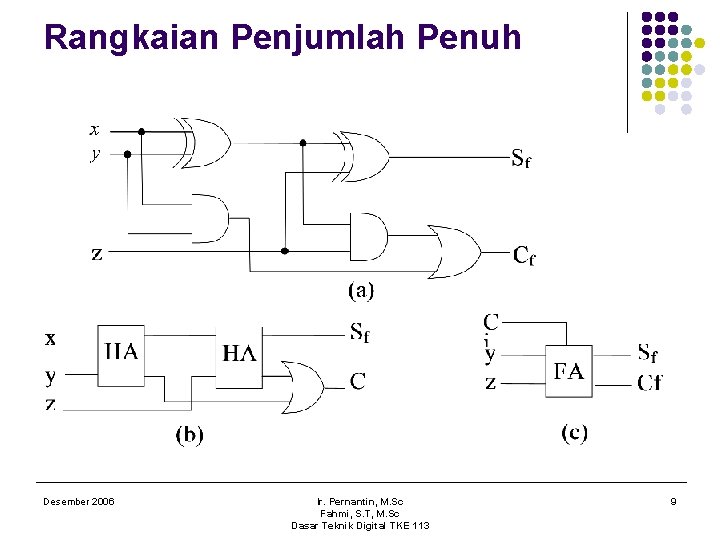

Rangkaian Penjumlah Penuh Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 9

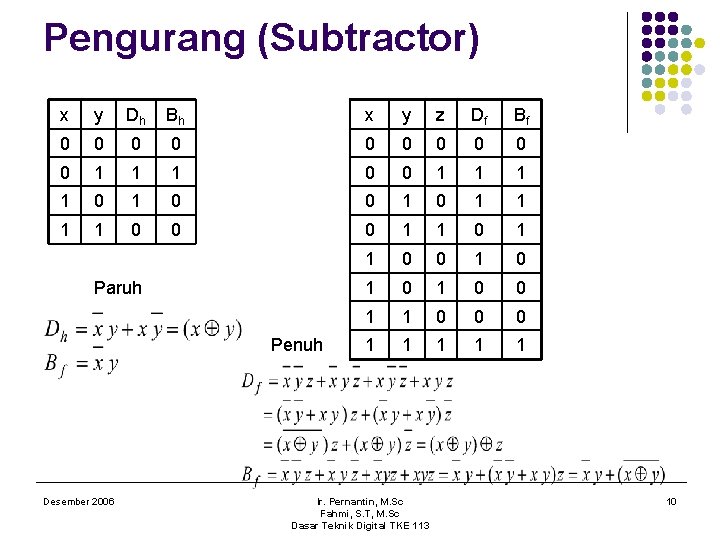

Pengurang (Subtractor) x y Dh Bh x y z Df Bf 0 0 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 Paruh Penuh Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 10

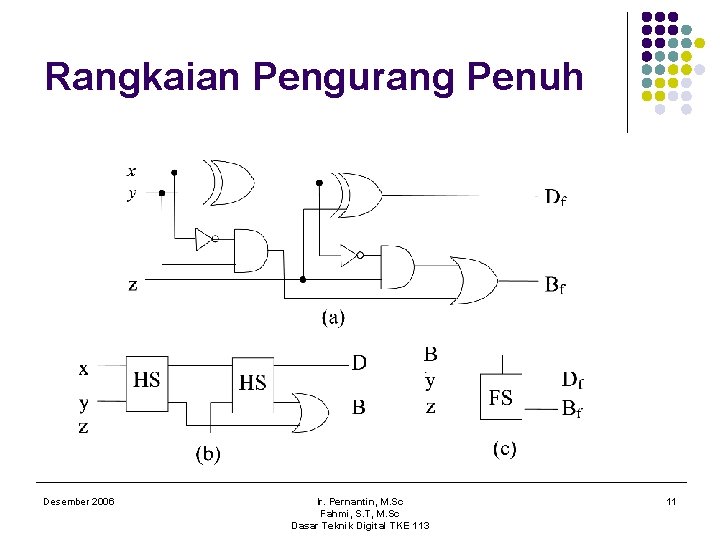

Rangkaian Pengurang Penuh Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 11

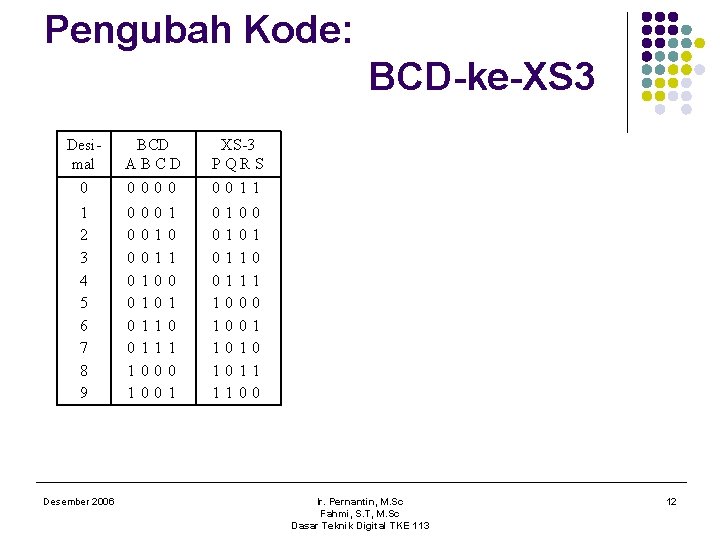

Pengubah Kode: BCD-ke-XS 3 Desimal 0 1 2 3 4 5 6 7 8 9 Desember 2006 BCD A B C D 0000 XS-3 P Q R S 0011 0 0 0 0 1 1 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 0 1 1 0 0 1 0 1 0 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 12

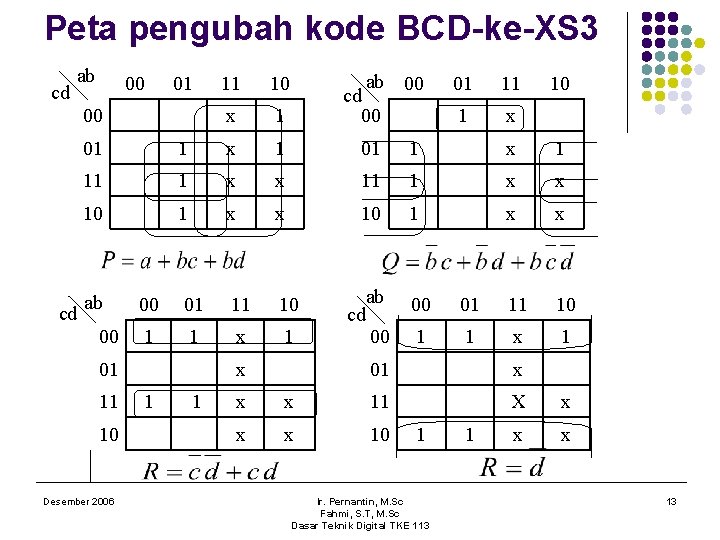

Peta pengubah kode BCD-ke-XS 3 ab 00 cd 01 11 10 x 1 ab 00 cd 00 01 11 10 1 x x 1 00 01 1 x 1 01 1 11 1 x x 10 1 x x ab 00 01 11 10 00 1 1 x 1 cd 00 1 1 x 1 01 x 01 11 1 1 x x 11 10 x x 10 cd Desember 2006 1 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 x X x 1 x x 13

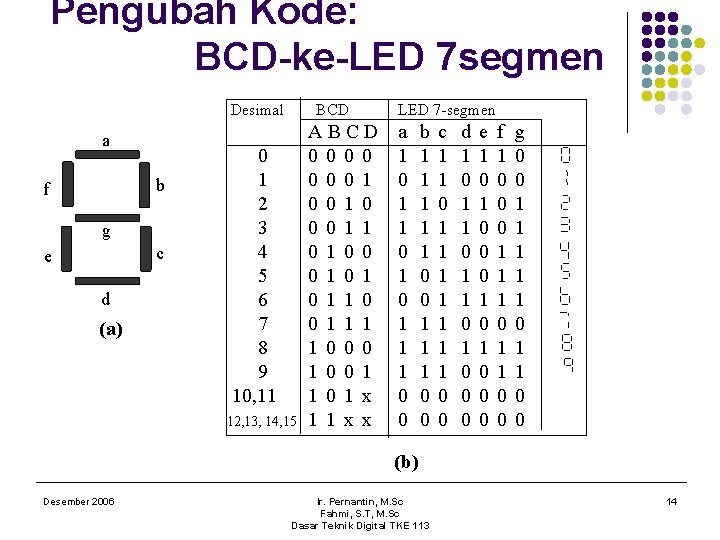

Pengubah Kode: BCD-ke-LED 7 segmen Desimal BCD a b f g c e d (a) LED 7 -segmen A B C D a 0 0 0 1 1 0 0 0 1 0 2 0 0 1 3 0 0 1 1 1 4 0 1 0 0 0 5 0 1 1 6 0 1 1 0 0 7 0 1 1 8 1 0 0 0 1 9 1 0 0 1 1 10, 11 1 0 1 x 0 12, 13, 14, 15 1 1 x x 0 b c 1 1 1 0 1 1 1 1 0 0 d e f g 1 1 1 0 0 0 1 1 1 0 1 1 1 0 0 1 1 0 0 0 0 (b) Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 14

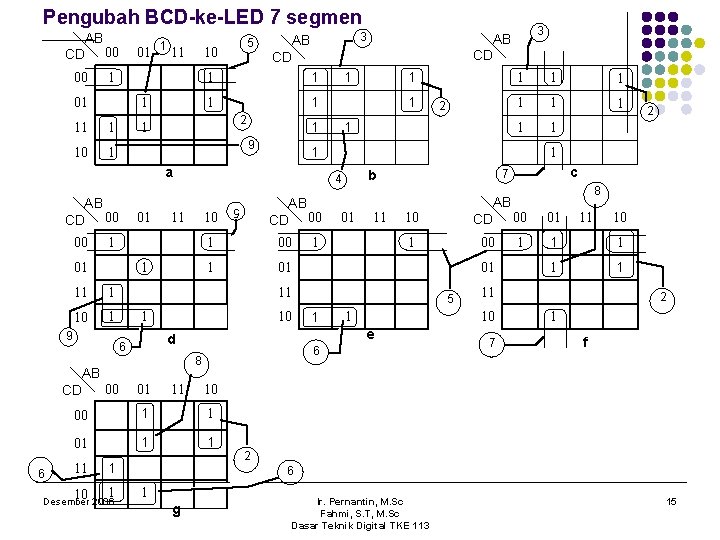

Pengubah BCD-ke-LED 7 segmen AB CD 00 00 01 1 11 10 1 01 1 10 1 5 3 AB CD 1 1 2 1 9 AB CD 00 01 00 1 1 00 01 1 1 01 11 1 10 1 1 1 01 1 1 10 1 9 Desember 2006 01 11 10 1 1 1 00 1 1 1 c 2 1 01 8 11 7 10 1 1 11 10 6 10 1 AB CD 00 5 8 11 1 7 e 1 1 b 01 d 01 1 10 00 11 AB CD 00 5 10 2 1 11 6 AB 00 CD 1 4 11 1 1 a 9 1 1 3 AB CD 2 1 f 2 6 1 g Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 15

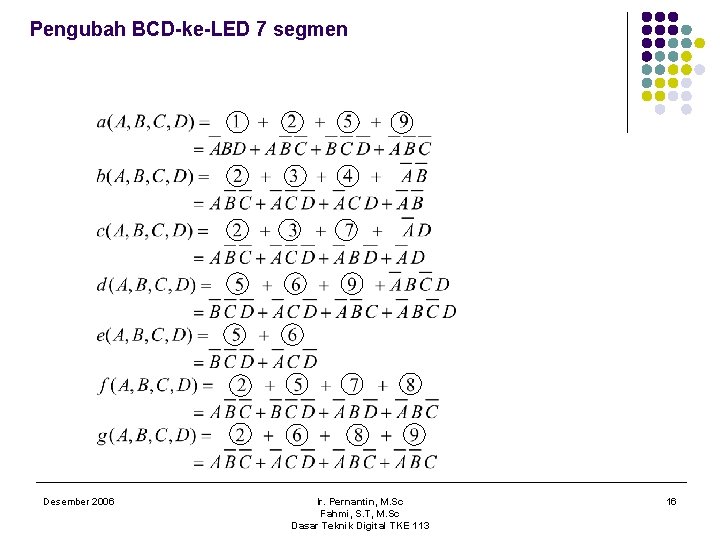

Pengubah BCD-ke-LED 7 segmen Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 16

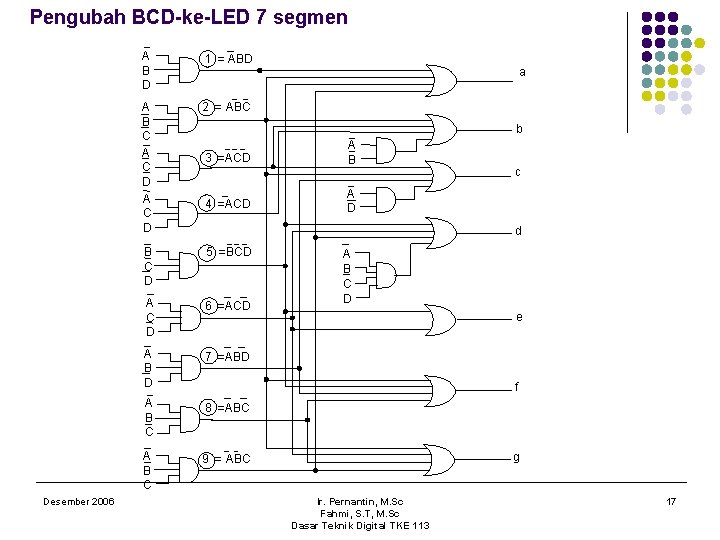

Pengubah BCD-ke-LED 7 segmen Desember 2006 A B D 1 = ABD A B C A C D 2 = ABC B C D 5 =BCD A C D 6 =ACD A B D 7 =ABD A B C 8 =ABC A B C 9 = ABC a b 3 =ACD 4 =ACD A B c A D d A B C D e f g Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 17

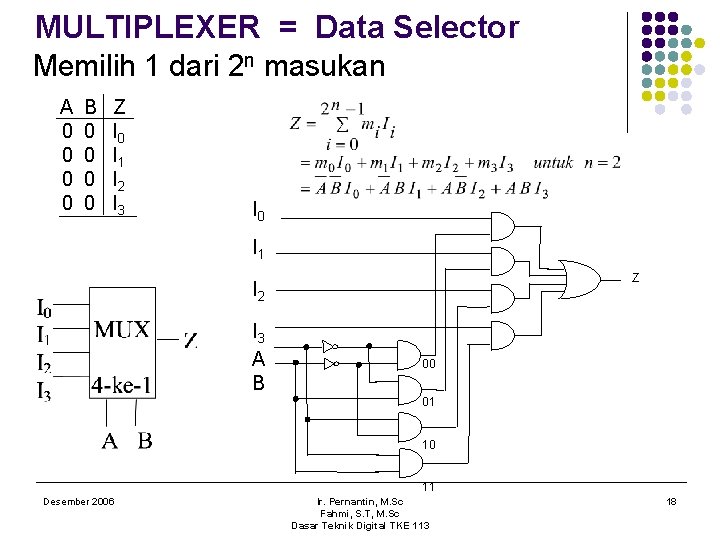

MULTIPLEXER = Data Selector Memilih 1 dari 2 n masukan A 0 0 B 0 0 Z I 0 I 1 I 2 I 3 I 0 I 1 Z I 2 I 3 A B 00 01 10 11 Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 18

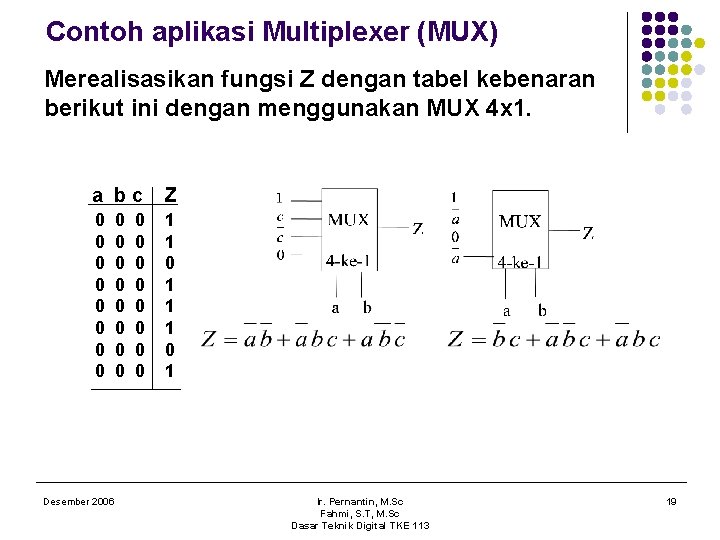

Contoh aplikasi Multiplexer (MUX) Merealisasikan fungsi Z dengan tabel kebenaran berikut ini dengan menggunakan MUX 4 x 1. a bc Z 0 0 0 0 1 1 0 1 Desember 2006 0 0 0 0 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 19

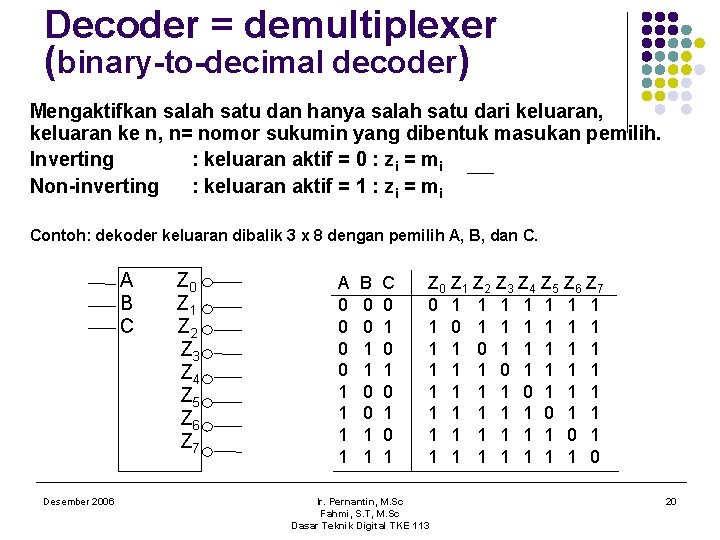

Decoder = demultiplexer (binary-to-decimal decoder) Mengaktifkan salah satu dan hanya salah satu dari keluaran, keluaran ke n, n= nomor sukumin yang dibentuk masukan pemilih. Inverting : keluaran aktif = 0 : zi = mi Non-inverting : keluaran aktif = 1 : zi = mi Contoh: dekoder keluaran dibalik 3 x 8 dengan pemilih A, B, dan C. A B C Desember 2006 Z 0 Z 1 Z 2 Z 3 Z 4 Z 5 Z 6 Z 7 A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 Z 0 Z 1 Z 2 Z 3 Z 4 Z 5 Z 6 Z 7 0 1 1 1 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 20

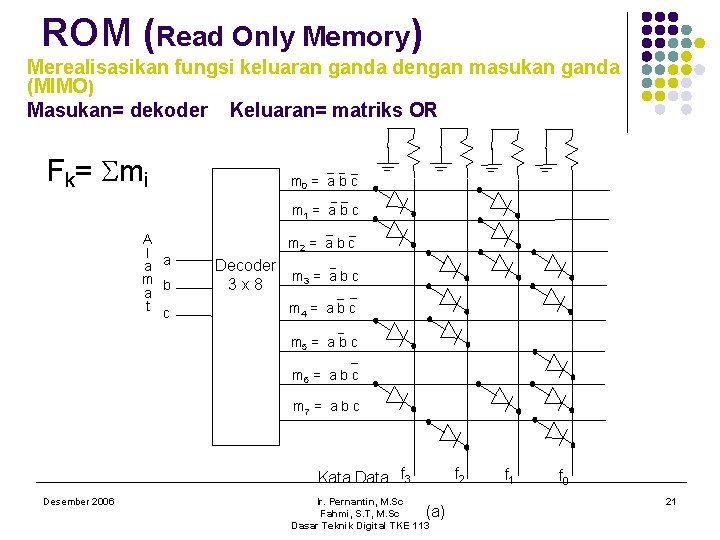

ROM (Read Only Memory) Merealisasikan fungsi keluaran ganda dengan masukan ganda (MIMO) Masukan= dekoder Keluaran= matriks OR Fk= mi m 0 = a b c m 1 = a b c A l a a m b a t c m 2 = a b c Decoder 3 x 8 m 3 = a b c m 4 = a b c m 5 = a b c m 6 = a b c m 7 = a b c Kata Data f 3 Desember 2006 f 2 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 (a) f 1 f 0 21

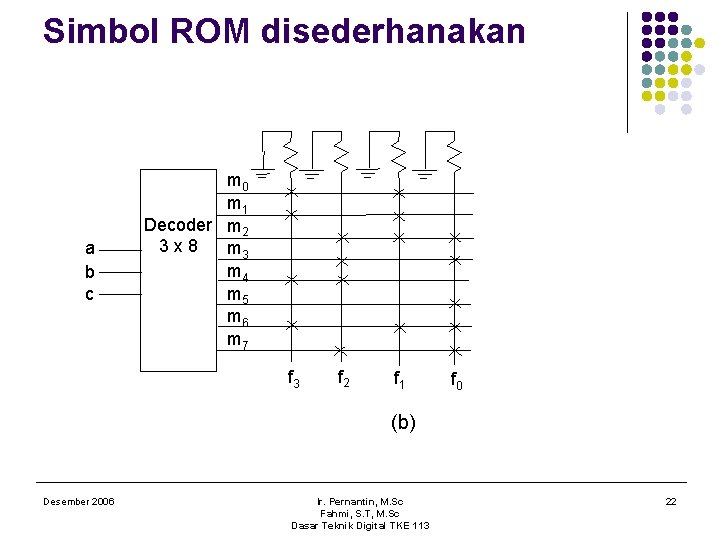

Simbol ROM disederhanakan a b c m 0 m 1 Decoder m 2 3 x 8 m 3 m 4 m 5 m 6 m 7 f 3 f 2 f 1 f 0 (b) Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 22

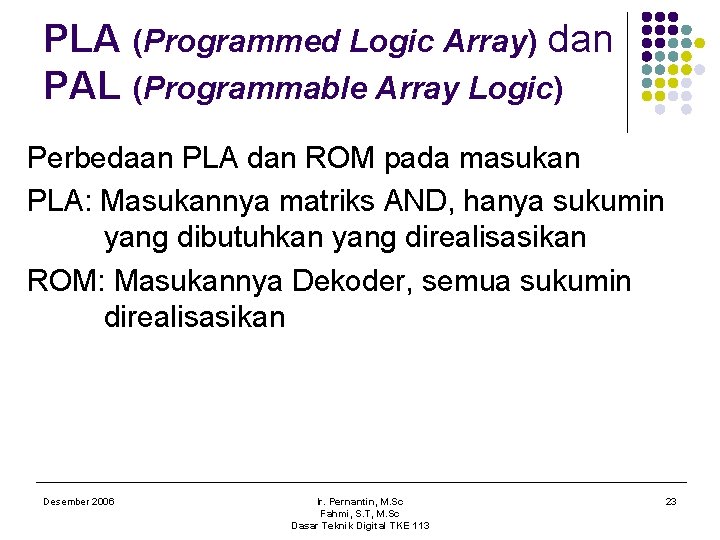

PLA (Programmed Logic Array) dan PAL (Programmable Array Logic) Perbedaan PLA dan ROM pada masukan PLA: Masukannya matriks AND, hanya sukumin yang dibutuhkan yang direalisasikan ROM: Masukannya Dekoder, semua sukumin direalisasikan Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 23

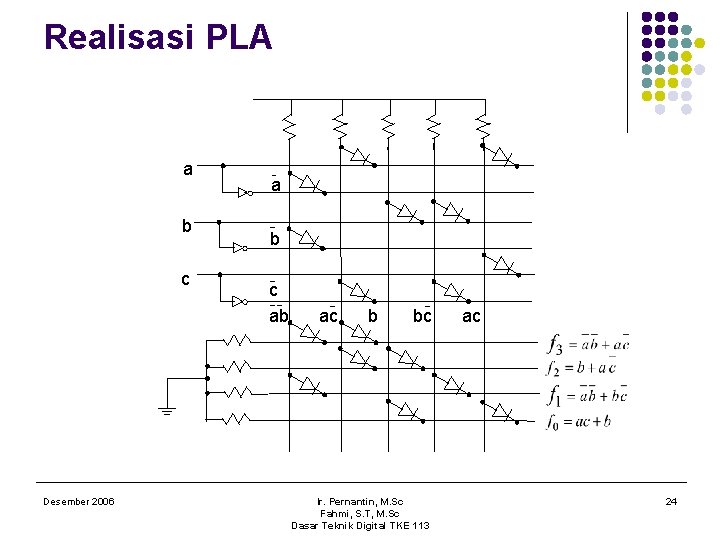

Realisasi PLA a b c Desember 2006 a b c ab ac b bc Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 ac 24

PAL Perbedaan PAL dan PLA pada keluarannya: PLA: matriks OR keluaran dapat diprogram PLA: matriks OR terhubung tetap (tak dapat diprogram) PLA dan PAL: matriks AND masukannya dapat diprogram Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 25

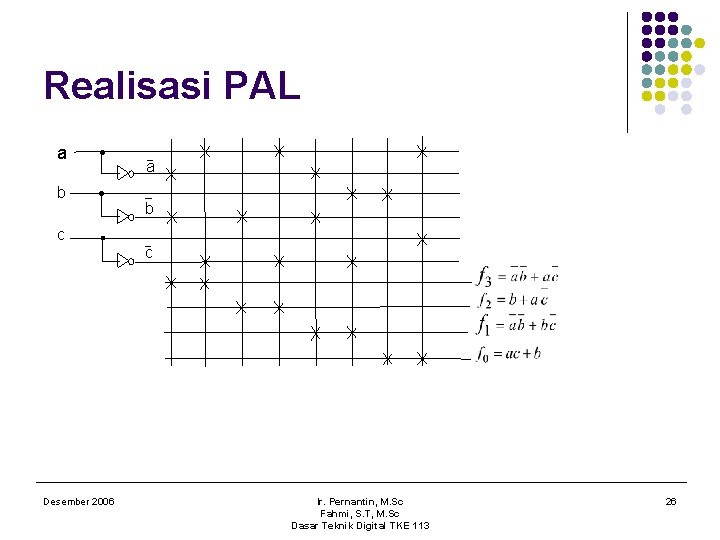

Realisasi PAL a b c c Desember 2006 Ir. Pernantin, M. Sc Fahmi, S. T, M. Sc Dasar Teknik Digital TKE 113 26

- Slides: 26