PENYEDERHANAAN RANGKAIAN LOGIKA PENYEDERHANAAN y AC ABC l

PENYEDERHANAAN RANGKAIAN LOGIKA

PENYEDERHANAAN y = AC + ABC l y diperoleh dengan cara: l 1. Meng. ANDkan A dan C l 2. Meng. ANDkan A, B, dan C l 3. Meng. ORkan AC dan ABC l y= AC + ABC = AC(1+B) = AC 2

PENYEDERHANAAN y= AC + ABC = AC(1+B) = AC 3

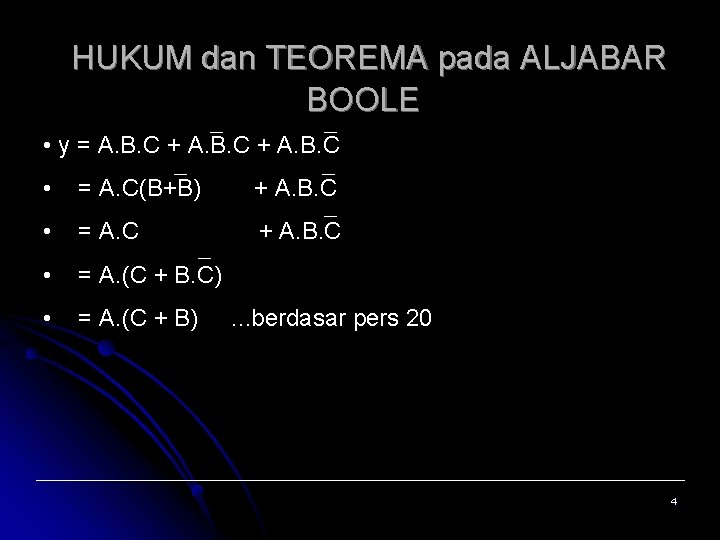

HUKUM dan TEOREMA pada ALJABAR BOOLE • y = A. B. C + A. B. C • = A. C(B+B) + A. B. C • = A. C + A. B. C • = A. (C + B. C) • = A. (C + B) . . . berdasar pers 20 4

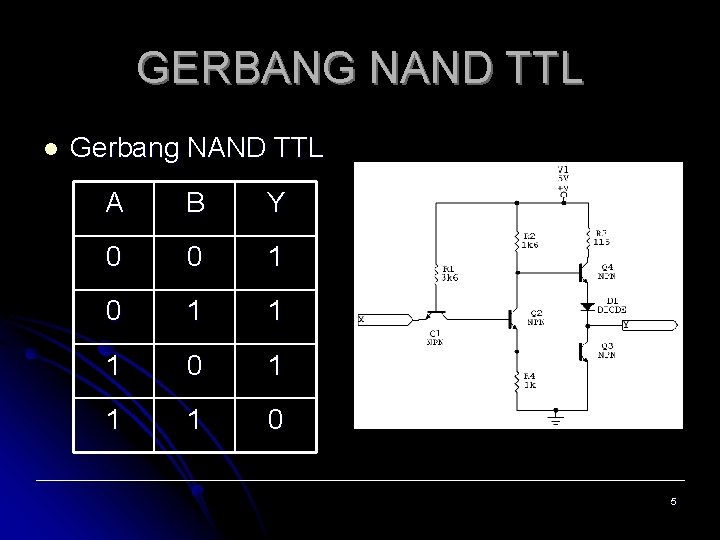

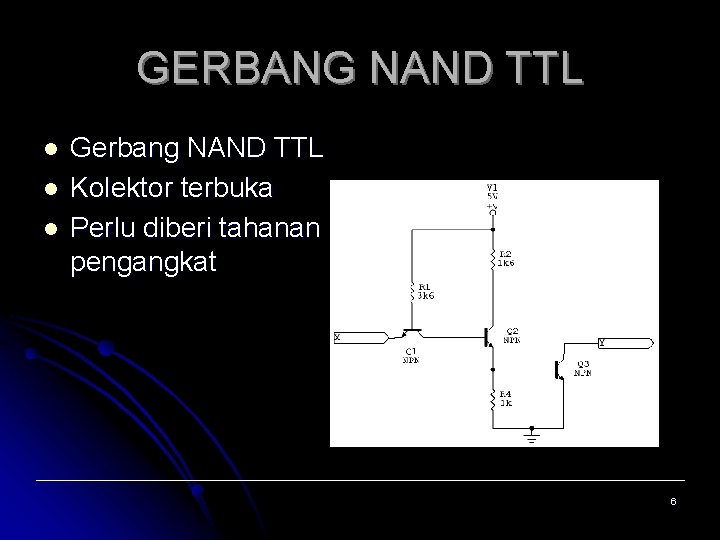

GERBANG NAND TTL l Gerbang NAND TTL A B Y 0 0 1 1 1 0 5

GERBANG NAND TTL l l l Gerbang NAND TTL Kolektor terbuka Perlu diberi tahanan pengangkat 6

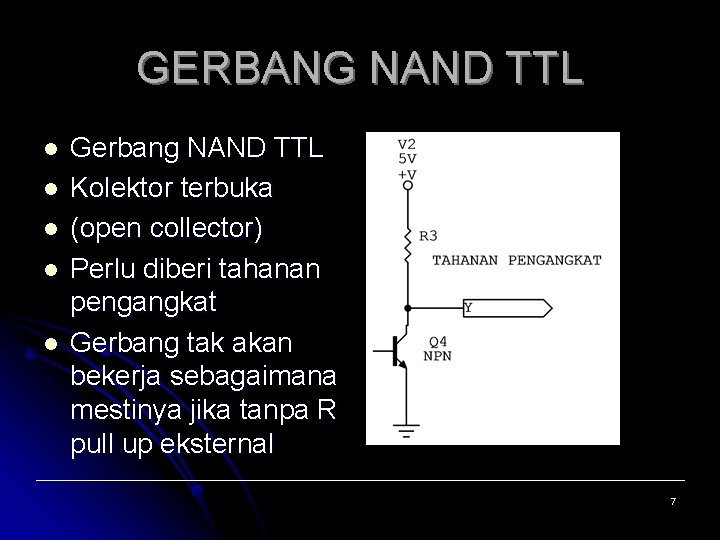

GERBANG NAND TTL l l l Gerbang NAND TTL Kolektor terbuka (open collector) Perlu diberi tahanan pengangkat Gerbang tak akan bekerja sebagaimana mestinya jika tanpa R pull up eksternal 7

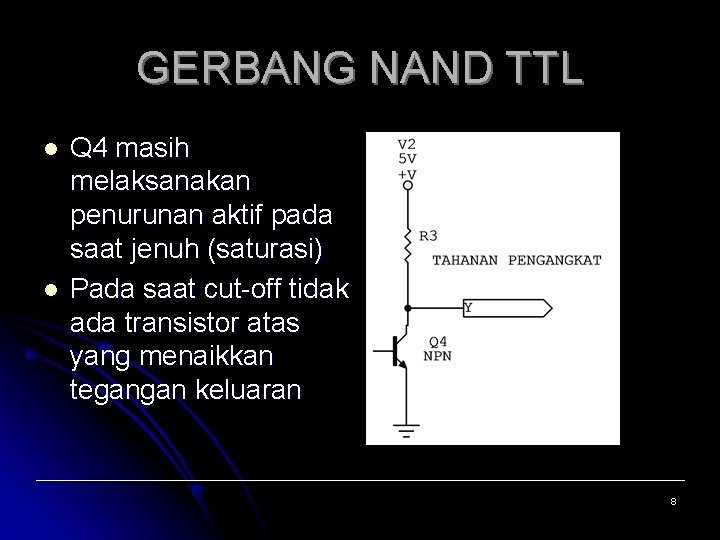

GERBANG NAND TTL l l Q 4 masih melaksanakan penurunan aktif pada saat jenuh (saturasi) Pada saat cut-off tidak ada transistor atas yang menaikkan tegangan keluaran 8

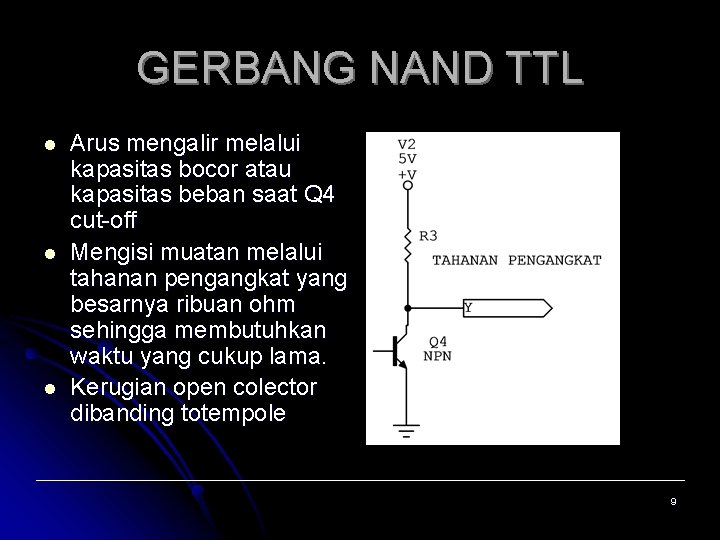

GERBANG NAND TTL l l l Arus mengalir melalui kapasitas bocor atau kapasitas beban saat Q 4 cut-off Mengisi muatan melalui tahanan pengangkat yang besarnya ribuan ohm sehingga membutuhkan waktu yang cukup lama. Kerugian open colector dibanding totempole 9

AND-Tergabung (Wire-AND) l l Keluaran open collector dapat digabungkan menjadi satu dan dihubungkan dengan sebuah tahanan pengangkat gabungan. Meniadakan kebutuhan Gerbang AND penggabung 10

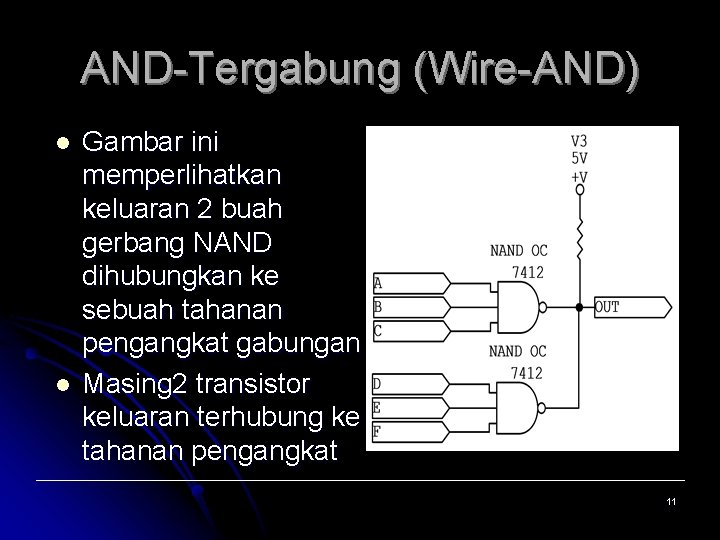

AND-Tergabung (Wire-AND) l l Gambar ini memperlihatkan keluaran 2 buah gerbang NAND dihubungkan ke sebuah tahanan pengangkat gabungan Masing 2 transistor keluaran terhubung ke tahanan pengangkat 11

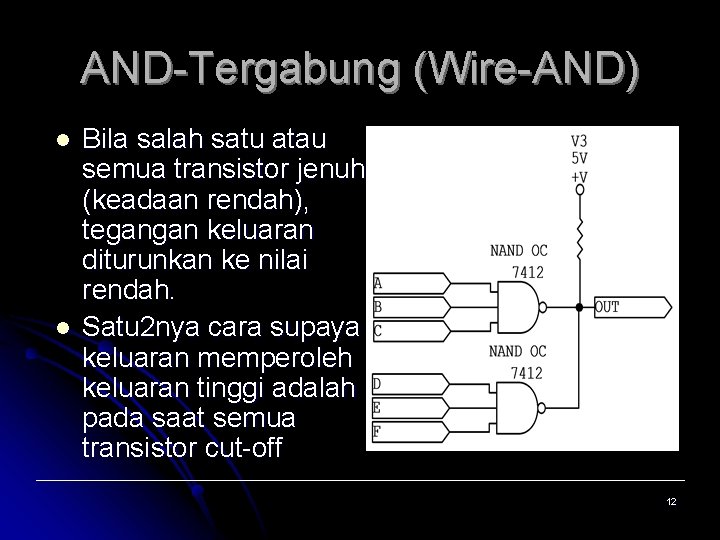

AND-Tergabung (Wire-AND) l l Bila salah satu atau semua transistor jenuh (keadaan rendah), tegangan keluaran diturunkan ke nilai rendah. Satu 2 nya cara supaya keluaran memperoleh keluaran tinggi adalah pada saat semua transistor cut-off 12

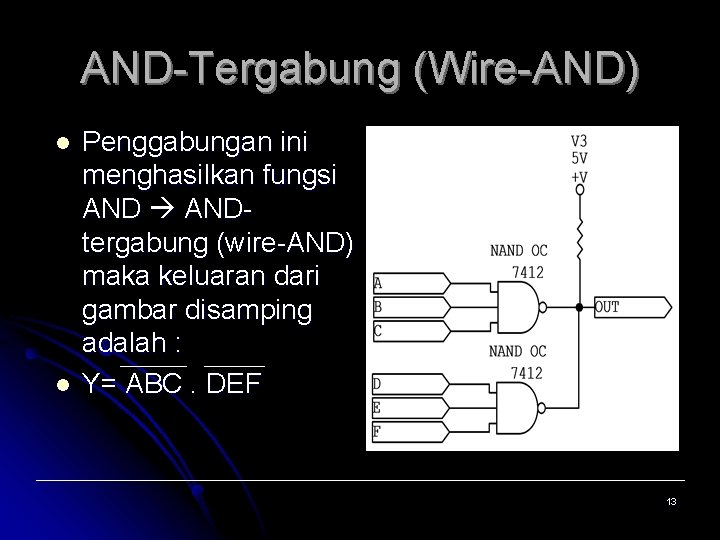

AND-Tergabung (Wire-AND) l l Penggabungan ini menghasilkan fungsi ANDtergabung (wire-AND) maka keluaran dari gambar disamping adalah : Y= ABC. DEF 13

AND-Tergabung (Wire-AND) l l l Penggunaan wire-AND sangat penting dalam sistem digital bus terorganisasi OR-Tergabung (wire-OR) Y=ABC. DEF Berdasar teorema pertama De Morgan Y= ABC + DEF OR-tergabung (wire-OR) 14

DUALITAS TEOREMA ALJABAR BOOLE l l l A+B=B+A A+(B+C)=(A+B)+C A(B+C)=AB+AC A+0=A A+1=1 A+A=A A+A=1 A=A A+B=A. B A+AB=A+B l l l AB=BA A(BC)=(AB)C A+BC=(A+B)(A+C) A. 1=A A. 0=0 A. A=A A. A=0 A=A A+B=A+B A(A+B)=A+B 15

- Slides: 15