Penosov soustavy VY32INOVACEpszczolka 06 3 10 Registry paraleln

- Slides: 10

Přenosové soustavy VY_32_INOVACE_pszczolka_ 06 -3 -10 -Registry – paralelní, sériový Autor: Pszczółka Tomáš Tento výukový materiál byl zpracován v rámci projektu EU peníze středním školám - OP VK 1. 5. CZ. 1. 07/1. 5. 00/34. 0195 – Individualizace a inovace výuky

Anotace Žák získá základní znalosti z oblasti registrů. Bude znát jejich ü Popis ü Realizaci ü Princip

Paralelní registr - úvod ü Také označován statická paměť, paměťový reg. ü Slouží pro vložení a uchování n – bitové informace ü Lze je sestavit z klopných obvodů D i JK ü Během jednoho hodinového impulzu se celá informace zaznamená do celého registru až do příchodu dalšího hodinového impulzu ü Kapacita paměti je určena počtem klopných obvodů

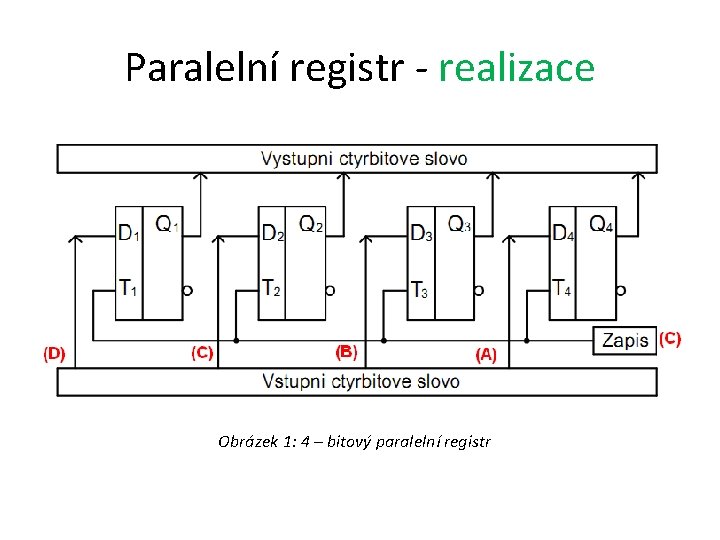

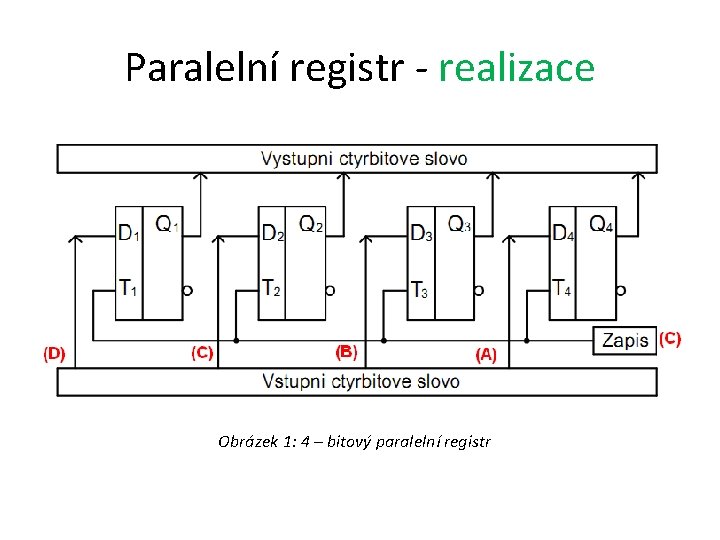

Paralelní registr - realizace Obrázek 1: 4 – bitový paralelní registr

Paralelní registr - závěr ü V praxi se paralelních registrů používá v mnoha digitálních obvodech, především v statických pamětích. ü Rovněž tyto obvody mohou být vybaveny nastavovacím a nulovacím obvodem.

Sériový (posuvný) registr - úvod ü Slouží pro posouvání informace doleva či doprava pomoci hodinového impulzu ü Lze je sestavit z klopných obvodů D i JK ü Mohou být: Sériový vstup, sériový výstup Sériový vstup, paralelní výstup Pozn. : Sériový – Informace vstupuje nebo vystupuje v jednom místě. Paralelní – informace z jednotlivých výstupu jsou přístupny všechny najednou.

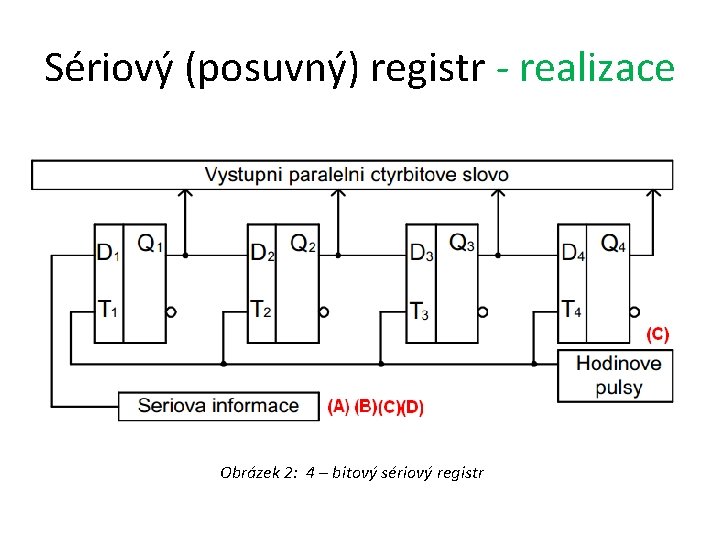

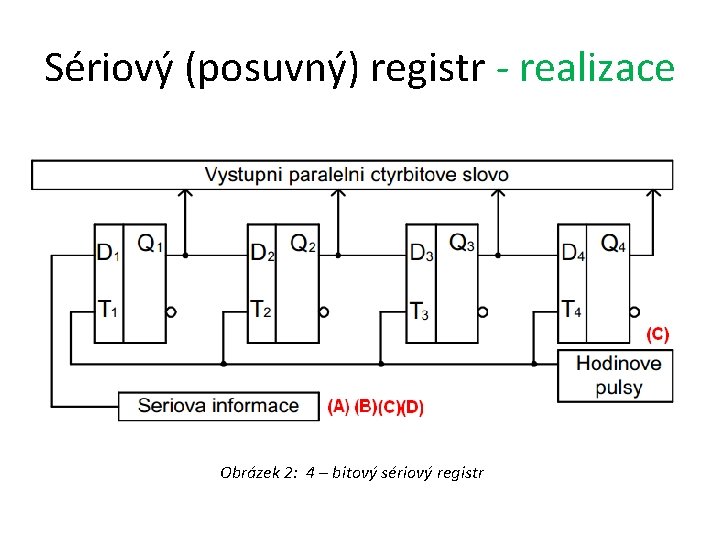

Sériový (posuvný) registr - realizace Obrázek 2: 4 – bitový sériový registr

Sériový (posuvný) registr - princip ü Informace přivedena na vstup prvního klopného obvodu se příchodem hodinového impulzu přenese na jeho výstup, který je spojen se vstupem dalšího klopného obvodu. ü U 4 -bitového registru se tedy celá informace zaznamená čtyřmi hodinovými impulzy a to postupným posouváním celého obsahu registru o jeden stupeň vpravo.

Sériový (posuvný) registr – princip (2) ü Informaci můžeme nyní najednou vybrat. ü Nebo při pokračování hodinových impulzu můžeme informaci postupně snímat z výstupu posledního členu.

POUŽITÁ LITERATURA 1. KESL, Jan. Elektronika 3: Číslicová technika. 2. vyd. Praha: BEN - technická literatura, 2008, ISBN 978 -80 -7300 -182 -7