Penosov soustavy VY32INOVACEpszczolka 06 3 08 Vstup a

![Ukázka využití obvodu 7490 Obrázek 3: Čítač modulo 6 Volně přepracováno dle [2] Ukázka využití obvodu 7490 Obrázek 3: Čítač modulo 6 Volně přepracováno dle [2]](https://slidetodoc.com/presentation_image_h/f297bbd7e7c414ddebba0e7817313cf2/image-9.jpg)

- Slides: 10

Přenosové soustavy VY_32_INOVACE_pszczolka_ 06 -3 -08 -Vstup a výstup čítače - principy Autor: Pszczółka Tomáš Tento výukový materiál byl zpracován v rámci projektu EU peníze středním školám - OP VK 1. 5. CZ. 1. 07/1. 5. 00/34. 0195 – Individualizace a inovace výuky

Anotace Žák získá rozšířené znalosti z oblasti integrovaných čítačů. Bude umět s nimi pracovat a bude se orientovat v pojmech: - Nastavení - Vynulování - Modulo - Atd. .

Integrované čítače - nulování ü Integrované čítače jsou vybaveny společným nulováním pro všechny čtyři klopné obvody. ü Vnitřní signál nulování MR je vytvářen hradlem AND ze vstupních signálu MR 1, MR 2. ü Tedy když oba vstupy nulování budou v logické 1, dojde k vynulování obvodu. ü Tyto vstupy nulování lze použit k realizaci zkráceného cyklu čítaní.

Integrované čítače - nastavení ü Integrované čítače jsou vybaveny vstupem nastavení pro všechny stupně najednou na stav logická 1. ü Pokud na oba nastavovací vstupy přivedeme logickou jedničku, dojde k nastavení na maximální hodnotu čítače. ü U 7490 to je „ 9“ (1001). ü Vstupy nastavení se dají využít k nastavení zkráceného cyklu.

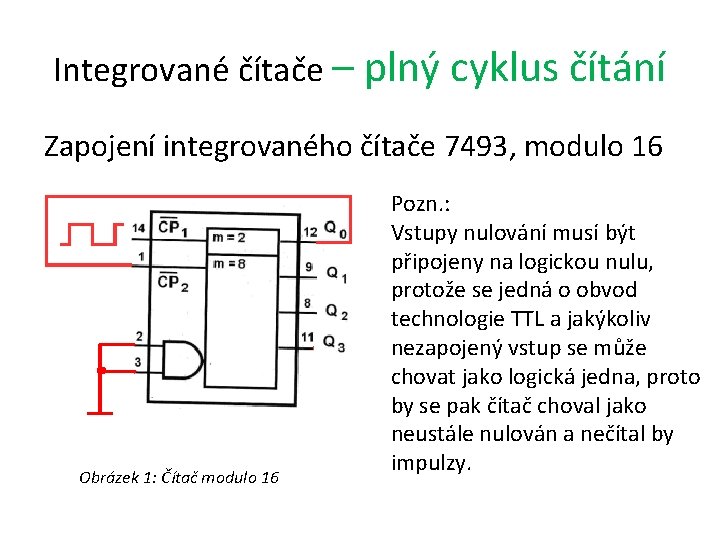

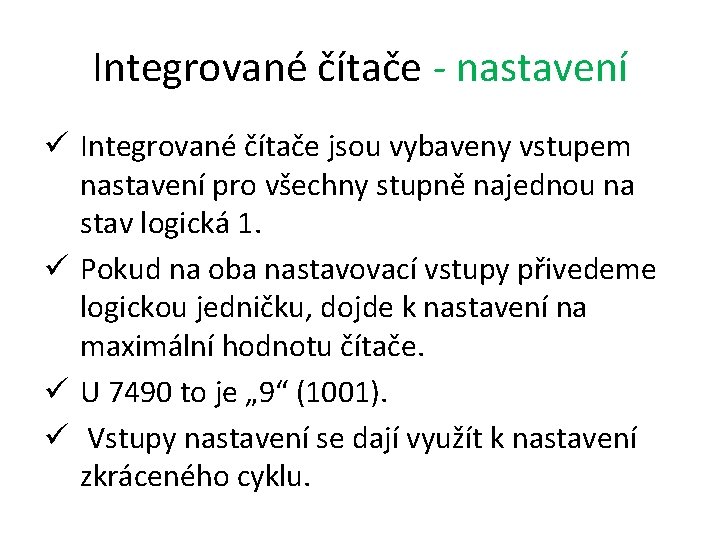

Integrované čítače – plný cyklus čítání Zapojení integrovaného čítače 7493, modulo 16 Obrázek 1: Čítač modulo 16 Pozn. : Vstupy nulování musí být připojeny na logickou nulu, protože se jedná o obvod technologie TTL a jakýkoliv nezapojený vstup se může chovat jako logická jedna, proto by se pak čítač choval jako neustále nulován a nečítal by impulzy.

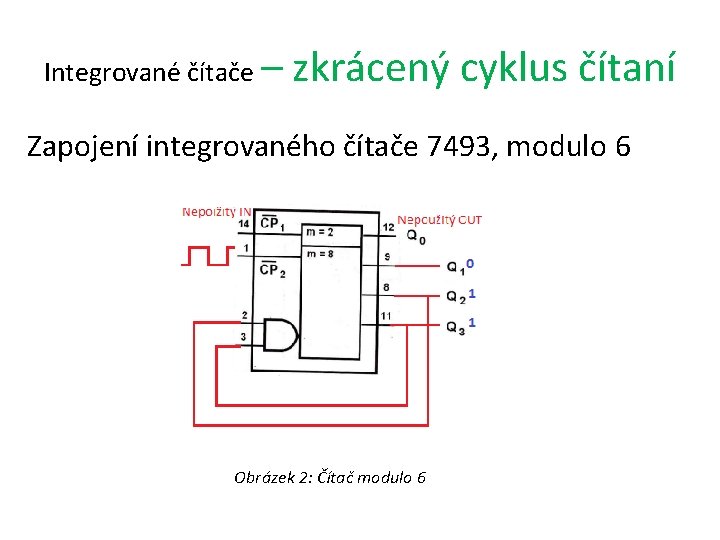

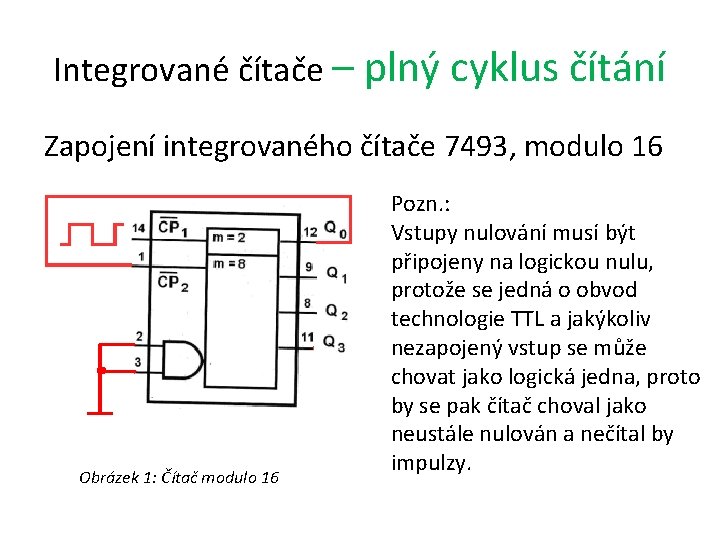

Integrované čítače – zkrácený cyklus čítaní Zapojení integrovaného čítače 7493, modulo 6 Obrázek 2: Čítač modulo 6

Integrované čítače – zkrácený cyklus čítaní ü Obsahuje -li požadované maximální čítané číslo v binárním vyjádření jen dvě logické 1, Např. : 011 - 6 ü je možné provést ztracený cyklus propojením výstupů na kterých má být úroveň 1 se vstupy nulování (viz obrázek 2). ü Má –li být cyklus zkrácen na číslo (111 – 7), které obsahuje tři jedničky je třeba použít externí hradlo AND.

Integrované čítače – prodloužený cyklus čítaní Integrované obvody se řadí za sebou a pak výstup Q 3 připojíme na vstup dalšího stupně čítače. Pozn. : I tady lze nastavit zkrácený cyklus čítaní.

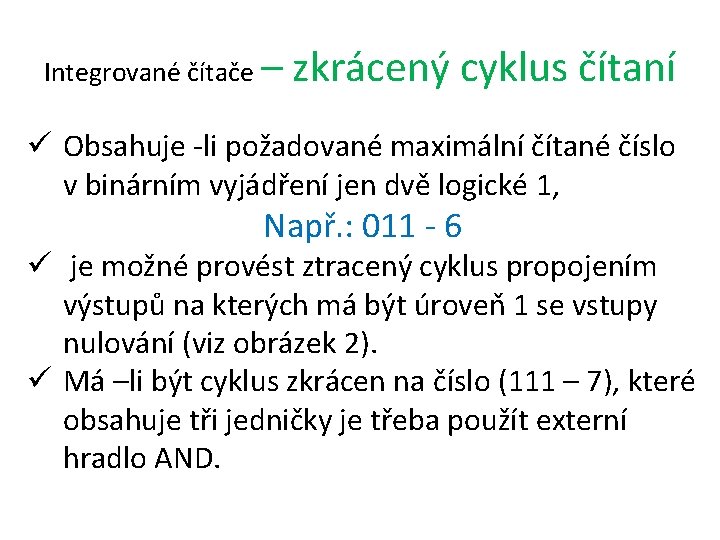

![Ukázka využití obvodu 7490 Obrázek 3 Čítač modulo 6 Volně přepracováno dle 2 Ukázka využití obvodu 7490 Obrázek 3: Čítač modulo 6 Volně přepracováno dle [2]](https://slidetodoc.com/presentation_image_h/f297bbd7e7c414ddebba0e7817313cf2/image-9.jpg)

Ukázka využití obvodu 7490 Obrázek 3: Čítač modulo 6 Volně přepracováno dle [2]

POUŽITÁ LITERATURA 1. JEDLIČKA, Petr. Přehled obvodů řady TTL 7400. 2. vyd. Praha: BEN - technická literatura, 2005, 287 s. ISBN 80 -730 -0169 -1 2. MATOUŠEK, David. Číslicová technika: základy konstruktérské praxe. 1. vyd. Praha: BEN - technická literatura, 2001, 207 s. ISBN 80 -730 -0025 -3