PEBS Electronics W Karpinski I Physikalisches Institut Aachen

PEBS Electronics W. Karpinski I. Physikalisches Institut Aachen, 10 January 2007 5 Feb 2007 Waclaw Karpinski 1

Outline An overview of the PEBS Electronics Subdetector Readout: - TRD - Tracker - ECAL - To. F - TGB (Trigger Box) Summary 5 Feb 2007 Waclaw Karpinski 2

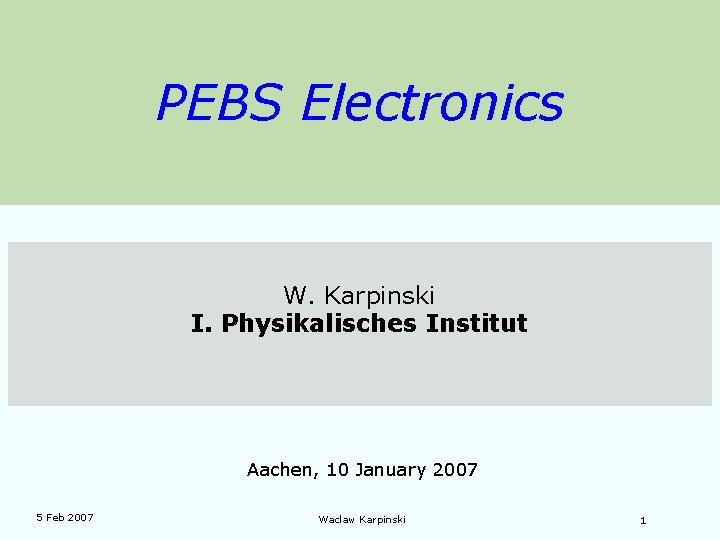

PEBS Electronics 5 Feb 2007 Waclaw Karpinski 3

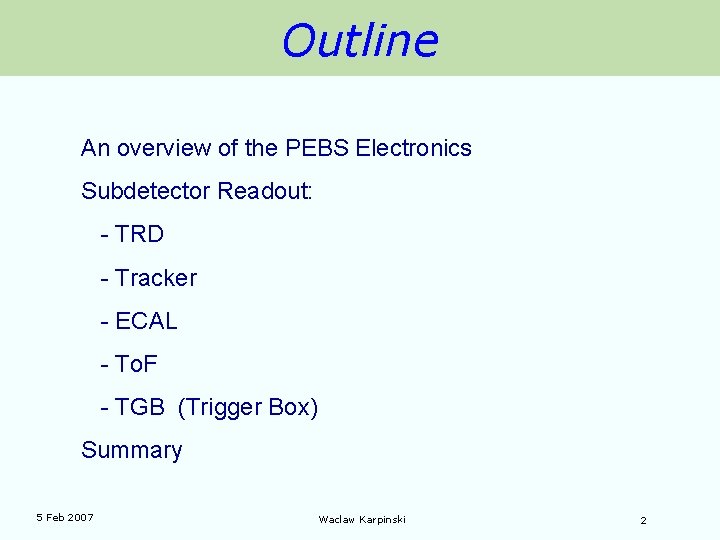

AMS Electronics 5 Feb 2007 Waclaw Karpinski 4

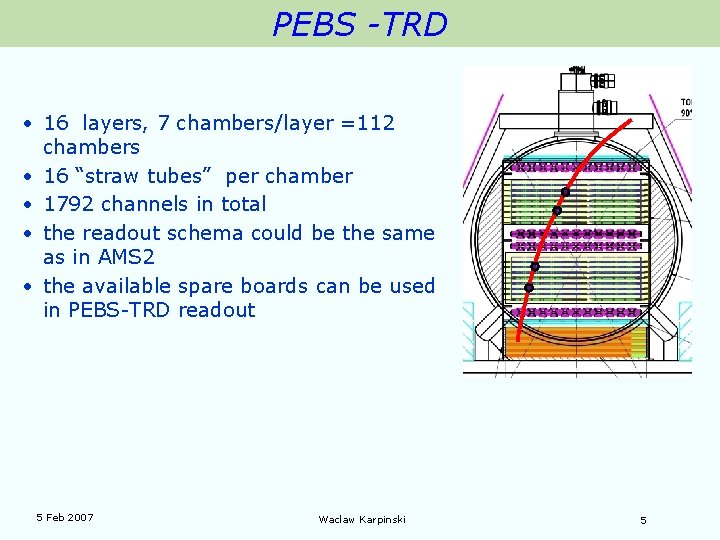

PEBS -TRD • 16 layers, 7 chambers/layer =112 chambers • 16 “straw tubes” per chamber • 1792 channels in total • the readout schema could be the same as in AMS 2 • the available spare boards can be used in PEBS-TRD readout 5 Feb 2007 Waclaw Karpinski 5

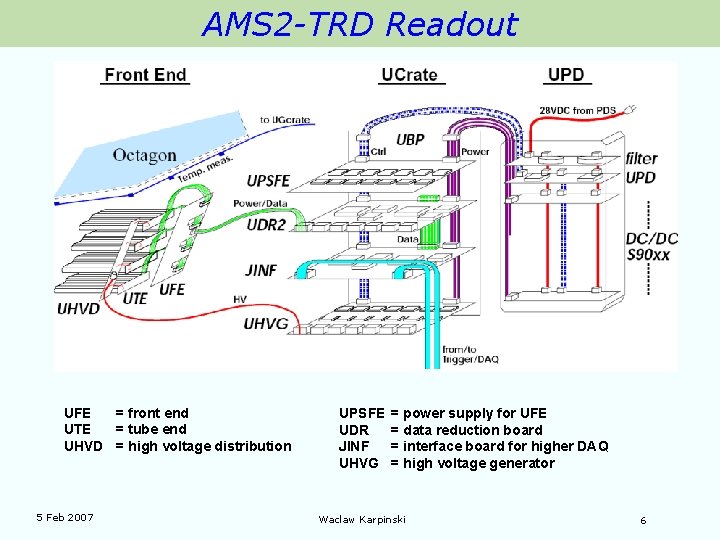

AMS 2 -TRD Readout UFE = front end UTE = tube end UHVD = high voltage distribution 5 Feb 2007 UPSFE UDR JINF UHVG = power supply for UFE = data reduction board = interface board for higher DAQ = high voltage generator Waclaw Karpinski 6

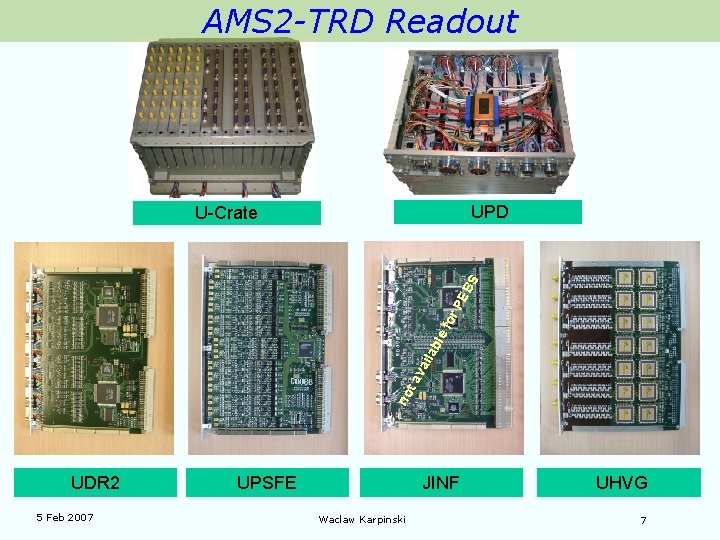

AMS 2 -TRD Readout UPD no t a v ail ab le fo r P EB S U-Crate UDR 2 5 Feb 2007 UPSFE JINF Waclaw Karpinski UHVG 7

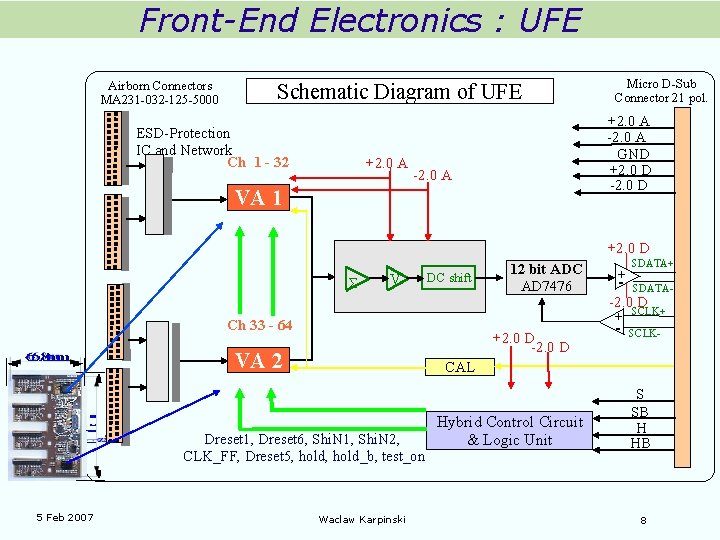

Front-End Electronics : UFE Airborn Connectors MA 231 -032 -125 -5000 Schematic Diagram of UFE ESD-Protection IC and Network Ch 1 - 32 +2. 0 A Micro D-Sub Connector 21 pol. +2. 0 A -2. 0 A GND +2. 0 D -2. 0 A VA 1 +2. 0 D V DC shift Ch 33 - 64 +2. 0 D -2. 0 D VA 2 + - SDATA+ SDATA- -2. 0 SCLK+ D + - SCLK- CAL Dreset 1, Dreset 6, Shi. N 1, Shi. N 2, CLK_FF, Dreset 5, hold_b, test_on 5 Feb 2007 12 bit ADC AD 7476 Waclaw Karpinski Hybrid Control Circuit & Logic Unit S SB H HB 8

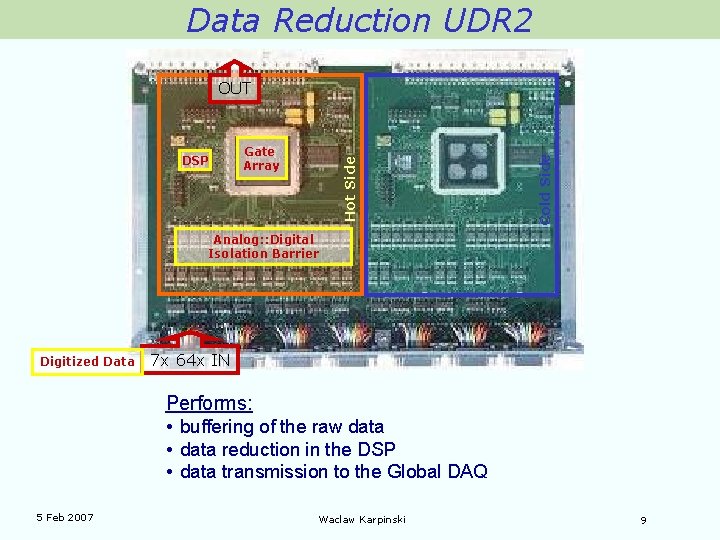

Data Reduction UDR 2 Gate Array Hot Side DSP Cold Side OUT Analog: : Digital Isolation Barrier Digitized Data 7 x 64 x IN Performs: • buffering of the raw data • data reduction in the DSP • data transmission to the Global DAQ 5 Feb 2007 Waclaw Karpinski 9

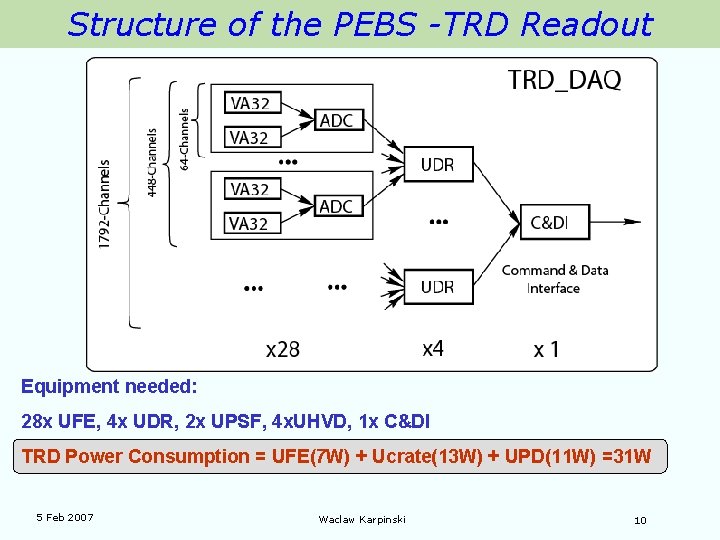

Structure of the PEBS -TRD Readout Equipment needed: 28 x UFE, 4 x UDR, 2 x UPSF, 4 x. UHVD, 1 x C&DI TRD Power Consumption = UFE(7 W) + Ucrate(13 W) + UPD(11 W) =31 W 5 Feb 2007 Waclaw Karpinski 10

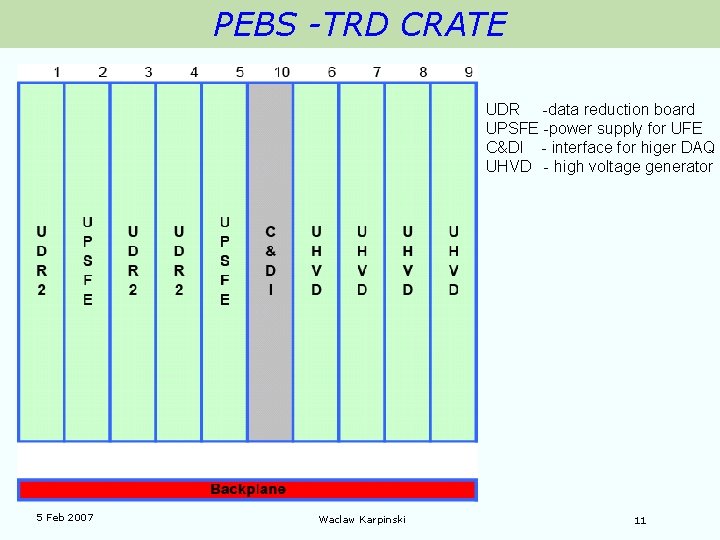

PEBS -TRD CRATE UDR -data reduction board UPSFE -power supply for UFE C&DI - interface for higer DAQ UHVD - high voltage generator 5 Feb 2007 Waclaw Karpinski 11

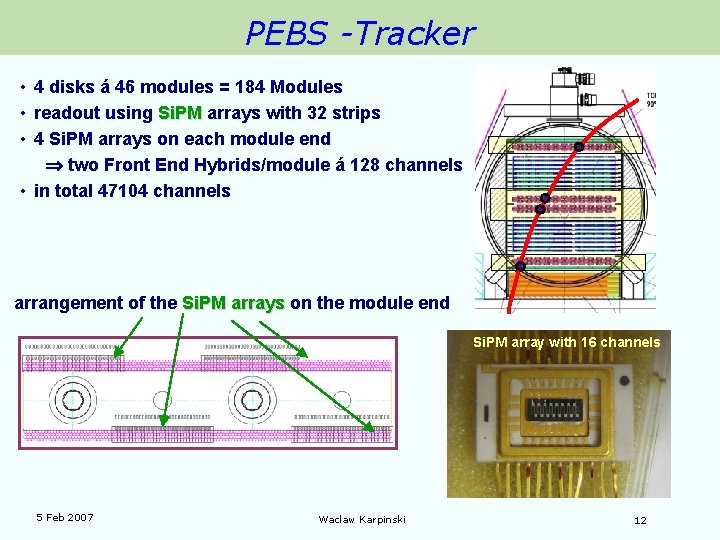

PEBS -Tracker • 4 disks á 46 modules = 184 Modules • readout using Si. PM arrays with 32 strips Si. PM • 4 Si. PM arrays on each module end two Front End Hybrids/module á 128 channels • in total 47104 channels arrangement of the Si. PM arrays on the module end arrays Si. PM array with 16 channels 5 Feb 2007 Waclaw Karpinski 12

PEBS -Tracker • Si. PM specifications Si. PM - channel size: 1 mm x 0. 25 mm - pixel size: 0. 043 x 0. 043 mm 2 = 135 pixels/channel 8 bit ADC - operating voltage: ~ 40 V - gain = 0. 8 x 106 preamplifier with large dynamic range necessary - Si. PM gain varies with bias voltage: 40% / 1 V Do we need gain adjustment for individual channels ? If yes, it must be implemented on chip level (DAC) new chip design necessary significant increase of cost and development time - dark current =500 n. A/channel - dark count ~. 5 MHz (40 V, T=22°C) fast shaping time required to reduce pile up ac coupling between detector and preamplifier or active leakage current compensation on the chip 5 Feb 2007 Waclaw Karpinski 13

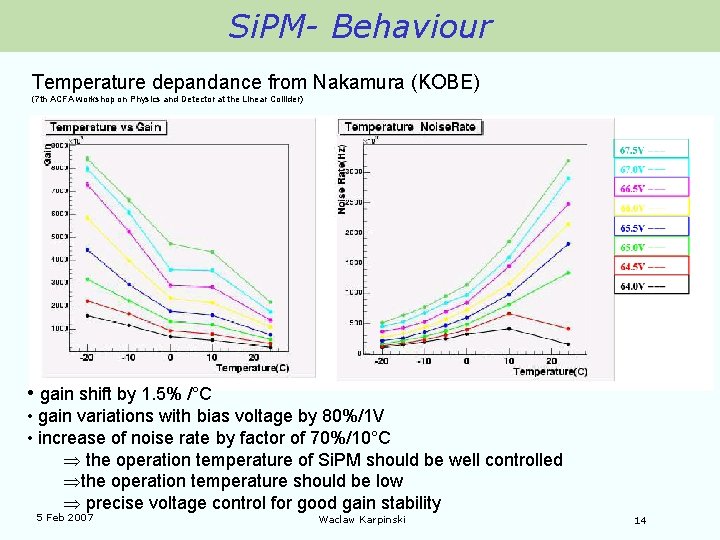

Si. PM- Behaviour Temperature depandance from Nakamura (KOBE) (7 th ACFA workshop on Physics and Detector at the Linear Collider) • gain shift by 1. 5% /°C • gain variations with bias voltage by 80%/1 V • increase of noise rate by factor of 70%/10°C the operation temperature of Si. PM should be well controlled the operation temperature should be low precise voltage control for good gain stability 5 Feb 2007 Waclaw Karpinski 14

ROCs possibly adequate for Si. PM signal processing 5 Feb 2007 Waclaw Karpinski 15

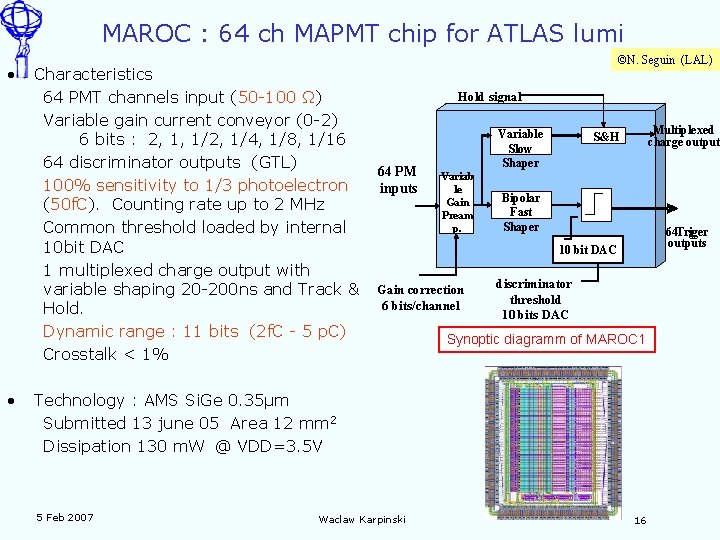

MAROC : 64 ch MAPMT chip for ATLAS lumi • • Characteristics 64 PMT channels input (50 -100 Ω) Variable gain current conveyor (0 -2) 6 bits : 2, 1, 1/2, 1/4, 1/8, 1/16 64 discriminator outputs (GTL) 100% sensitivity to 1/3 photoelectron (50 f. C). Counting rate up to 2 MHz Common threshold loaded by internal 10 bit DAC 1 multiplexed charge output with variable shaping 20 -200 ns and Track & Hold. Dynamic range : 11 bits (2 f. C - 5 p. C) Crosstalk < 1% ©N. Seguin (LAL) Hold signal 64 PM inputs Variable Slow Shaper Variab le Gain Pream p. Multiplexed charge output S&H Bipolar Fast Shaper 64 Trigger outputs 10 bit DAC Gain correction 6 bits/channel discriminator threshold 10 bits DAC Synoptic diagramm of MAROC 1 Technology : AMS Si. Ge 0. 35µm Submitted 13 june 05 Area 12 mm 2 Dissipation 130 m. W @ VDD=3. 5 V 5 Feb 2007 Waclaw Karpinski 16

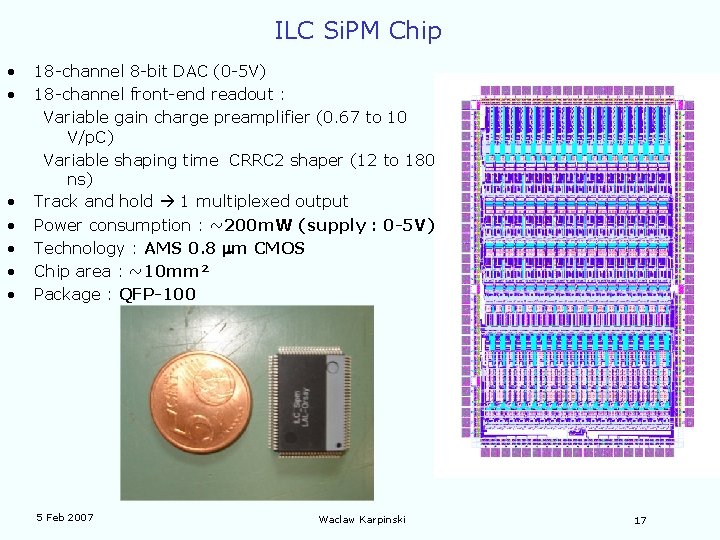

ILC Si. PM Chip • • 18 -channel 8 -bit DAC (0 -5 V) 18 -channel front-end readout : Variable gain charge preamplifier (0. 67 to 10 V/p. C) Variable shaping time CRRC 2 shaper (12 to 180 ns) Track and hold 1 multiplexed output Power consumption : ~200 m. W (supply : 0 -5 V) Technology : AMS 0. 8 m CMOS Chip area : ~10 mm² Package : QFP-100 5 Feb 2007 Waclaw Karpinski 17

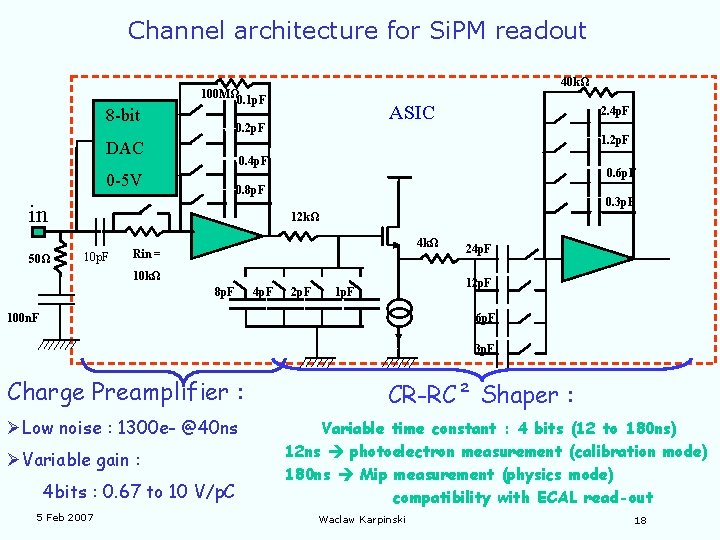

Channel architecture for Si. PM readout 8 -bit ASIC 0. 2 p. F DAC 2. 4 p. F 1. 2 p. F 0. 4 p. F 0 -5 V 0. 6 p. F 0. 8 p. F in 50Ω 40 kΩ 100 MΩ 0. 1 p. F 0. 3 p. F 12 kΩ 10 p. F 4 kΩ Rin = 10 kΩ 8 p. F 4 p. F 24 p. F 12 p. F 100 n. F 6 p. F 3 p. F Charge Preamplifier : ØLow noise : 1300 e- @40 ns ØVariable gain : 4 bits : 0. 67 to 10 V/p. C 5 Feb 2007 CR-RC² Shaper : Variable time constant : 4 bits (12 to 180 ns) 12 ns photoelectron measurement (calibration mode) 180 ns Mip measurement (physics mode) compatibility with ECAL read-out Waclaw Karpinski 18

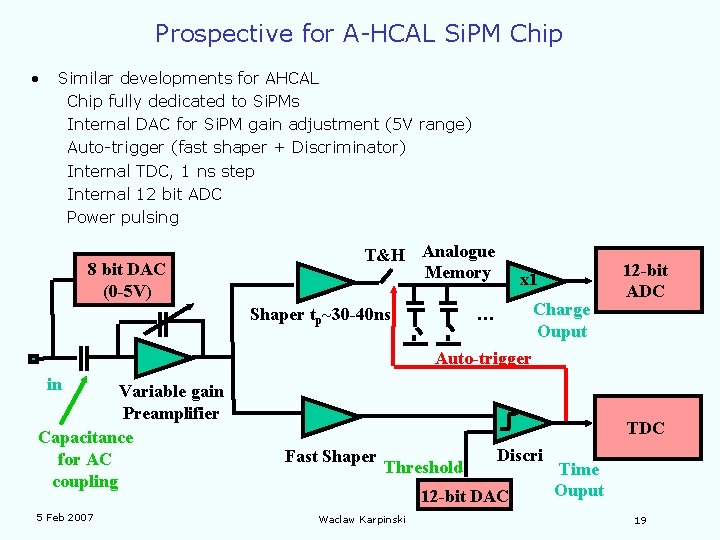

Prospective for A-HCAL Si. PM Chip • Similar developments for AHCAL Chip fully dedicated to Si. PMs Internal DAC for Si. PM gain adjustment (5 V range) Auto-trigger (fast shaper + Discriminator) Internal TDC, 1 ns step Internal 12 bit ADC Power pulsing 8 bit DAC (0 -5 V) T&H Analogue Memory Shaper tp~30 -40 ns x 1 Charge Ouput … 12 -bit ADC Auto-trigger in Variable gain Preamplifier Capacitance for AC coupling 5 Feb 2007 TDC Fast Shaper Threshold Discri 12 -bit DAC Waclaw Karpinski Time Ouput 19

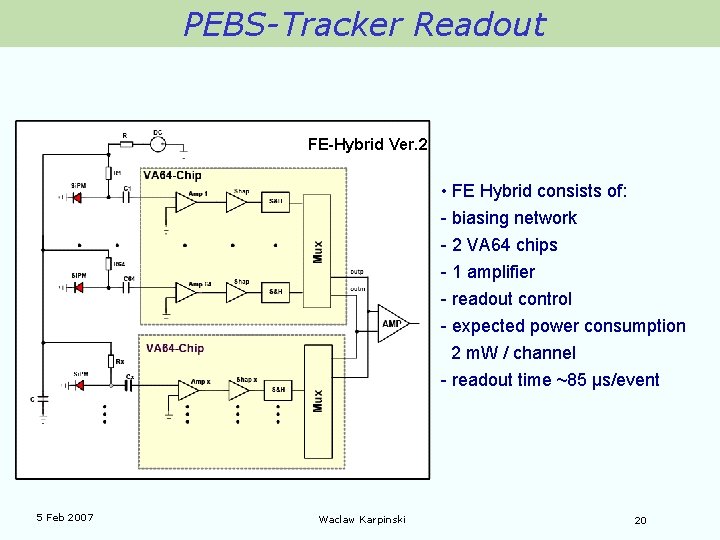

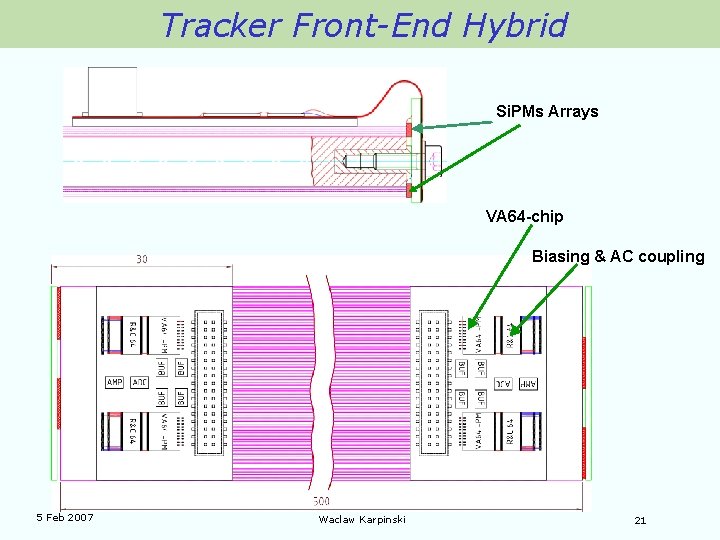

PEBS-Tracker Readout FE-Hybrid Ver. 2 • FE Hybrid consists of: - biasing network - 2 VA 64 chips - 1 amplifier - readout control - expected power consumption 2 m. W / channel - readout time ~85 µs/event 5 Feb 2007 Waclaw Karpinski 20

Tracker Front-End Hybrid Si. PMs Arrays VA 64 -chip Biasing & AC coupling 5 Feb 2007 Waclaw Karpinski 21

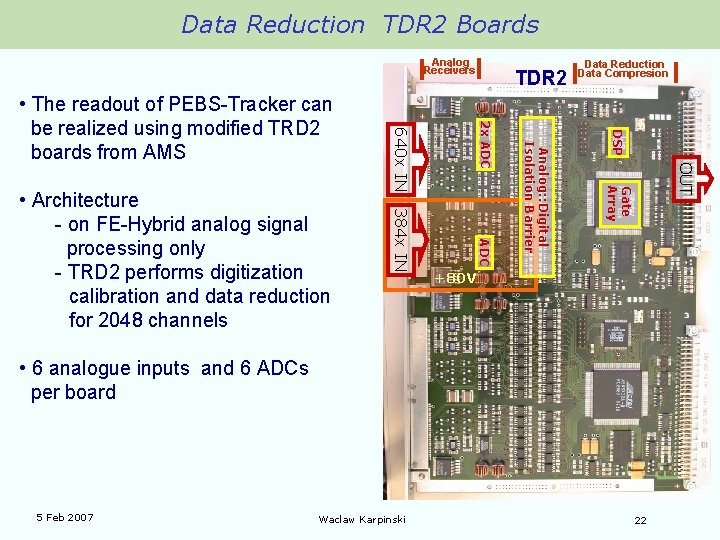

Data Reduction TDR 2 Boards Analog Receivers DSP +80 V • 6 analogue inputs and 6 ADCs per board 5 Feb 2007 Waclaw Karpinski 22 OUT Gate Array ADC 384 x IN Analog: : Digital Isolation Barrier 2 x ADC 640 x IN • The readout of PEBS-Tracker can be realized using modified TRD 2 boards from AMS • Architecture - on FE-Hybrid analog signal processing only - TRD 2 performs digitization calibration and data reduction for 2048 channels TDR 2 Data Reduction Data Compresion

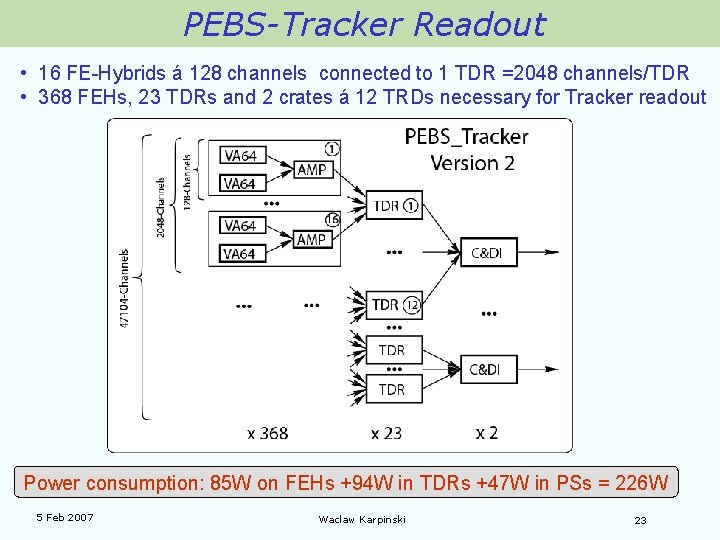

PEBS-Tracker Readout • 16 FE-Hybrids á 128 channels connected to 1 TDR =2048 channels/TDR • 368 FEHs, 23 TDRs and 2 crates á 12 TRDs necessary for Tracker readout Power consumption: 85 W on FEHs +94 W in TDRs +47 W in PSs = 226 W 5 Feb 2007 Waclaw Karpinski 23

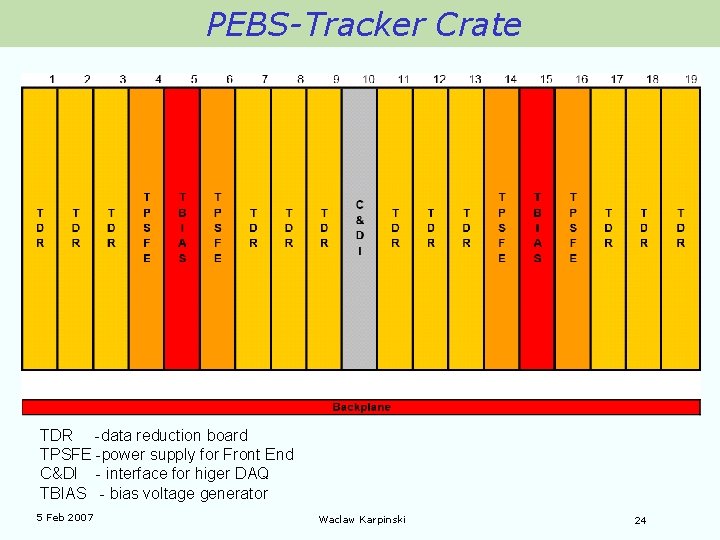

PEBS-Tracker Crate TDR -data reduction board TPSFE -power supply for Front End C&DI - interface for higer DAQ TBIAS - bias voltage generator 5 Feb 2007 Waclaw Karpinski 24

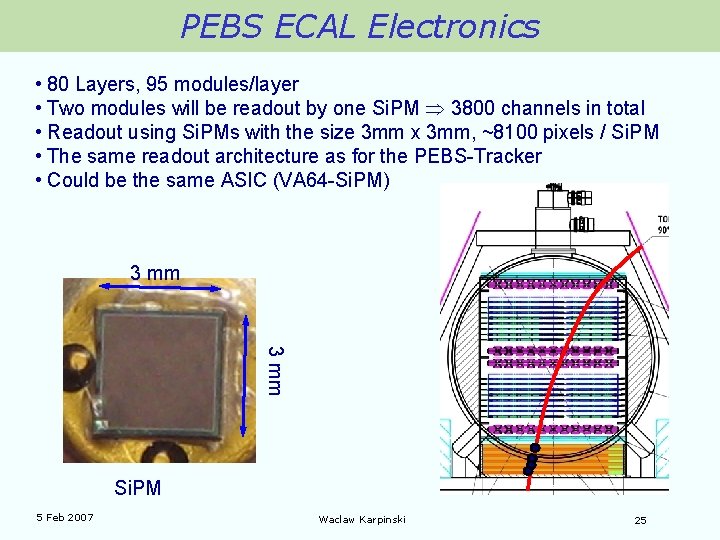

PEBS ECAL Electronics • 80 Layers, 95 modules/layer • Two modules will be readout by one Si. PM 3800 channels in total • Readout using Si. PMs with the size 3 mm x 3 mm, ~8100 pixels / Si. PM • The same readout architecture as for the PEBS-Tracker • Could be the same ASIC (VA 64 -Si. PM) 3 mm Si. PM 5 Feb 2007 Waclaw Karpinski 25

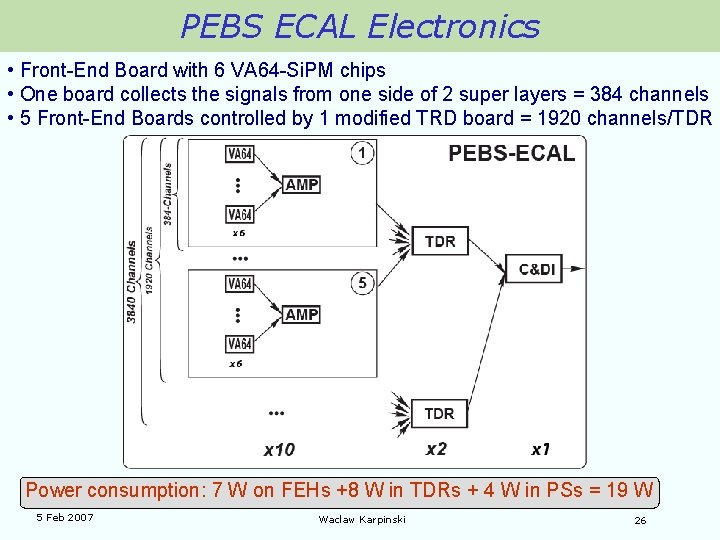

PEBS ECAL Electronics • Front-End Board with 6 VA 64 -Si. PM chips • One board collects the signals from one side of 2 super layers = 384 channels • 5 Front-End Boards controlled by 1 modified TRD board = 1920 channels/TDR Power consumption: 7 W on FEHs +8 W in TDRs + 4 W in PSs = 19 W 5 Feb 2007 Waclaw Karpinski 26

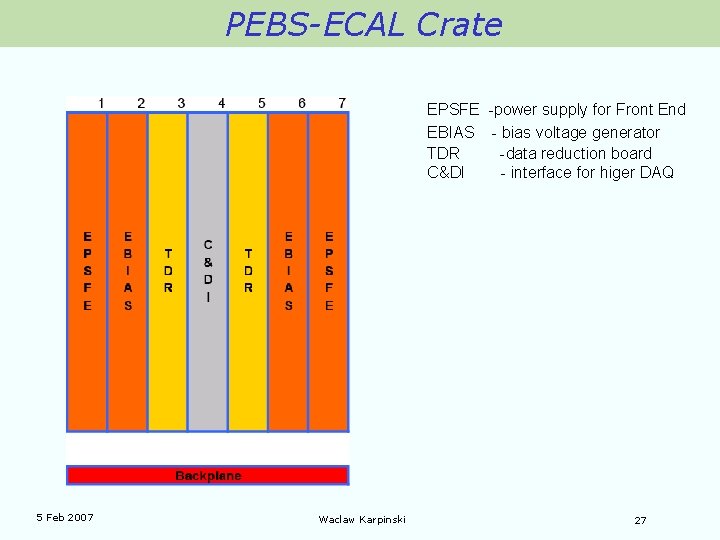

PEBS-ECAL Crate EPSFE -power supply for Front End EBIAS - bias voltage generator TDR -data reduction board C&DI - interface for higer DAQ 5 Feb 2007 Waclaw Karpinski 27

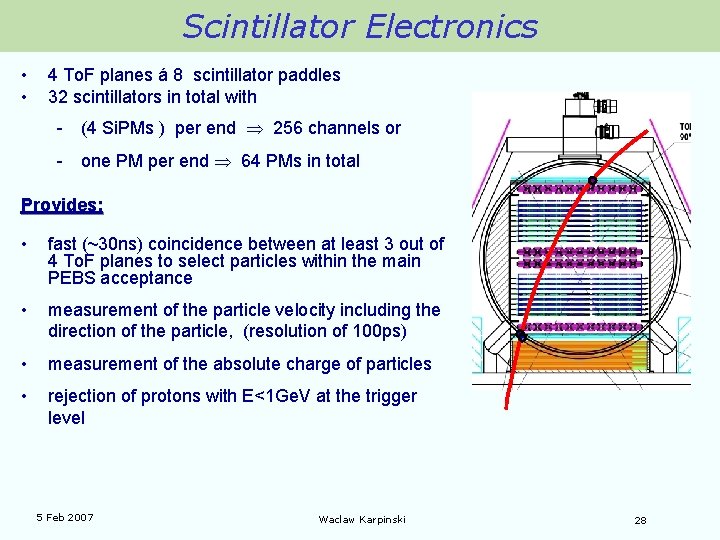

Scintillator Electronics • • 4 To. F planes á 8 scintillator paddles 32 scintillators in total with - (4 Si. PMs ) per end 256 channels or - one PM per end 64 PMs in total Provides: • fast (~30 ns) coincidence between at least 3 out of 4 To. F planes to select particles within the main PEBS acceptance • measurement of the particle velocity including the direction of the particle, (resolution of 100 ps) • measurement of the absolute charge of particles • rejection of protons with E<1 Ge. V at the trigger level 5 Feb 2007 Waclaw Karpinski 28

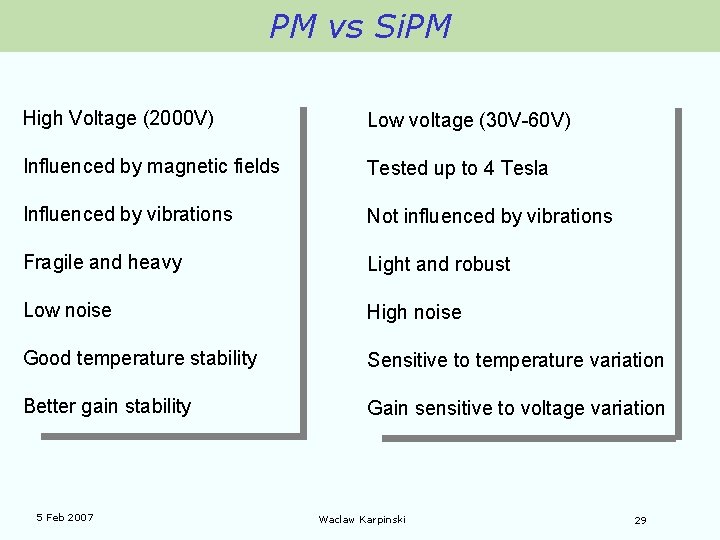

PM vs Si. PM High Voltage (2000 V) Low voltage (30 V-60 V) Influenced by magnetic fields Tested up to 4 Tesla Influenced by vibrations Not influenced by vibrations Fragile and heavy Light and robust Low noise High noise Good temperature stability Sensitive to temperature variation Better gain stability Gain sensitive to voltage variation 5 Feb 2007 Waclaw Karpinski 29

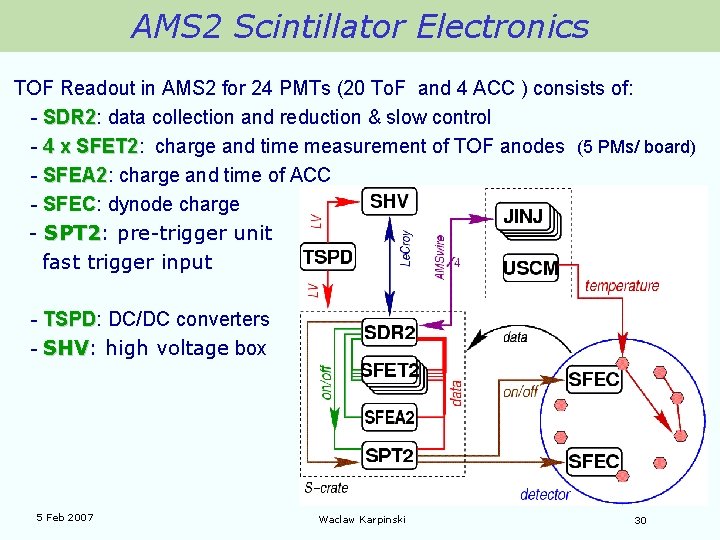

AMS 2 Scintillator Electronics TOF Readout in AMS 2 for 24 PMTs (20 To. F and 4 ACC ) consists of: - SDR 2: data collection and reduction & slow control SDR 2 - 4 x SFET 2: charge and time measurement of TOF anodes (5 PMs/ board) 4 x SFET 2 - SFEA 2: charge and time of ACC SFEA 2 - SFEC: dynode charge SFEC - SPT 2: SPT 2 pre-trigger unit fast trigger input - TSPD: DC/DC converters TSPD - SHV: SHV high voltage box 5 Feb 2007 Waclaw Karpinski 30

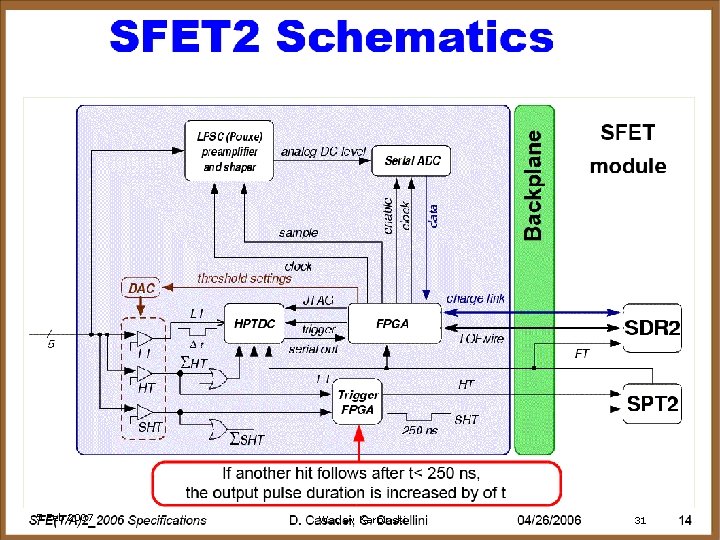

5 Feb 2007 Waclaw Karpinski 31

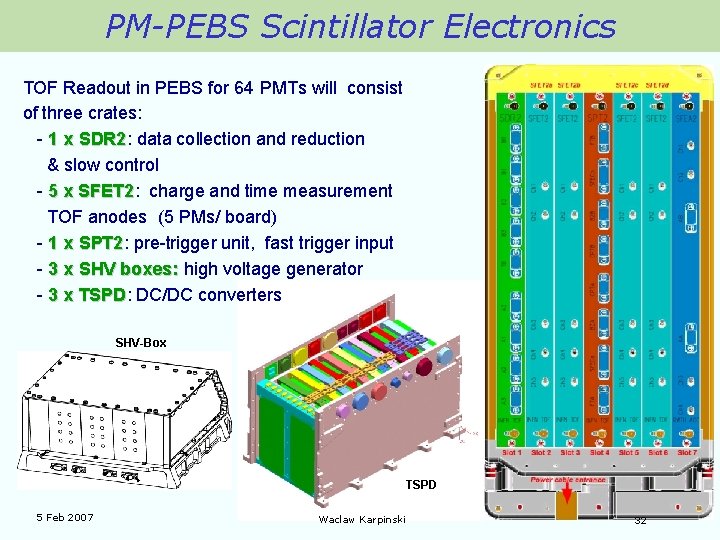

PM-PEBS Scintillator Electronics TOF Readout in PEBS for 64 PMTs will consist of three crates: - 1 x SDR 2: data collection and reduction SDR 2 & slow control - 5 x SFET 2: charge and time measurement 5 x SFET 2 TOF anodes (5 PMs/ board) - 1 x SPT 2: pre-trigger unit, fast trigger input SPT 2 - 3 x SHV boxes: high voltage generator SHV boxes: - 3 x TSPD: DC/DC converters TSPD SHV-Box TSPD 5 Feb 2007 Waclaw Karpinski 32

Potential ROCs for To. F with Si. Pms 5 Feb 2007 Waclaw Karpinski 33

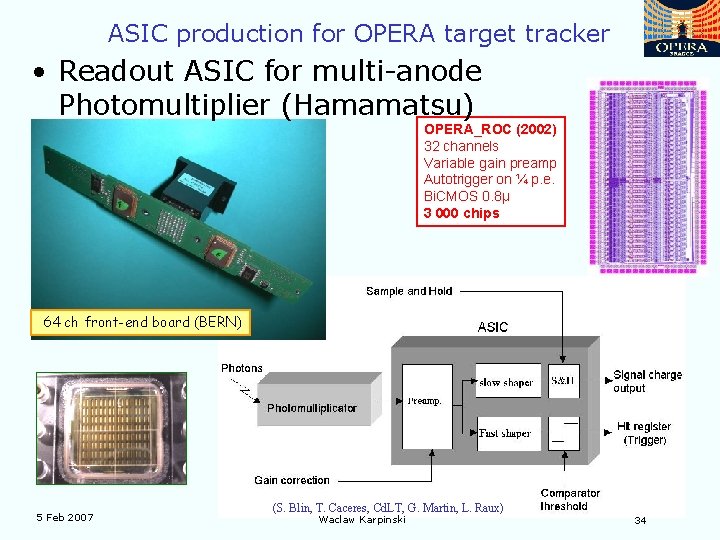

ASIC production for OPERA target tracker • Readout ASIC for multi-anode Photomultiplier (Hamamatsu) OPERA_ROC (2002) 32 channels Variable gain preamp Autotrigger on ¼ p. e. Bi. CMOS 0. 8µ 3 000 chips 64 ch front-end board (BERN) 5 Feb 2007 (S. Blin, T. Caceres, Cd. LT, G. Martin, L. Raux) Waclaw Karpinski 34

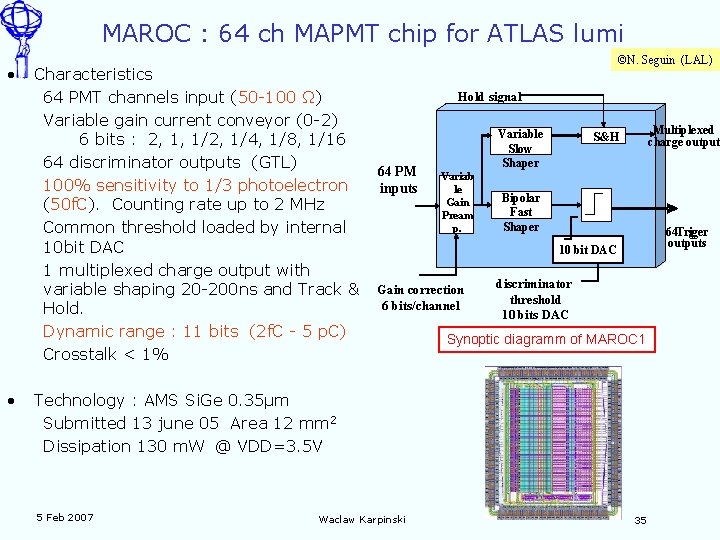

MAROC : 64 ch MAPMT chip for ATLAS lumi • • Characteristics 64 PMT channels input (50 -100 Ω) Variable gain current conveyor (0 -2) 6 bits : 2, 1, 1/2, 1/4, 1/8, 1/16 64 discriminator outputs (GTL) 100% sensitivity to 1/3 photoelectron (50 f. C). Counting rate up to 2 MHz Common threshold loaded by internal 10 bit DAC 1 multiplexed charge output with variable shaping 20 -200 ns and Track & Hold. Dynamic range : 11 bits (2 f. C - 5 p. C) Crosstalk < 1% ©N. Seguin (LAL) Hold signal 64 PM inputs Variable Slow Shaper Variab le Gain Pream p. Multiplexed charge output S&H Bipolar Fast Shaper 64 Trigger outputs 10 bit DAC Gain correction 6 bits/channel discriminator threshold 10 bits DAC Synoptic diagramm of MAROC 1 Technology : AMS Si. Ge 0. 35µm Submitted 13 june 05 Area 12 mm 2 Dissipation 130 m. W @ VDD=3. 5 V 5 Feb 2007 Waclaw Karpinski 35

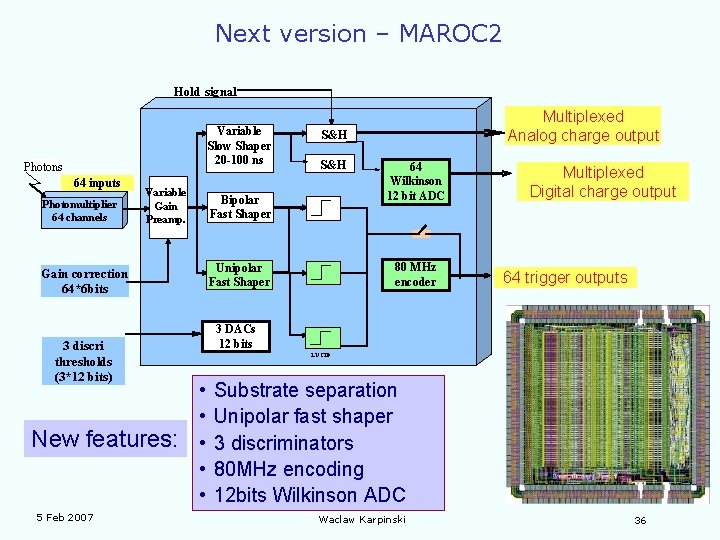

Next version – MAROC 2 Hold signal Variable Slow Shaper 20 -100 ns Photons 64 inputs Photomultiplier 64 channels Variable Gain Preamp. Gain correction 64*6 bits 3 discri thresholds (3*12 bits) • • New features: • • • 5 Feb 2007 Multiplexed Analog charge output S&H Bipolar Fast Shaper 64 Wilkinson 12 bit ADC 80 MHz encoder Unipolar Fast Shaper Multiplexed Digital charge output 64 trigger outputs 3 DACs 12 bits LUCID Substrate separation Unipolar fast shaper 3 discriminators 80 MHz encoding 12 bits Wilkinson ADC Waclaw Karpinski 36

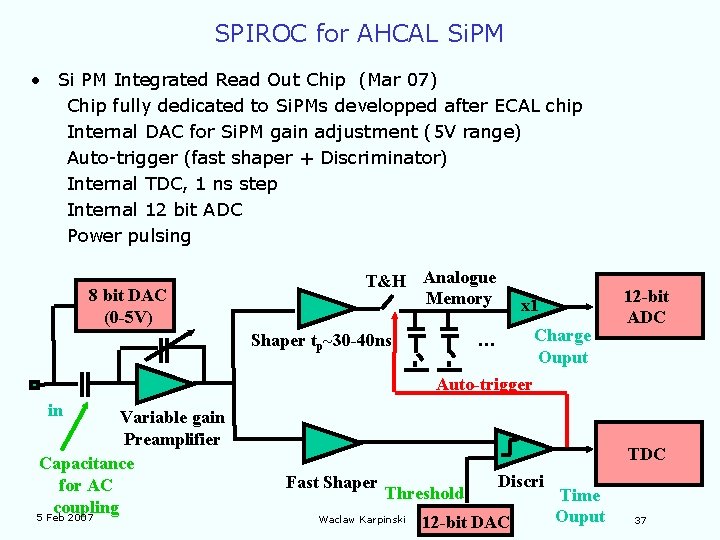

SPIROC for AHCAL Si. PM • Si PM Integrated Read Out Chip (Mar 07) Chip fully dedicated to Si. PMs developped after ECAL chip Internal DAC for Si. PM gain adjustment (5 V range) Auto-trigger (fast shaper + Discriminator) Internal TDC, 1 ns step Internal 12 bit ADC Power pulsing 8 bit DAC (0 -5 V) T&H Analogue Memory Shaper tp~30 -40 ns x 1 Charge Ouput … 12 -bit ADC Auto-trigger in Variable gain Preamplifier Capacitance for AC coupling 5 Feb 2007 TDC Fast Shaper Threshold Waclaw Karpinski Discri 12 -bit DAC Time Ouput 37

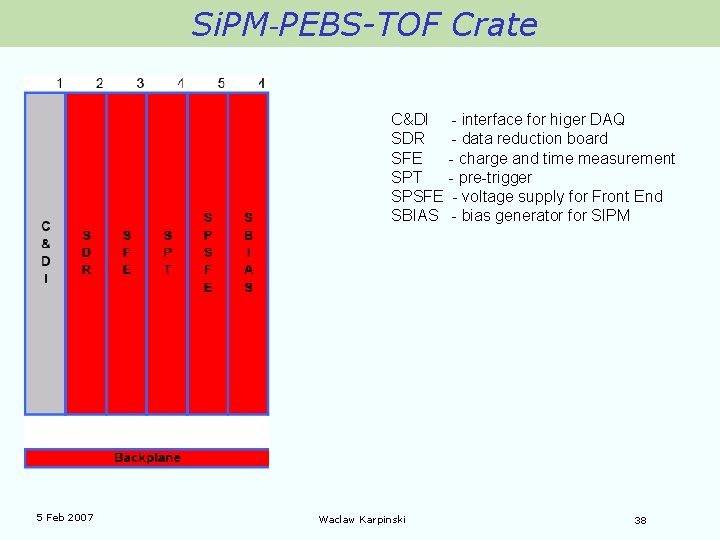

Si. PM-PEBS-TOF Crate C&DI - interface for higer DAQ SDR - data reduction board SFE - charge and time measurement SPT - pre-trigger SPSFE - voltage supply for Front End SBIAS - bias generator for SIPM 5 Feb 2007 Waclaw Karpinski 38

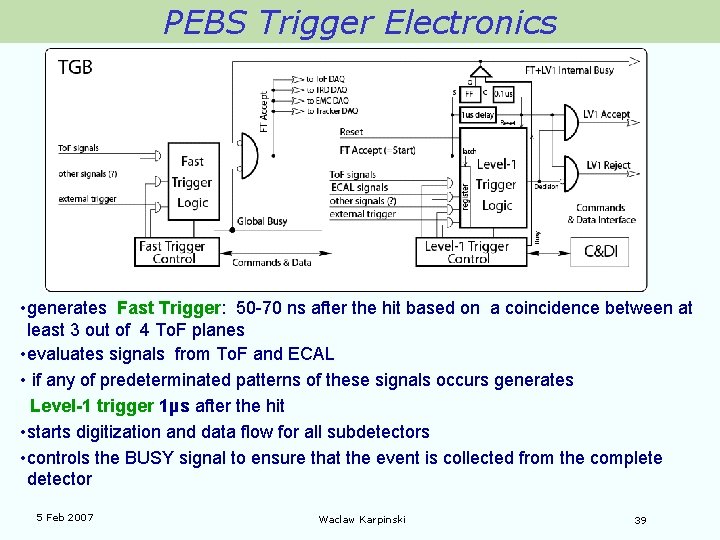

PEBS Trigger Electronics • generates Fast Trigger: 50 -70 ns after the hit based on a coincidence between at least 3 out of 4 To. F planes • evaluates signals from To. F and ECAL • if any of predeterminated patterns of these signals occurs generates Level-1 trigger 1µs after the hit • starts digitization and data flow for all subdetectors • controls the BUSY signal to ensure that the event is collected from the complete detector 5 Feb 2007 Waclaw Karpinski 39

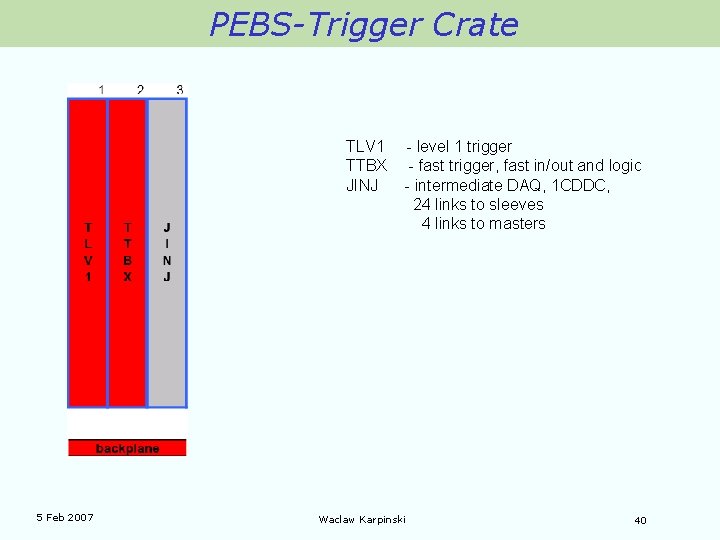

PEBS-Trigger Crate TLV 1 - level 1 trigger TTBX - fast trigger, fast in/out and logic JINJ - intermediate DAQ, 1 CDDC, 24 links to sleeves 4 links to masters 5 Feb 2007 Waclaw Karpinski 40

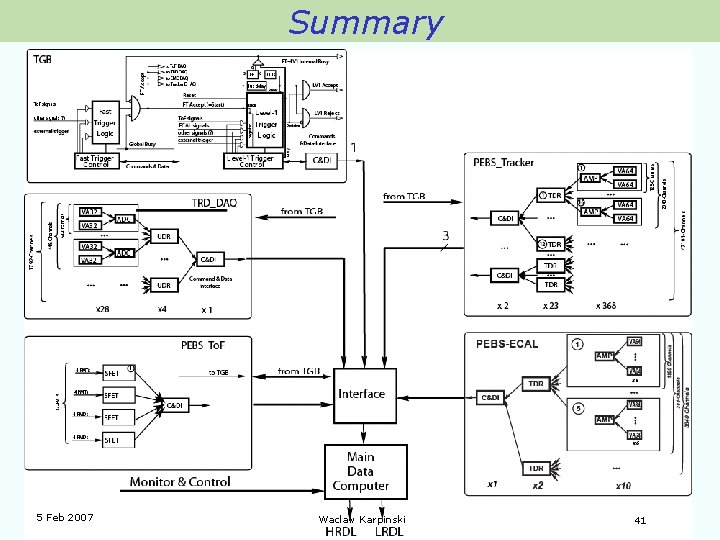

Summary 5 Feb 2007 Waclaw Karpinski 41

![Summary Power Consumption (To. F readout with PMs) Channels Power FE [W] Power DAQ Summary Power Consumption (To. F readout with PMs) Channels Power FE [W] Power DAQ](http://slidetodoc.com/presentation_image/4e52f507528f356ac1d248caafc50656/image-42.jpg)

Summary Power Consumption (To. F readout with PMs) Channels Power FE [W] Power DAQ [W] Power PS [W] Power Total [W] TRD 1792 7 13 11 31 Tracker 47104 94 94 47 236 ECAL 3800 8 8 4 19 64 11 68 32 112 Trigger 5 Slow Control 2 1 3 Main DAQ 45 PDS 60 Contingency 100 Subsystem TOF å» 5 Feb 2007 Waclaw Karpinski 610 42

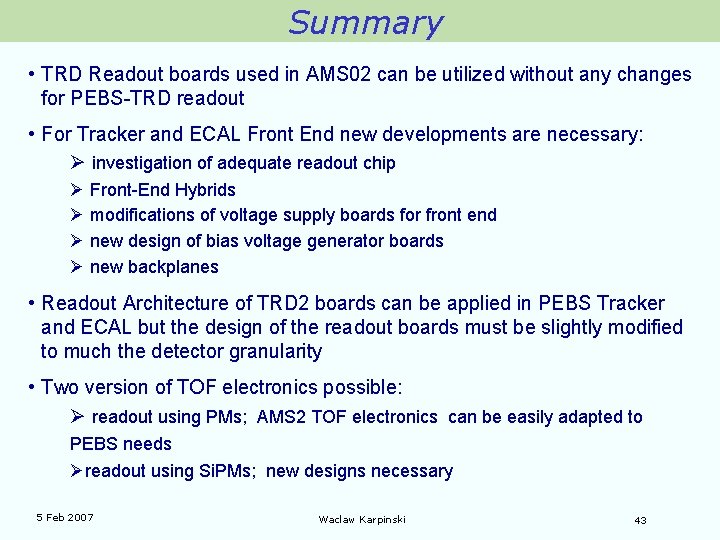

Summary • TRD Readout boards used in AMS 02 can be utilized without any changes for PEBS-TRD readout • For Tracker and ECAL Front End new developments are necessary: Ø investigation of adequate readout chip Ø Front-End Hybrids Ø modifications of voltage supply boards for front end Ø new design of bias voltage generator boards Ø new backplanes • Readout Architecture of TRD 2 boards can be applied in PEBS Tracker and ECAL but the design of the readout boards must be slightly modified to much the detector granularity • Two version of TOF electronics possible: Ø readout using PMs; AMS 2 TOF electronics can be easily adapted to PEBS needs Øreadout using Si. PMs; new designs necessary 5 Feb 2007 Waclaw Karpinski 43

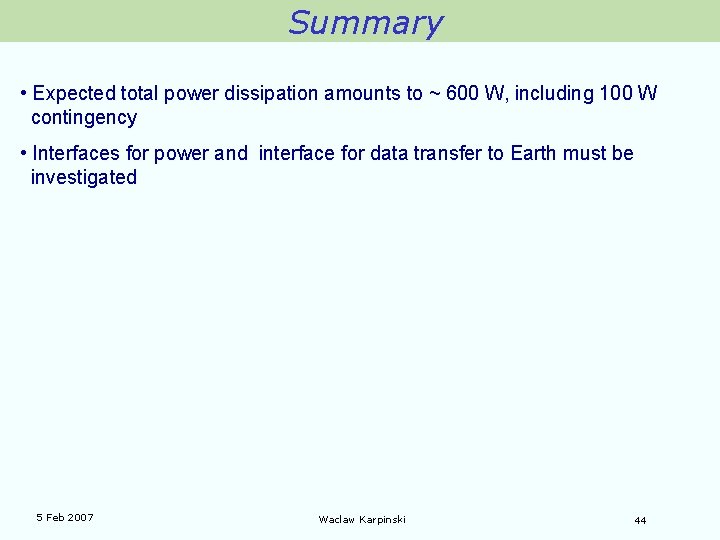

Summary • Expected total power dissipation amounts to ~ 600 W, including 100 W contingency • Interfaces for power and interface for data transfer to Earth must be investigated 5 Feb 2007 Waclaw Karpinski 44

- Slides: 44