PCIe 40 firmware development status GBT Design migration

PCIe 40 firmware development status • GBT • Design migration from Stratix V to Arria 10 • Complete Simulation of the firmware • Implemented it in PCIe 40 • Latency Measurement • Making of GBT QSYS wrapper • Did board to board testing of GBT protocol between Stratix V and Arria 10 • TO DO: • Do test with GBT chip • PCIe • Gen 2 x 8 +Gen 2 x 8 test for 16 lane connectivity • Basic read write test on BAR • 12 channel Transceiver tool kit design is made to test board to board communication between Stratix V and Arria 10 • For power estimation of CRU a low level interface is made : • 48 GBT link + x 16 PCIe Gen 3 + SFP+(Transceiver Toolkit design) 1 st July, 2015 Presented by Jubin MITRA 1

For Resource estimation of complexity challenge • For power and resource estimation of CRU a low level interface is made : • 48 GBT link + x 16 PCIe Gen 3 + SFP+(Transceiver Toolkit design) • It is composed of total 65 High speed links each attached with its dedicated pattern generator and pattern checker • The entire design is integrated in QSYS tool • In this design it is assumed to operate PCIe 40 in extended configuration • No user or glue logic is taken into account in this preliminary resource estimation Presented by Jubin MITRA

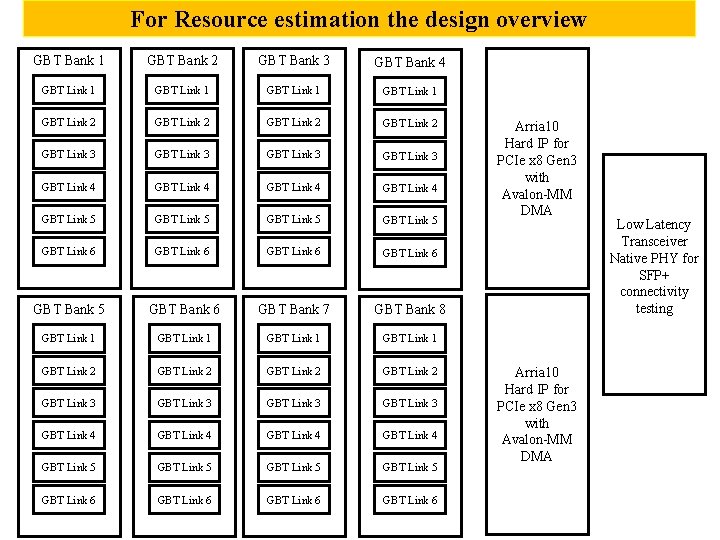

For Resource estimation the design overview GBT Bank 1 GBT Bank 2 GBT Bank 3 GBT Bank 4 GBT Link 1 GBT Link 2 GBT Link 3 GBT Link 4 GBT Link 5 GBT Link 6 GBT Bank 5 GBT Bank 6 GBT Bank 7 GBT Bank 8 GBT Link 1 GBT Link 2 GBT Link 3 GBT Link 4 GBT Link 5 GBT Link 6 Arria 10 Hard IP for PCIe x 8 Gen 3 with Avalon-MM DMA Low Latency Transceiver Native PHY for SFP+ connectivity testing

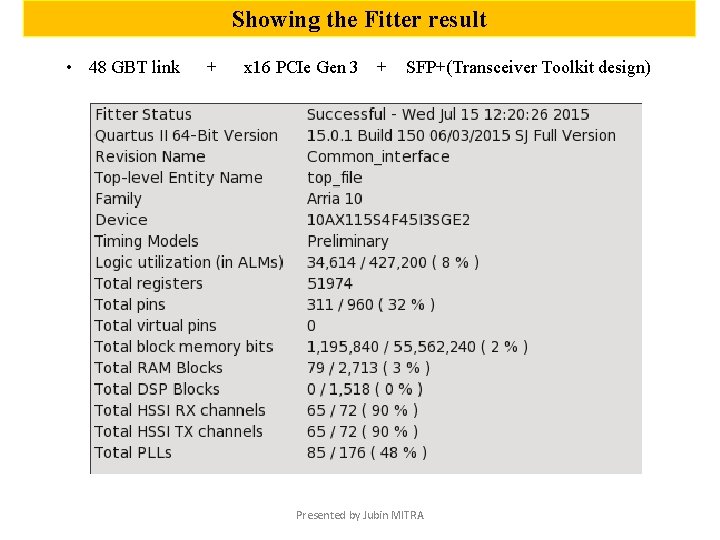

Showing the Fitter result • 48 GBT link + x 16 PCIe Gen 3 + SFP+(Transceiver Toolkit design) Presented by Jubin MITRA

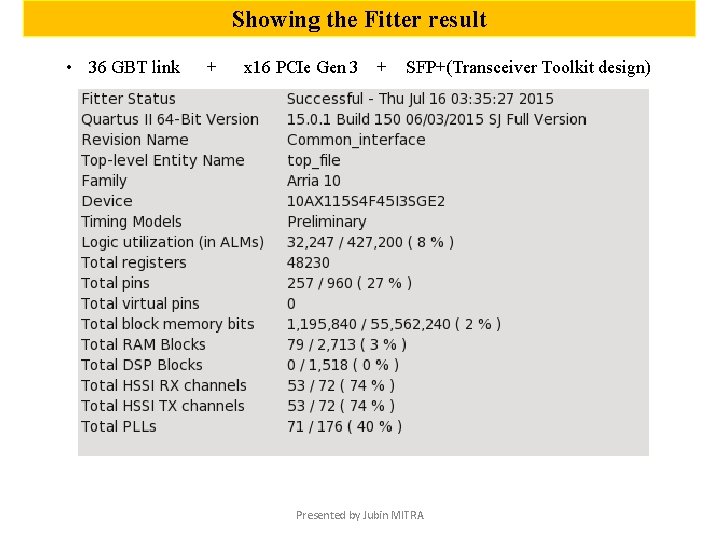

Showing the Fitter result • 36 GBT link + x 16 PCIe Gen 3 + SFP+(Transceiver Toolkit design) Presented by Jubin MITRA

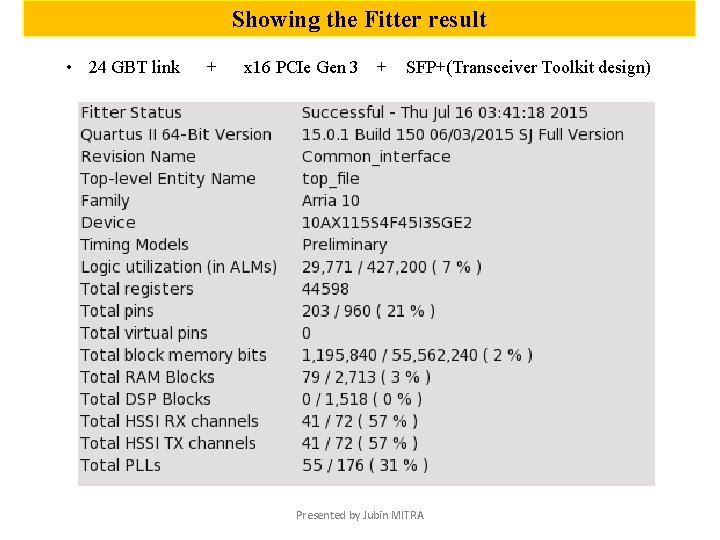

Showing the Fitter result • 24 GBT link + x 16 PCIe Gen 3 + SFP+(Transceiver Toolkit design) Presented by Jubin MITRA

- Slides: 6