PCI Express Design with Altera Transceiver Devices 2010

- Slides: 32

PCI Express Design with Altera Transceiver Devices 2010 Technology Roadshow © 2010 Altera Corporation—Public

Agenda n n PCI® and PCI Express® overview Introduction to Altera transceiver devices Design with PCI Express HIP Design resources © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 2

Introduction of PCI and PCI Express n PCI/PCIe has a significant ecosystem available in the market today! - Many different devices spanning a large number of various functionalities - Large investment made in drivers and other software - PCI Express (PCIe) completely leverages the software model developed for PCI n n PCI/PCIe is a defacto standard on PCs, servers, workstations, Blade, and embedded processors PCI/PCIe is replacing proprietary bus architectures found in older embedded designs: - Chip-to-chip interconnects - Control backplane busses - Embedded system busses © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 3

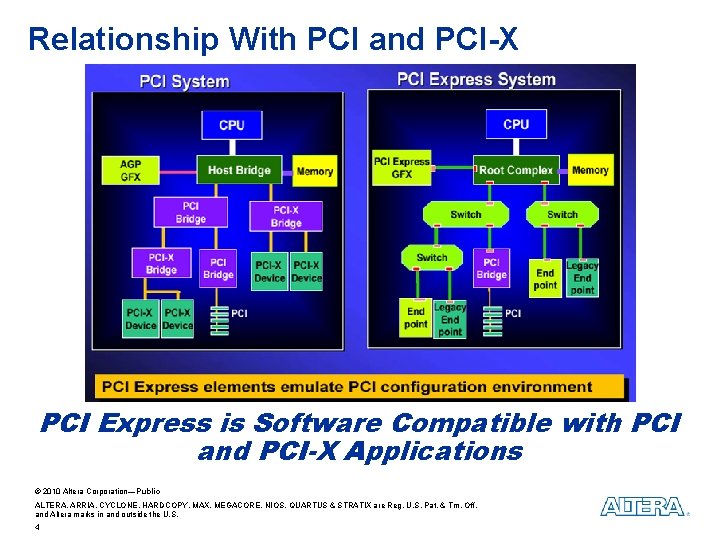

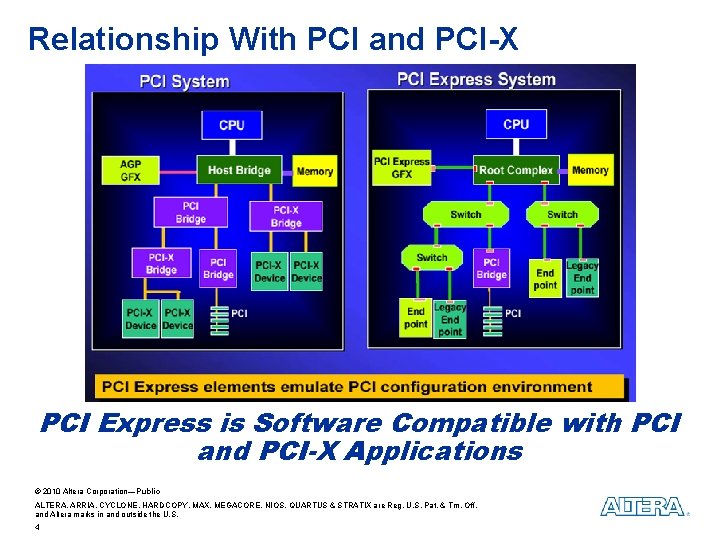

Relationship With PCI and PCI-X PCI Express is Software Compatible with PCI and PCI-X Applications © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 4

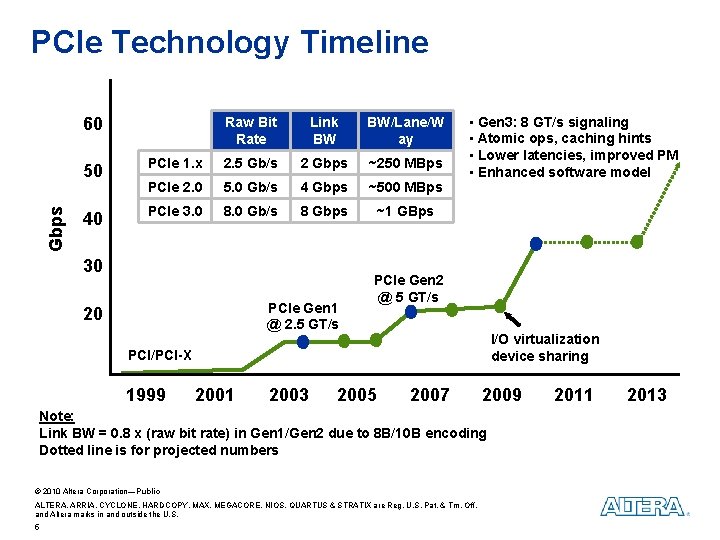

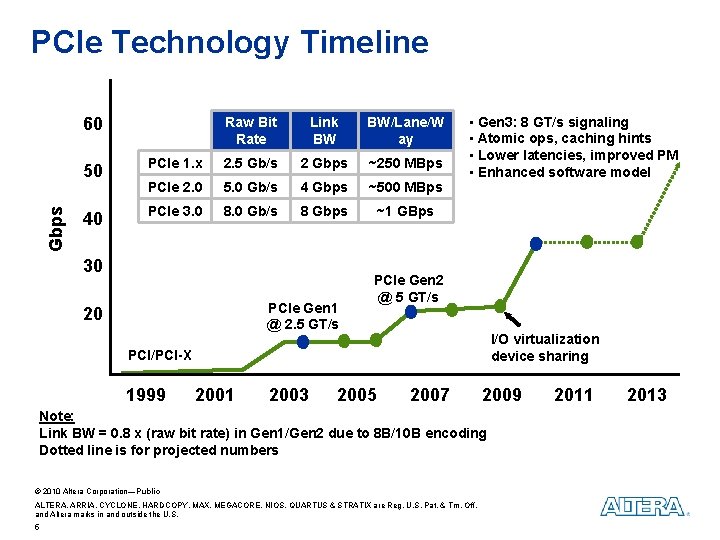

PCIe Technology Timeline Gbps 60 Raw Bit Rate Link BW BW/Lane/W ay 50 PCIe 1. x 2. 5 Gb/s 2 Gbps ~250 MBps PCIe 2. 0 5. 0 Gb/s 4 Gbps ~500 MBps 40 PCIe 3. 0 8. 0 Gb/s 8 Gbps ~1 GBps 30 PCIe Gen 1 @ 2. 5 GT/s 20 • Gen 3: 8 GT/s signaling • Atomic ops, caching hints • Lower latencies, improved PM • Enhanced software model PCIe Gen 2 @ 5 GT/s I/O virtualization device sharing PCI/PCI-X 1999 2001 2003 2005 2007 2009 Note: Link BW = 0. 8 x (raw bit rate) in Gen 1/Gen 2 due to 8 B/10 B encoding Dotted line is for projected numbers © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 5 2011 2013

Transceiver Devices Supporting PCI Express n FPGA families - Cyclone IV GX FPGAs - Arria II GX FPGAs - Stratix IV GX/GT FPGAs - Stratix V GS/GX/GT FPGAs n ASIC families - Hard. Copy IV GX devices © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 6

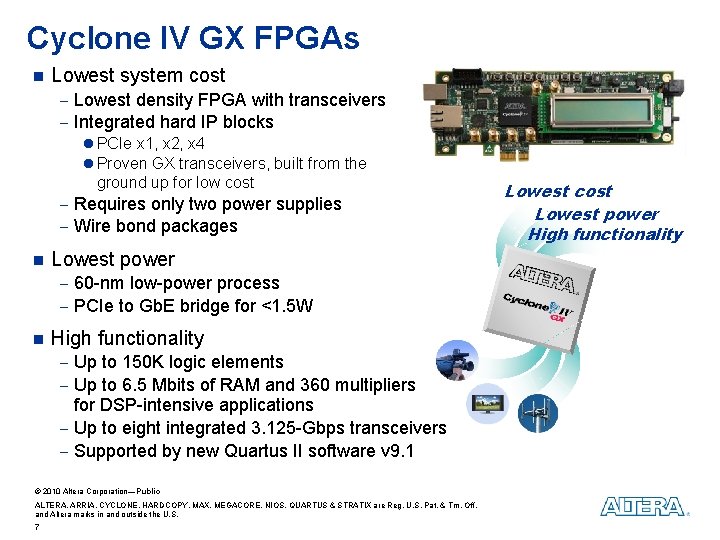

Cyclone IV GX FPGAs n Lowest system cost - Lowest density FPGA with transceivers - Integrated hard IP blocks l PCIe x 1, x 2, x 4 l Proven GX transceivers, built from the ground up for low cost - Requires only two power supplies - Wire bond packages n Lowest power - 60 -nm low-power process - PCIe to Gb. E bridge for <1. 5 W n High functionality - Up to 150 K logic elements - Up to 6. 5 Mbits of RAM and 360 multipliers for DSP-intensive applications - Up to eight integrated 3. 125 -Gbps transceivers - Supported by new Quartus II software v 9. 1 © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 7 Lowest cost Lowest power High functionality

Arria II FPGAs n High functionality - High-performance ALM-based fabric - High density—up to 350 K LEs - Up to 24 transceivers at 6. 375 Gbps - Up to 16. 4 Mb of memory - Highest ratio of DSP-to-logic resources in its class n Low power - Up to 50% lower power than competing high- end FPGAs n Design with ease - Built-in PCI Express hard IP - Single design environment - Jump-start design with protocol IP packs, reference designs, and development kits © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 8

Stratix IV GX/GT FPGAs n n 1 st transceiver variant of Stratix IV family Highest density - n Highest bandwidth and performance - n Up to 530 K logic elements (LEs) Up to 20. 3 Mb internal RAM Up to 1, 288 18 x 18 multipliers Up to 32 full-duplex transceivers operating at up to 8. 5/11. 3 Gbps Up to 16 PMA-only transceivers operating up to 6. 5 Gbps Up to 4 x 8 hard intellectual property (IP) blocks for PCI Express Gen 1 and Gen 2 Over 700 million multiply-accumulate operations per second (GMACS) performance (for DSP) Lowest power - Programmable Power Technology Quartus® II Power. Play technology 40 -nm process benefits, including 0. 9 V core voltage © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 9

Stratix V FPGAs—Built for Bandwidth n Highest bandwidth - 66 transceivers capable of 12. 5 Gbps and 6 x 72 800 -MHz DDR 3 interfaces - Devices with 28 -Gbps transceivers n Highest Bandwidth Hard IP and Flexibility IP Solutions and Ecosystem Unprecedented level of integration - Embedded Hard. Copy blocks supporting PCI Express Gen 3 and 40 G/100 G Ethernet - High-performance, high-precision DSP - Enhanced logic fabric with 1, 100 K LEs, 50 Mb RAM, and 3, 510 18 x 18 multipliers n Ultimate flexibility - Fine-grained, easy-to-use partial reconfiguration - Configuration via PCI Express n 50% higher system performance and 30% lower power © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 10 IP

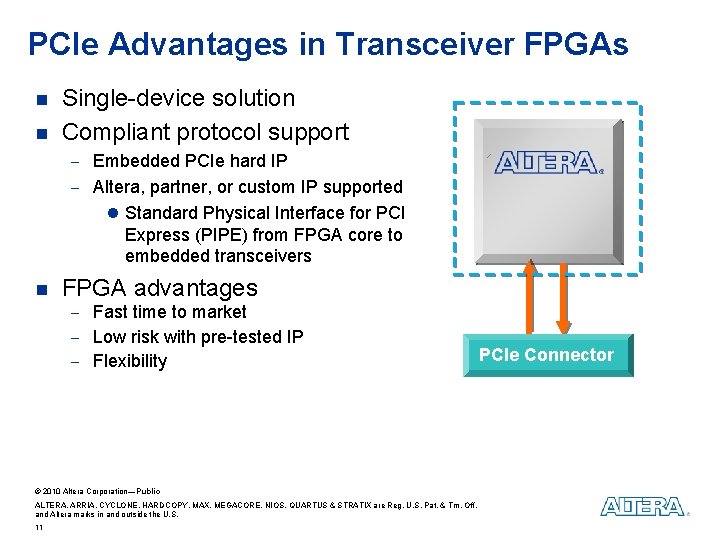

PCIe Advantages in Transceiver FPGAs n n Single-device solution Compliant protocol support - Embedded PCIe hard IP - Altera, partner, or custom IP supported l Standard Physical Interface for PCI Express (PIPE) from FPGA core to embedded transceivers n FPGA advantages - Fast time to market - Low risk with pre-tested IP - Flexibility © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 11 PCIe Connector

PCIe Hard IP Implementation Advantages n Cost - $0 list price - Resources l ~Zero LEs used l Zero core memory blocks used n Ease of use - No licensing or special ordering code - Significantly reduced compile times - Lower power than comparable soft IP solutions n Low risk - Pre-verified PCI Express base rev 1. 1 - or 2. 0 -compliant core - Fully tested l Tested with industry-standard BFMs l Functional coverage with directed and random tests l PCI-SIG compliance hardware-tested with internal and external PHYs © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 12

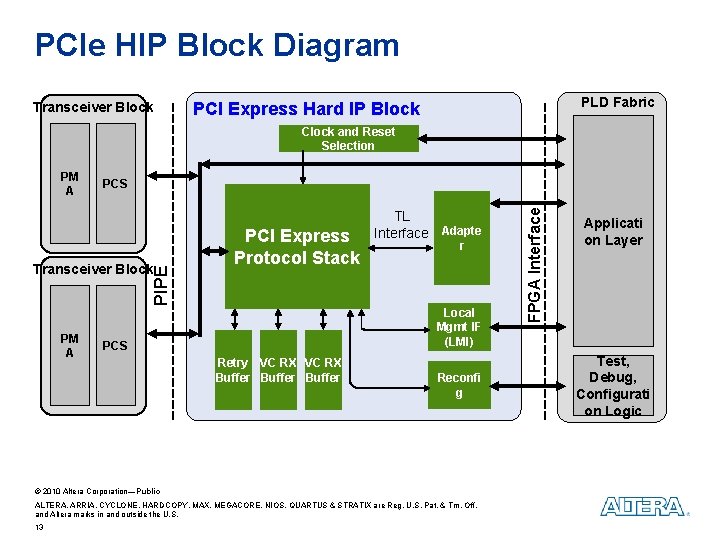

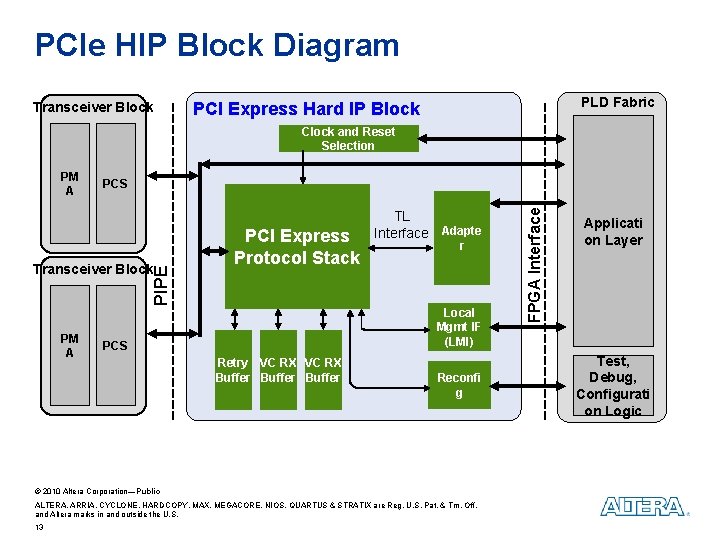

PCIe HIP Block Diagram Transceiver Block PLD Fabric PCI Express Hard IP Block Clock and Reset Selection PCS PIPE Transceiver Block PM A PCI Express Protocol Stack TL Interface Adapte r Local Mgmt IF (LMI) PCS Retry VC RX Buffer Reconfi g © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 13 FPGA Interface PM A Applicati on Layer Test, Debug, Configurati on Logic

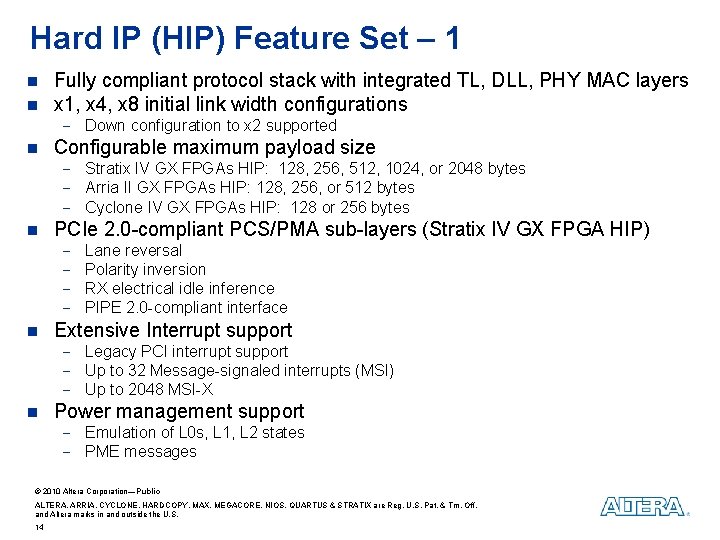

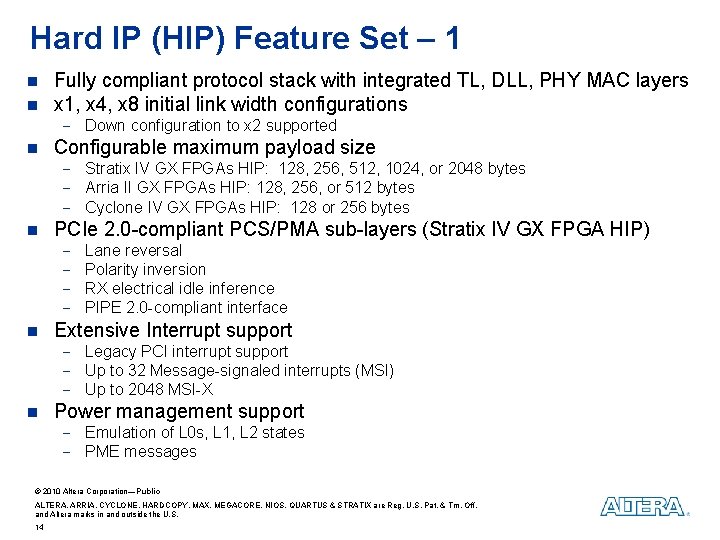

Hard IP (HIP) Feature Set – 1 n n Fully compliant protocol stack with integrated TL, DLL, PHY MAC layers x 1, x 4, x 8 initial link width configurations - Down configuration to x 2 supported n Configurable maximum payload size - Stratix IV GX FPGAs HIP: 128, 256, 512, 1024, or 2048 bytes - Arria II GX FPGAs HIP: 128, 256, or 512 bytes - Cyclone IV GX FPGAs HIP: 128 or 256 bytes n PCIe 2. 0 -compliant PCS/PMA sub-layers (Stratix IV GX FPGA HIP) - n Lane reversal Polarity inversion RX electrical idle inference PIPE 2. 0 -compliant interface Extensive Interrupt support - Legacy PCI interrupt support - Up to 32 Message-signaled interrupts (MSI) - Up to 2048 MSI-X n Power management support - Emulation of L 0 s, L 1, L 2 states - PME messages © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 14

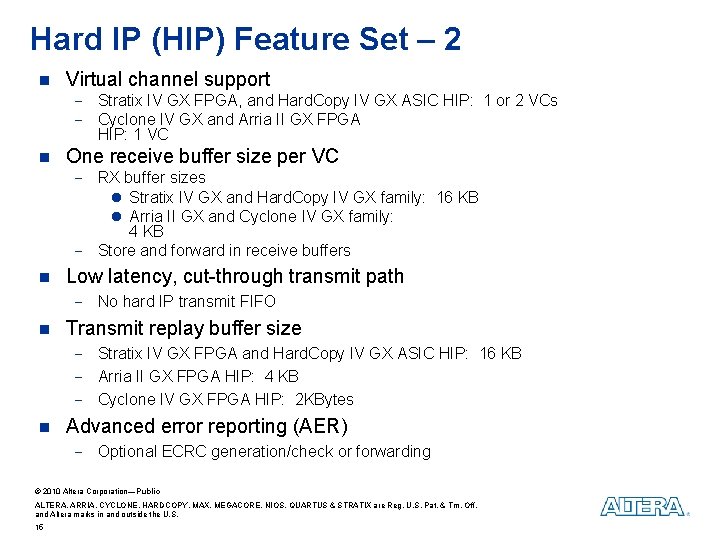

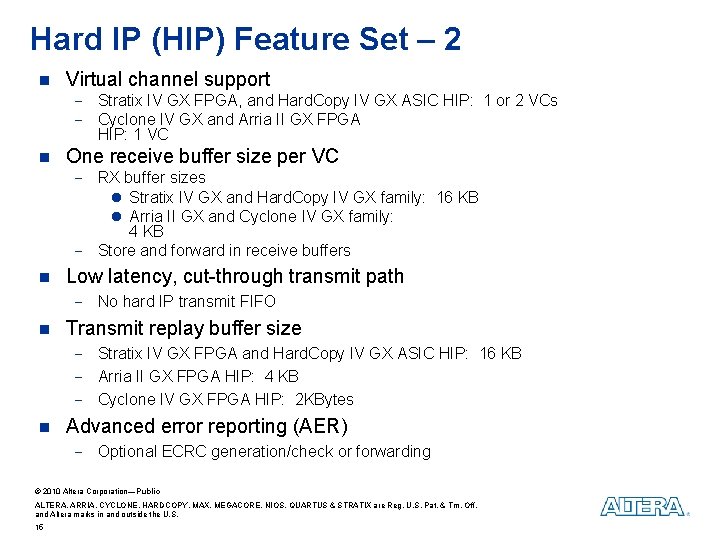

Hard IP (HIP) Feature Set – 2 n Virtual channel support - Stratix IV GX FPGA, and Hard. Copy IV GX ASIC HIP: 1 or 2 VCs - Cyclone IV GX and Arria II GX FPGA HIP: 1 VC n One receive buffer size per VC - RX buffer sizes l Stratix IV GX and Hard. Copy IV GX family: 16 KB l Arria II GX and Cyclone IV GX family: 4 KB - Store and forward in receive buffers n Low latency, cut-through transmit path - No hard IP transmit FIFO n Transmit replay buffer size - Stratix IV GX FPGA and Hard. Copy IV GX ASIC HIP: 16 KB - Arria II GX FPGA HIP: 4 KB - Cyclone IV GX FPGA HIP: 2 KBytes n Advanced error reporting (AER) - Optional ECRC generation/check or forwarding © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 15

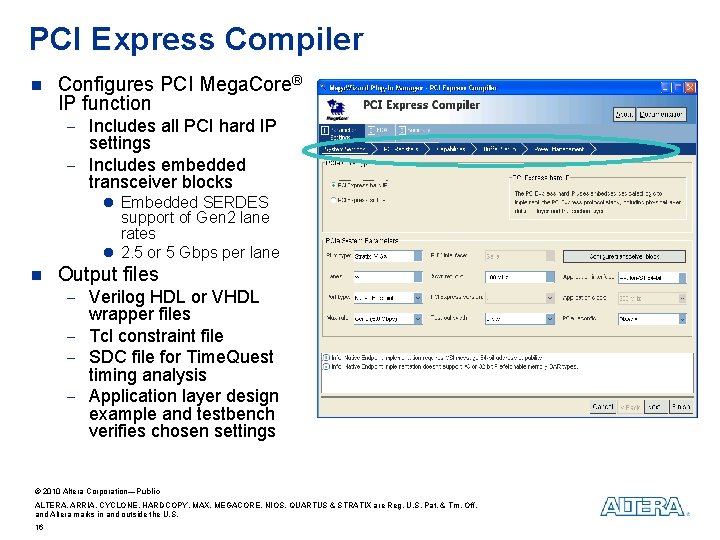

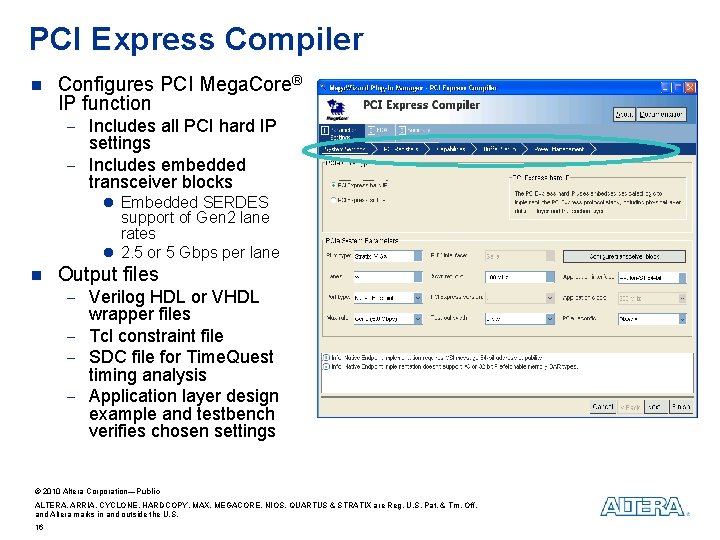

PCI Express Compiler n Configures PCI Mega. Core® IP function - Includes all PCI hard IP settings - Includes embedded transceiver blocks l Embedded SERDES support of Gen 2 lane rates l 2. 5 or 5 Gbps per lane n Output files - Verilog HDL or VHDL wrapper files - Tcl constraint file - SDC file for Time. Quest timing analysis - Application layer design example and testbench verifies chosen settings © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 16

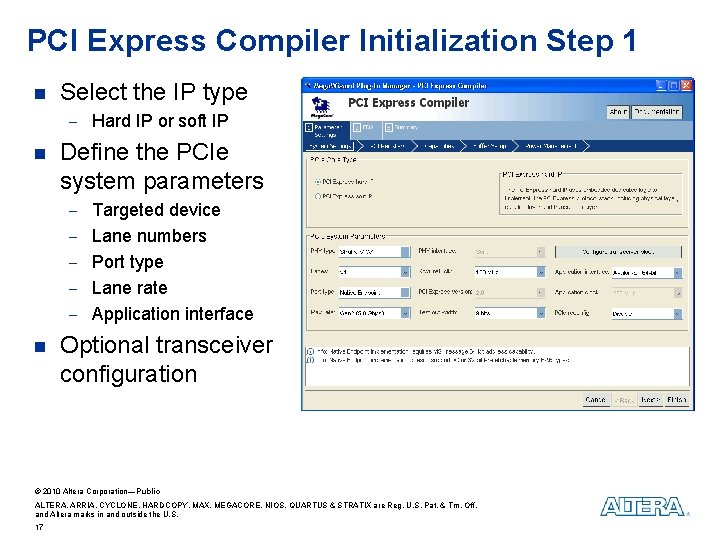

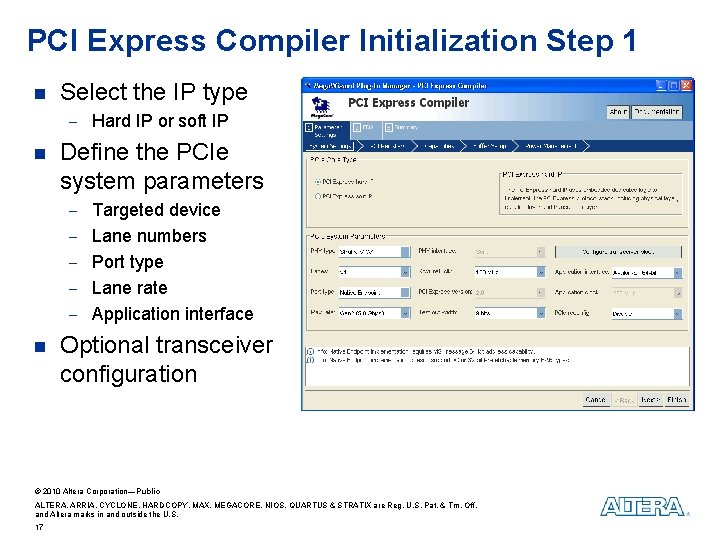

PCI Express Compiler Initialization Step 1 n Select the IP type - Hard IP or soft IP n Define the PCIe system parameters - Targeted device - Lane numbers - Port type - Lane rate - Application interface n Optional transceiver configuration © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 17

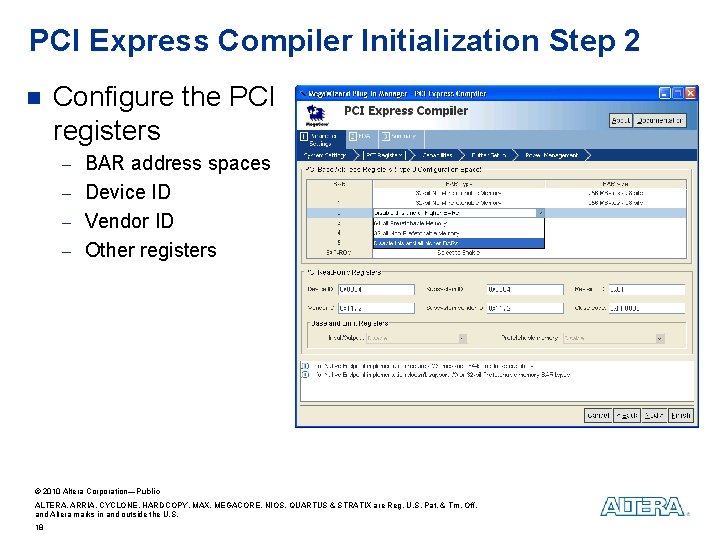

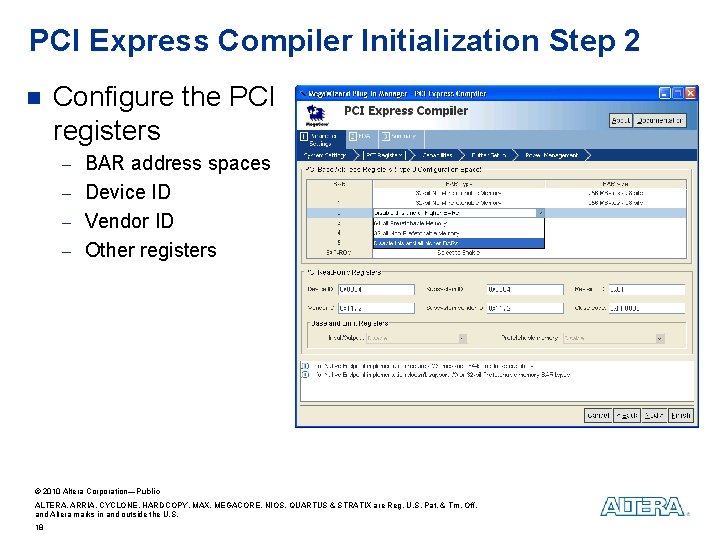

PCI Express Compiler Initialization Step 2 n Configure the PCI registers - BAR address spaces - Device ID - Vendor ID - Other registers © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 18

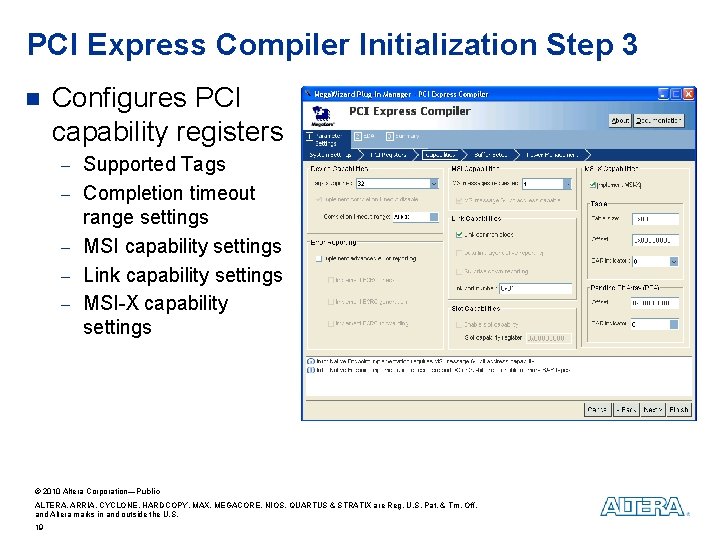

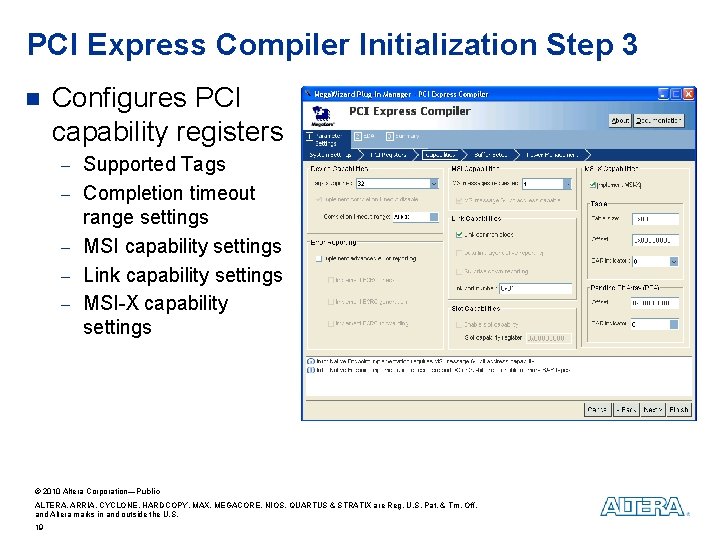

PCI Express Compiler Initialization Step 3 n Configures PCI capability registers - Supported Tags - Completion timeout range settings - MSI capability settings - Link capability settings - MSI-X capability settings © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 19

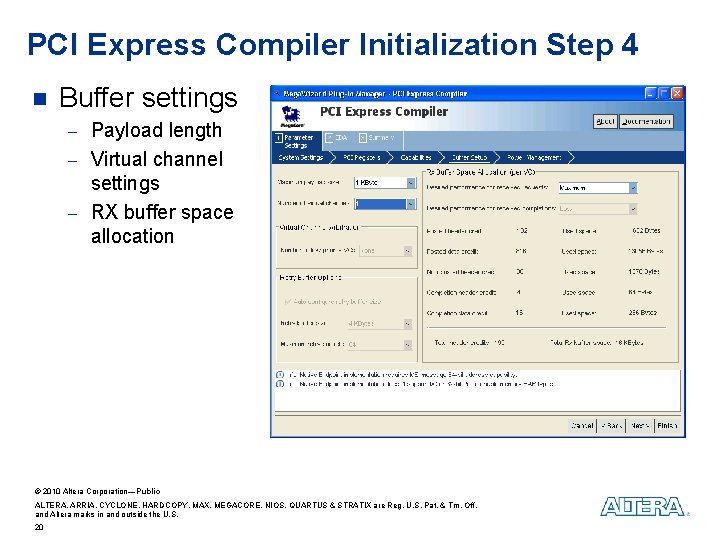

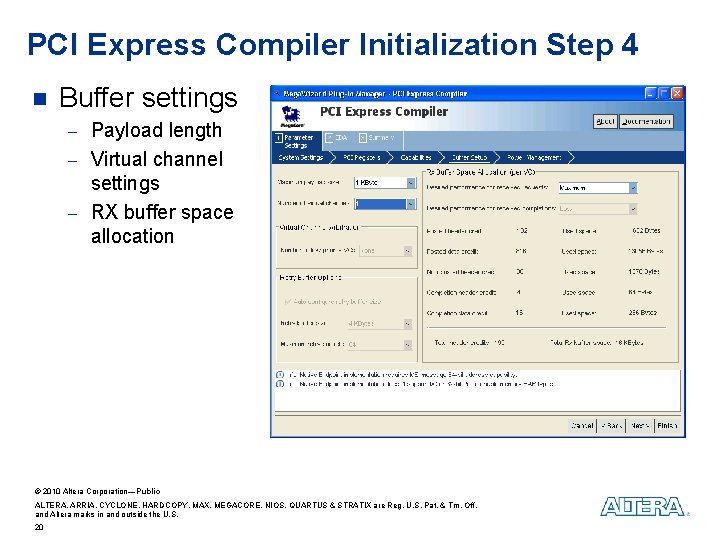

PCI Express Compiler Initialization Step 4 n Buffer settings - Payload length - Virtual channel settings - RX buffer space allocation © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 20

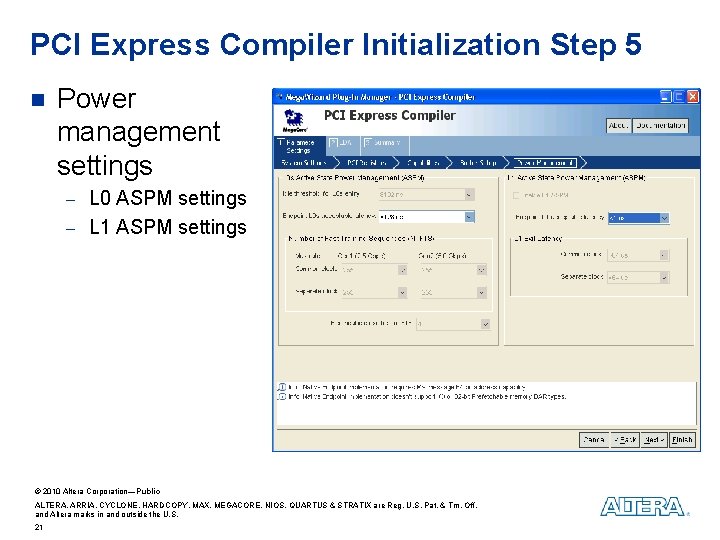

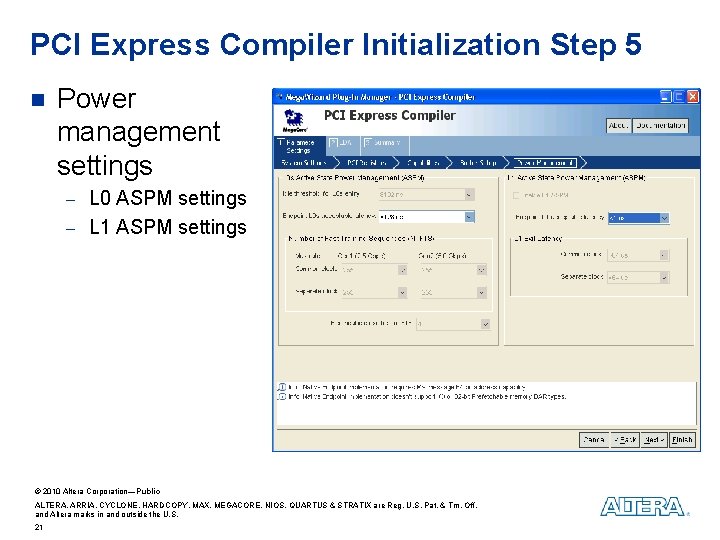

PCI Express Compiler Initialization Step 5 n Power management settings - L 0 ASPM settings - L 1 ASPM settings © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 21

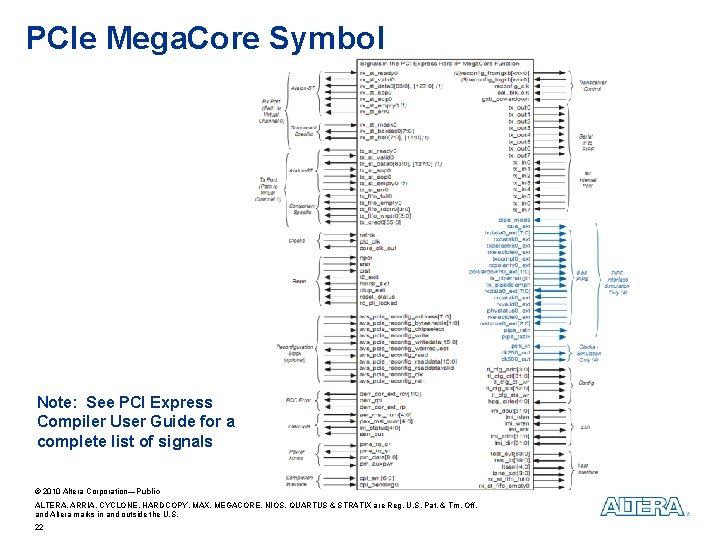

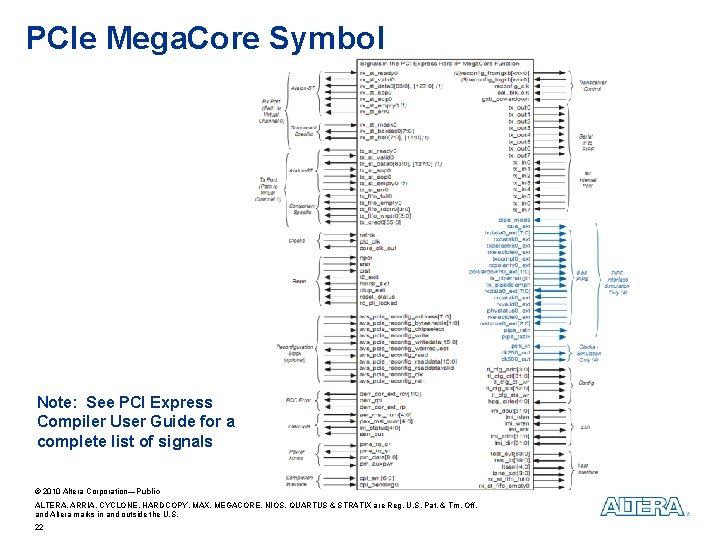

PCIe Mega. Core Symbol Note: See PCI Express Compiler User Guide for a complete list of signals © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 22

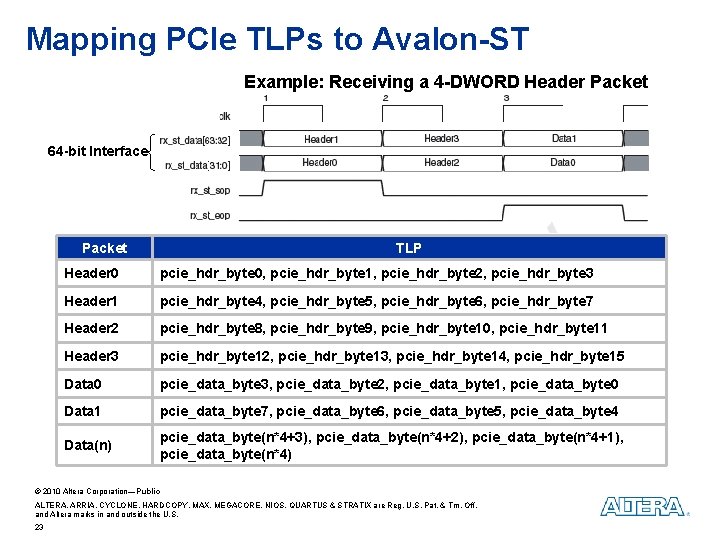

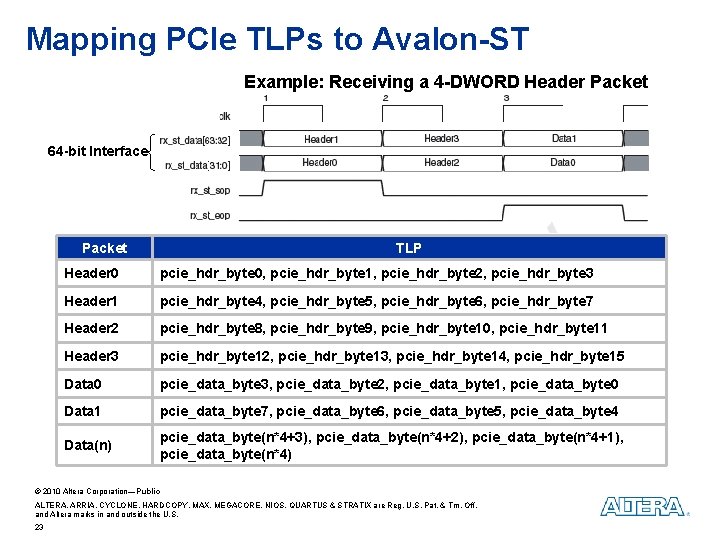

Mapping PCIe TLPs to Avalon-ST Example: Receiving a 4 -DWORD Header Packet 64 -bit Interface Packet TLP Header 0 pcie_hdr_byte 0, pcie_hdr_byte 1, pcie_hdr_byte 2, pcie_hdr_byte 3 Header 1 pcie_hdr_byte 4, pcie_hdr_byte 5, pcie_hdr_byte 6, pcie_hdr_byte 7 Header 2 pcie_hdr_byte 8, pcie_hdr_byte 9, pcie_hdr_byte 10, pcie_hdr_byte 11 Header 3 pcie_hdr_byte 12, pcie_hdr_byte 13, pcie_hdr_byte 14, pcie_hdr_byte 15 Data 0 pcie_data_byte 3, pcie_data_byte 2, pcie_data_byte 1, pcie_data_byte 0 Data 1 pcie_data_byte 7, pcie_data_byte 6, pcie_data_byte 5, pcie_data_byte 4 Data(n) pcie_data_byte(n*4+3), pcie_data_byte(n*4+2), pcie_data_byte(n*4+1), pcie_data_byte(n*4) © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 23

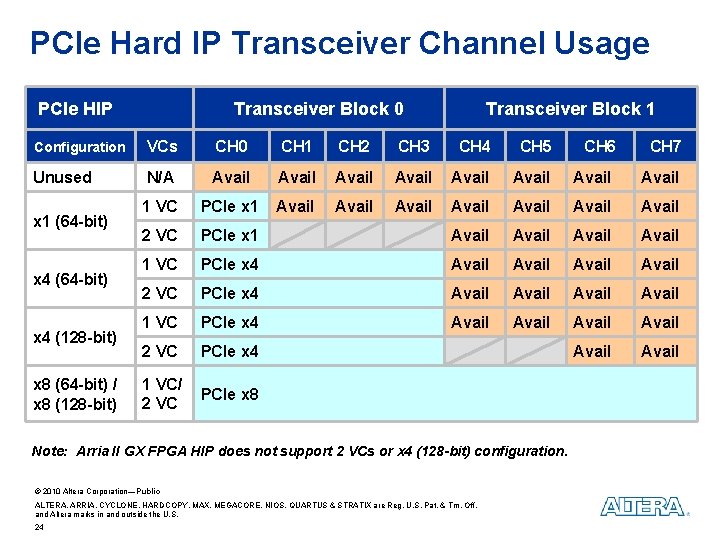

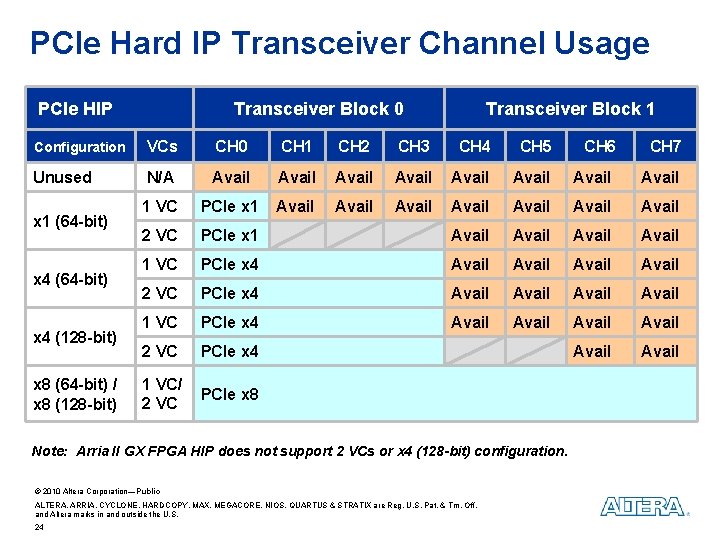

PCIe Hard IP Transceiver Channel Usage PCIe HIP Transceiver Block 0 Transceiver Block 1 Configuration VCs CH 0 CH 1 CH 2 CH 3 CH 4 CH 5 CH 6 CH 7 Unused N/A Avail Avail 1 VC PCIe x 1 Avail Avail 2 VC PCIe x 1 Avail Avail 1 VC PCIe x 4 Avail Avail 2 VC PCIe x 4 Avail 1 VC/ 2 VC PCIe x 8 x 1 (64 -bit) x 4 (128 -bit) x 8 (64 -bit) / x 8 (128 -bit) Note: Arria II GX FPGA HIP does not support 2 VCs or x 4 (128 -bit) configuration. © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 24

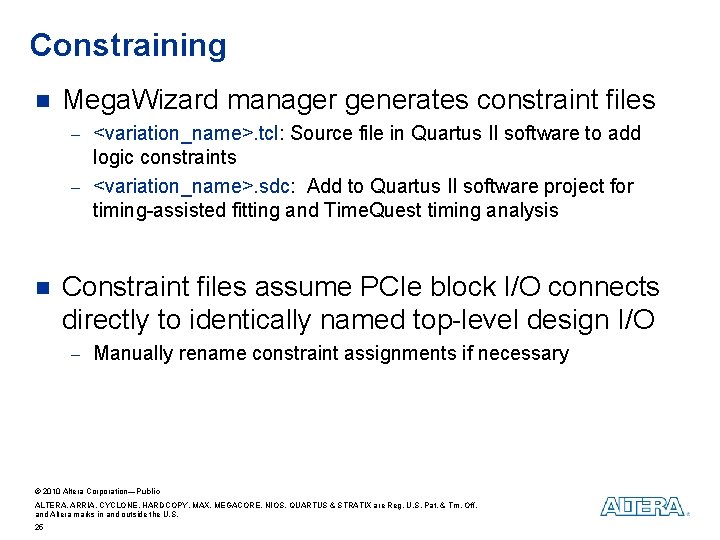

Constraining n Mega. Wizard manager generates constraint files - <variation_name>. tcl: Source file in Quartus II software to add logic constraints - <variation_name>. sdc: Add to Quartus II software project for timing-assisted fitting and Time. Quest timing analysis n Constraint files assume PCIe block I/O connects directly to identically named top-level design I/O - Manually rename constraint assignments if necessary © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 25

Design Examples and Simulation Models n Fully functioning application-layer design examples - Endpoint design example and testbench - Root port design example and testbench n Mega. Core IP functional simulation model - Option to generate in Verilog or VHDL during Mega. Wizard configuration - Requires Altera simulation model libraries l General: altera_mf, 220 model and sgate l Device specific - Stratix IV devices: straixiv_hssi, stratixiv_pcie_hip - Arria II GX devices: arriaii_hssi, arriaii_pcie_hip - Hard. Copy IV devices: hardcopyiv_hssi, hardcopyiv_pcie_hip - Cyclone IV devices: cycloneiv_hssi, cycloneiv_pcie_hip l See Quartus II Handbook chapter “Simulating Altera IP in Third-Party Simulation Tools” for more details on setting up and using Altera libraries © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 26

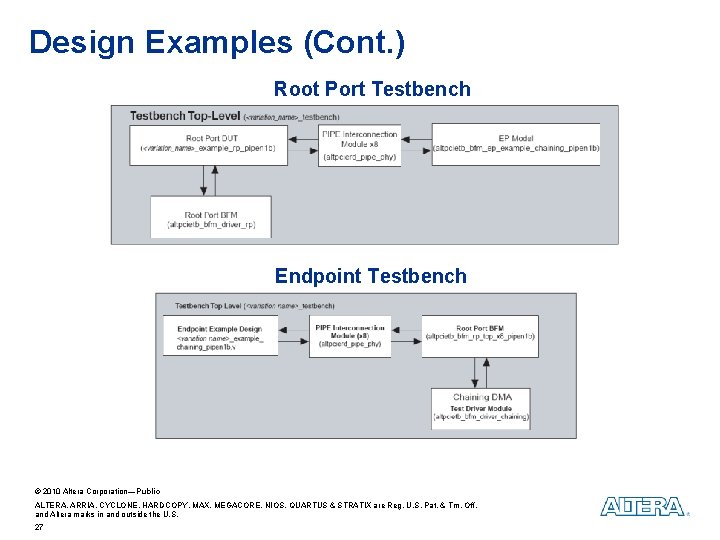

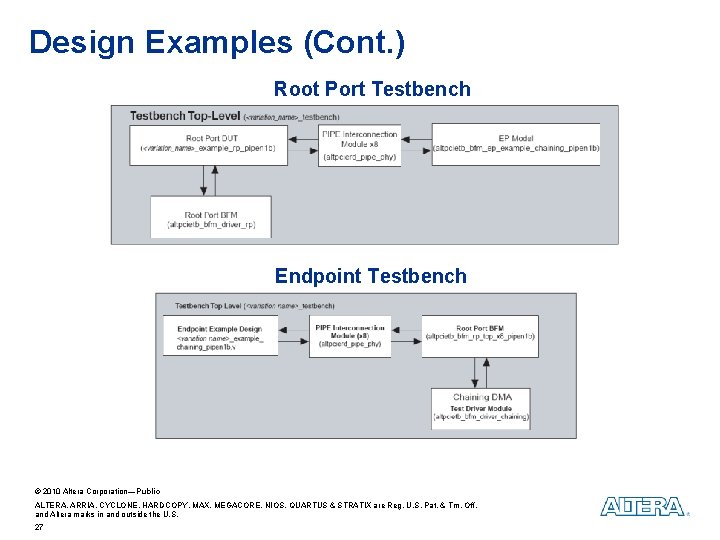

Design Examples (Cont. ) Root Port Testbench Endpoint Testbench © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 27

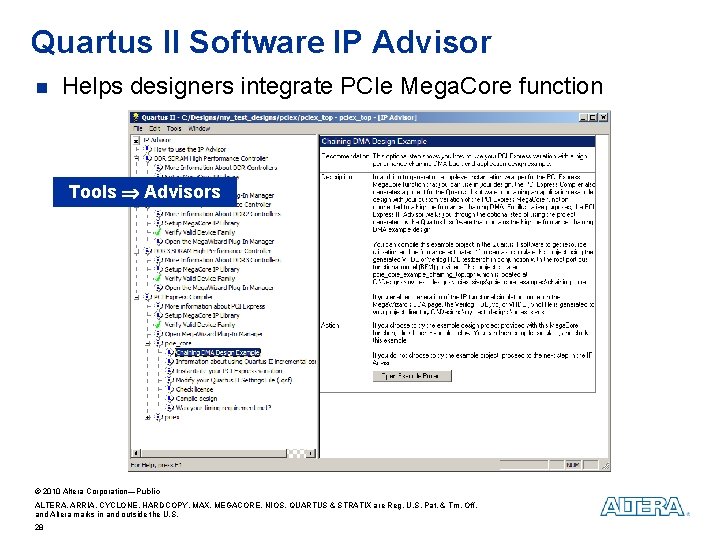

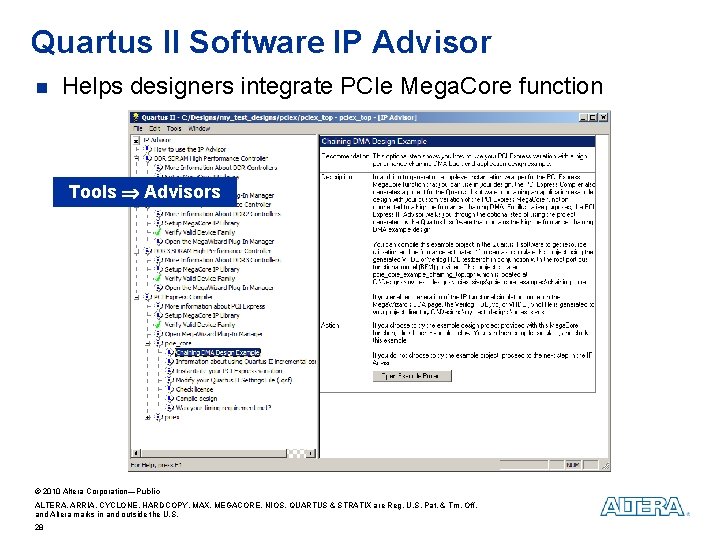

Quartus II Software IP Advisor n Helps designers integrate PCIe Mega. Core function Tools Advisors © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 28

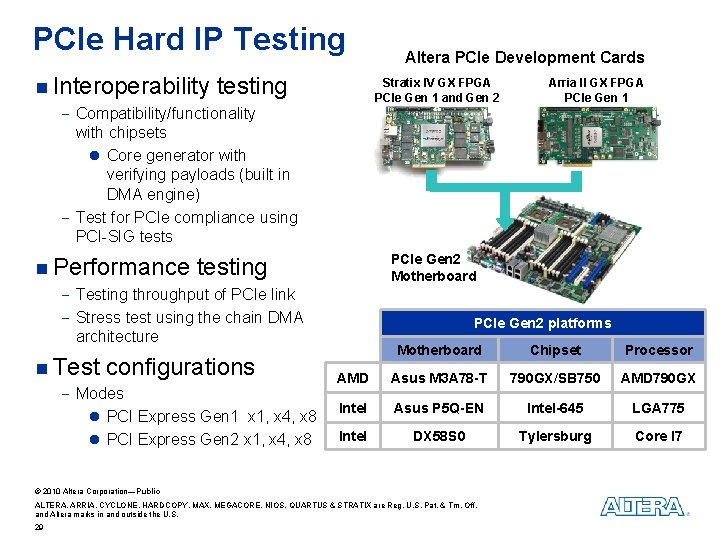

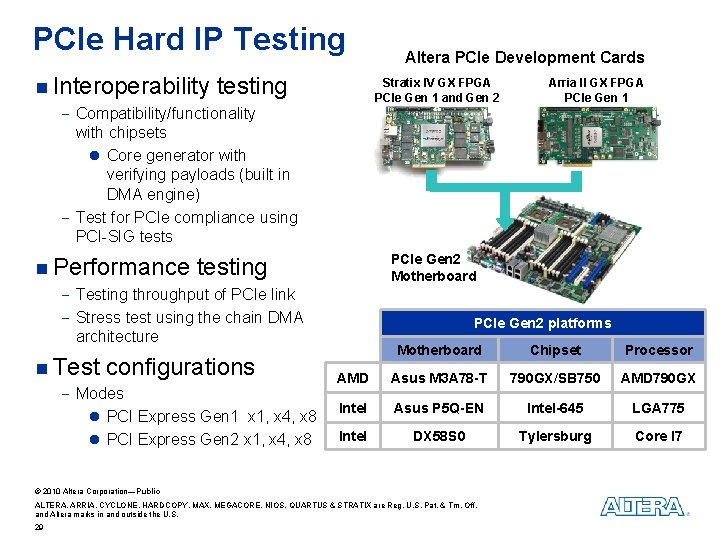

PCIe Hard IP Testing n Interoperability testing Altera PCIe Development Cards Stratix IV GX FPGA PCIe Gen 1 and Gen 2 - Compatibility/functionality Arria II GX FPGA PCIe Gen 1 with chipsets l Core generator with verifying payloads (built in DMA engine) - Test for PCIe compliance using PCI-SIG tests n Performance PCIe Gen 2 Motherboard testing - Testing throughput of PCIe link - Stress test using the chain DMA PCle Gen 2 platforms architecture n Test configurations - Modes l PCI Express Gen 1 x 1, x 4, x 8 l PCI Express Gen 2 x 1, x 4, x 8 Motherboard Chipset Processor AMD Asus M 3 A 78 -T 790 GX/SB 750 AMD 790 GX Intel Asus P 5 Q-EN Intel-645 LGA 775 Intel DX 58 S 0 Tylersburg Core I 7 © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 29

PCIe IP Core Resource Center n Provides links to extensive materials on using PCIe IP Mega. Core © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 30

Documentation and Resources n n n Altera PCI Express Solutions webpage Altera PCI Express Hard IP webpage Device resources - - n Altera Online training - n Cyclone IV device family l Cyclone IV FPGA Overview page l Hard. Copy IV FPGA Getting Started page l Cyclone IV Device Handbook Arria II GX device family l Arria II GX FPGA Overview page l Arria II GX FPGA Getting Started page l Arria II GX Device Handbook Stratix IV device family l Stratix IV FPGA Overview page l Stratix IV FPGA Getting Started page l Stratix IV Device Handbook Hard. Copy IV device family l Hard. Copy IV FPGA Overview page l Hard. Vopy IV FPGA Getting Started page l Hard. Copy IV Device Handbook Using SOPC Builder PCI Express Compiler User Guide © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 31

Thank You! For more information visit: www. altera. com © 2010 Altera Corporation—Public