PCB Material Selection for HighSpeed Digital Design EECS

PCB Material Selection for High-Speed Digital Design EECS 713 – Final Project Bradley Henry 12/5/2019

Contents • • Materials Simulated Djordjevic-Sarkar Dielectric Model Simulation Details Stripline Frequency-Domain characteristics PRBS circuit simulation details PRBS Time-Domain outputs Eye Diagrams Other High-speed considerations

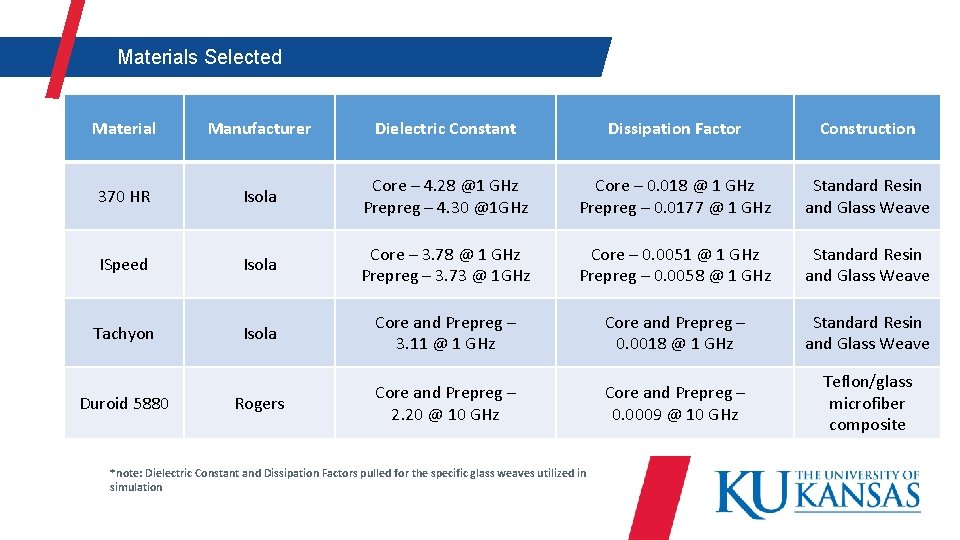

Materials Selected Material Manufacturer Dielectric Constant Dissipation Factor Construction 370 HR Isola Core – 4. 28 @1 GHz Prepreg – 4. 30 @1 GHz Core – 0. 018 @ 1 GHz Prepreg – 0. 0177 @ 1 GHz Standard Resin and Glass Weave ISpeed Isola Core – 3. 78 @ 1 GHz Prepreg – 3. 73 @ 1 GHz Core – 0. 0051 @ 1 GHz Prepreg – 0. 0058 @ 1 GHz Standard Resin and Glass Weave Tachyon Isola Core and Prepreg – 3. 11 @ 1 GHz Core and Prepreg – 0. 0018 @ 1 GHz Standard Resin and Glass Weave Rogers Core and Prepreg – 2. 20 @ 10 GHz Core and Prepreg – 0. 0009 @ 10 GHz Teflon/glass microfiber composite Duroid 5880 *note: Dielectric Constant and Dissipation Factors pulled for the specific glass weaves utilized in simulation

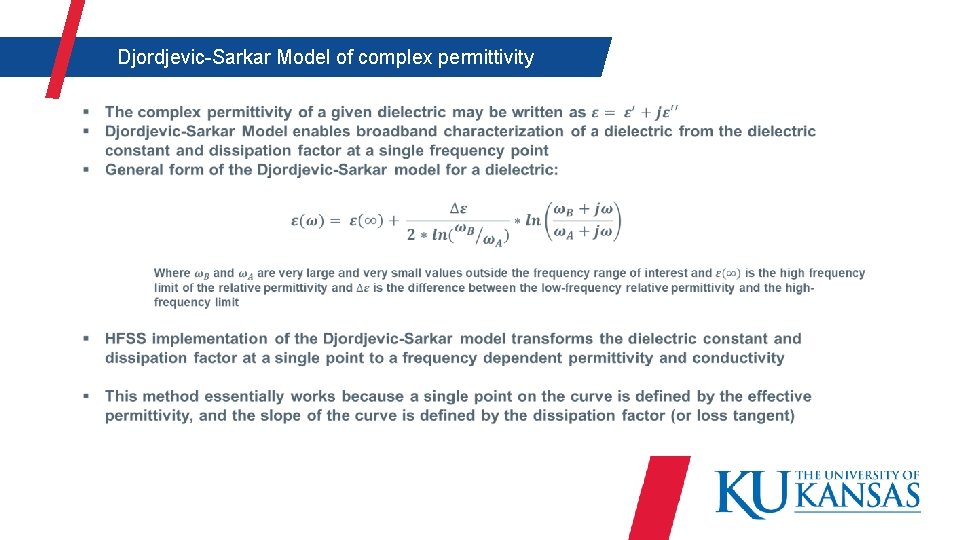

Djordjevic-Sarkar Model of complex permittivity

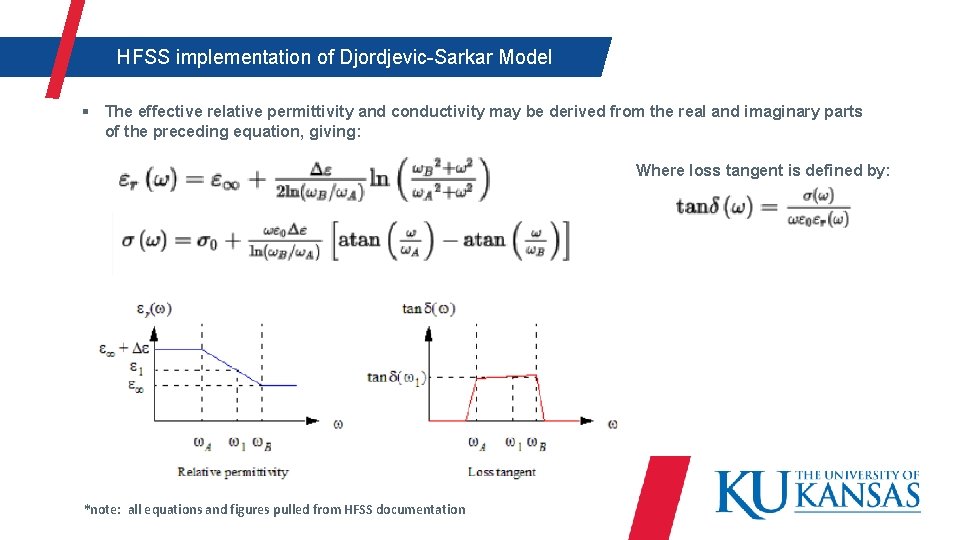

HFSS implementation of Djordjevic-Sarkar Model § The effective relative permittivity and conductivity may be derived from the real and imaginary parts of the preceding equation, giving: Where loss tangent is defined by: *note: all equations and figures pulled from HFSS documentation

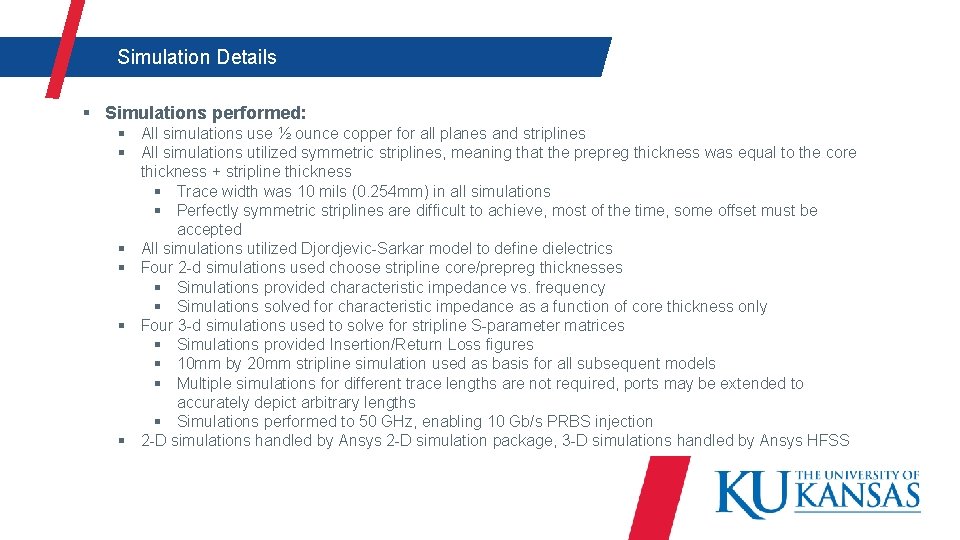

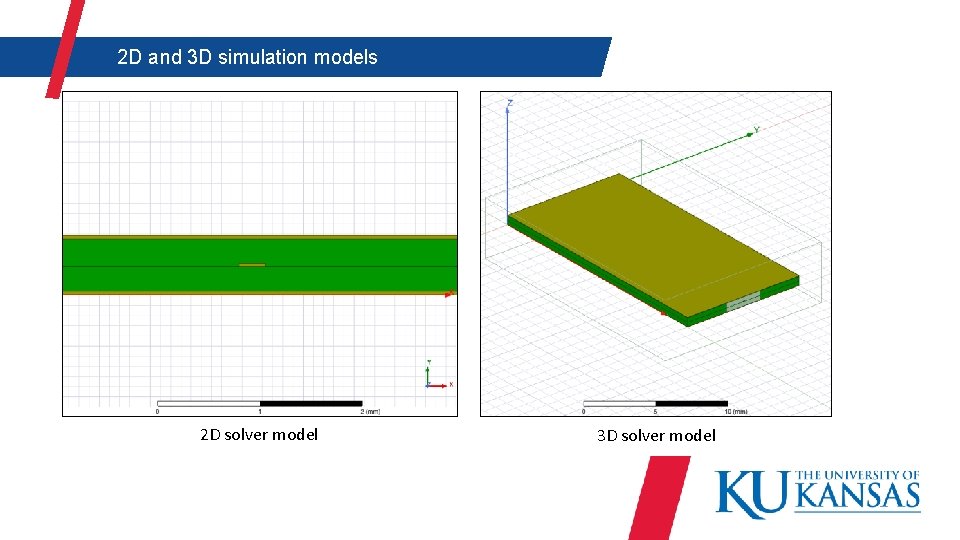

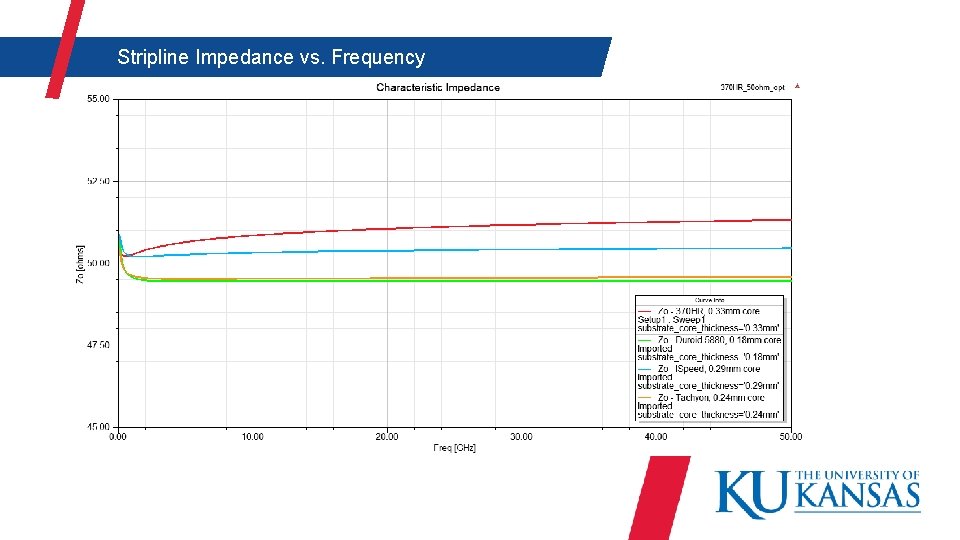

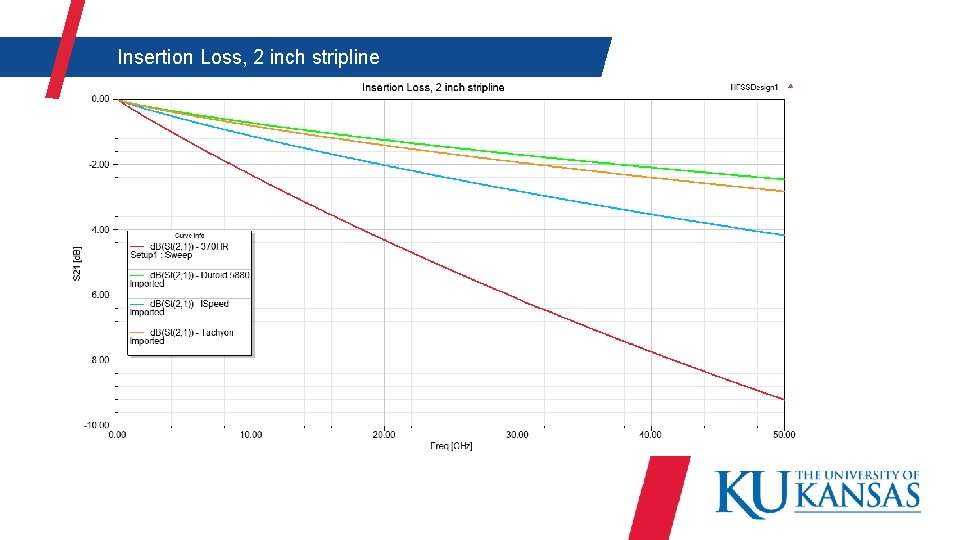

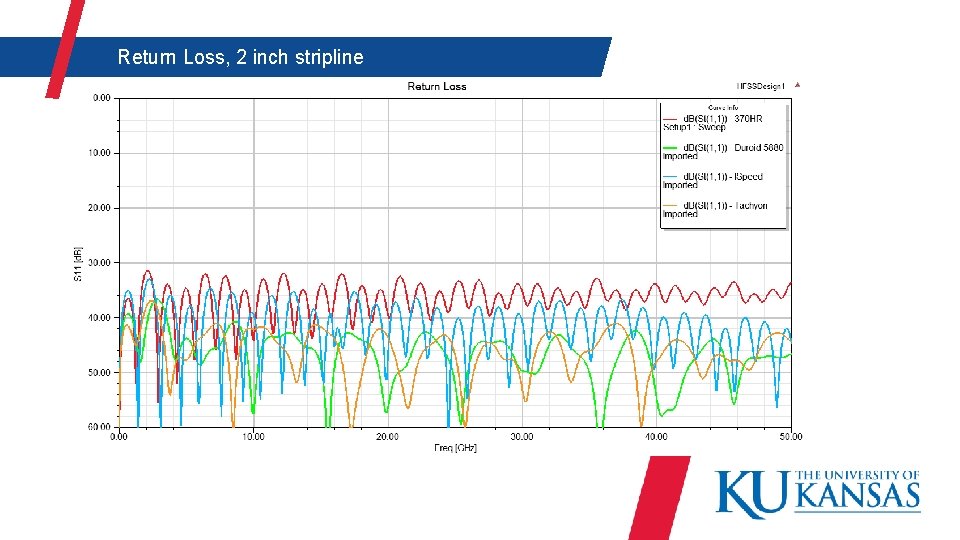

Simulation Details § Simulations performed: § All simulations use ½ ounce copper for all planes and striplines § All simulations utilized symmetric striplines, meaning that the prepreg thickness was equal to the core thickness + stripline thickness § Trace width was 10 mils (0. 254 mm) in all simulations § Perfectly symmetric striplines are difficult to achieve, most of the time, some offset must be accepted § All simulations utilized Djordjevic-Sarkar model to define dielectrics § Four 2 -d simulations used choose stripline core/prepreg thicknesses § Simulations provided characteristic impedance vs. frequency § Simulations solved for characteristic impedance as a function of core thickness only § Four 3 -d simulations used to solve for stripline S-parameter matrices § Simulations provided Insertion/Return Loss figures § 10 mm by 20 mm stripline simulation used as basis for all subsequent models § Multiple simulations for different trace lengths are not required, ports may be extended to accurately depict arbitrary lengths § Simulations performed to 50 GHz, enabling 10 Gb/s PRBS injection § 2 -D simulations handled by Ansys 2 -D simulation package, 3 -D simulations handled by Ansys HFSS

2 D and 3 D simulation models 2 D solver model 3 D solver model

Stripline Impedance vs. Frequency

Insertion Loss, 2 inch stripline

Return Loss, 2 inch stripline

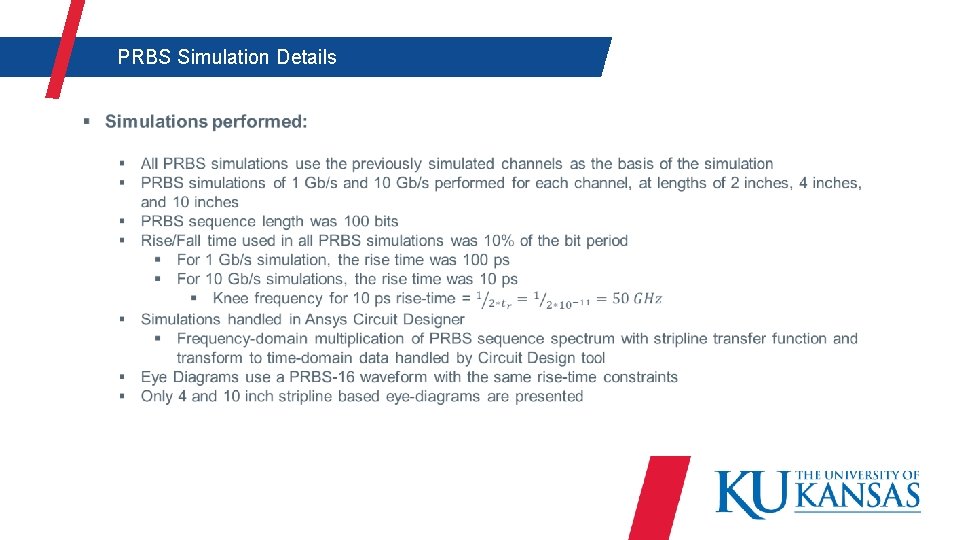

PRBS Simulation Details

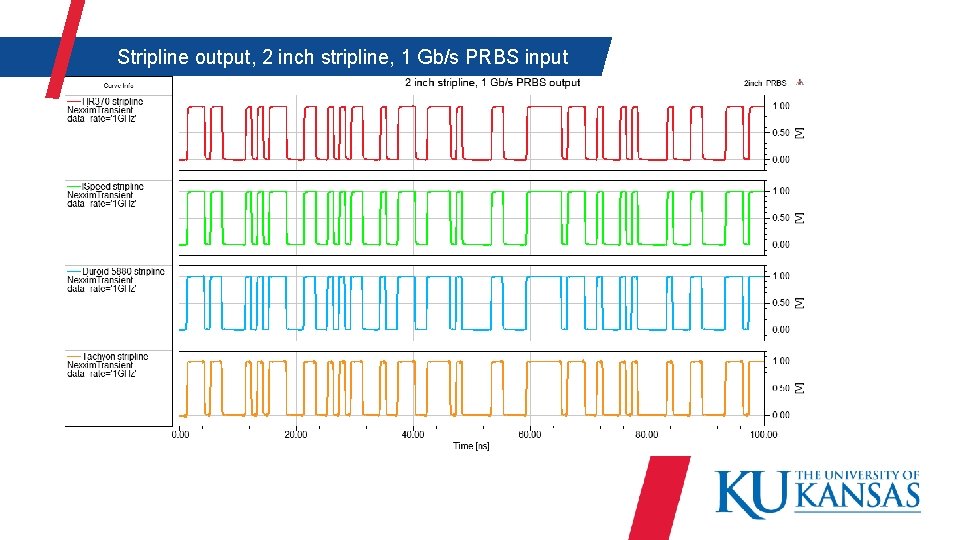

Stripline output, 2 inch stripline, 1 Gb/s PRBS input

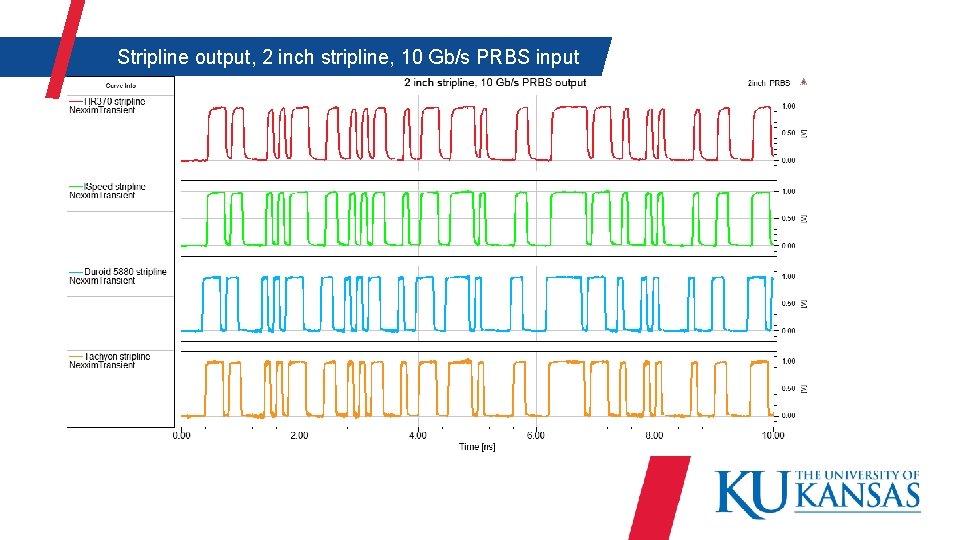

Stripline output, 2 inch stripline, 10 Gb/s PRBS input

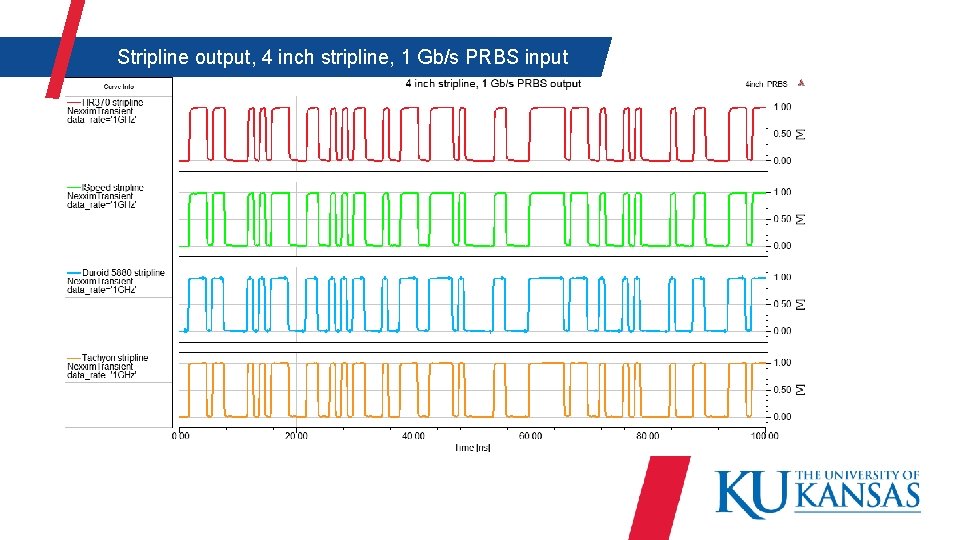

Stripline output, 4 inch stripline, 1 Gb/s PRBS input

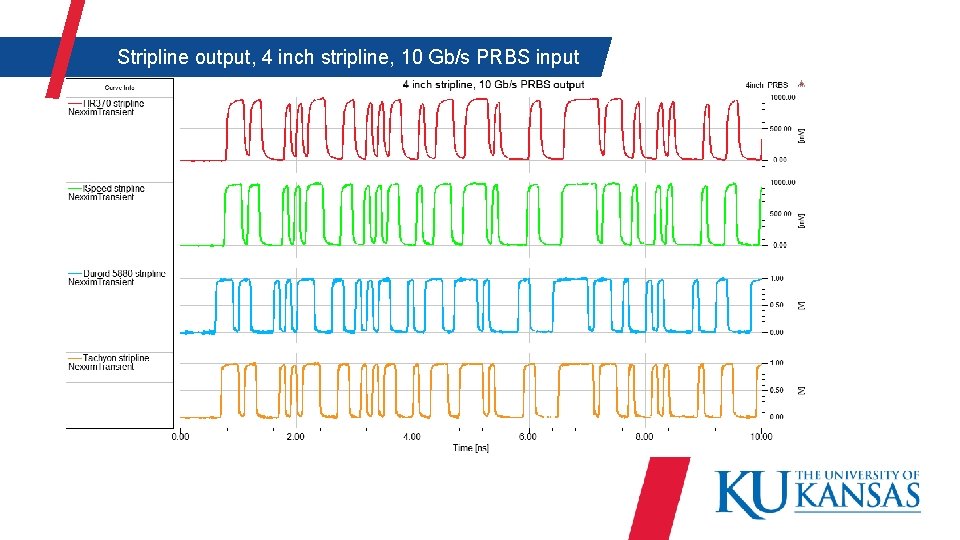

Stripline output, 4 inch stripline, 10 Gb/s PRBS input

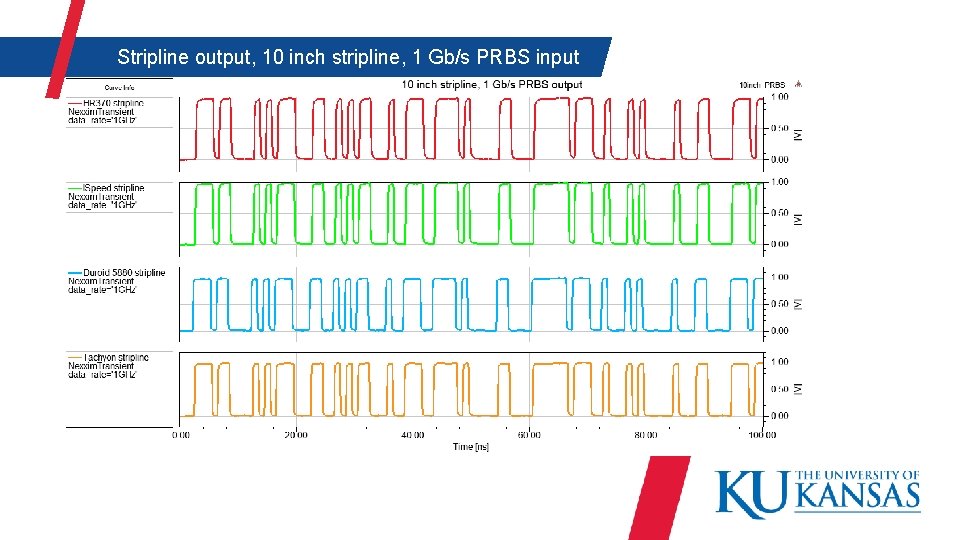

Stripline output, 10 inch stripline, 1 Gb/s PRBS input

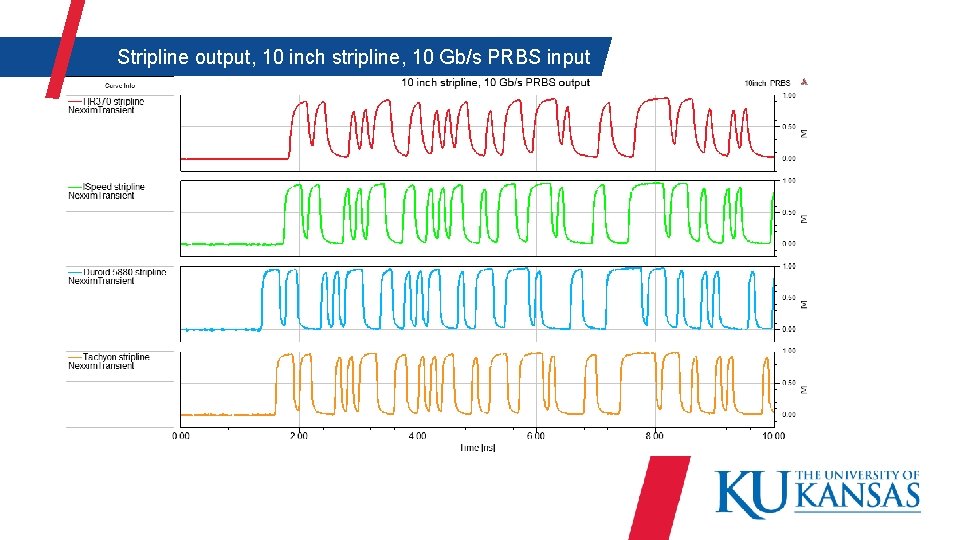

Stripline output, 10 inch stripline, 10 Gb/s PRBS input

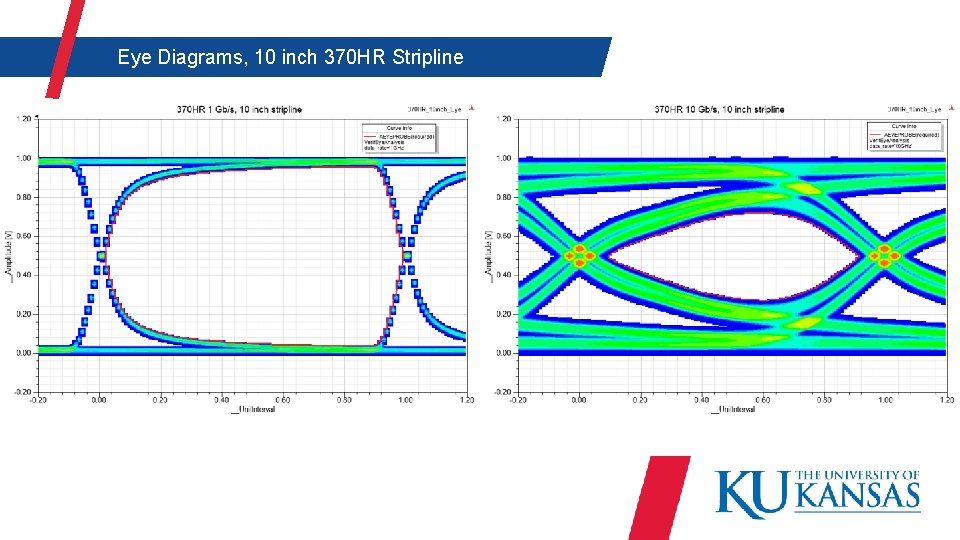

Eye Diagrams, 10 inch 370 HR Stripline

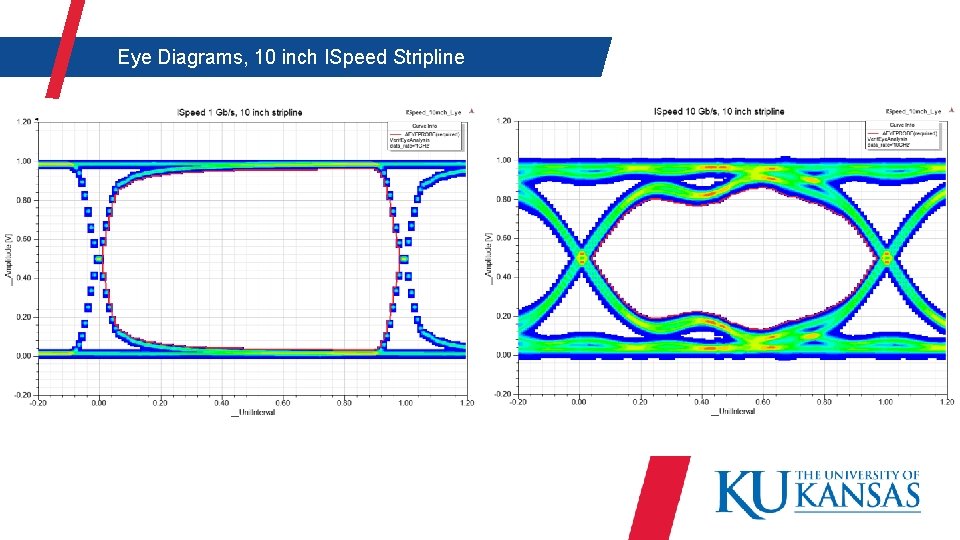

Eye Diagrams, 10 inch ISpeed Stripline

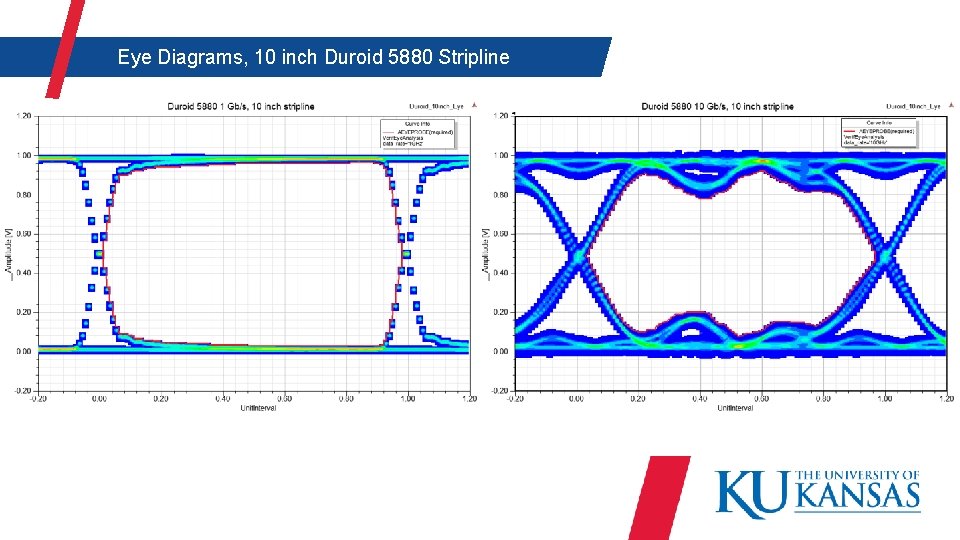

Eye Diagrams, 10 inch Duroid 5880 Stripline

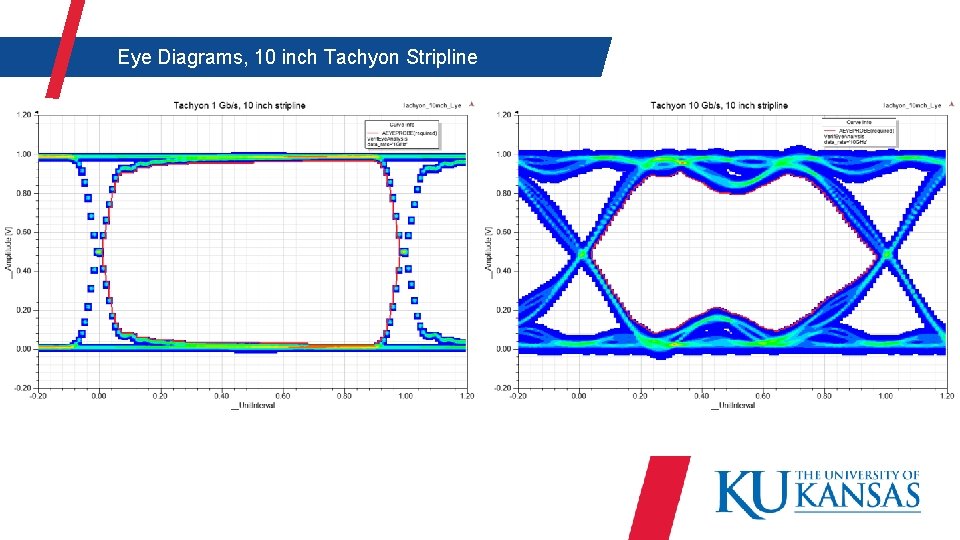

Eye Diagrams, 10 inch Tachyon Stripline

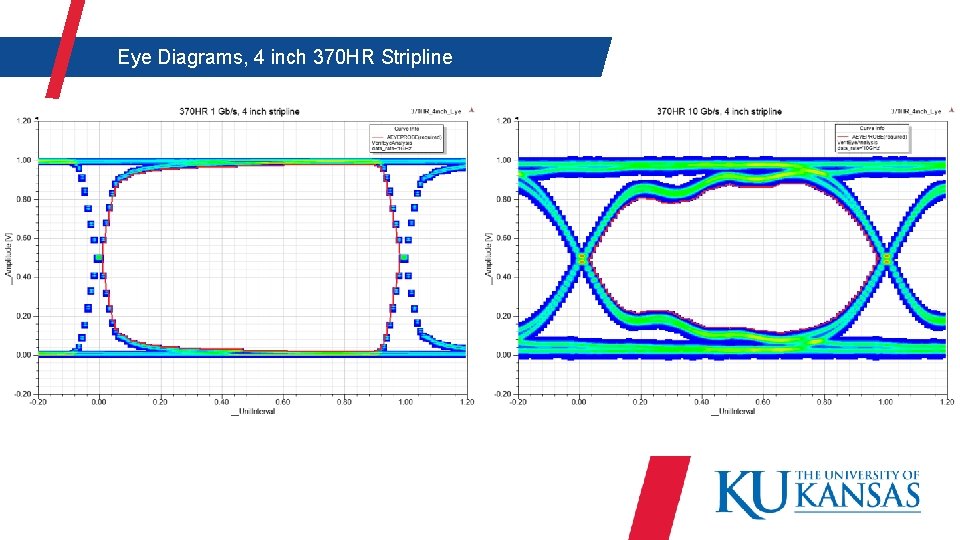

Eye Diagrams, 4 inch 370 HR Stripline

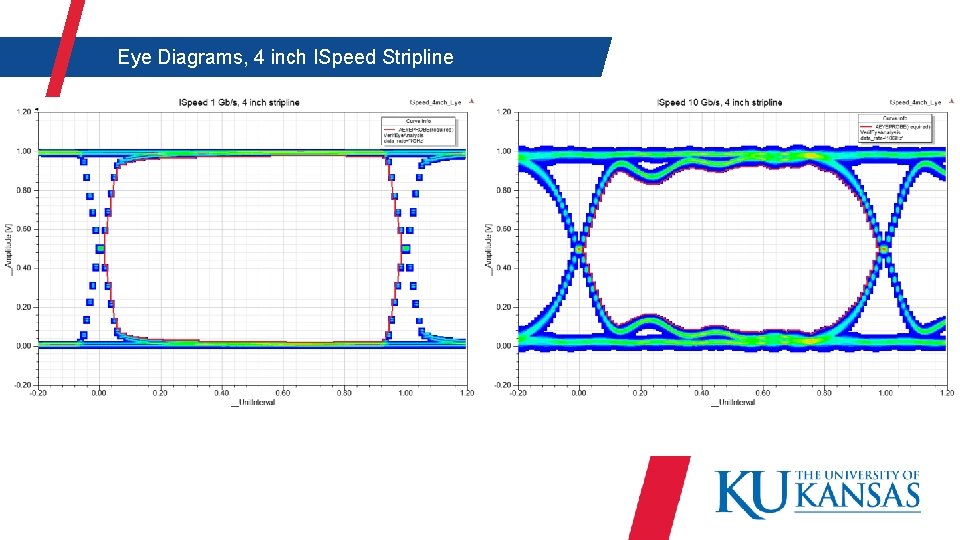

Eye Diagrams, 4 inch ISpeed Stripline

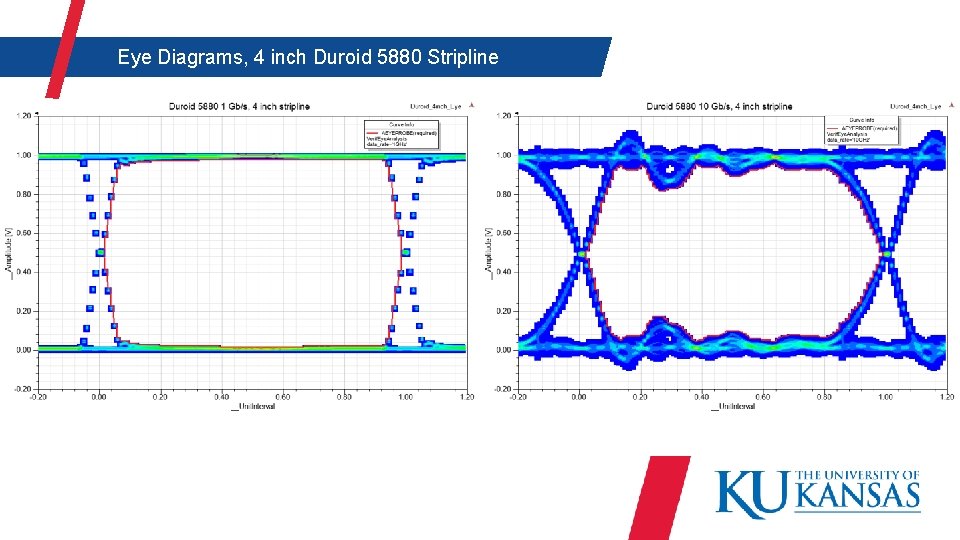

Eye Diagrams, 4 inch Duroid 5880 Stripline

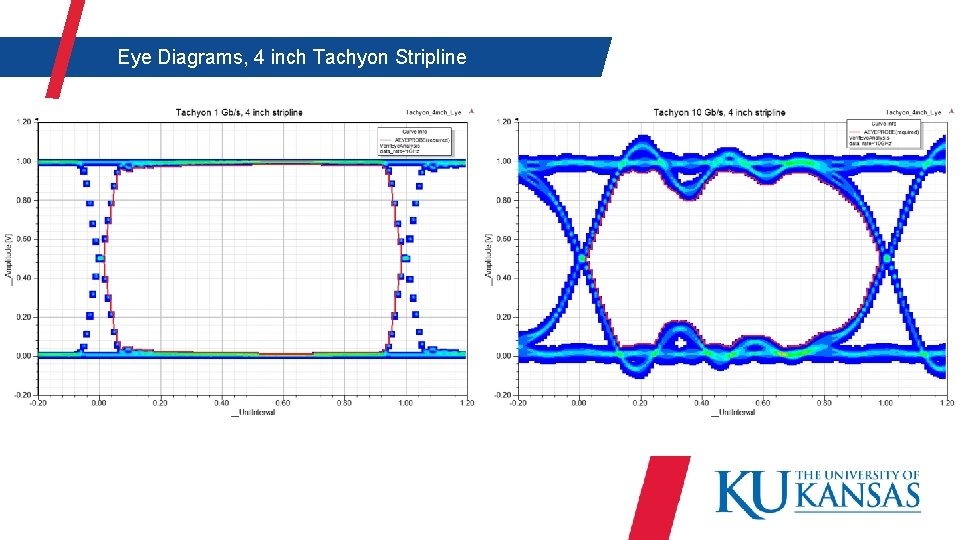

Eye Diagrams, 4 inch Tachyon Stripline

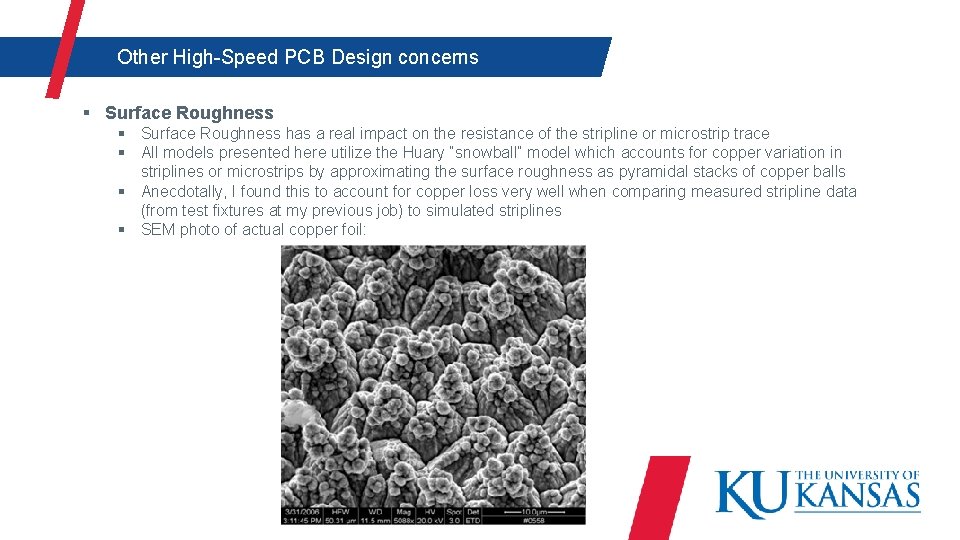

Other High-Speed PCB Design concerns § Surface Roughness has a real impact on the resistance of the stripline or microstrip trace § All models presented here utilize the Huary “snowball” model which accounts for copper variation in striplines or microstrips by approximating the surface roughness as pyramidal stacks of copper balls § Anecdotally, I found this to account for copper loss very well when comparing measured stripline data (from test fixtures at my previous job) to simulated striplines § SEM photo of actual copper foil:

Other High-Speed PCB Design concerns § Glass weave and trace orientation § Glass weave typically is hatched together in a ‘north-south’ and ‘east-west’ type configuration § Most PCB designers route in straight lines in a relatively ‘north-south’ and/or ‘east-west’ configuration when possible § As such, when a trace happens to sit directly on top of the glass-weave fiber, a pronounced difference in dielectric constant (and therefore characteristic impedance) negatively impacts an otherwise welldesigned circuit connection § Approaches to minimize the likelihood of this occurring: § Use a composite material (such as the Rogers Duroid in this report) which has glass microfibers in random orientations throughout the substrate § Check material datasheets to find “mechanically-spread” substrates, these have a much wider and well-accounted for distribution of the glass weave § PCB manufacturers are able to rotate the substrates such that PCB traces routed in ‘north-south’ or ‘east-west’ orientations will not encounter a long run of fiber (typically they offer a 15 degree rotation)

- Slides: 27