PC Maintenance Preparing for A Certification Chapter 5

- Slides: 27

PC Maintenance: Preparing for A+ Certification Chapter 5: CPUs

Chapter 5 Objectives Understand how a CPU holds and processes data n Identify ways by which a CPU is categorized and evaluated n Distinguish between PGA and SECC packaging n Understand how modern CPUs have evolved from earlier versions n

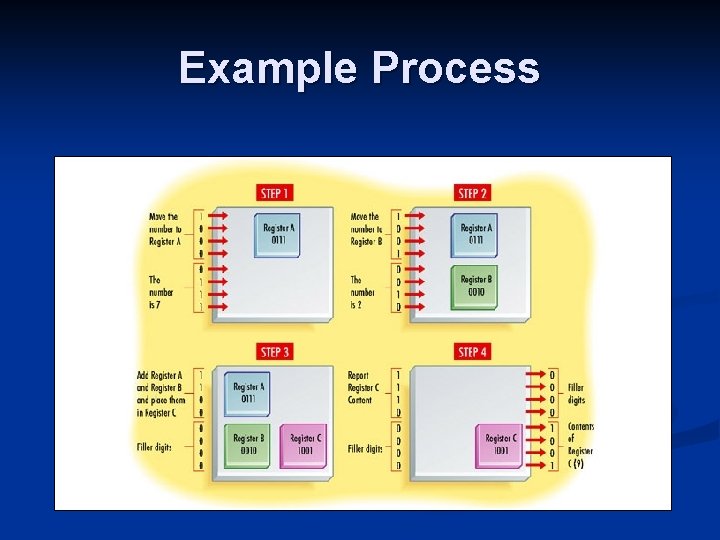

Inside the CPU Low-order bits: data that represents numbers to be calculated n High-order bits: data that represents instructions to the CPU n

Inside the CPU Instruction set: high-order bit codes that the CPU understands n Registers: holding areas for data inside the CPU n

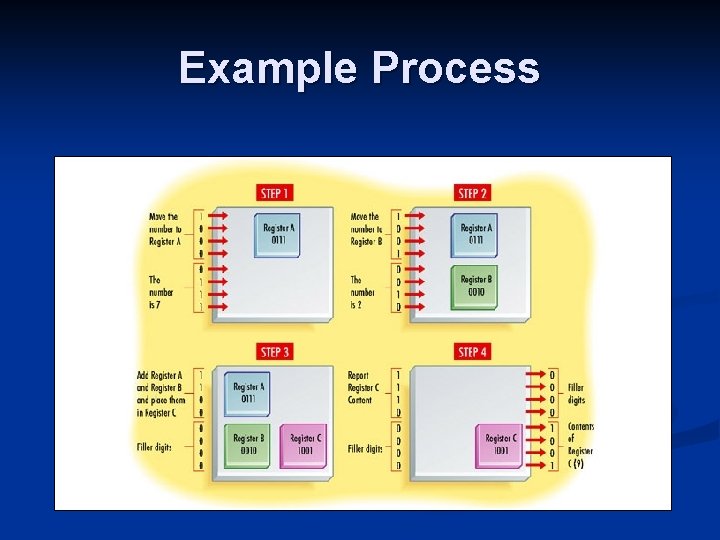

Example Process

Data Processing Speed n External speed Speed at which motherboard and CPU communicate n Controlled by system crystal n n Internal speed Speed at which CPU performs internal operations n Usually a multiple of the external speed n

Overclocking and Underclocking Overclocking: operating a CPU at a higher internal speed than it is rated for n Underclocking: operating a CPU at a lower internal speed than it is rated for n

Core Voltage that the CPU requires to operate n Ranges from approximately +1. 5 v to +5 v n Newer CPUs = lower voltages n Motherboard must provide correct voltage n

CPU Cache Usage n L 1 cache Front-side cache n Holds data waiting to enter the CPU n Built into the CPU on modern systems n n L 2 cache Back-side cache n Holds data exiting the CPU n Built into the CPU packaging, but on a separate chip n

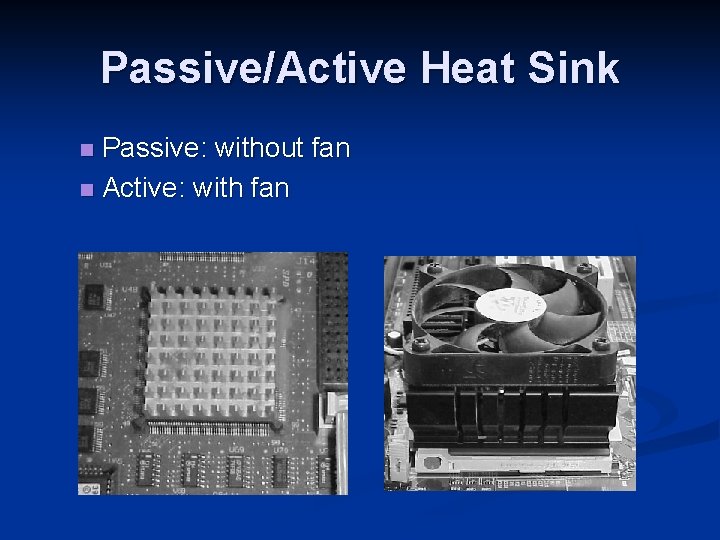

CPU Cooling n Fan n n Pulls heat away from CPU Heat sink n Spikes channel heat away from CPU

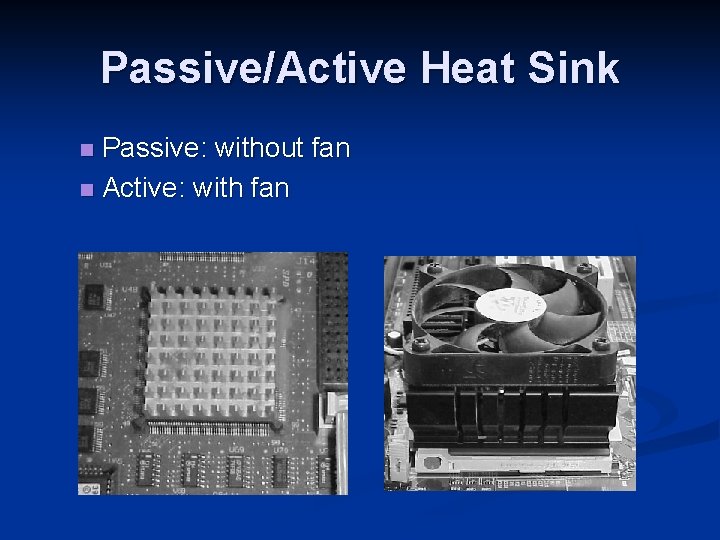

Passive/Active Heat Sink Passive: without fan n Active: with fan n

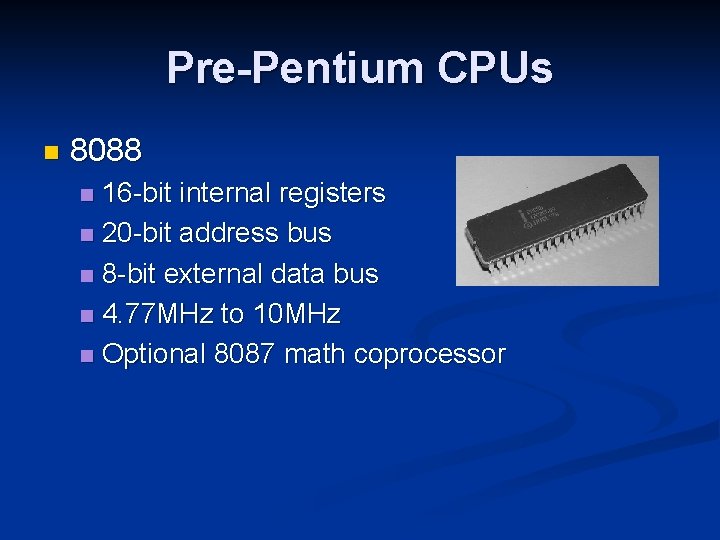

Pre-Pentium CPUs n 8088 16 -bit internal registers n 20 -bit address bus n 8 -bit external data bus n 4. 77 MHz to 10 MHz n Optional 8087 math coprocessor n

Pre-Pentium CPUs n 80286 n Could run in Protected Mode n More RAM could be addressed n Multitasking n Could run in Real Mode n Backward compatible with applications for 8088 Could use expanded memory on an ISA expansion board n Up to 20 MHz in speed n

Pre-Pentium CPUs n 80386 (i 386) 386 protected mode, 286 protected mode, and real mode n Virtual memory n Virtual 8086 mode n n 386 DX versus 386 SX 32 -bit versus 16 -bit external data bus n 32 -bit versus 24 -bit address bus n

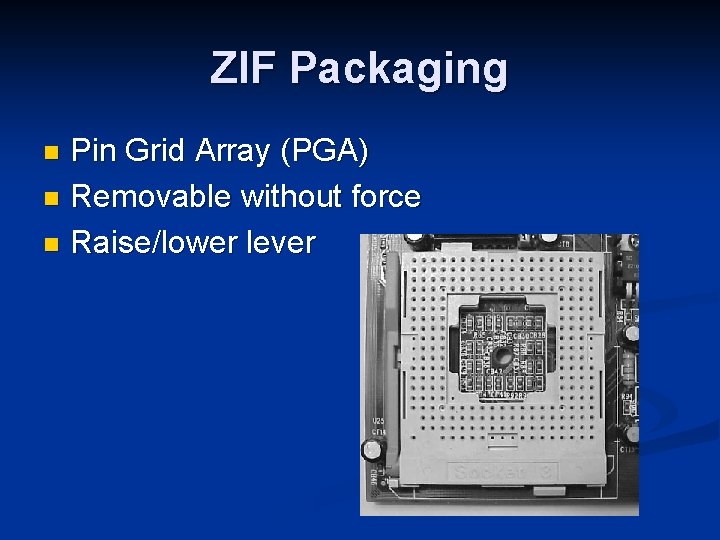

Pre-Pentium CPUs n 80486 (i 486) Built-in coprocessor (on DX models) n Clock multipliers n Up to 120 MHz (clock-tripled) n First CPU to use ZIF packaging n n 486 DX versus 486 SX n Disabled math coprocessor on 486 SX

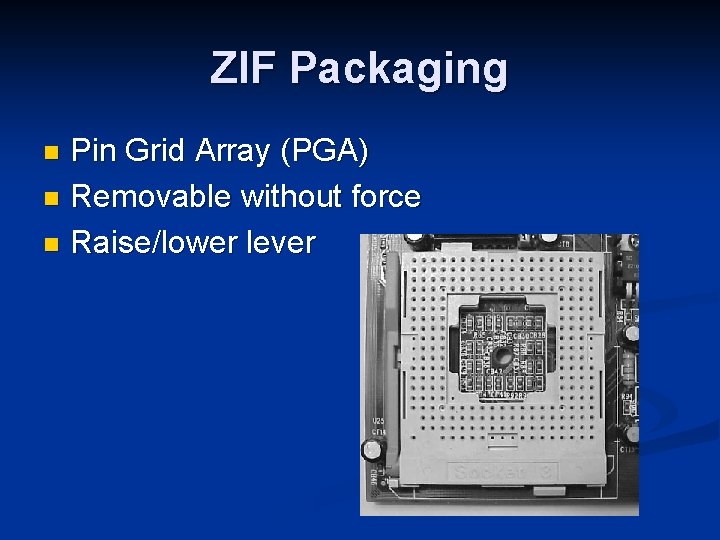

ZIF Packaging Pin Grid Array (PGA) n Removable without force n Raise/lower lever n

Pentium Packaging n Socket 4 +5 v socket n Used for 1 st Generation Pentium (60, 66 MHz) n 273 -pin n n Socket 3 Variable-voltage socket, +3. 3 v or +5 v n Introduced after Socket 4 n Works with either 486 or 1 st Generation Pentium n

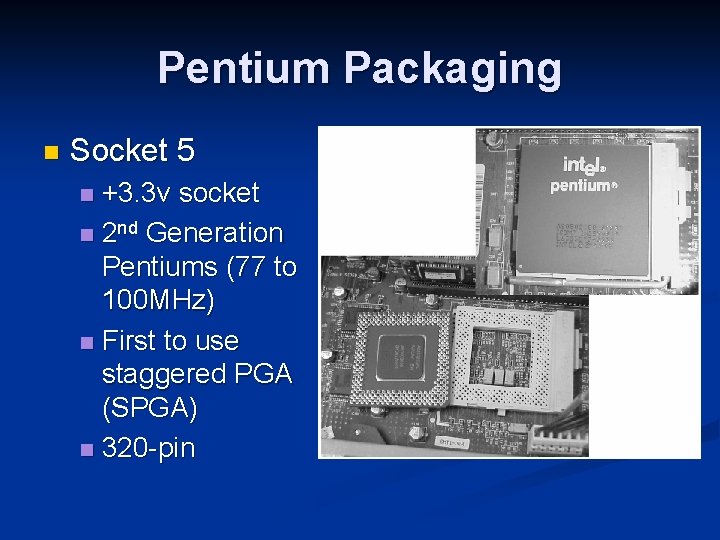

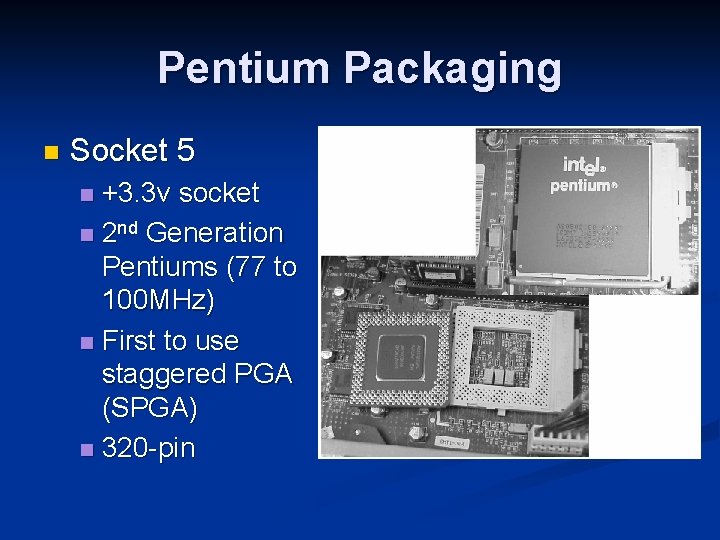

Pentium Packaging n Socket 5 +3. 3 v socket n 2 nd Generation Pentiums (77 to 100 MHz) n First to use staggered PGA (SPGA) n 320 -pin n

Pentium Packaging n n Socket 6 n +3. 3 v socket n Used for Pentium Over. Drive and 486 DX 4 Socket 7 n n n Variable voltage socket, +3. 3 v or +5 v 321 pins (rather than 320 on Socket 5) Otherwise the same as Socket 5

Pentium Packaging n Super Socket 7 (Super 7) n n n Enhanced Socket 7 Used with 2 nd Generation Pentium and non-Intel competitor chips Provides split voltage capability that allows higher external than internal voltage

Pentium CPUs n First-Generation 60 or 66 MHz n Used Socket 3 or Socket 4 n n Second-Generation 75 to 100 MHz n Used Socket 5 or Socket 7 n n Third-Generation 166 to 233 MHz n Adds MMX capability n

Pentium Pro Improvement on Second-Generation Pentium n Introduced quad pipelining n Introduced on-chip L 2 cache n Lacked MMX n Optimized for 32 -bit operating systems n Socket 8: +3 v rectangular socket, 387 pins n

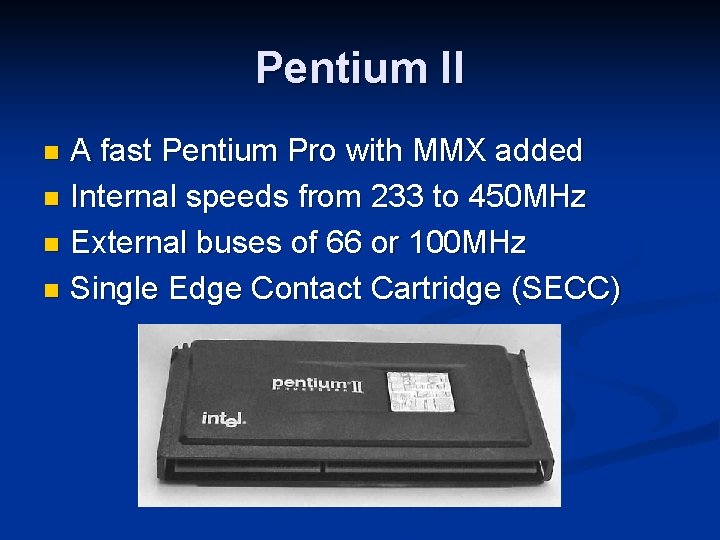

Pentium II A fast Pentium Pro with MMX added n Internal speeds from 233 to 450 MHz n External buses of 66 or 100 MHz n Single Edge Contact Cartridge (SECC) n

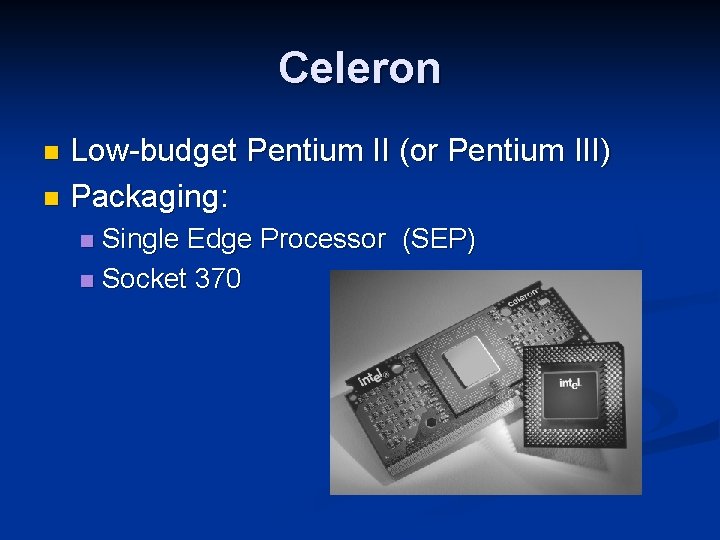

Celeron Low-budget Pentium II (or Pentium III) n Packaging: n Single Edge Processor (SEP) n Socket 370 n

AMD K 6 Competitor to Pentium II n Socket 7 PGA chip n Versions: n K 6: 166 to 300 MHz n K 6 -2: 266 to 475 MHz, 3 DNow! Technology n K 6 -3: 400 to 450 MHz, full-speed L 2 cache n

Pentium III 450 MHz to 1 GHz n Packaging: n SECC 2 n Socket 370 n Flip-Chip (FC) design n

Pentium 4 1. 3 GHz to more than 2. 8 GHz n Socket 423 or Socket 478 n Net. Burst architecture n 64 -bit, 100 MHz quad pipelining n 20 Kb L 1 cache, 256 KB full-speed L 2 cache n