PC Address Instruction Memory Next PC Logic Simplified

![Basic Instruction Fetch PC + 4 PC Adder 4 PC Address Instruction Memory M[PC] Basic Instruction Fetch PC + 4 PC Adder 4 PC Address Instruction Memory M[PC]](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-7.jpg)

![load word M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 R load word M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 R](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-18.jpg)

![store word R[rt] M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 store word R[rt] M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-19.jpg)

![Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-22.jpg)

![Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-23.jpg)

![Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-24.jpg)

![Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs - Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs -](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-25.jpg)

![Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs - Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs -](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-26.jpg)

- Slides: 27

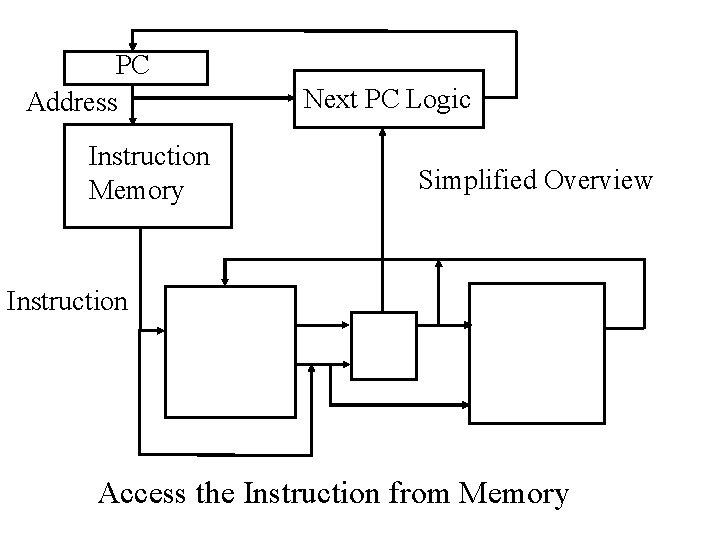

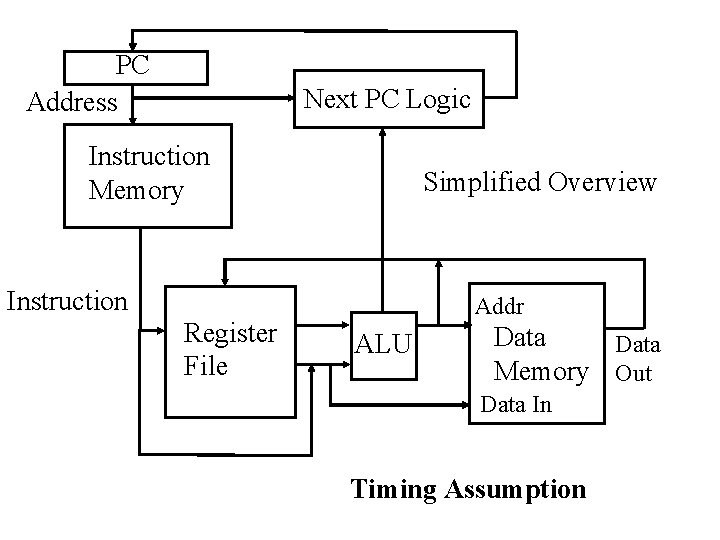

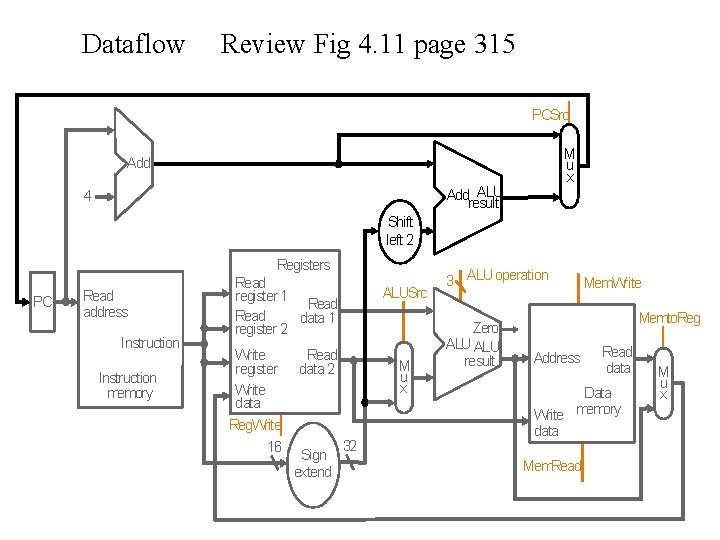

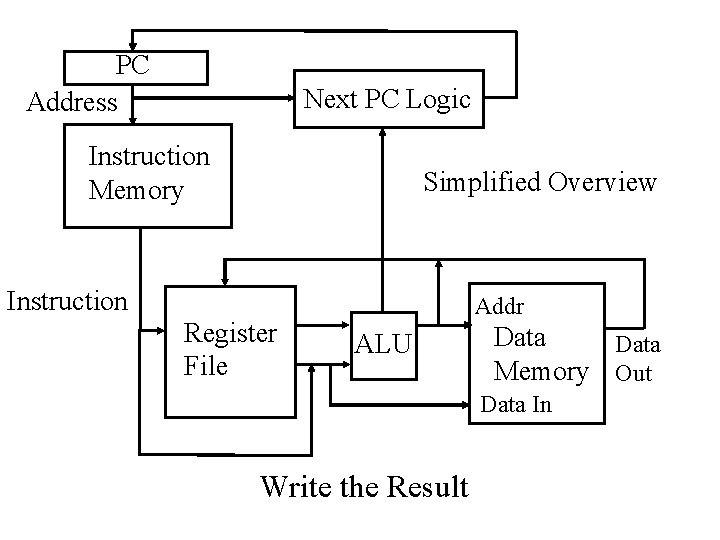

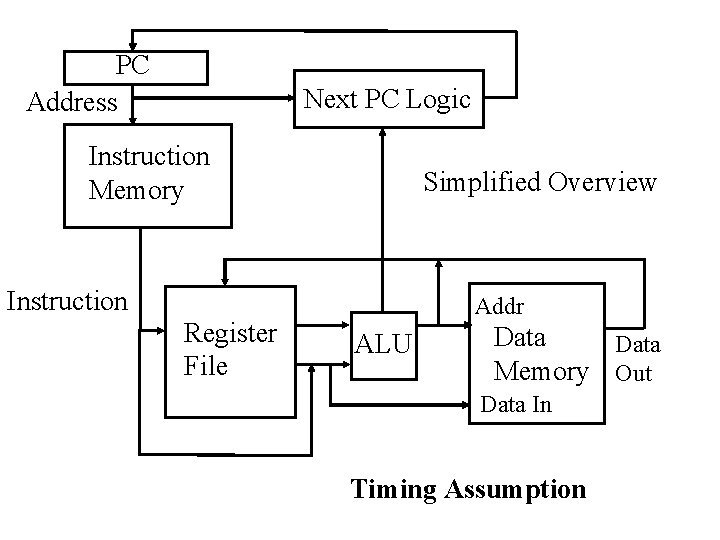

PC Address Instruction Memory Next PC Logic Simplified Overview Instruction Access the Instruction from Memory

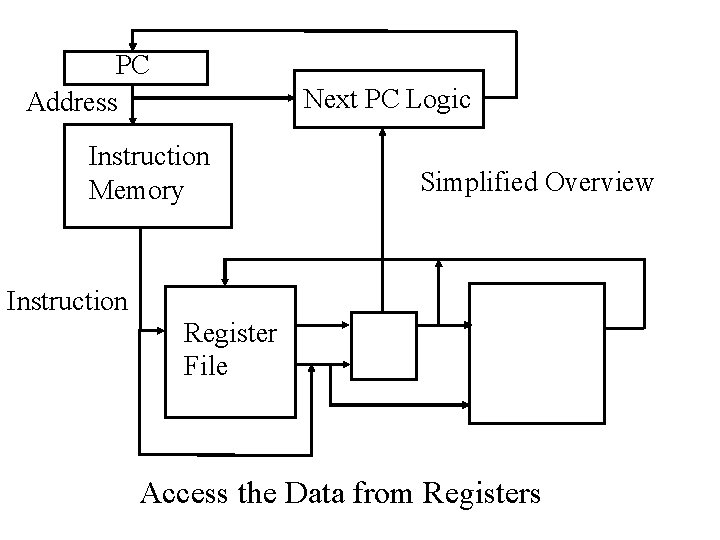

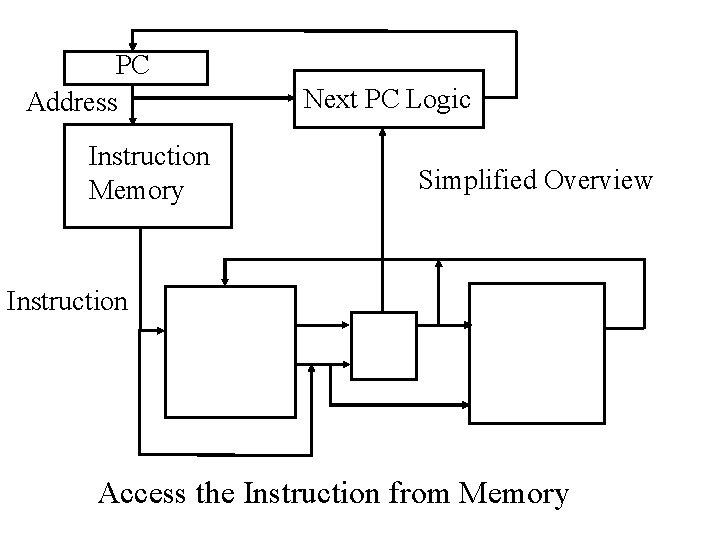

PC Address Next PC Logic Instruction Memory Simplified Overview Instruction Register File Access the Data from Registers

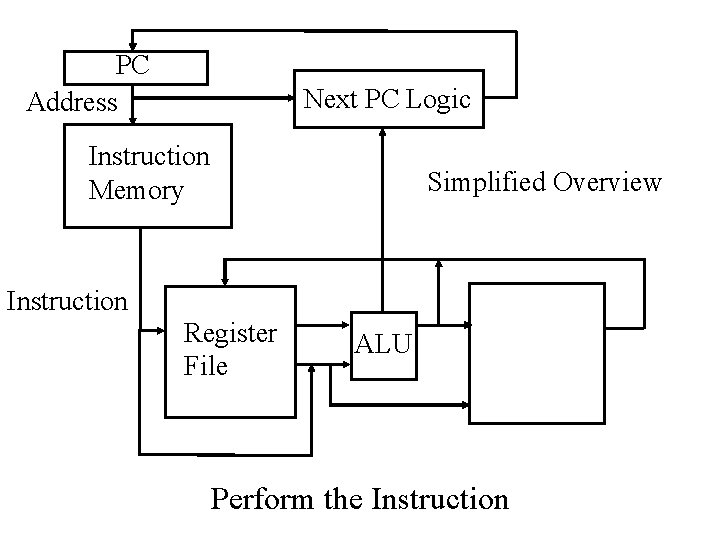

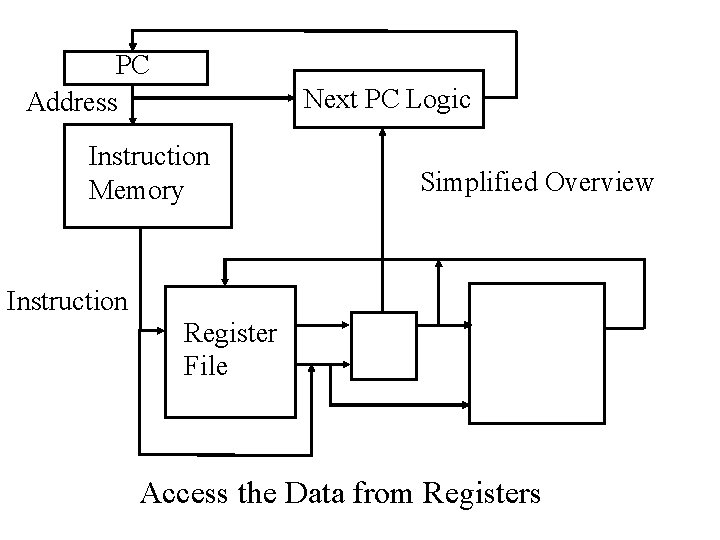

PC Address Next PC Logic Instruction Memory Simplified Overview Instruction Register File ALU Perform the Instruction

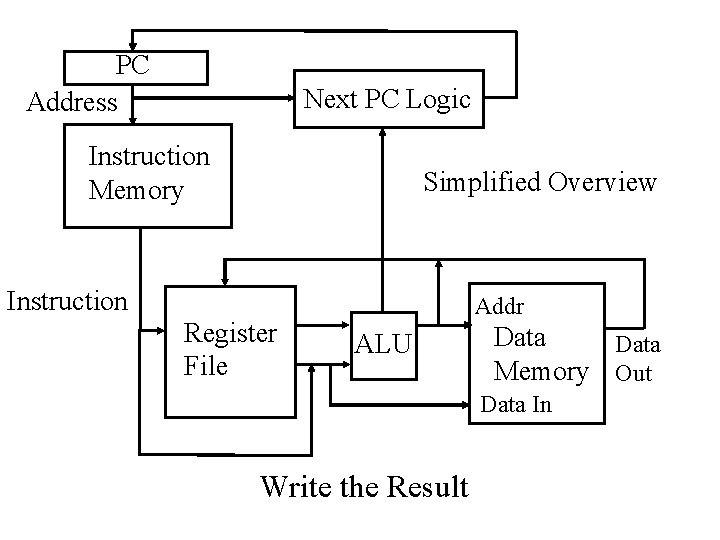

PC Address Next PC Logic Instruction Memory Simplified Overview Instruction Register File Addr ALU Data Memory Out Data In Write the Result

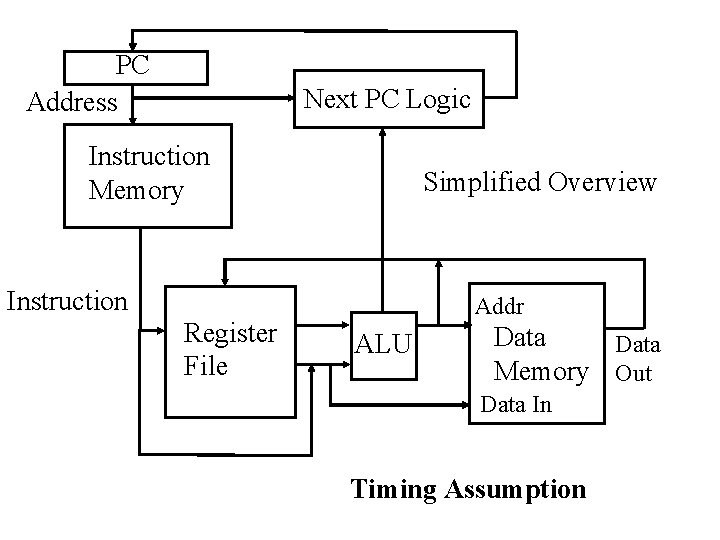

PC Address Next PC Logic Instruction Memory Simplified Overview Instruction Register File Addr ALU Data Memory Out Data In Timing Assumption

![Basic Instruction Fetch PC 4 PC Adder 4 PC Address Instruction Memory MPC Basic Instruction Fetch PC + 4 PC Adder 4 PC Address Instruction Memory M[PC]](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-7.jpg)

Basic Instruction Fetch PC + 4 PC Adder 4 PC Address Instruction Memory M[PC]

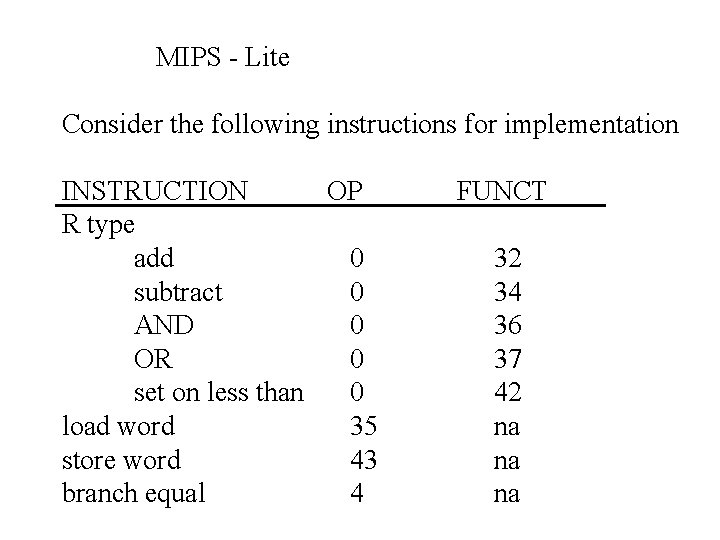

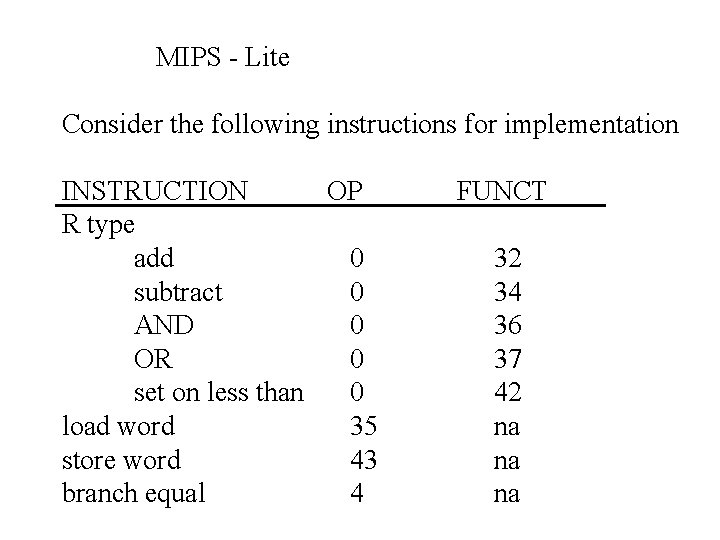

MIPS - Lite Consider the following instructions for implementation INSTRUCTION OP R type add 0 subtract 0 AND 0 OR 0 set on less than 0 load word 35 store word 43 branch equal 4 FUNCT 32 34 36 37 42 na na na

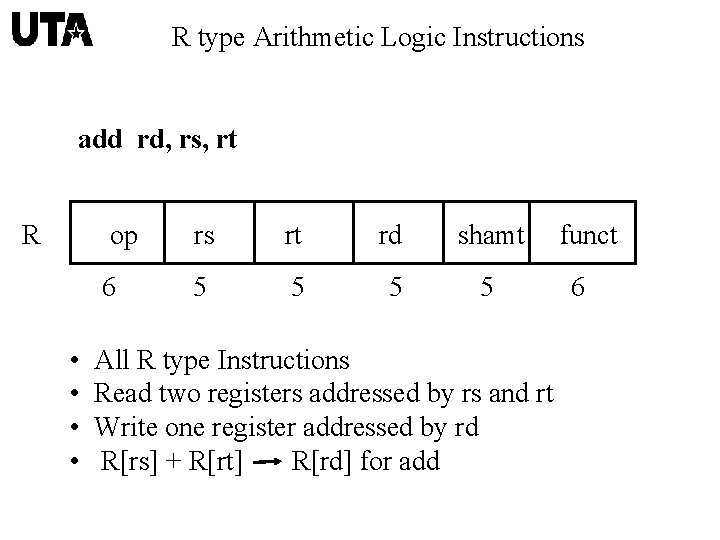

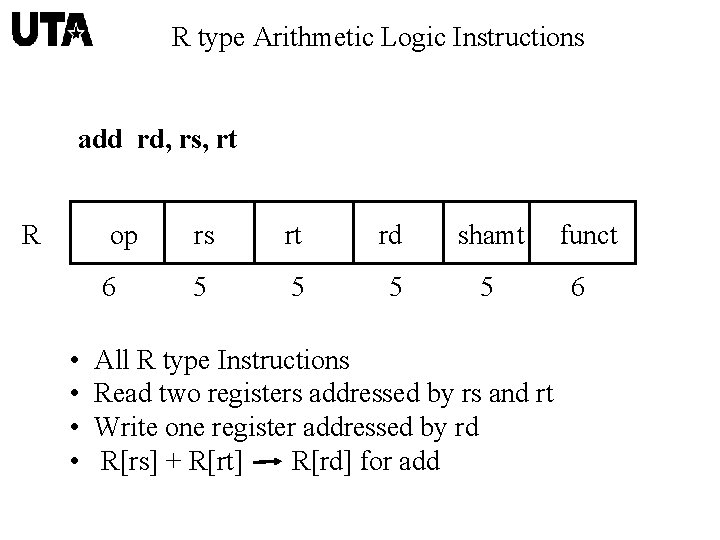

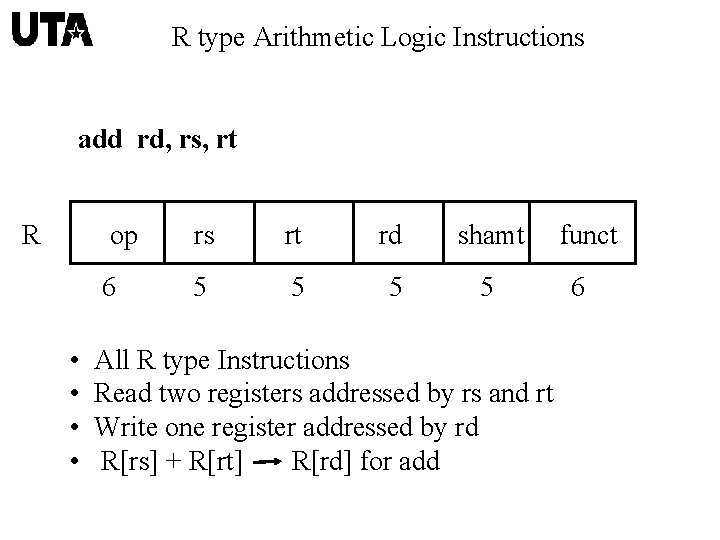

R type Arithmetic Logic Instructions add rd, rs, rt R • • op rs rt rd shamt 6 5 5 All R type Instructions Read two registers addressed by rs and rt Write one register addressed by rd R[rs] + R[rt] R[rd] for add funct 6

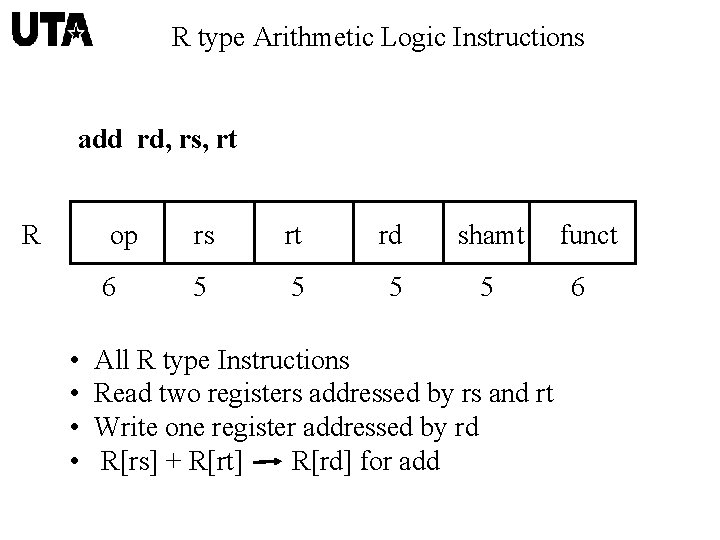

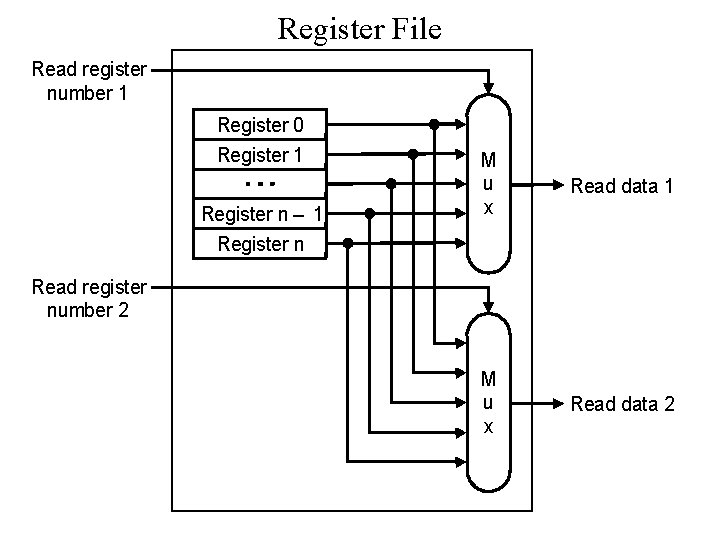

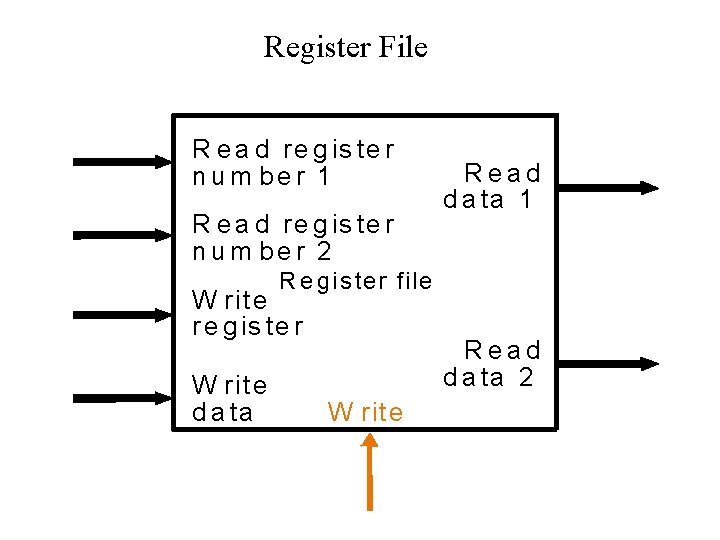

Register File Read register number 1 Register 0 Register 1 Register n – 1 Register n M u x Read data 1 M u x Read data 2 Read register number 2

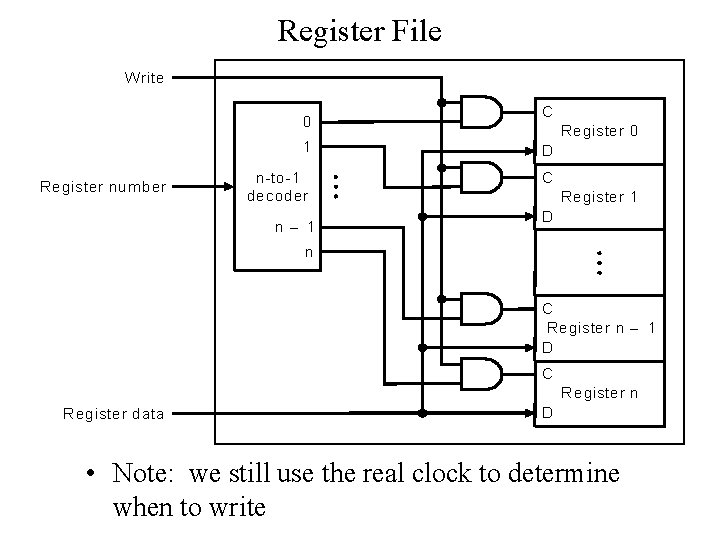

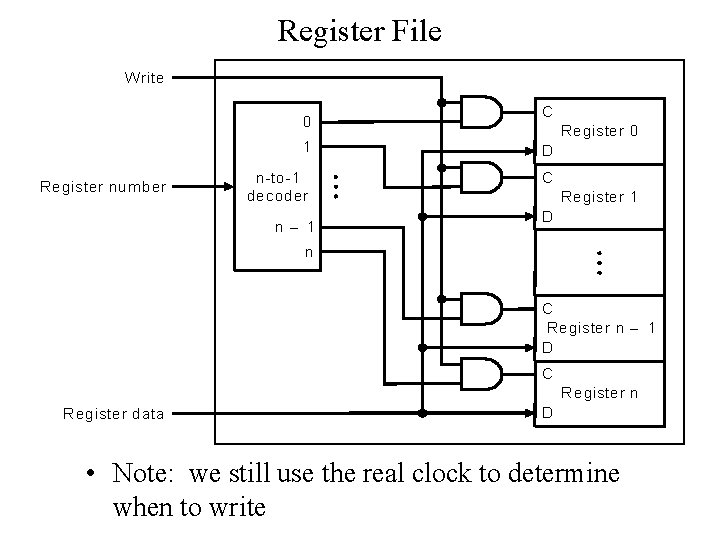

Register File W rite 0 R egister num be r C R e giste r 0 1 D n -to -1 de coder C n – 1 R e giste r 1 D n C R egister n – 1 D C R e giste r n R e gister data D • Note: we still use the real clock to determine when to write

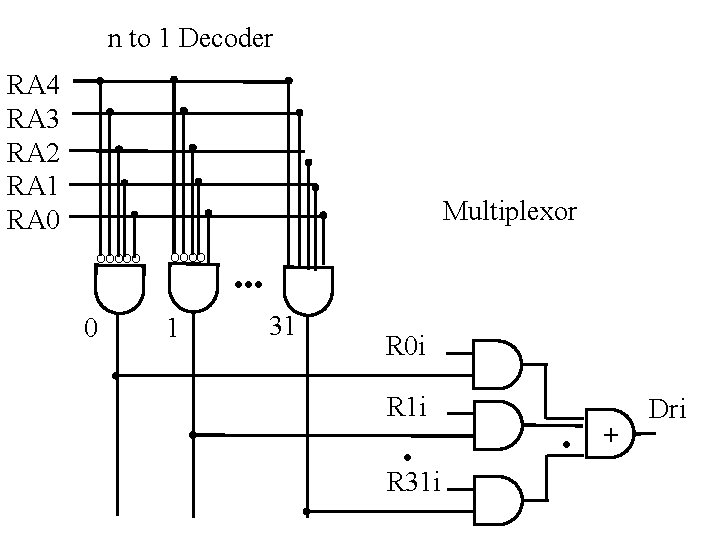

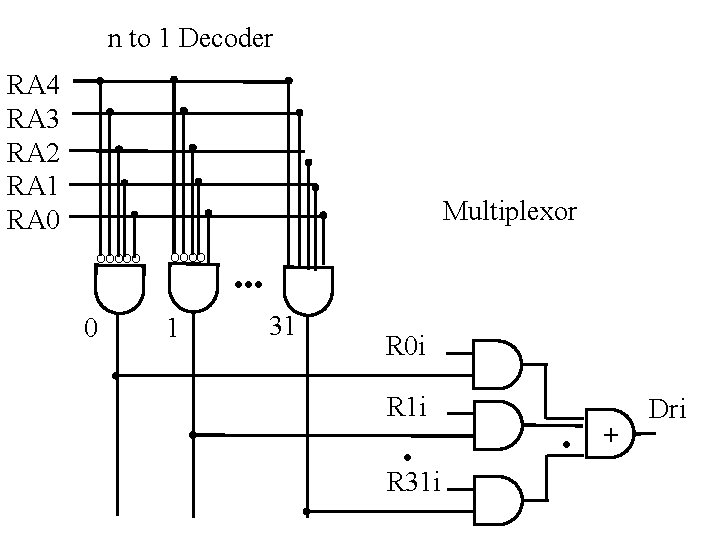

n to 1 Decoder RA 4 RA 3 RA 2 RA 1 RA 0 Multiplexor OOOOO • • • 0 1 31 R 0 i R 1 i • R 31 i • + Dri

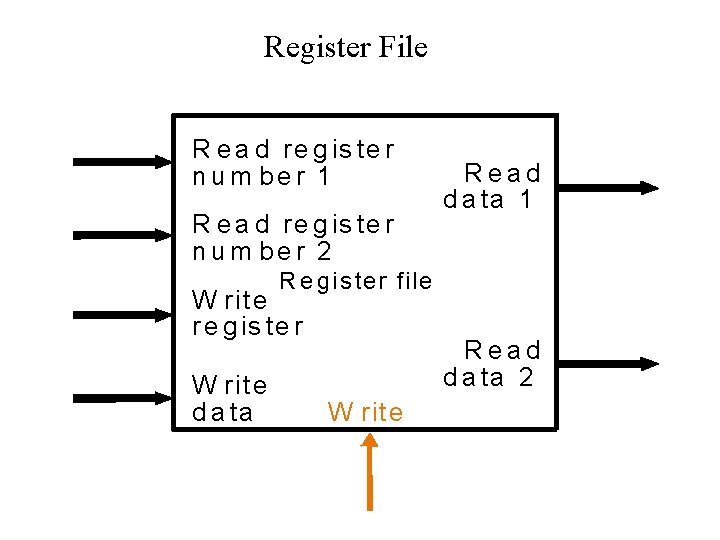

Register File R e a d re g is te r num ber 1 R e a d re g is te r num ber 2 R ead d a ta 1 R e g is te r file W rite re g is te r W rite d a ta R ead d a ta 2 W rit e

R type Arithmetic Logic Instructions add rd, rs, rt R • • op rs rt rd shamt 6 5 5 All R type Instructions Read two registers addressed by rs and rt Write one register addressed by rd R[rs] + R[rt] R[rd] for add funct 6

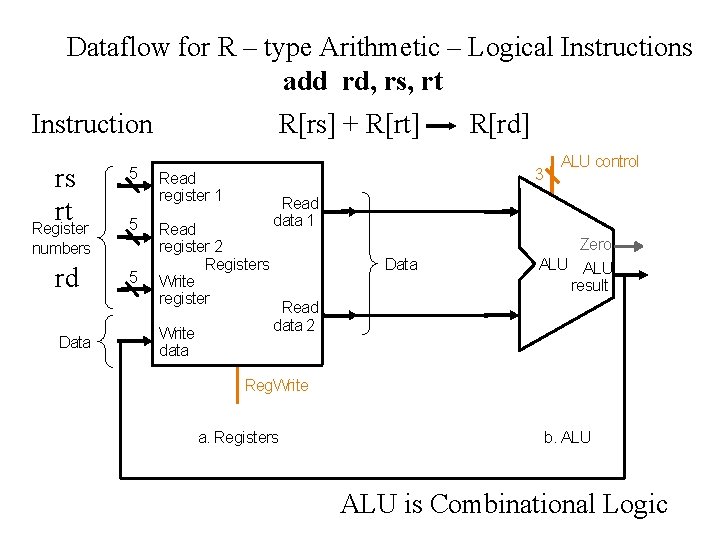

Dataflow for R – type Arithmetic – Logical Instructions add rd, rs, rt Instruction rs rt Register 5 5 numbers rd Data 5 R[rs] + R[rt] 3 Read register 1 Read register 2 Registers Write register Write data R[rd] ALU control Read data 1 Data Zero ALU result Read data 2 Reg. Write a. Registers b. ALU is Combinational Logic

PC Address Next PC Logic Instruction Memory Simplified Overview Instruction Register File Addr ALU Data Memory Out Data In Timing Assumption

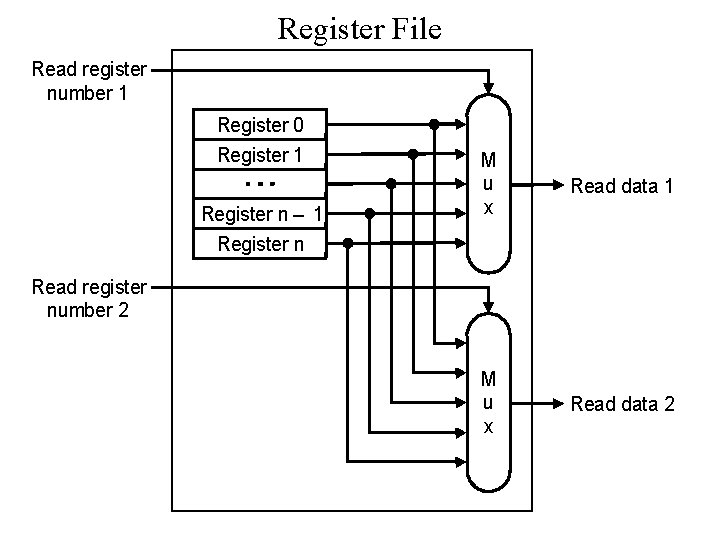

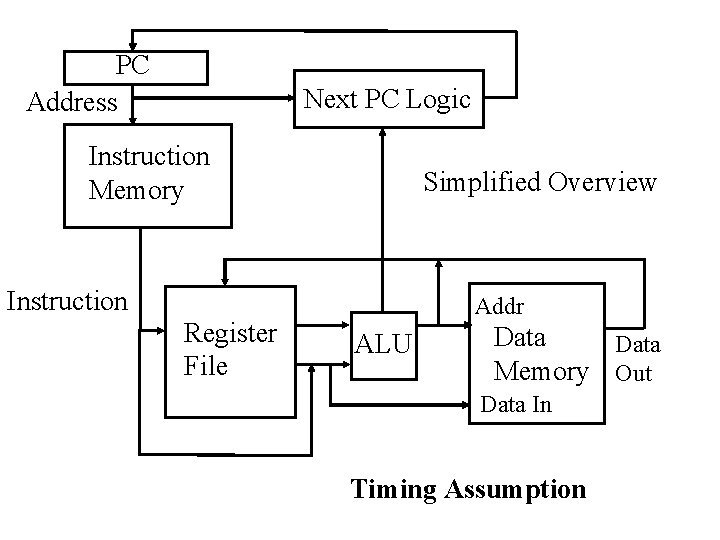

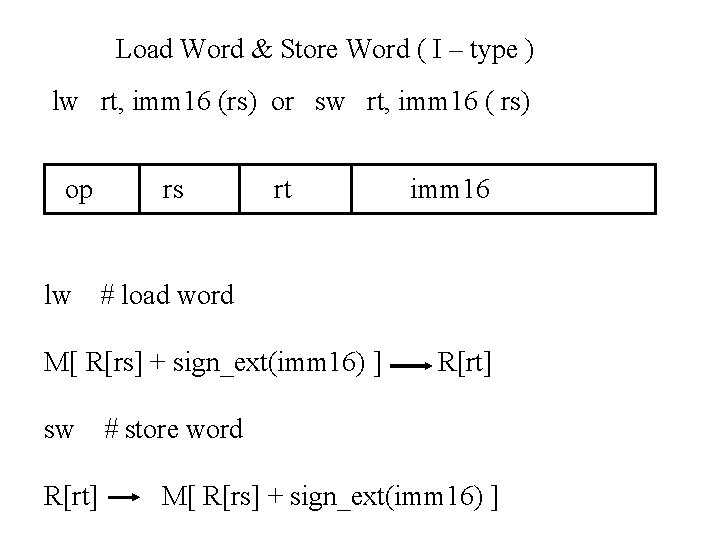

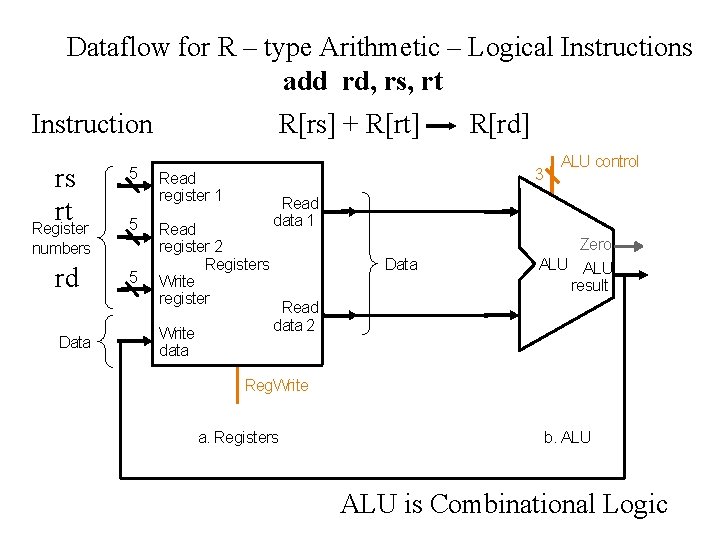

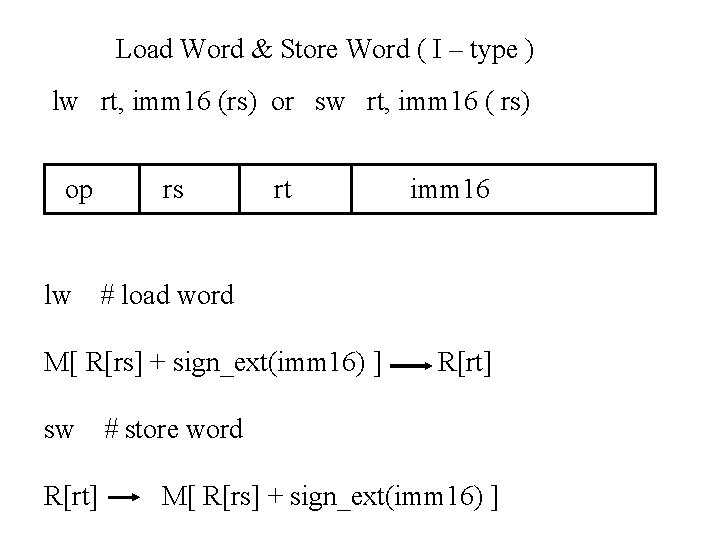

Load Word & Store Word ( I – type ) lw rt, imm 16 (rs) or sw rt, imm 16 ( rs) op lw rs rt # load word M[ R[rs] + sign_ext(imm 16) ] sw R[rt] imm 16 R[rt] # store word M[ R[rs] + sign_ext(imm 16) ]

![load word M Rrs signextimm 16 Registers rs rt R 1 R load word M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 R](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-18.jpg)

load word M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 R 2 Rw Dw imm 16 16 R[rt] Data Memory Dr 1 ALU Addr Dr 2 Dw sign ext 32 Dr

![store word Rrt M Rrs signextimm 16 Registers rs rt R 1 store word R[rt] M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-19.jpg)

store word R[rt] M[ R[rs] + sign_ext(imm 16) ] Registers rs rt R 1 R 2 Rw Dw imm 16 16 Data Memory Dr 1 ALU Addr Dr 2 Dw sign ext 32 Dr

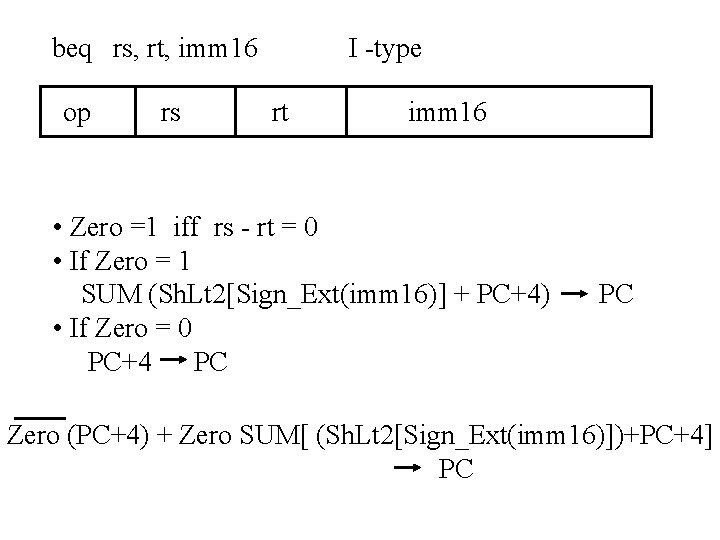

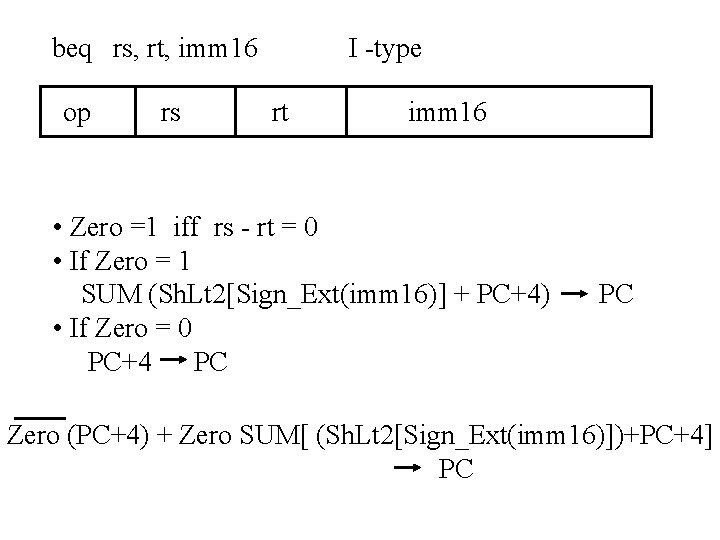

beq rs, rt, imm 16 op rs I -type rt imm 16 • Zero =1 iff rs - rt = 0 • If Zero = 1 SUM (Sh. Lt 2[Sign_Ext(imm 16)] + PC+4) • If Zero = 0 PC+4 PC PC Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC

![Zero PC4 Zero SUM Sh Lt 2SignExtimm 16PC4 PC Ex imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-22.jpg)

Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is 1011 0000 0011 1001

![Zero PC4 Zero SUM Sh Lt 2SignExtimm 16PC4 PC Ex imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-23.jpg)

Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is 1011 0000 0011 1001 Sign_Ext(imm 16) is 1111 1011 0000 0011 1001

![Zero PC4 Zero SUM Sh Lt 2SignExtimm 16PC4 PC Ex imm 16 is Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-24.jpg)

Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] PC Ex: imm 16 is 1011 0000 0011 1001 Sign_Ext(imm 16) is 1111 1011 0000 0011 1001 Sh. Lt 2[Sign_Ext(imm 16)] is 1111 1110 1100 0000 1110 0100

![Zero PC4 Zero SUM Sh Lt 2SignExtimm 16PC4 Zero 1 iff rs Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs -](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-25.jpg)

Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs - rt = 0 PC PC+4 Shift Left 2 branch equal imm 16 16 sign ext 32 ALU Sum to PC

![Zero PC4 Zero SUM Sh Lt 2SignExtimm 16PC4 Zero 1 iff rs Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs -](https://slidetodoc.com/presentation_image/cf7741b1c859307b1dfcd1759bda5a3d/image-26.jpg)

Zero (PC+4) + Zero SUM[ (Sh. Lt 2[Sign_Ext(imm 16)])+PC+4] Zero =1 iff rs - rt = 0 PC PC+4 branch equal Shift Left 2 Registers rs rt R 1 R 2 Rw Dw imm 16 16 ALU op Zero Dr 1 ALU Dr 2 sign ext Sum to PC ALU 32

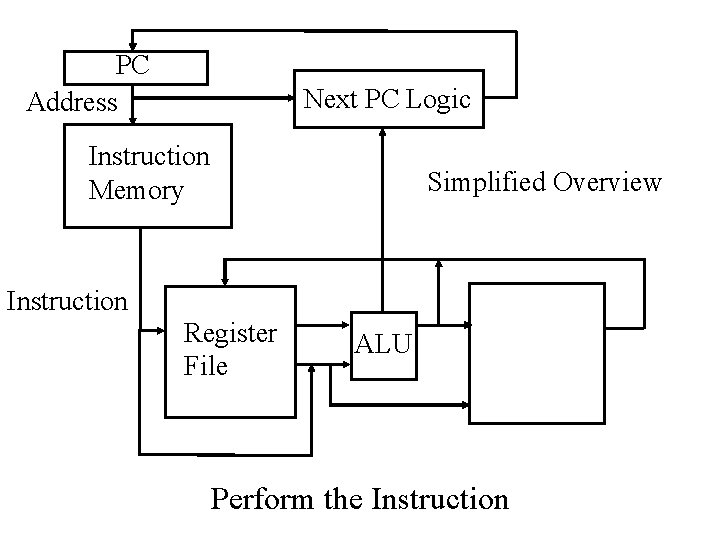

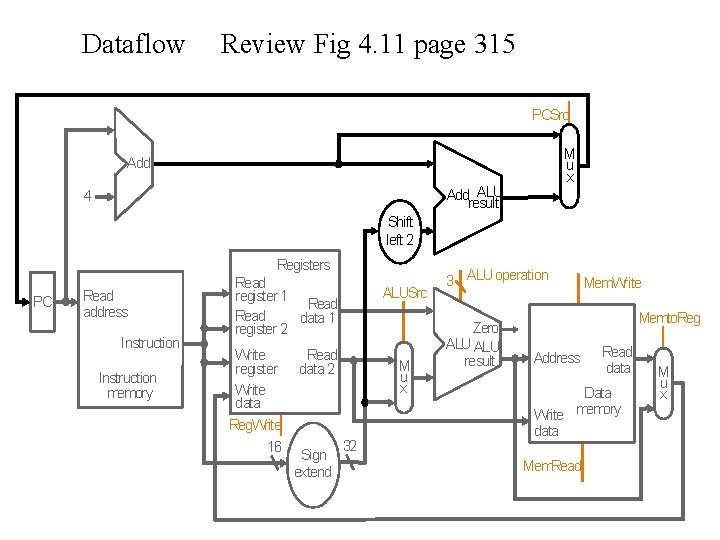

Dataflow Review Fig 4. 11 page 315 PCSrc M u x Add ALU result 4 Shift left 2 Registers PC Read address Instruction memory Read register 1 Read data 1 register 2 Write register Write data Reg. Write 16 ALUSrc Read data 2 Sign extend M u x 32 3 ALU operation Zero ALU result Mem. Write Memto. Reg Address Read data Data Write memory data Mem. Read M u x