Participation BB 130 PLL High Frequency Link 11

Participation à BB 130 PLL, High Frequency Link, 11 -bit SAR ADC Ludovic Raux, Damien Thienpont Mardi 15 mai 2018 Clermont-Ferrand Organization for Micro-Electronics desi. Gn and Applications

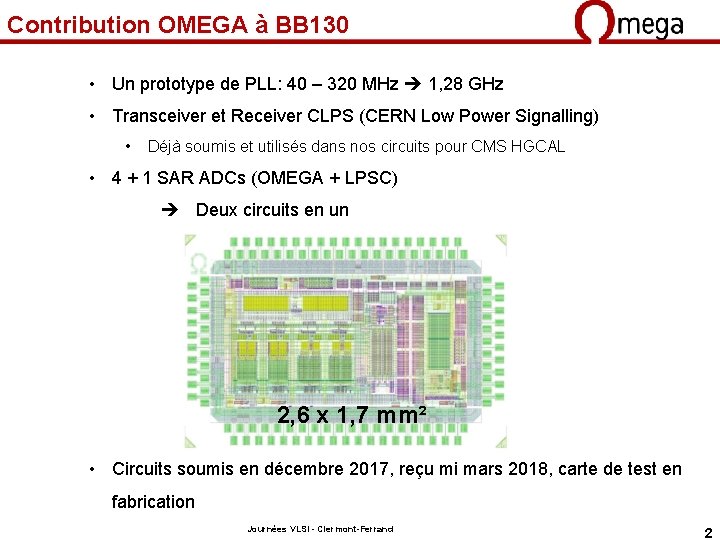

Contribution OMEGA à BB 130 • Un prototype de PLL: 40 – 320 MHz 1, 28 GHz • Transceiver et Receiver CLPS (CERN Low Power Signalling) • Déjà soumis et utilisés dans nos circuits pour CMS HGCAL • 4 + 1 SAR ADCs (OMEGA + LPSC) Deux circuits en un 2, 6 x 1, 7 mm² • Circuits soumis en décembre 2017, reçu mi mars 2018, carte de test en fabrication Journées VLSI - Clermont-Ferrand 2

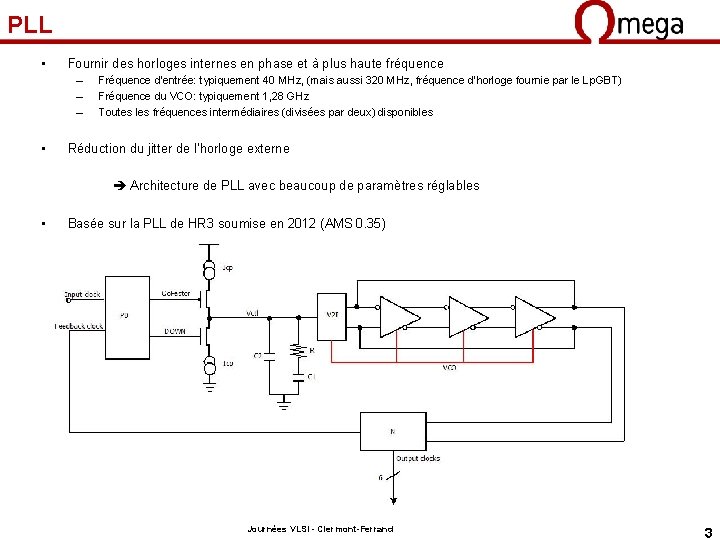

PLL • Fournir des horloges internes en phase et à plus haute fréquence – – – • Fréquence d’entrée: typiquement 40 MHz, (mais aussi 320 MHz, fréquence d’horloge fournie par le Lp. GBT) Fréquence du VCO: typiquement 1, 28 GHz Toutes les fréquences intermédiaires (divisées par deux) disponibles Réduction du jitter de l’horloge externe Architecture de PLL avec beaucoup de paramètres réglables • Basée sur la PLL de HR 3 soumise en 2012 (AMS 0. 35) Journées VLSI - Clermont-Ferrand 3

PLL • Beaucoup de paramètres d’ajustement – La pompe de charge: courant réglable sur 5 bits, bande-passante sur 5 bits – Filtre passe bas • R de 500 à 7500 Ω • C: 100 p. F ou 200 p. F – Gain VCO: 1 bit – Diviseur: 2, 4, 8, 16, 32 – Bit ON/OFF • Testabilité – Toutes les horloges peuvent être sorties – La tension d’entrée du VCO peut être contrôlée/observée de l’extérieur • Toutes les sous parties ont été mises sur du deep N-Well séparés par du substrat haute résistivité • Consommation: 5, 3 m. W (1, 2 V) • Dimension: 320 x 710 µm² Journées VLSI - Clermont-Ferrand 4

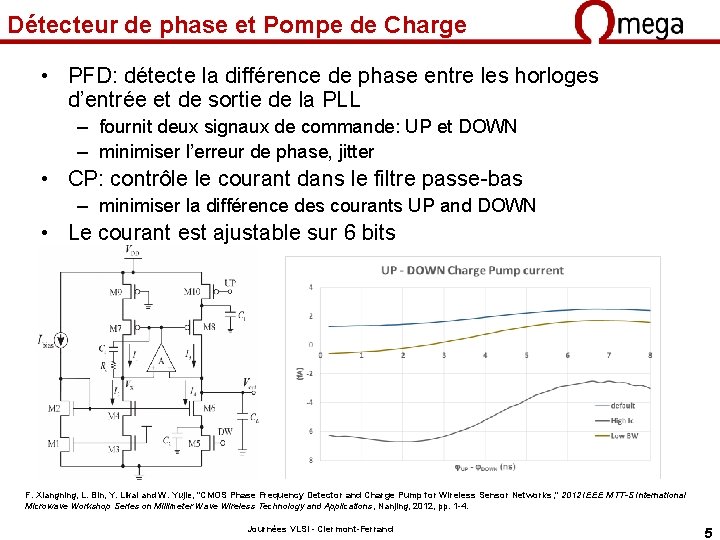

Détecteur de phase et Pompe de Charge • PFD: détecte la différence de phase entre les horloges d’entrée et de sortie de la PLL – fournit deux signaux de commande: UP et DOWN – minimiser l’erreur de phase, jitter • CP: contrôle le courant dans le filtre passe-bas – minimiser la différence des courants UP and DOWN • Le courant est ajustable sur 6 bits F. Xiangning, L. Bin, Y. Likai and W. Yujie, "CMOS Phase Frequency Detector and Charge Pump for Wireless Sensor Networks, " 2012 IEEE MTT-S International Microwave Workshop Series on Millimeter Wave Wireless Technology and Applications, Nanjing, 2012, pp. 1 -4. Journées VLSI - Clermont-Ferrand 5

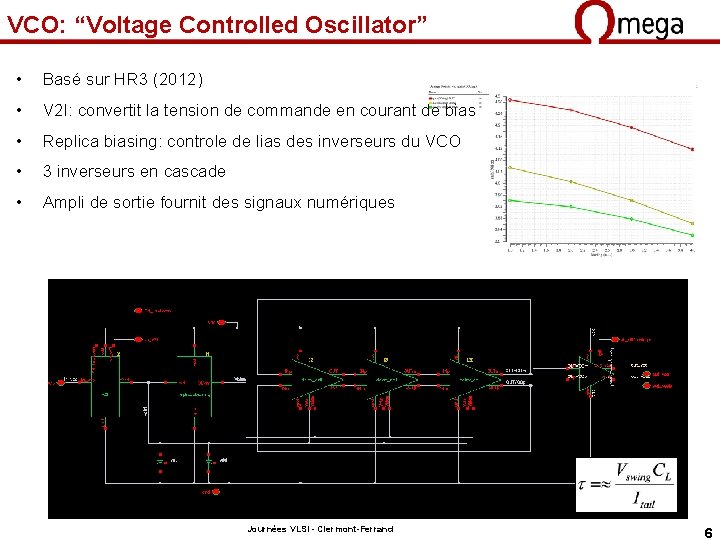

VCO: “Voltage Controlled Oscillator” • Basé sur HR 3 (2012) • V 2 I: convertit la tension de commande en courant de bias • Replica biasing: controle de lias des inverseurs du VCO • 3 inverseurs en cascade • Ampli de sortie fournit des signaux numériques Journées VLSI - Clermont-Ferrand 6

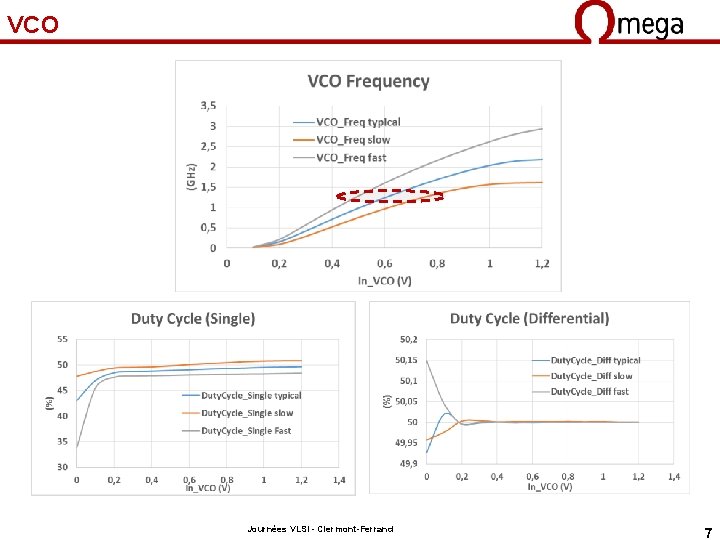

VCO Journées VLSI - Clermont-Ferrand 7

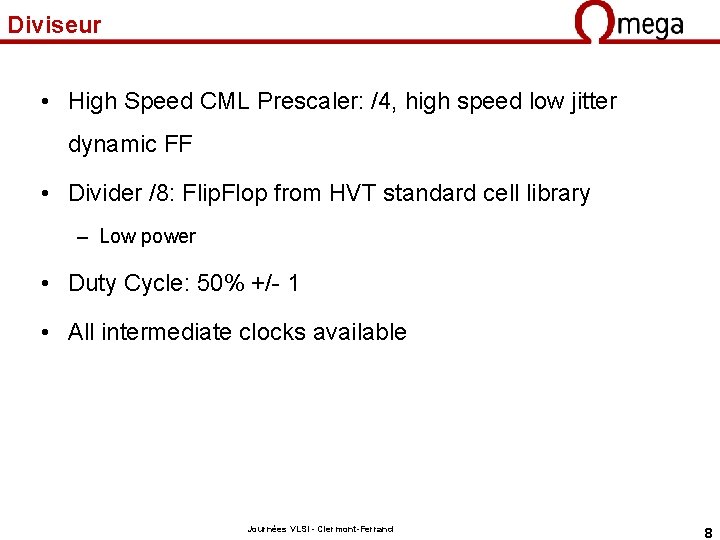

Diviseur • High Speed CML Prescaler: /4, high speed low jitter dynamic FF • Divider /8: Flip. Flop from HVT standard cell library – Low power • Duty Cycle: 50% +/- 1 • All intermediate clocks available Journées VLSI - Clermont-Ferrand 8

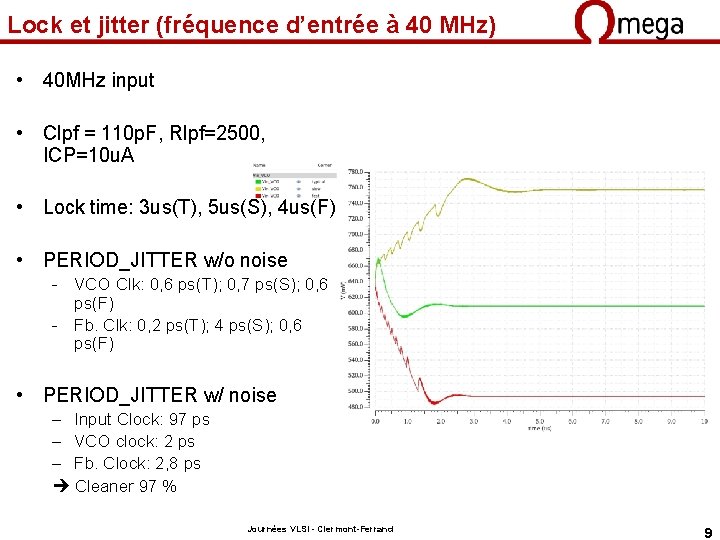

Lock et jitter (fréquence d’entrée à 40 MHz) • 40 MHz input • Clpf = 110 p. F, Rlpf=2500, ICP=10 u. A • Lock time: 3 us(T), 5 us(S), 4 us(F) • PERIOD_JITTER w/o noise - VCO Clk: 0, 6 ps(T); 0, 7 ps(S); 0, 6 ps(F) - Fb. Clk: 0, 2 ps(T); 4 ps(S); 0, 6 ps(F) • PERIOD_JITTER w/ noise – Input Clock: 97 ps – VCO clock: 2 ps – Fb. Clock: 2, 8 ps Cleaner 97 % Journées VLSI - Clermont-Ferrand 9

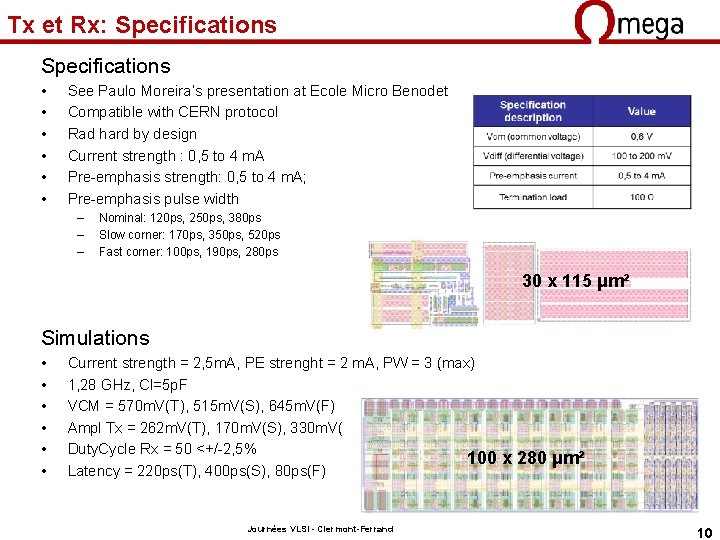

Tx et Rx: Specifications • • • See Paulo Moreira’s presentation at Ecole Micro Benodet Compatible with CERN protocol Rad hard by design Current strength : 0, 5 to 4 m. A Pre-emphasis strength: 0, 5 to 4 m. A; Pre-emphasis pulse width – – – Nominal: 120 ps, 250 ps, 380 ps Slow corner: 170 ps, 350 ps, 520 ps Fast corner: 100 ps, 190 ps, 280 ps 30 x 115 μm² Simulations • • • Current strength = 2, 5 m. A, PE strenght = 2 m. A, PW = 3 (max) 1, 28 GHz, Cl=5 p. F VCM = 570 m. V(T), 515 m. V(S), 645 m. V(F) Ampl Tx = 262 m. V(T), 170 m. V(S), 330 m. V(F) Duty. Cycle Rx = 50 <+/-2, 5% 100 Latency = 220 ps(T), 400 ps(S), 80 ps(F) Journées VLSI - Clermont-Ferrand x 280 μm² 10

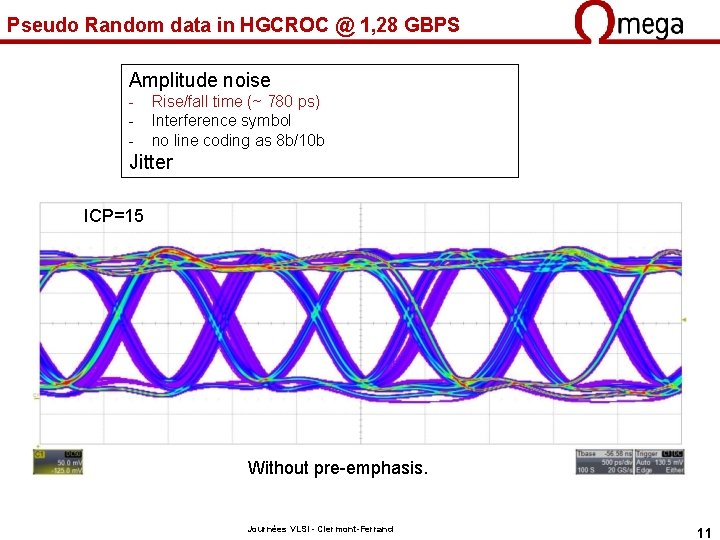

Pseudo Random data in HGCROC @ 1, 28 GBPS Amplitude noise - Rise/fall time (~ 780 ps) Interference symbol no line coding as 8 b/10 b Jitter ICP=15 Without pre-emphasis. Journées VLSI - Clermont-Ferrand 11

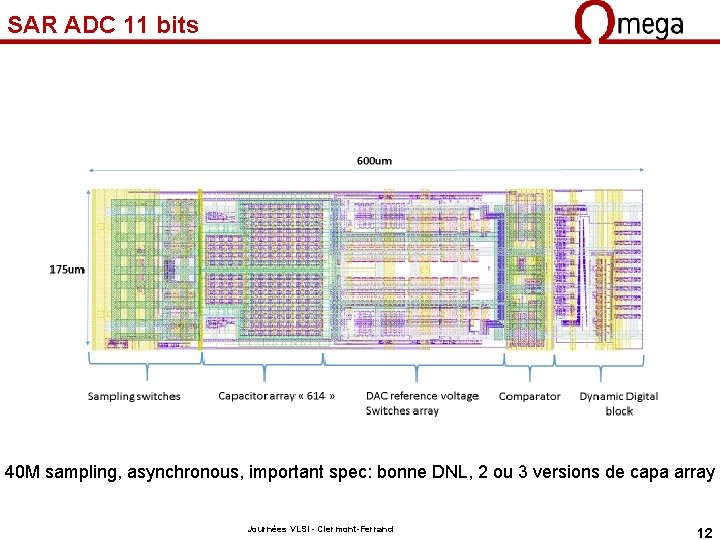

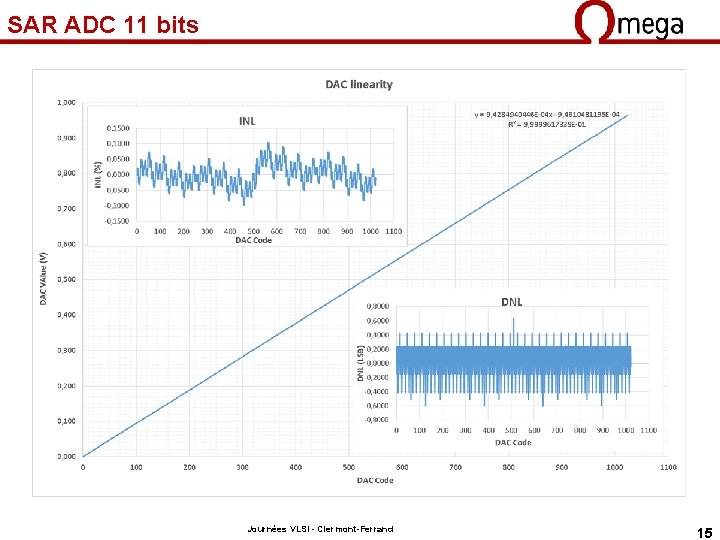

SAR ADC 11 bits 40 M sampling, asynchronous, important spec: bonne DNL, 2 ou 3 versions de capa array Journées VLSI - Clermont-Ferrand 12

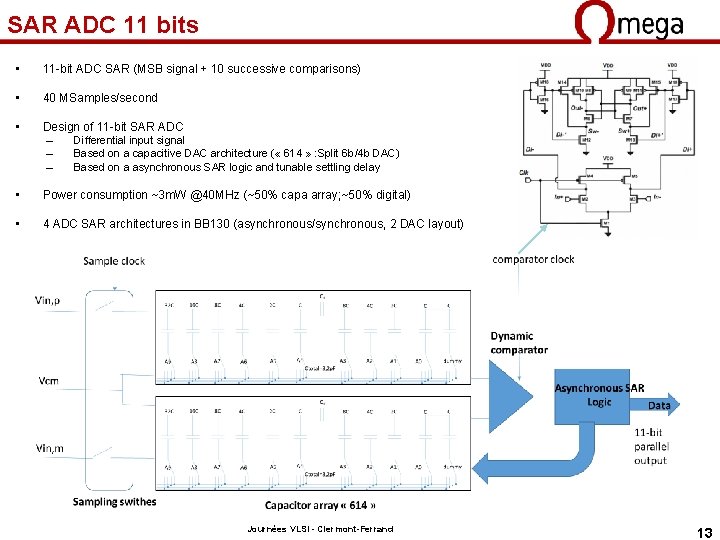

SAR ADC 11 bits • 11 -bit ADC SAR (MSB signal + 10 successive comparisons) • 40 MSamples/second • Design of 11 -bit SAR ADC – Differential input signal – Based on a capacitive DAC architecture ( « 614 » : Split 6 b/4 b DAC) – Based on a asynchronous SAR logic and tunable settling delay • Power consumption ~3 m. W @40 MHz (~50% capa array; ~50% digital) • 4 ADC SAR architectures in BB 130 (asynchronous/synchronous, 2 DAC layout) Journées VLSI - Clermont-Ferrand 13

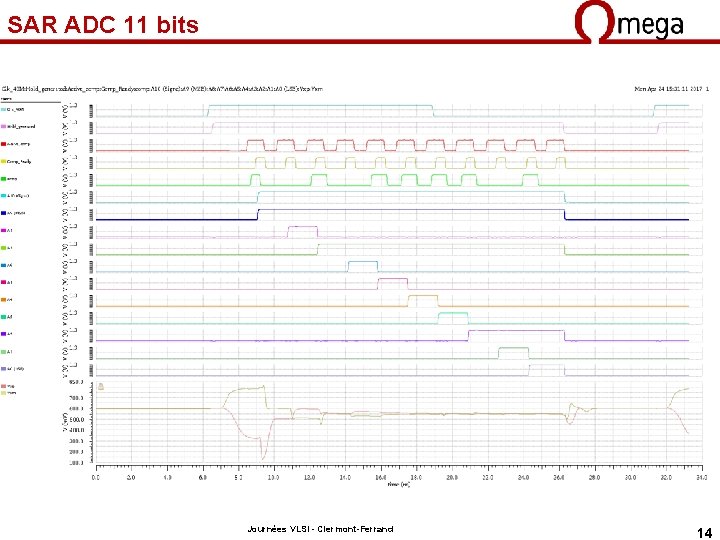

SAR ADC 11 bits Journées VLSI - Clermont-Ferrand 14

SAR ADC 11 bits Journées VLSI - Clermont-Ferrand 15

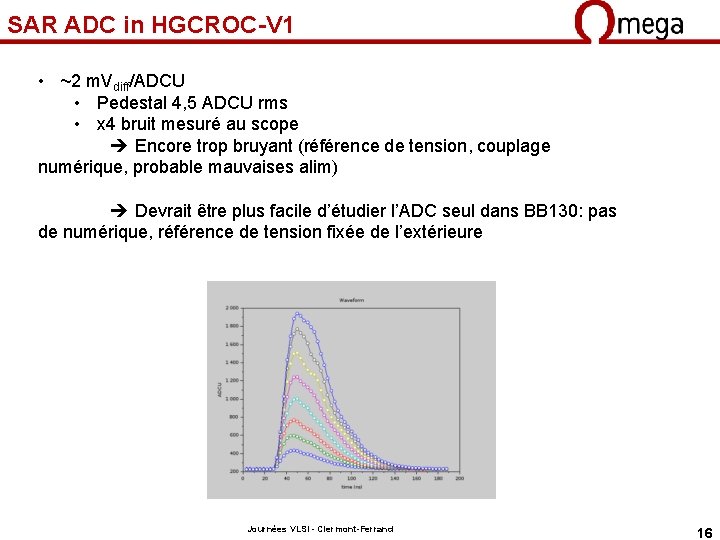

SAR ADC in HGCROC-V 1 • ~2 m. Vdiff/ADCU • Pedestal 4, 5 ADCU rms • x 4 bruit mesuré au scope Encore trop bruyant (référence de tension, couplage numérique, probable mauvaises alim) Devrait être plus facile d’étudier l’ADC seul dans BB 130: pas de numérique, référence de tension fixée de l’extérieure Journées VLSI - Clermont-Ferrand 16

Conclusion • Circuits reçus mi mars – Cartes de test en fabrication • Prototypes de circuits – ADC: intégration des références de tensions – PLL: trop de paramètres de réglage (? ), Détecteur de phase – Transceiver: amélioration du Pre-Emphasis, Rise/Fall time • Datasheet à écrire… Journées VLSI - Clermont-Ferrand 17

- Slides: 17