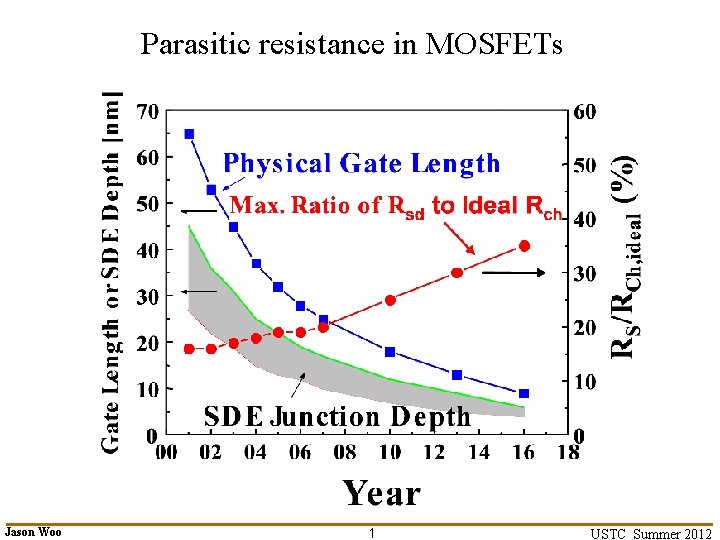

Parasitic resistance in MOSFETs Jason Woo 1 USTC

- Slides: 22

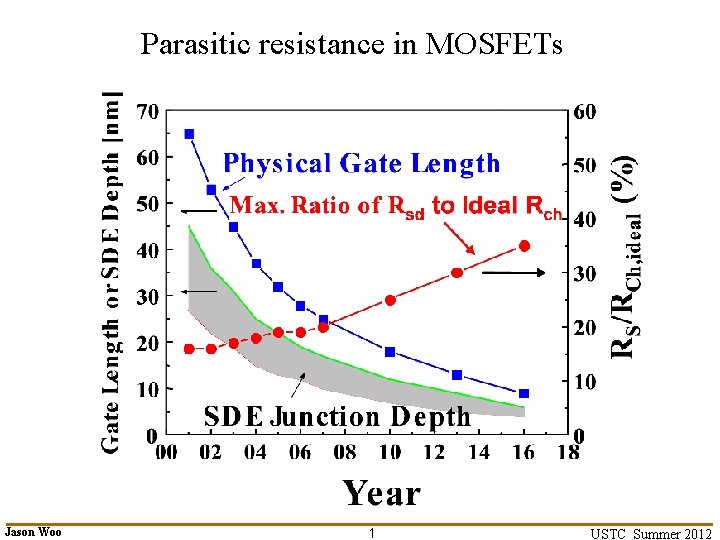

Parasitic resistance in MOSFETs Jason Woo 1 USTC Summer 2012

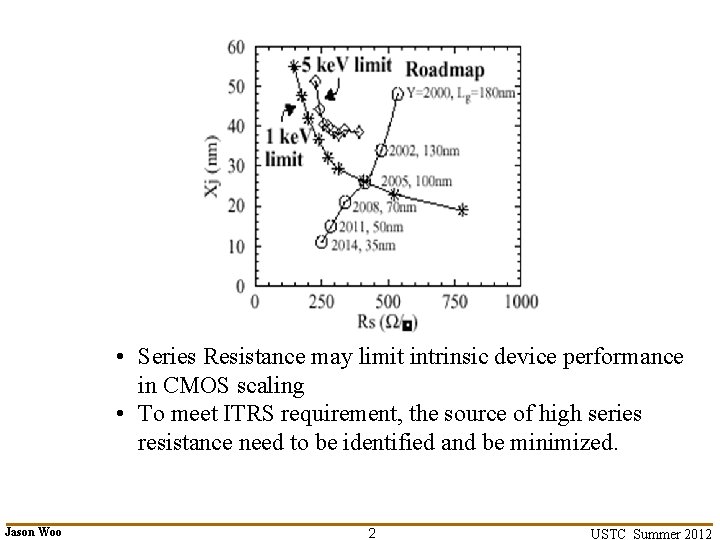

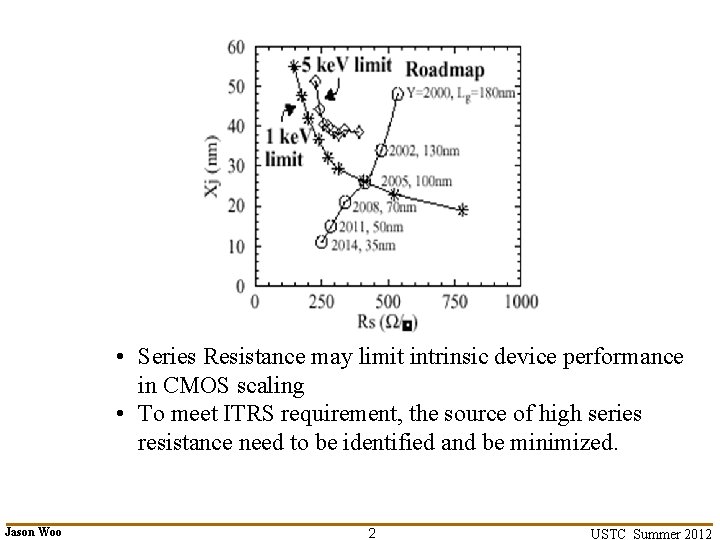

• Series Resistance may limit intrinsic device performance in CMOS scaling • To meet ITRS requirement, the source of high series resistance need to be identified and be minimized. Jason Woo 2 USTC Summer 2012

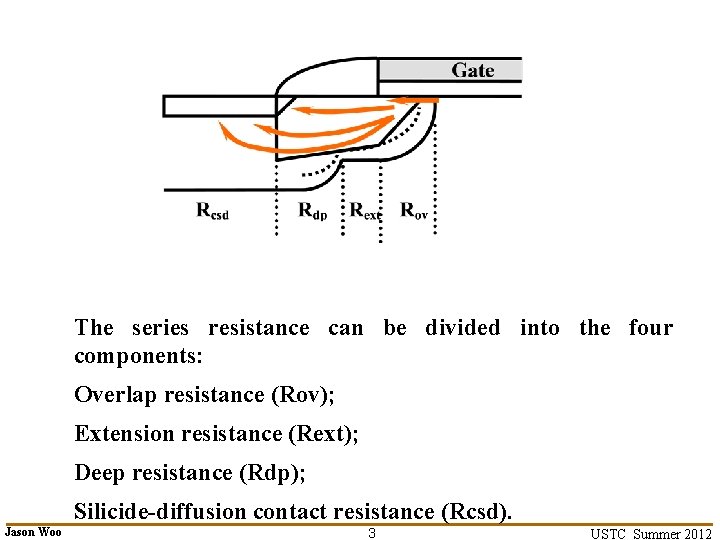

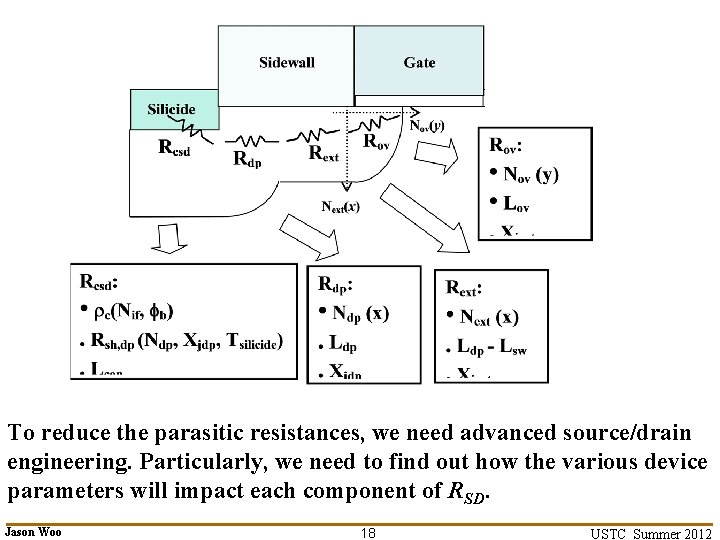

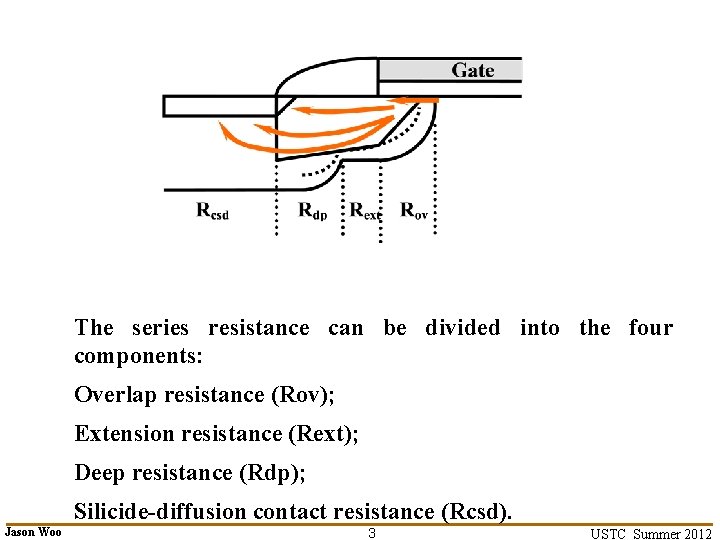

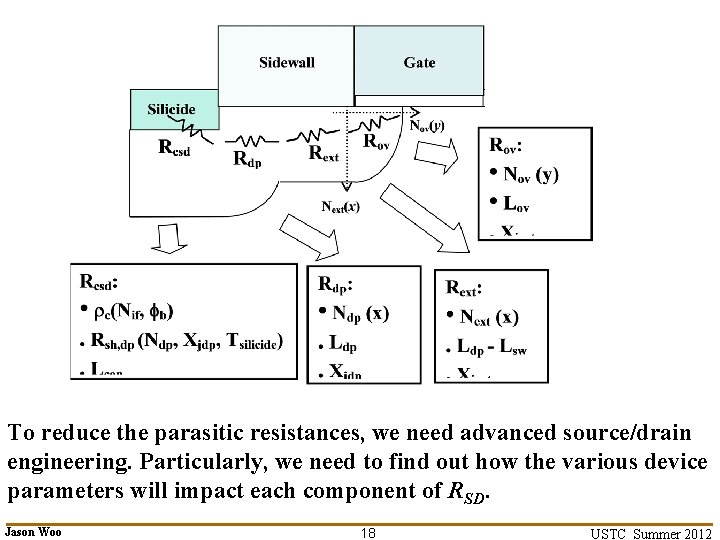

The series resistance can be divided into the four components: Overlap resistance (Rov); Extension resistance (Rext); Deep resistance (Rdp); Silicide-diffusion contact resistance (Rcsd). Jason Woo 3 USTC Summer 2012

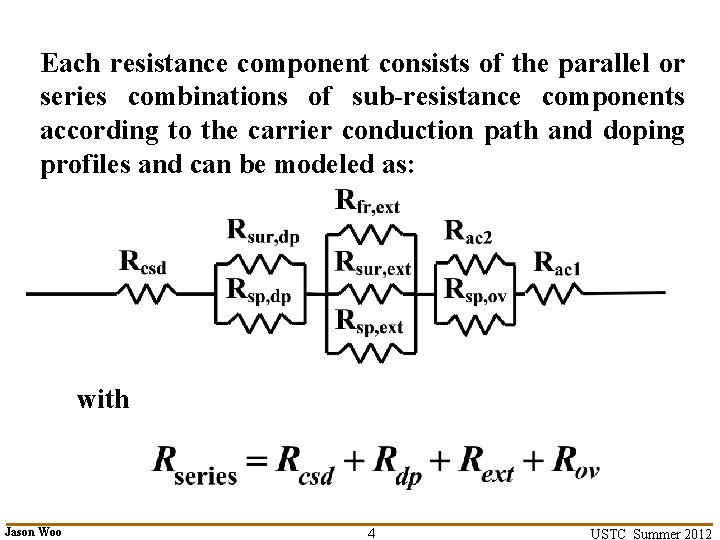

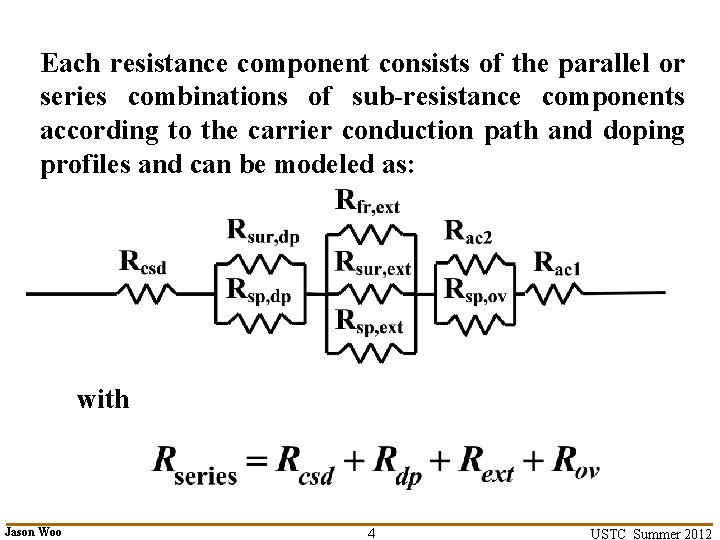

Each resistance component consists of the parallel or series combinations of sub-resistance components according to the carrier conduction path and doping profiles and can be modeled as: with Jason Woo 4 USTC Summer 2012

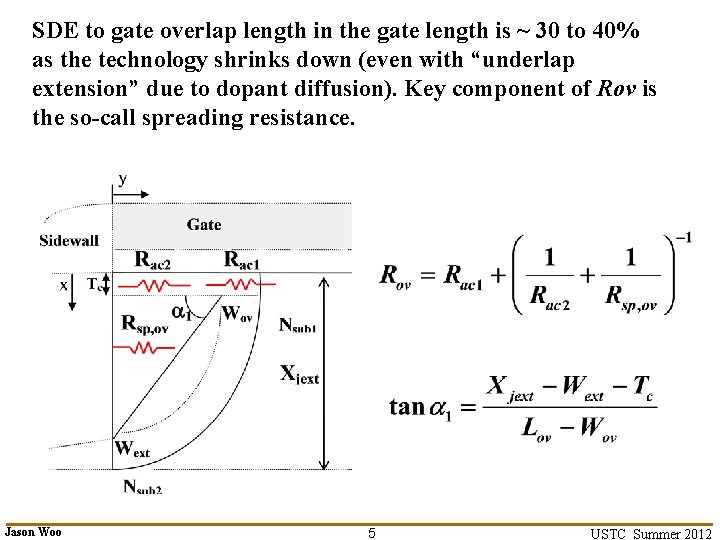

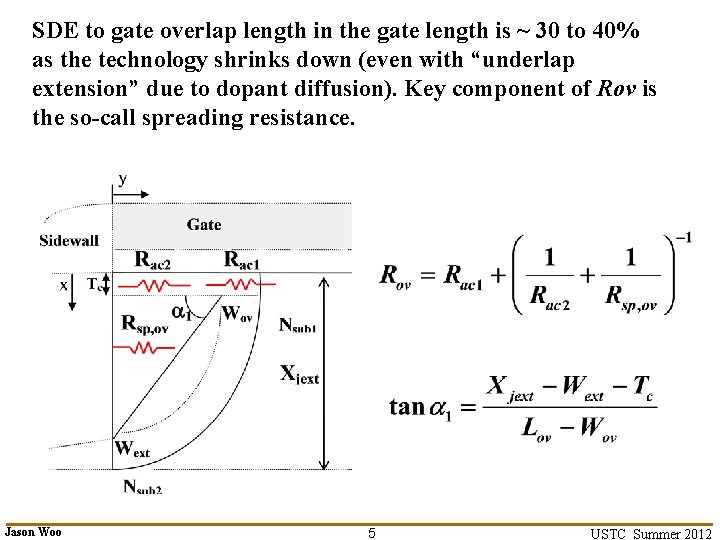

SDE to gate overlap length in the gate length is ~ 30 to 40% as the technology shrinks down (even with “underlap extension” due to dopant diffusion). Key component of Rov is the so-call spreading resistance. Jason Woo 5 USTC Summer 2012

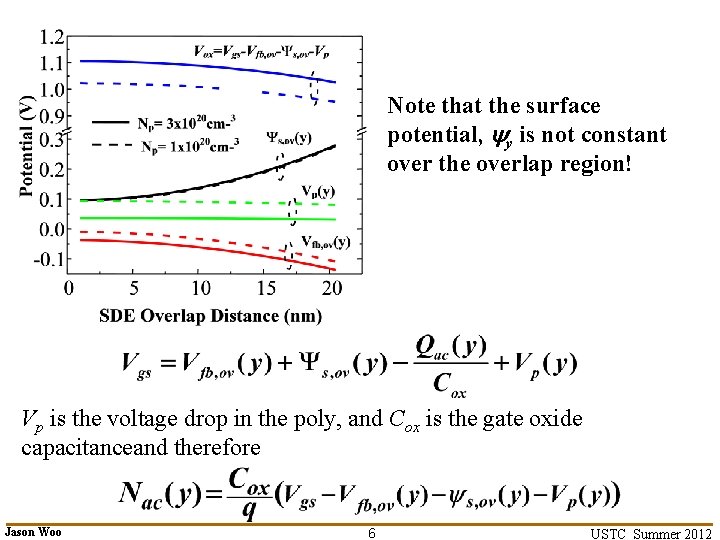

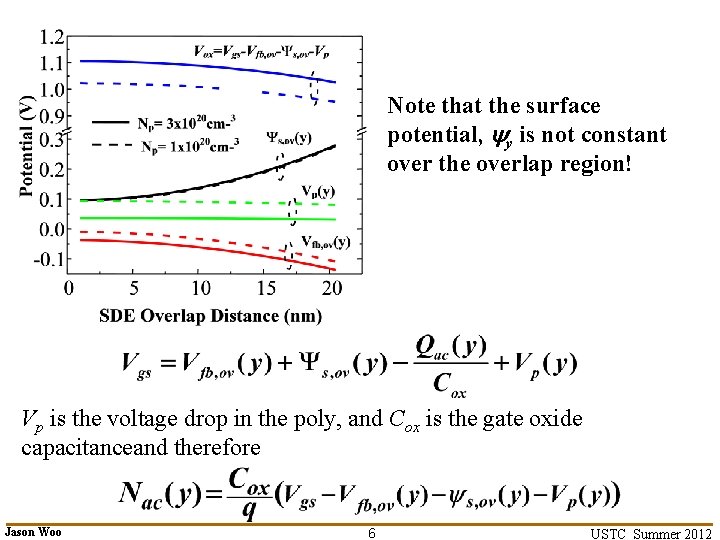

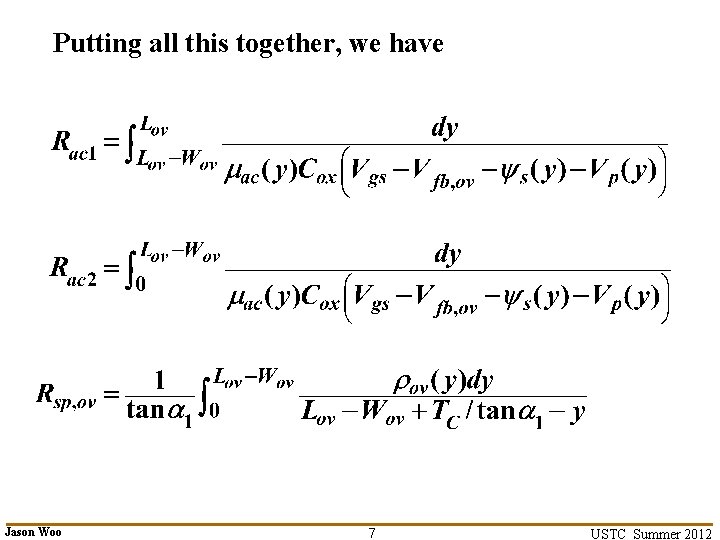

Note that the surface potential, yy is not constant over the overlap region! Vp is the voltage drop in the poly, and Cox is the gate oxide capacitanceand therefore Jason Woo 6 USTC Summer 2012

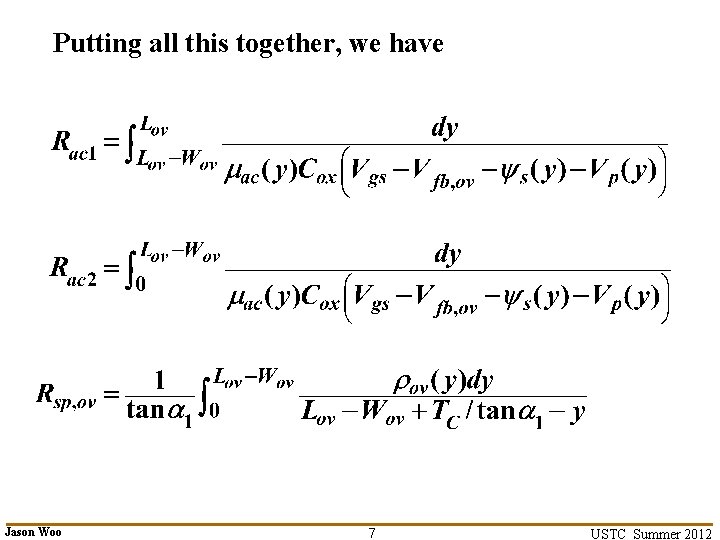

Putting all this together, we have Jason Woo 7 USTC Summer 2012

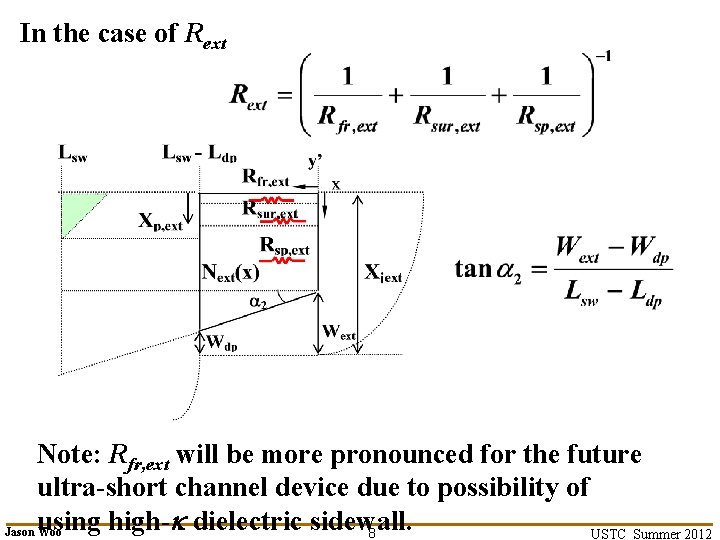

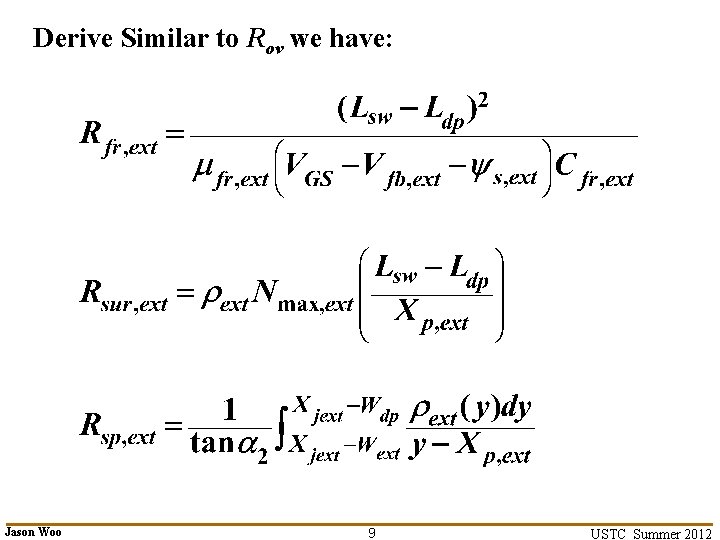

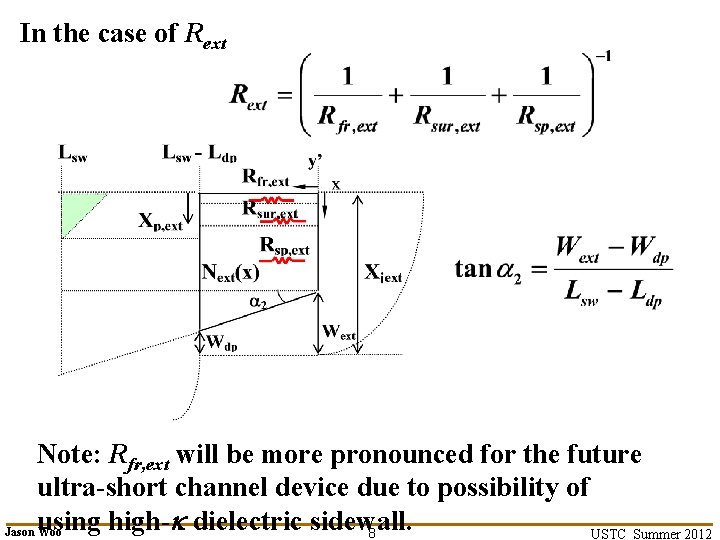

In the case of Rext Note: Rfr, ext will be more pronounced for the future ultra-short channel device due to possibility of using high-k dielectric sidewall. Jason Woo 8 USTC Summer 2012

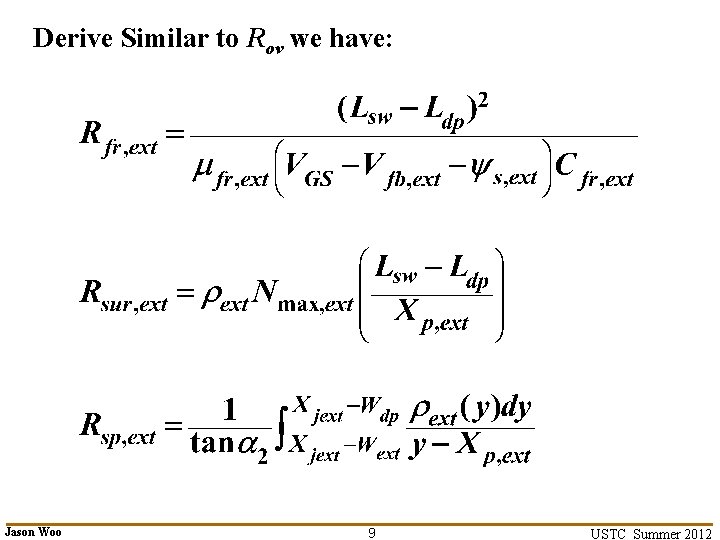

Derive Similar to Rov we have: Jason Woo 9 USTC Summer 2012

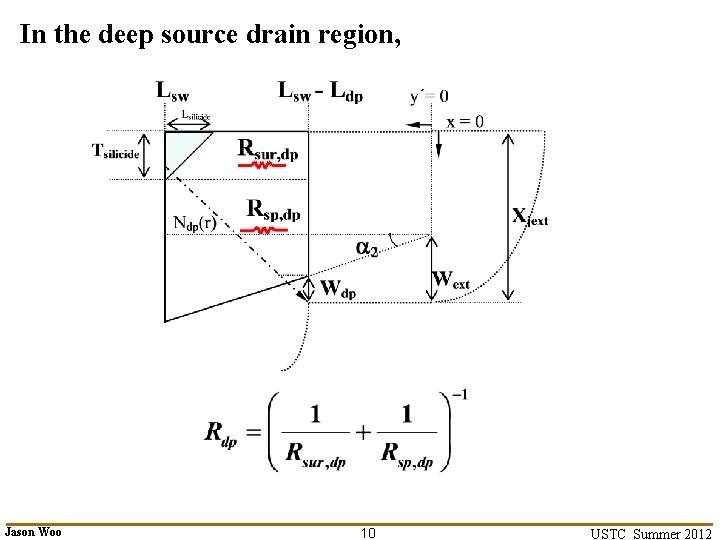

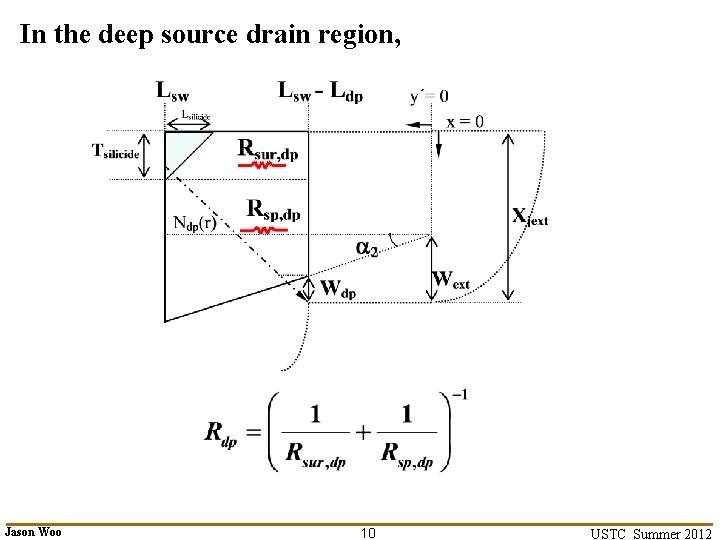

In the deep source drain region, Jason Woo 10 USTC Summer 2012

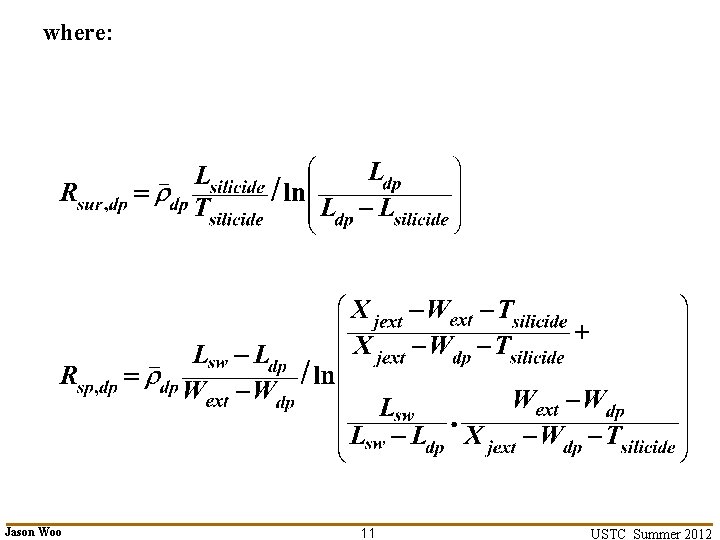

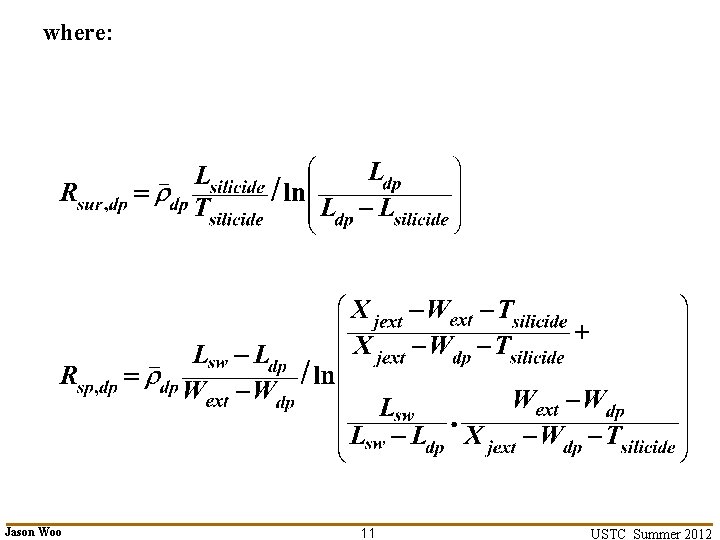

where: Jason Woo 11 USTC Summer 2012

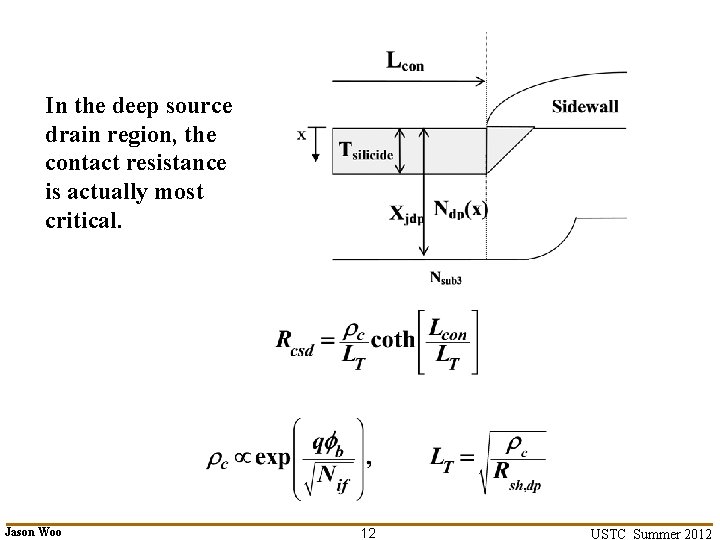

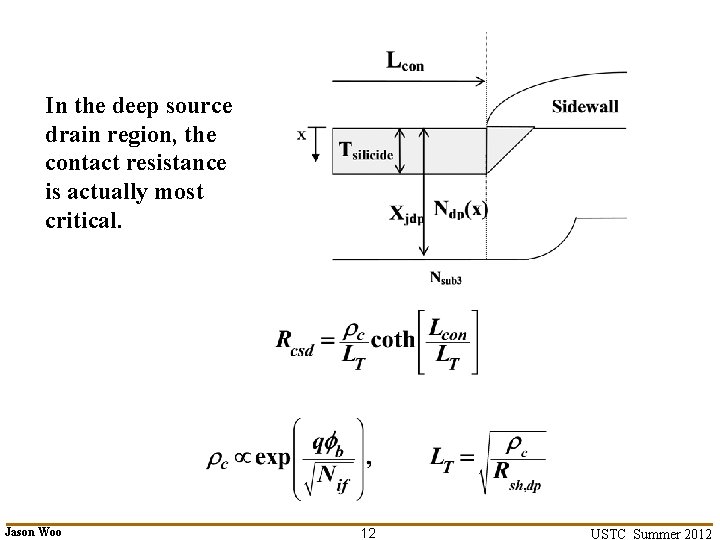

In the deep source drain region, the contact resistance is actually most critical. Jason Woo 12 USTC Summer 2012

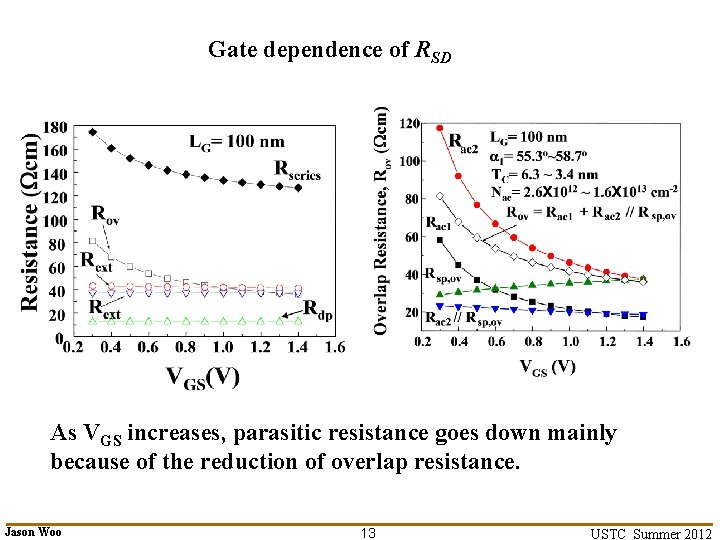

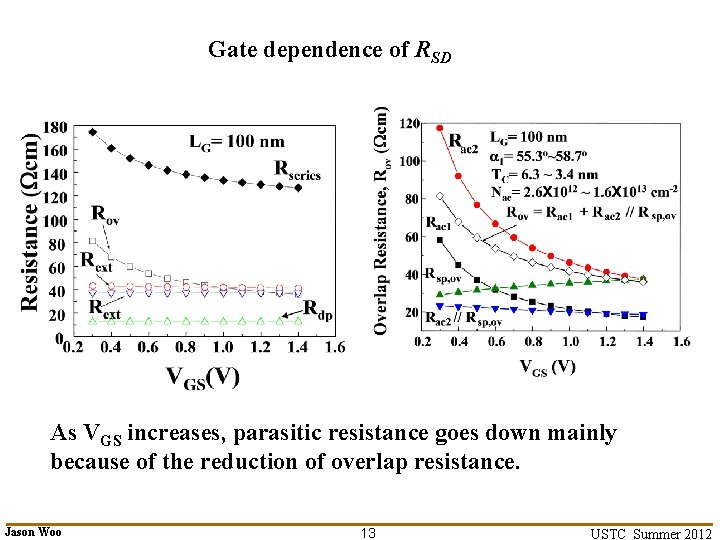

Gate dependence of RSD As VGS increases, parasitic resistance goes down mainly because of the reduction of overlap resistance. Jason Woo 13 USTC Summer 2012

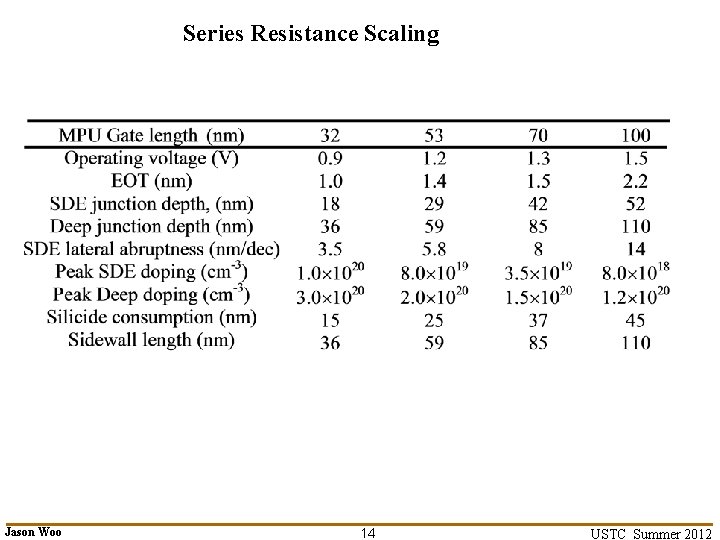

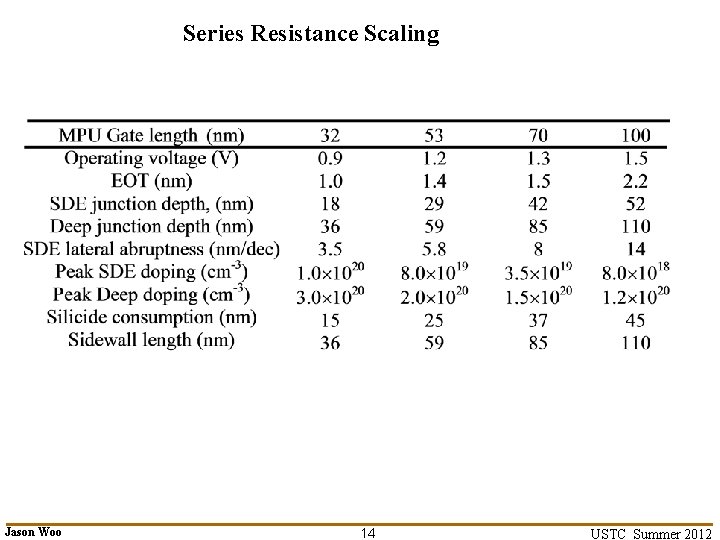

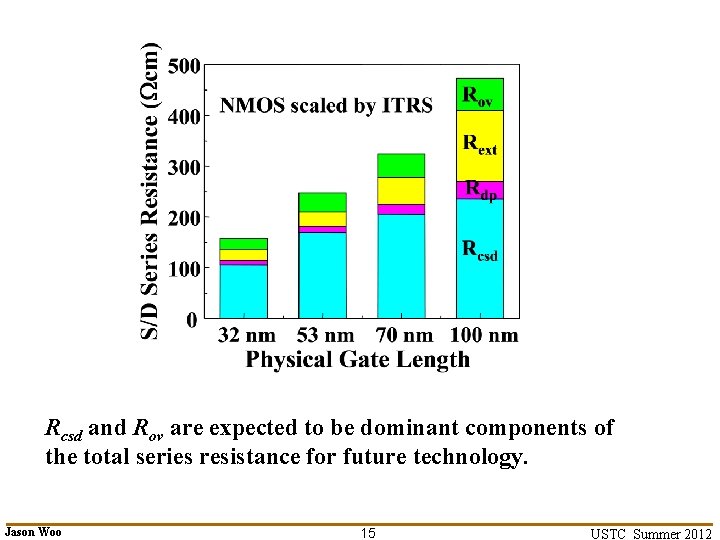

Series Resistance Scaling Jason Woo 14 USTC Summer 2012

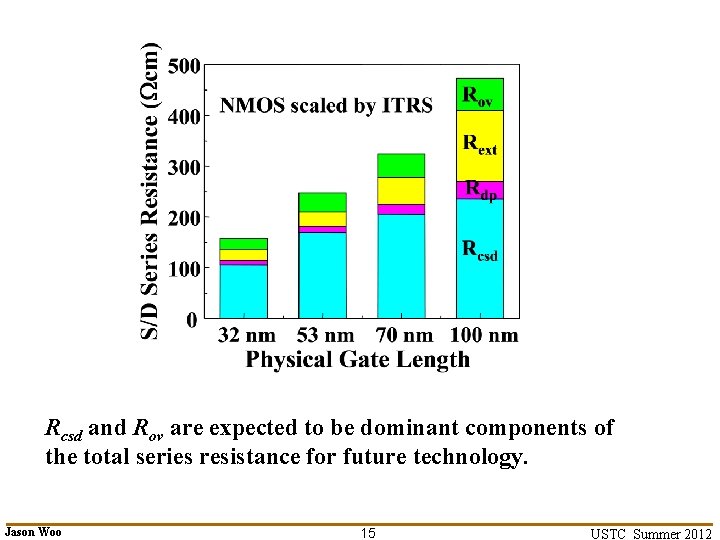

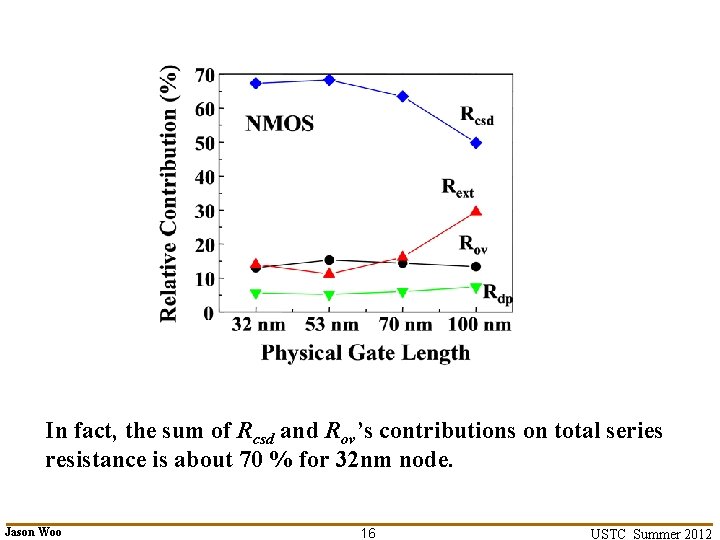

Rcsd and Rov are expected to be dominant components of the total series resistance for future technology. Jason Woo 15 USTC Summer 2012

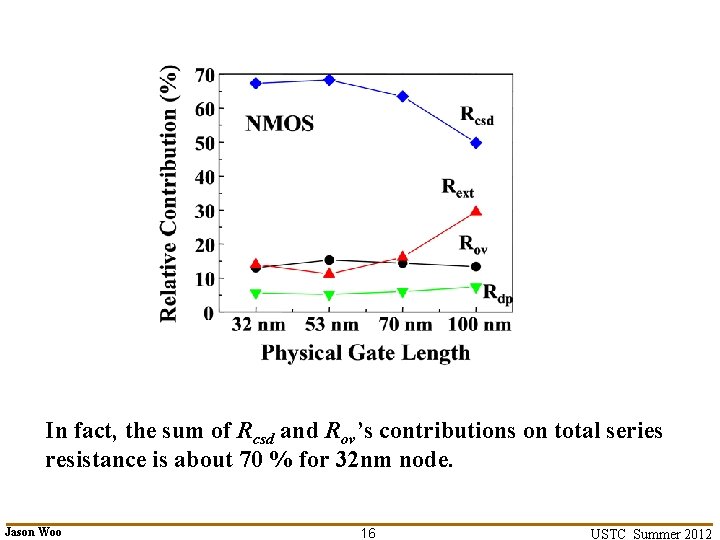

In fact, the sum of Rcsd and Rov’s contributions on total series resistance is about 70 % for 32 nm node. Jason Woo 16 USTC Summer 2012

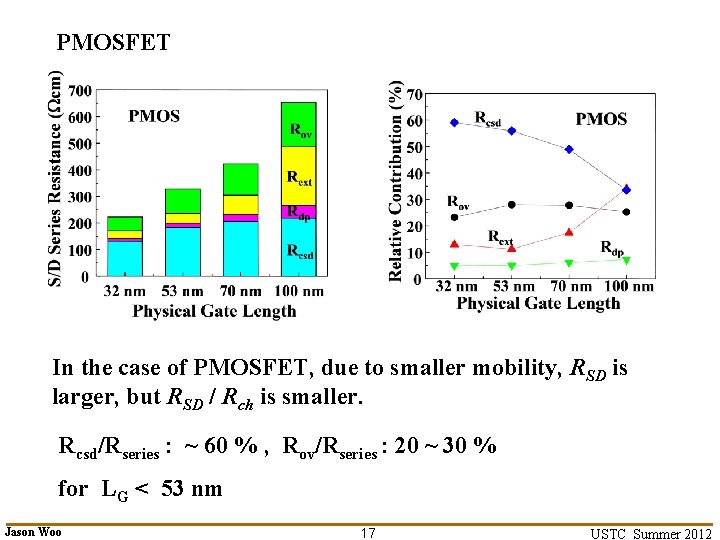

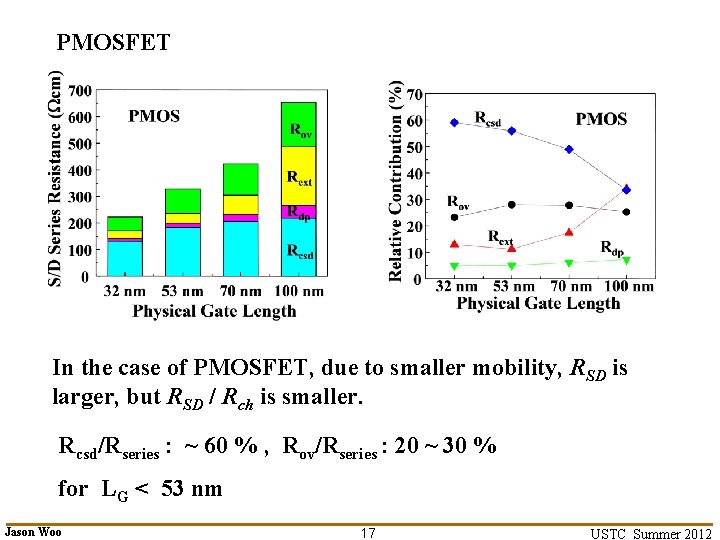

PMOSFET In the case of PMOSFET, due to smaller mobility, RSD is larger, but RSD / Rch is smaller. Rcsd/Rseries : ~ 60 % , Rov/Rseries : 20 ~ 30 % for LG < 53 nm Jason Woo 17 USTC Summer 2012

To reduce the parasitic resistances, we need advanced source/drain engineering. Particularly, we need to find out how the various device parameters will impact each component of RSD. Jason Woo 18 USTC Summer 2012

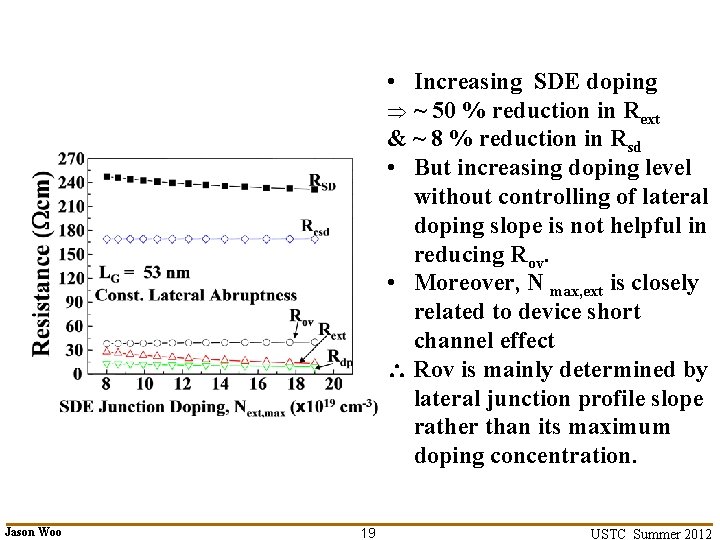

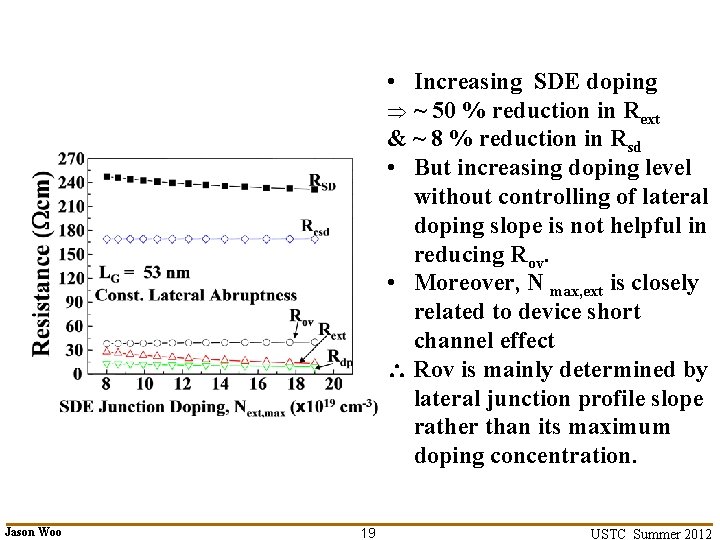

• Increasing SDE doping ~ 50 % reduction in Rext & ~ 8 % reduction in Rsd • But increasing doping level without controlling of lateral doping slope is not helpful in reducing Rov. • Moreover, N max, ext is closely related to device short channel effect Rov is mainly determined by lateral junction profile slope rather than its maximum doping concentration. Jason Woo 19 USTC Summer 2012

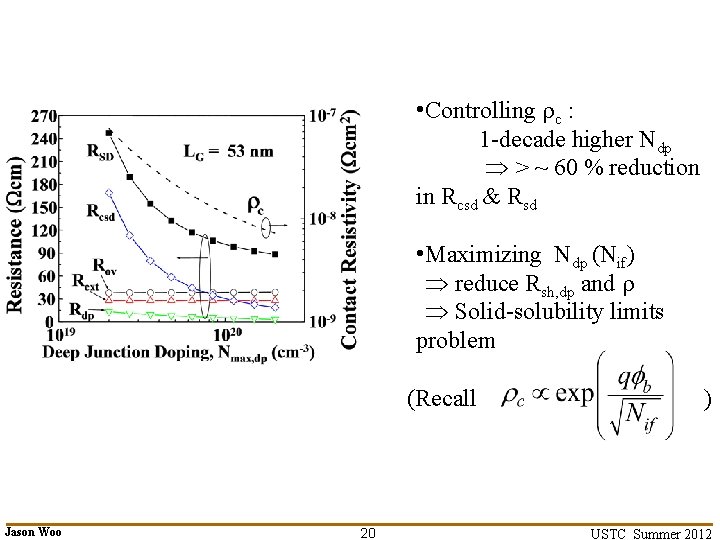

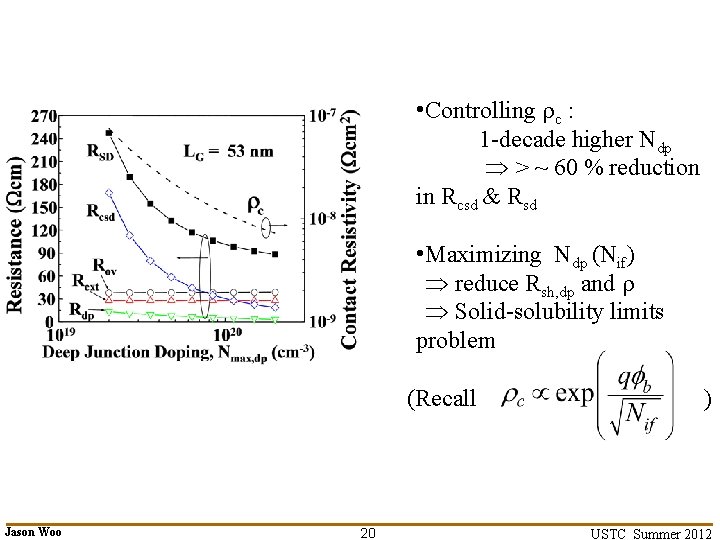

• Controlling c : 1 -decade higher Ndp > ~ 60 % reduction in Rcsd & Rsd • Maximizing Ndp (Nif) reduce Rsh, dp and Solid-solubility limits problem (Recall Jason Woo 20 ) USTC Summer 2012

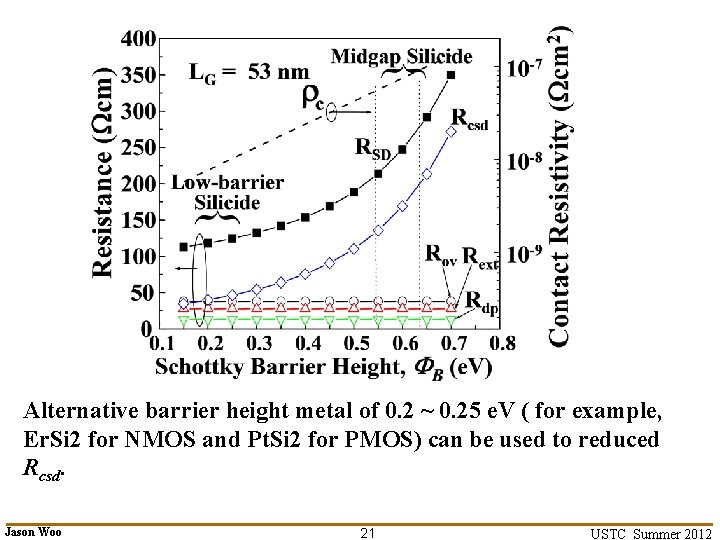

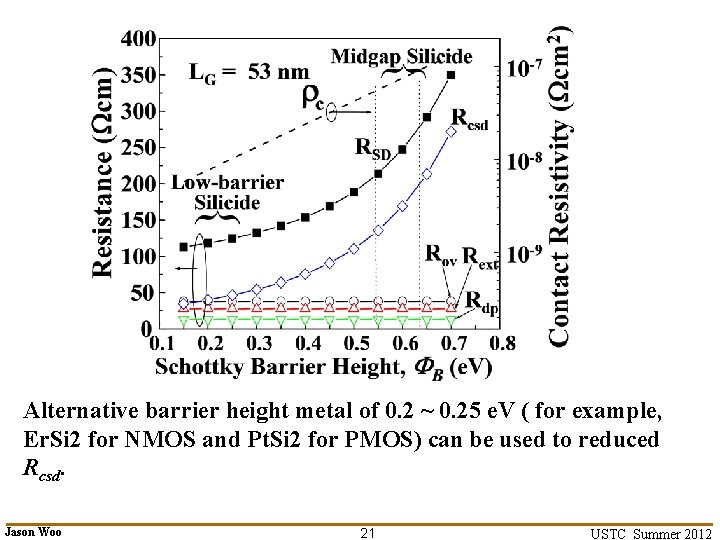

Alternative barrier height metal of 0. 2 ~ 0. 25 e. V ( for example, Er. Si 2 for NMOS and Pt. Si 2 for PMOS) can be used to reduced Rcsd. Jason Woo 21 USTC Summer 2012

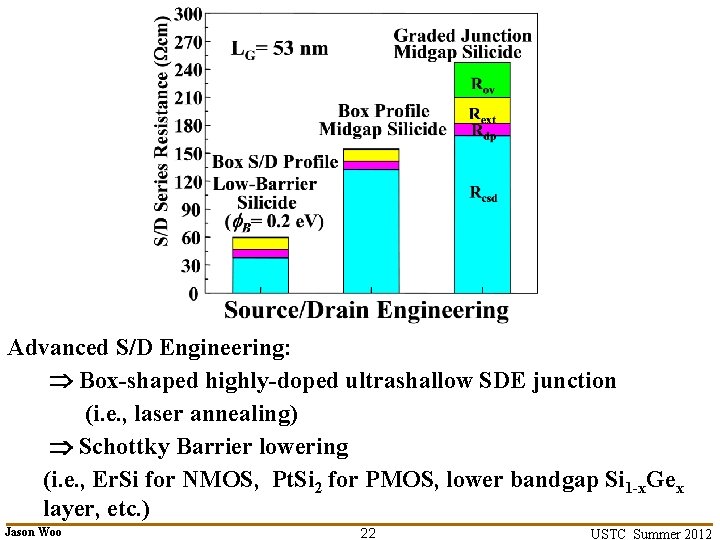

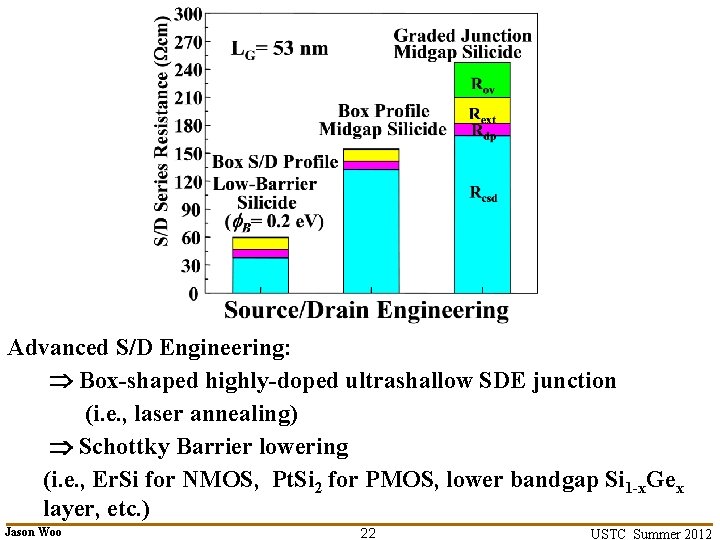

Advanced S/D Engineering: Box-shaped highly-doped ultrashallow SDE junction (i. e. , laser annealing) Schottky Barrier lowering (i. e. , Er. Si for NMOS, Pt. Si 2 for PMOS, lower bandgap Si 1 -x. Gex layer, etc. ) Jason Woo 22 USTC Summer 2012