Pamici Ernest Jamro Kat Elektroniki AGH Pamici klasyfikacja

- Slides: 77

Pamięci Ernest Jamro Kat. Elektroniki AGH

Pamięci - klasyfikacja • ROM (Read Only Memory) - nieulotne (non-volatile) – – – • • ROM (programowany podczas produkcji układu scalonego) PROM (programowane jednorazowo u użytkownika) EPROM (Erasable PROM – możliwa ale uciążliwa wielokrotna programowalność EEPROM (Electrically Erasable and Programmable ROM) Flash (błysk-awiczne EEPROM) RAM (Random Access Memory), Ulotne Pamięci specjalizowane

Pamięci ROM powstają bezpośrednio w procesie produkcji układu scalonego dlatego mają następujące cechy: • Stan pamięci określony na poziomie produkcji układu scalonego • Brak możliwości zmiany zawartości pamięci • Tanie w produkcji ale wymagają dużych nakładów (wykonania w milionach sztuk – drogie przy małej liczbie sztuk) • Długi okres produkcji – kilkanaście tygodni. • Pamięci coraz rzadziej stosowane

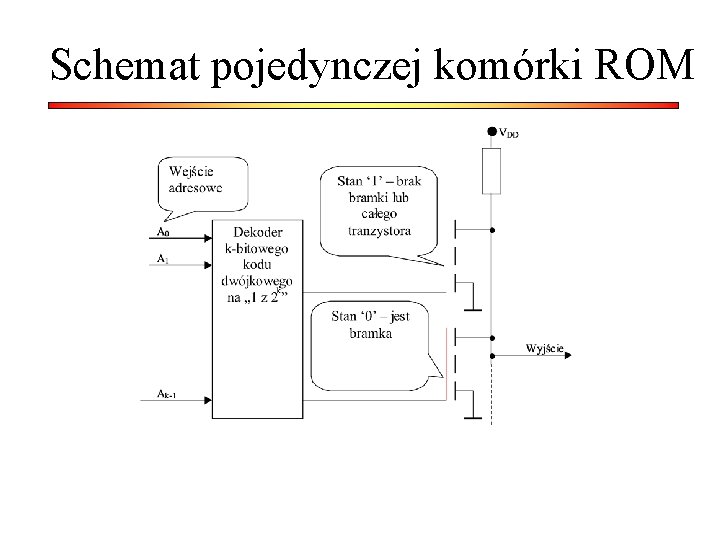

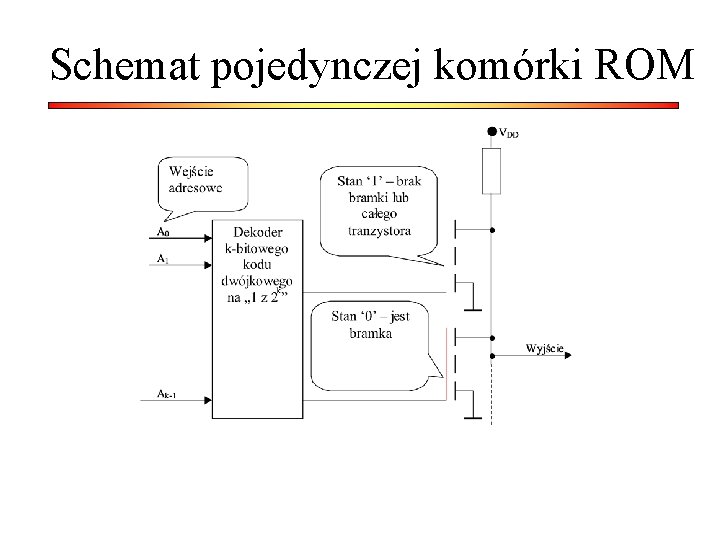

Schemat pojedynczej komórki ROM

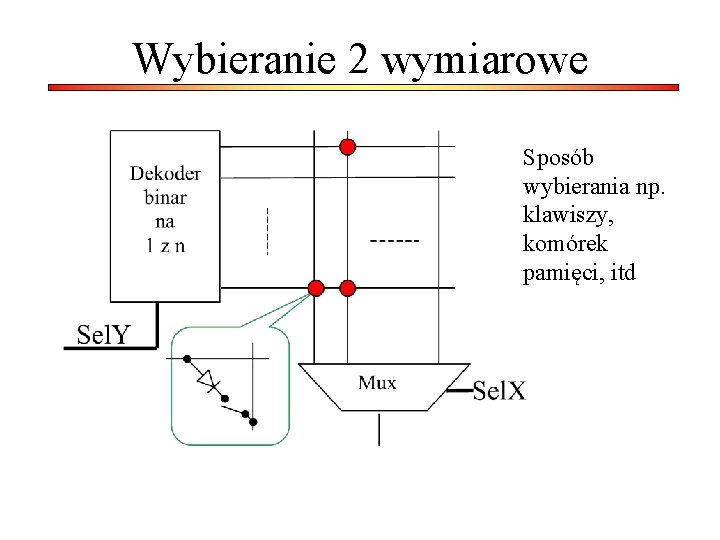

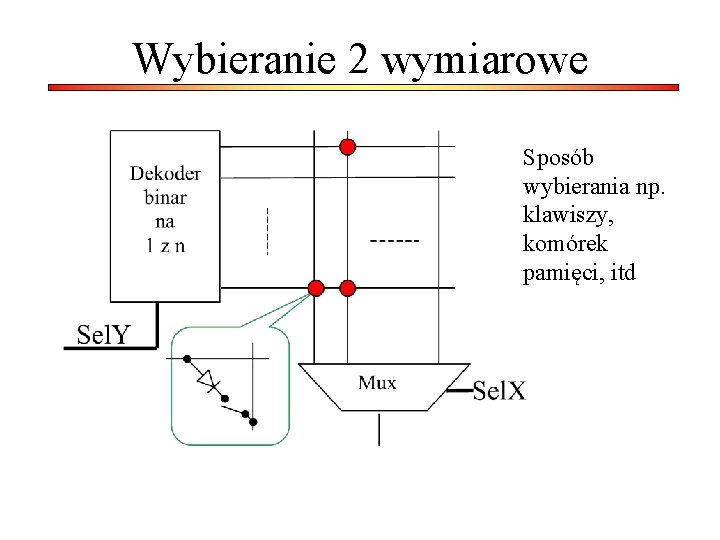

Wybieranie 2 wymiarowe Sposób wybierania np. klawiszy, komórek pamięci, itd

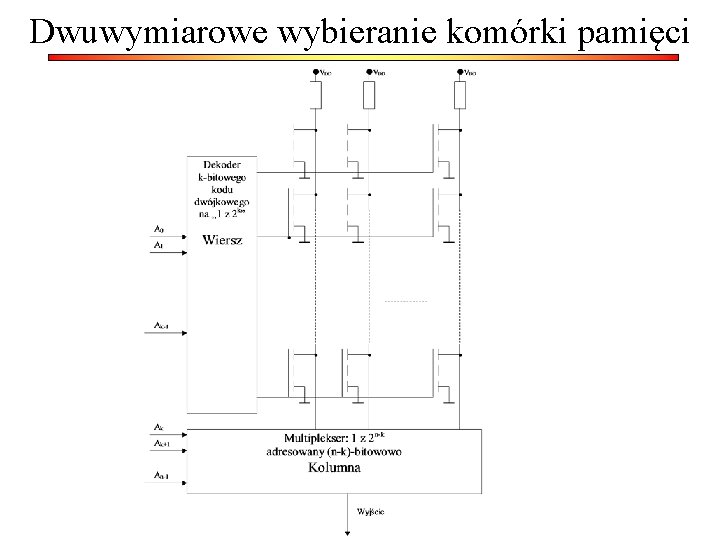

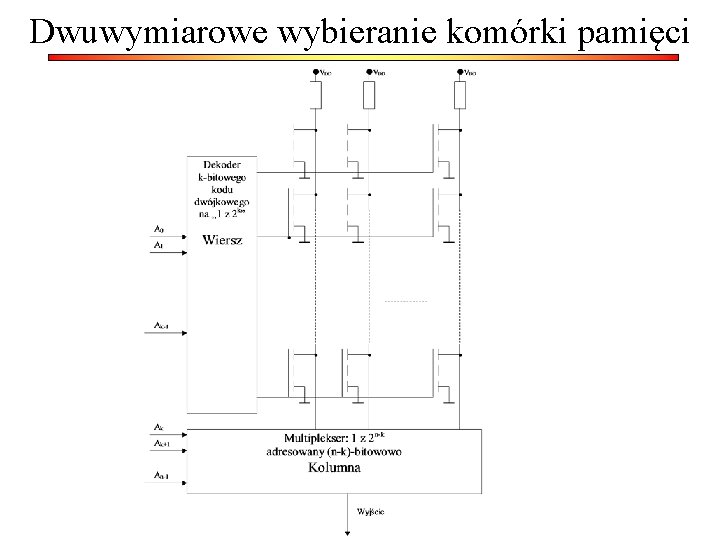

Dwuwymiarowe wybieranie komórki pamięci

Pamięci PROM Programmable Read Only Memory: Programowanie pamięci wykonywane jest przez użytkownika w specjalnym urządzeniu programującym. Programowanie następuje poprzez przepalenie tzw. bezpieczników (ang. fuse) i jest nieodwracalne. Pamięci te są dzisiaj rzadko stosowane

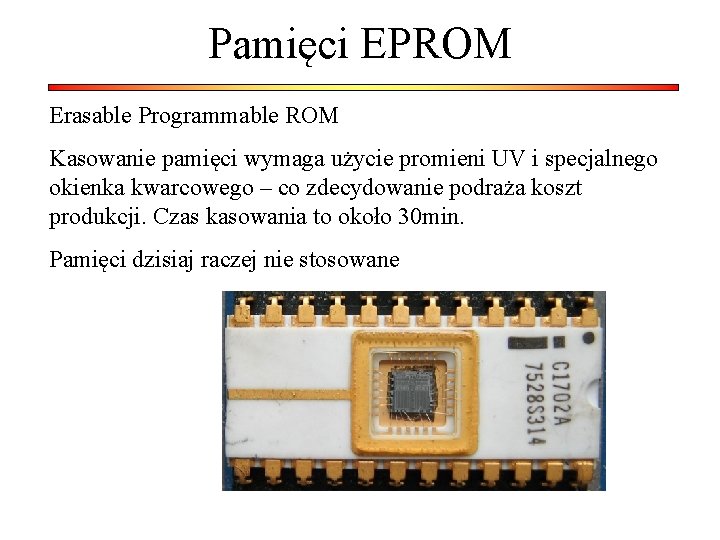

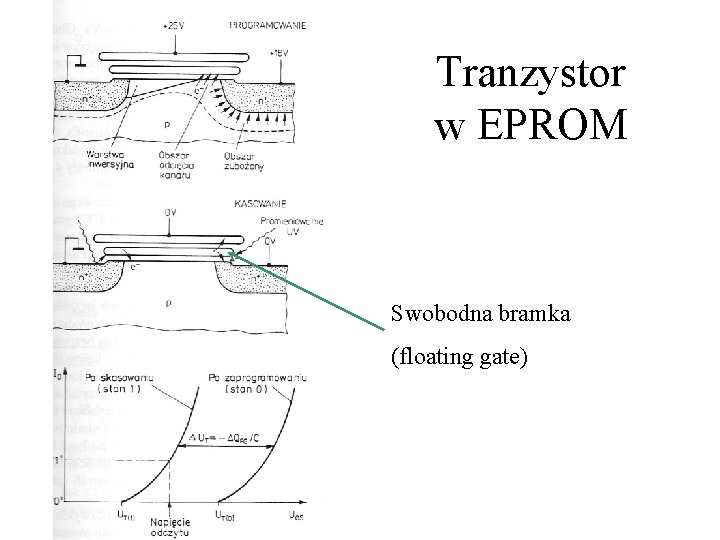

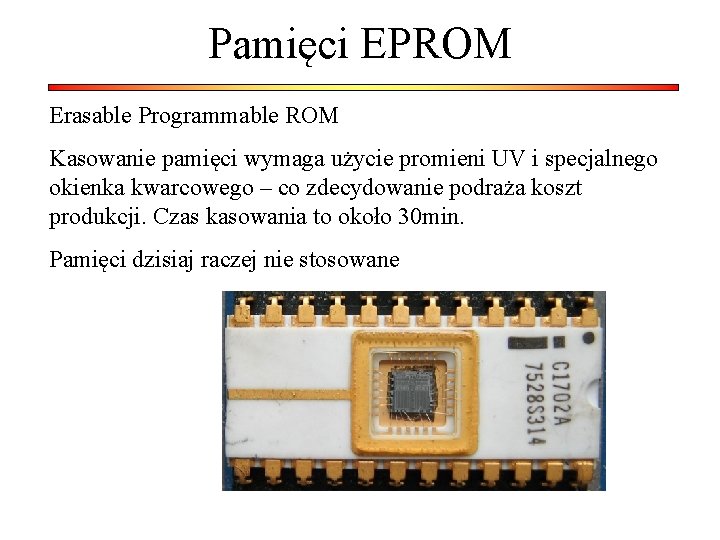

Pamięci EPROM Erasable Programmable ROM Kasowanie pamięci wymaga użycie promieni UV i specjalnego okienka kwarcowego – co zdecydowanie podraża koszt produkcji. Czas kasowania to około 30 min. Pamięci dzisiaj raczej nie stosowane

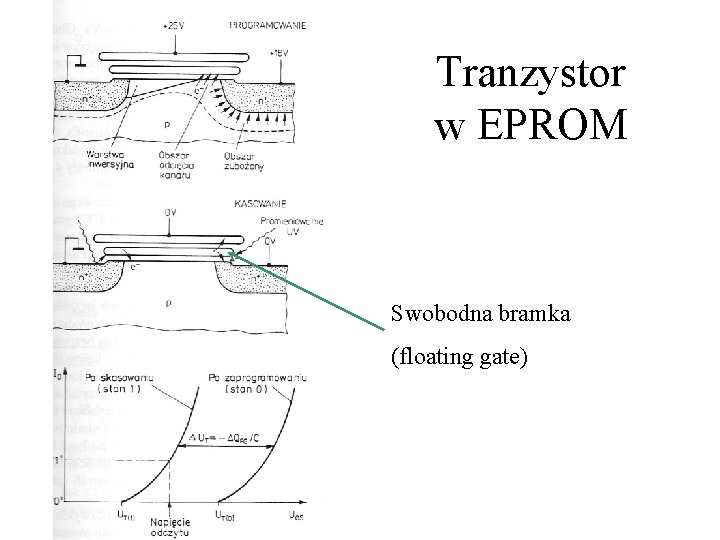

Tranzystor w EPROM Swobodna bramka (floating gate)

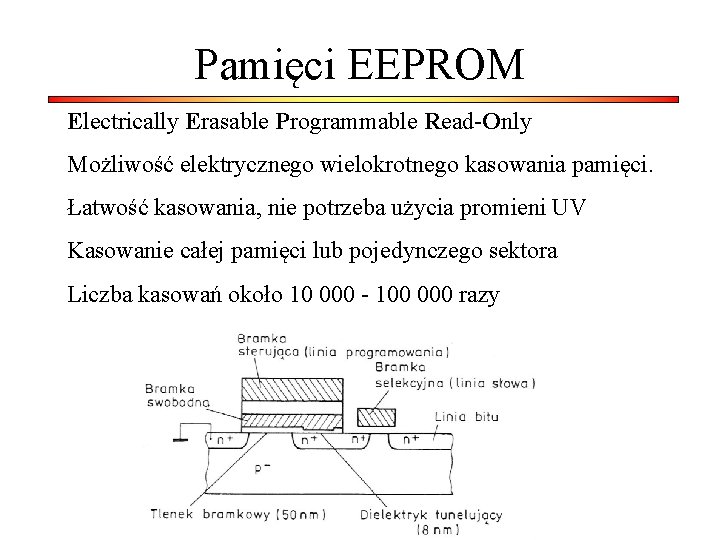

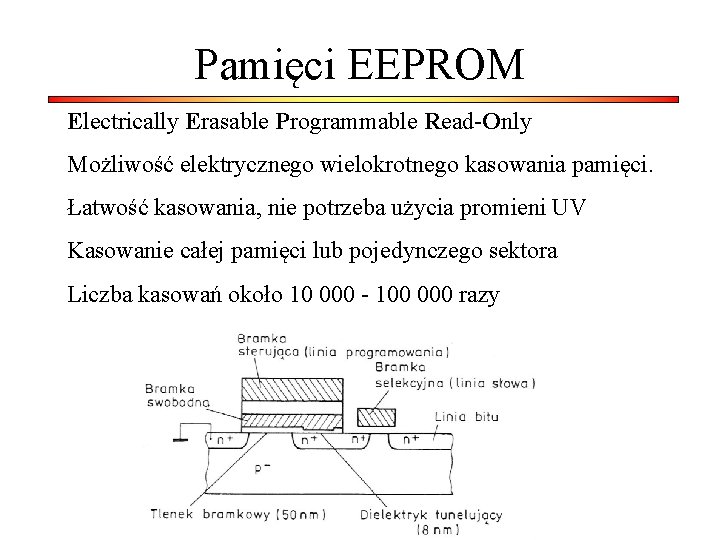

Pamięci EEPROM Electrically Erasable Programmable Read-Only Możliwość elektrycznego wielokrotnego kasowania pamięci. Łatwość kasowania, nie potrzeba użycia promieni UV Kasowanie całej pamięci lub pojedynczego sektora Liczba kasowań około 10 000 - 100 000 razy

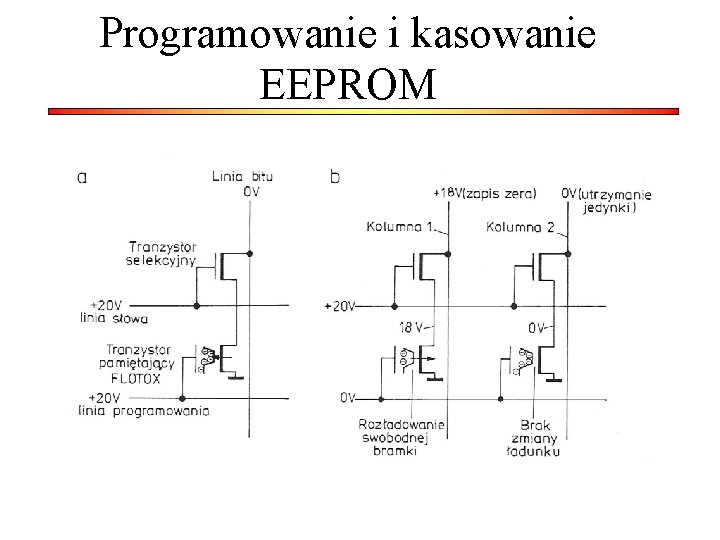

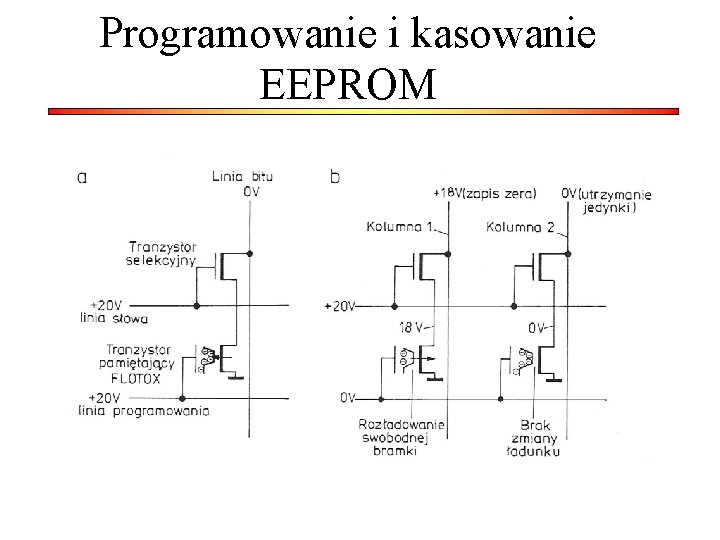

Programowanie i kasowanie EEPROM

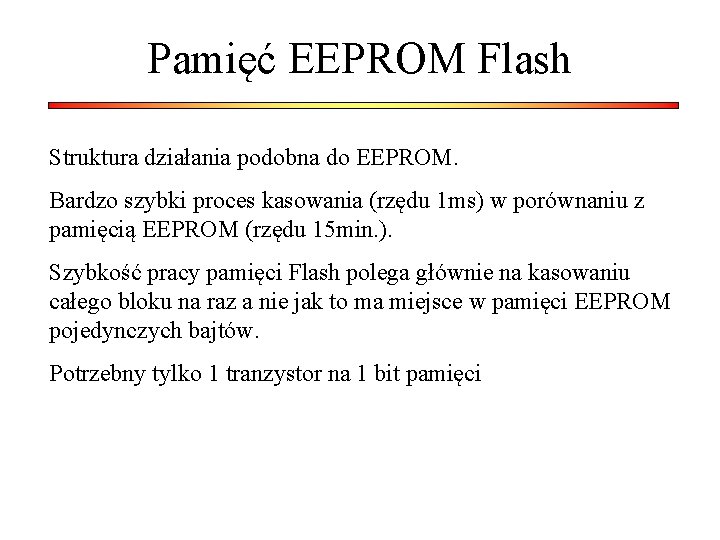

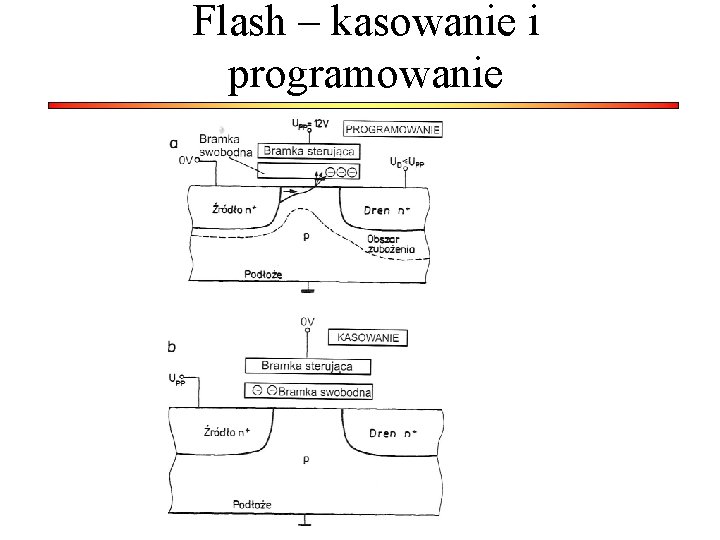

Pamięć EEPROM Flash Struktura działania podobna do EEPROM. Bardzo szybki proces kasowania (rzędu 1 ms) w porównaniu z pamięcią EEPROM (rzędu 15 min. ). Szybkość pracy pamięci Flash polega głównie na kasowaniu całego bloku na raz a nie jak to ma miejsce w pamięci EEPROM pojedynczych bajtów. Potrzebny tylko 1 tranzystor na 1 bit pamięci

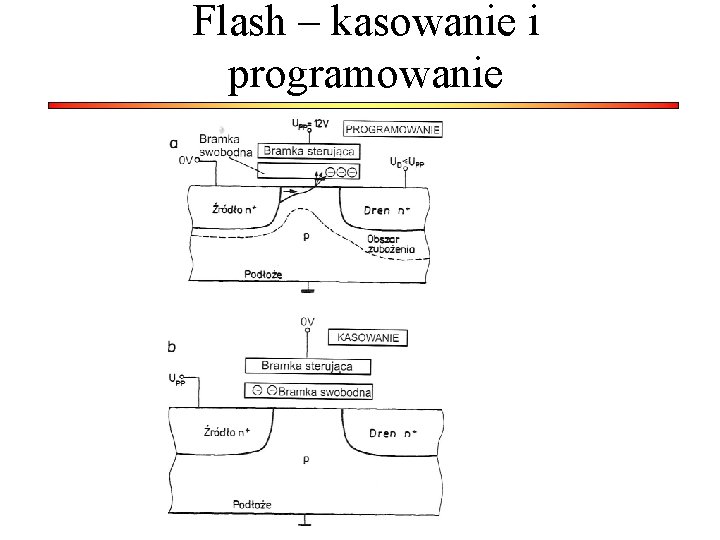

Flash – kasowanie i programowanie

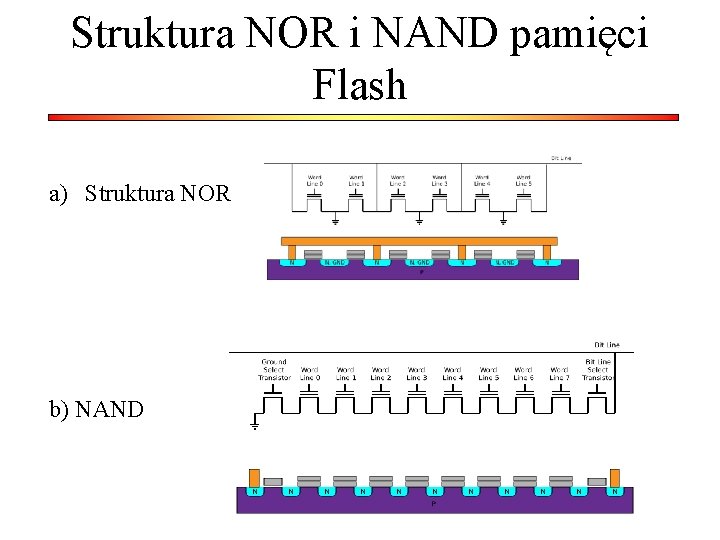

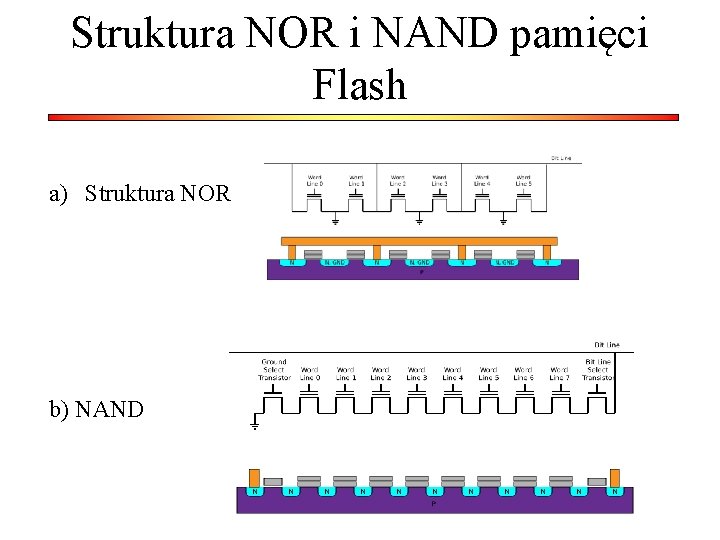

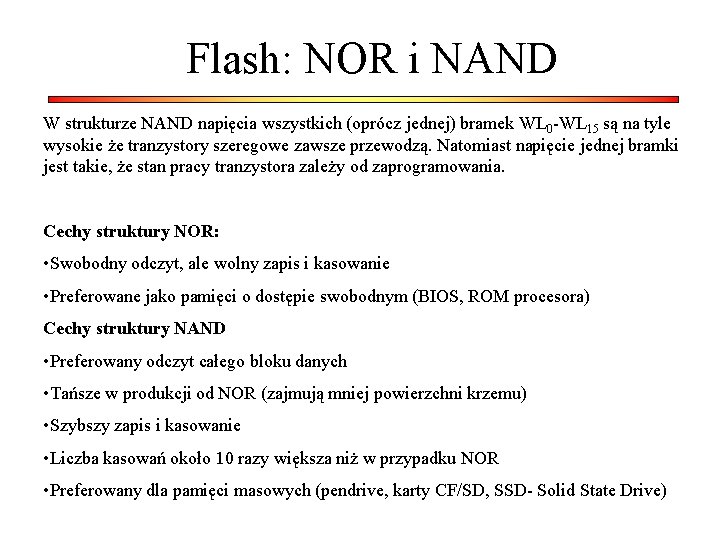

Struktura NOR i NAND pamięci Flash a) Struktura NOR b) NAND

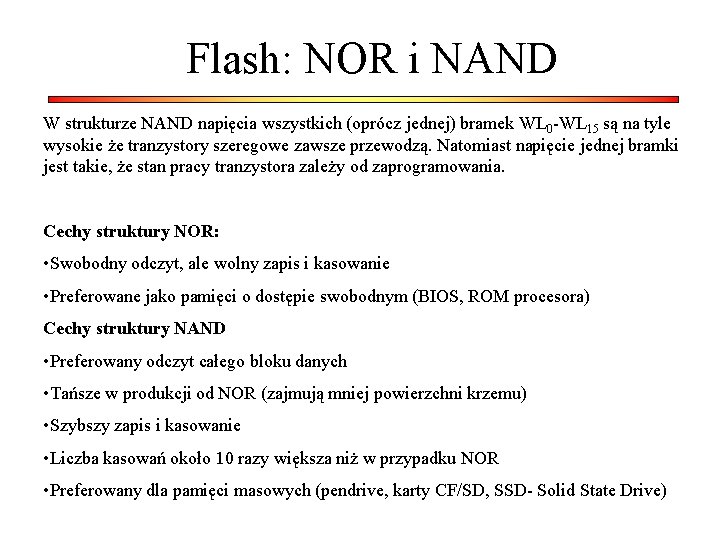

Flash: NOR i NAND W strukturze NAND napięcia wszystkich (oprócz jednej) bramek WL 0 -WL 15 są na tyle wysokie że tranzystory szeregowe zawsze przewodzą. Natomiast napięcie jednej bramki jest takie, że stan pracy tranzystora zależy od zaprogramowania. Cechy struktury NOR: • Swobodny odczyt, ale wolny zapis i kasowanie • Preferowane jako pamięci o dostępie swobodnym (BIOS, ROM procesora) Cechy struktury NAND • Preferowany odczyt całego bloku danych • Tańsze w produkcji od NOR (zajmują mniej powierzchni krzemu) • Szybszy zapis i kasowanie • Liczba kasowań około 10 razy większa niż w przypadku NOR • Preferowany dla pamięci masowych (pendrive, karty CF/SD, SSD- Solid State Drive)

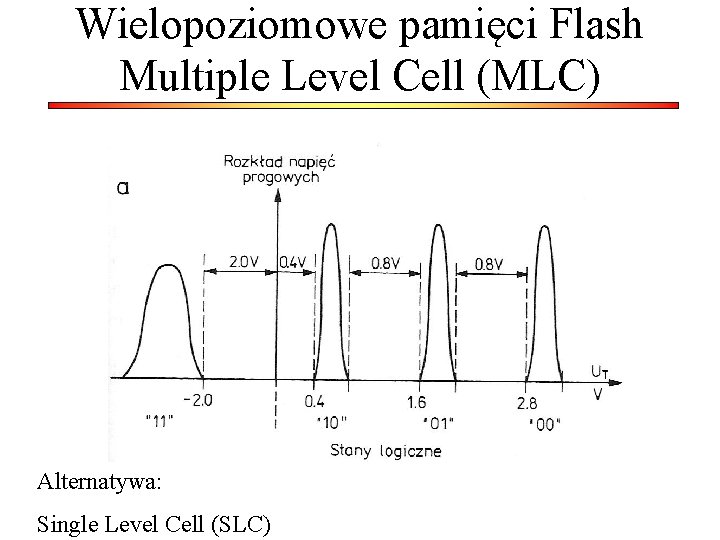

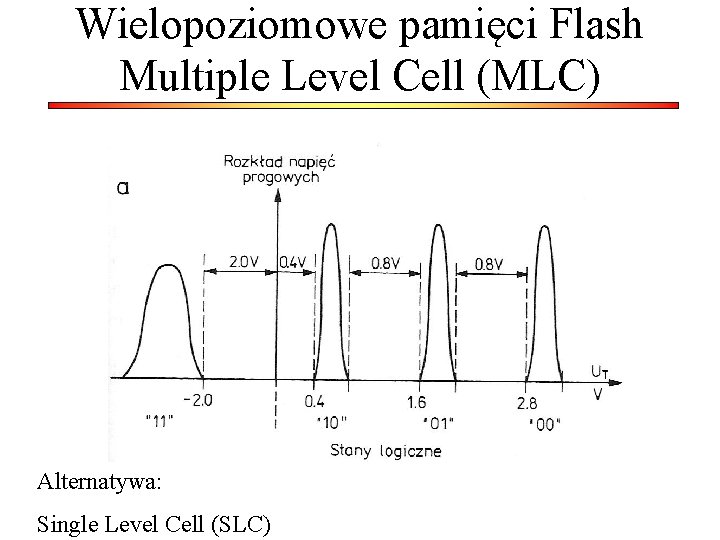

Wielopoziomowe pamięci Flash Multiple Level Cell (MLC) Alternatywa: Single Level Cell (SLC)

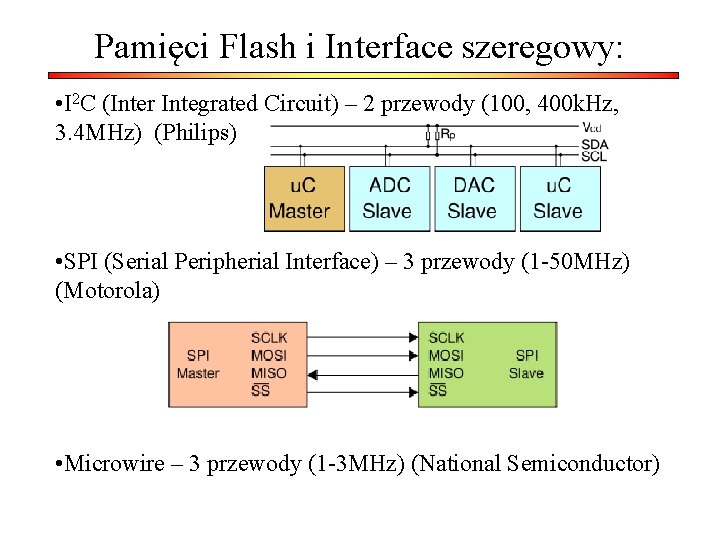

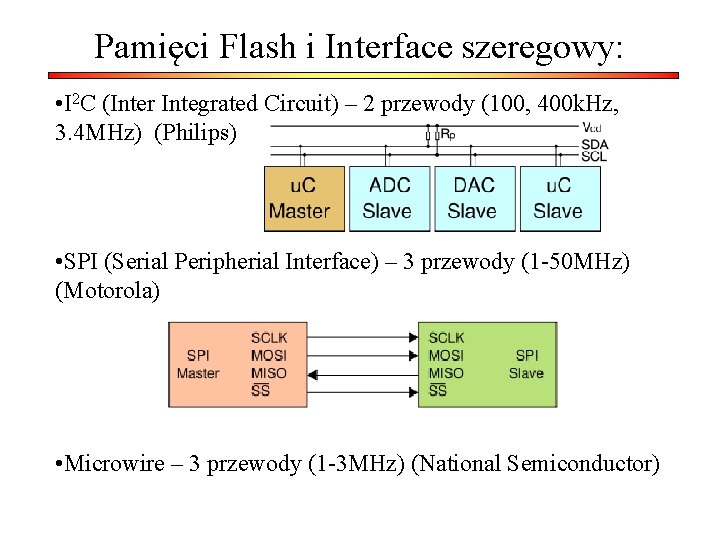

Pamięci Flash i Interface szeregowy: • I 2 C (Inter Integrated Circuit) – 2 przewody (100, 400 k. Hz, 3. 4 MHz) (Philips) • SPI (Serial Peripherial Interface) – 3 przewody (1 -50 MHz) (Motorola) • Microwire – 3 przewody (1 -3 MHz) (National Semiconductor)

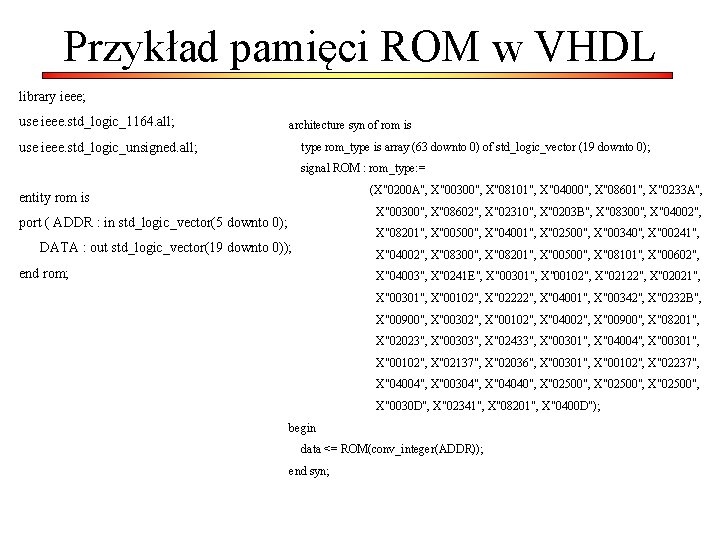

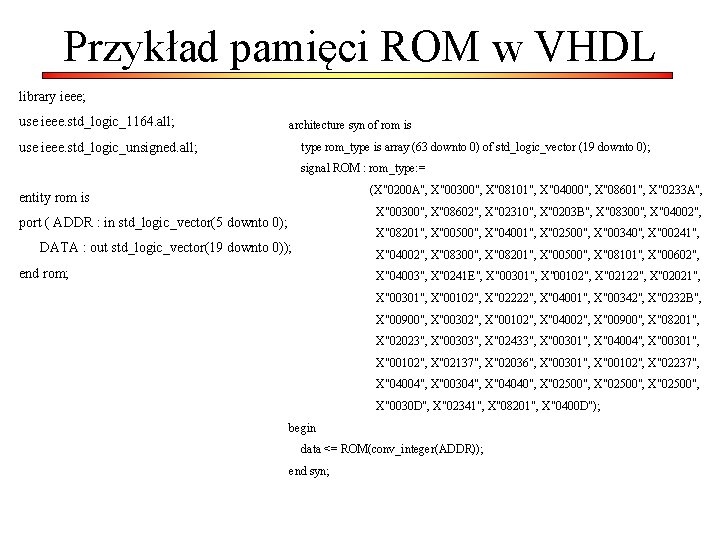

Przykład pamięci ROM w VHDL library ieee; use ieee. std_logic_1164. all; architecture syn of rom is use ieee. std_logic_unsigned. all; type rom_type is array (63 downto 0) of std_logic_vector (19 downto 0); signal ROM : rom_type: = (X"0200 A", X"00300", X"08101", X"04000", X"08601", X"0233 A", entity rom is X"00300", X"08602", X"02310", X"0203 B", X"08300", X"04002", port ( ADDR : in std_logic_vector(5 downto 0); X"08201", X"00500", X"04001", X"02500", X"00340", X"00241", DATA : out std_logic_vector(19 downto 0)); X"04002", X"08300", X"08201", X"00500", X"08101", X"00602", end rom; X"04003", X"0241 E", X"00301", X"00102", X"02122", X"02021", X"00301", X"00102", X"02222", X"04001", X"00342", X"0232 B", X"00900", X"00302", X"00102", X"04002", X"00900", X"08201", X"02023", X"00303", X"02433", X"00301", X"04004", X"00301", X"00102", X"02137", X"02036", X"00301", X"00102", X"02237", X"04004", X"00304", X"04040", X"02500", X"0030 D", X"02341", X"08201", X"0400 D"); begin data <= ROM(conv_integer(ADDR)); end syn;

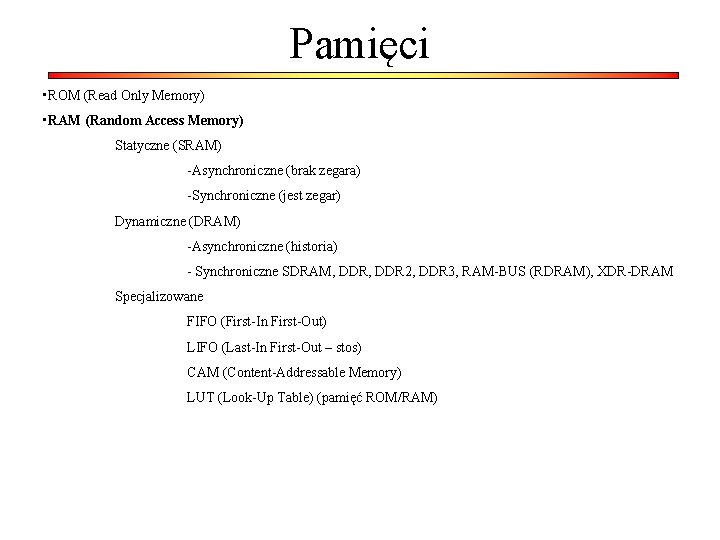

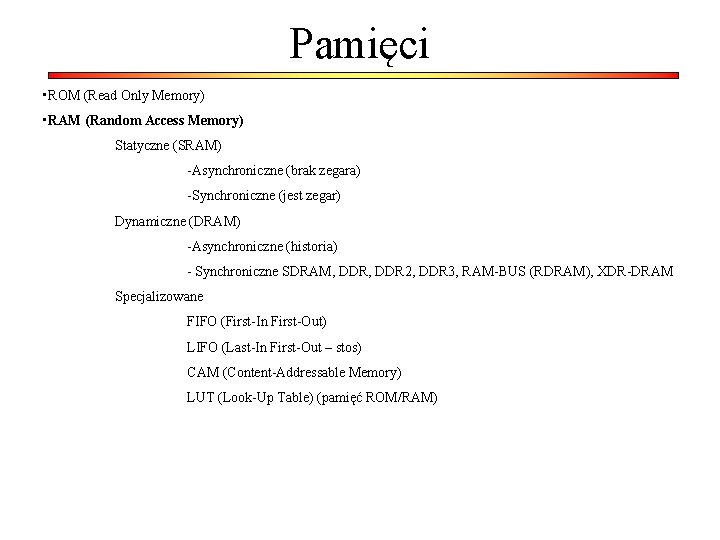

Pamięci • ROM (Read Only Memory) • RAM (Random Access Memory) Statyczne (SRAM) -Asynchroniczne (brak zegara) -Synchroniczne (jest zegar) Dynamiczne (DRAM) -Asynchroniczne (historia) - Synchroniczne SDRAM, DDR 2, DDR 3, RAM-BUS (RDRAM), XDR-DRAM Specjalizowane FIFO (First-In First-Out) LIFO (Last-In First-Out – stos) CAM (Content-Addressable Memory) LUT (Look-Up Table) (pamięć ROM/RAM)

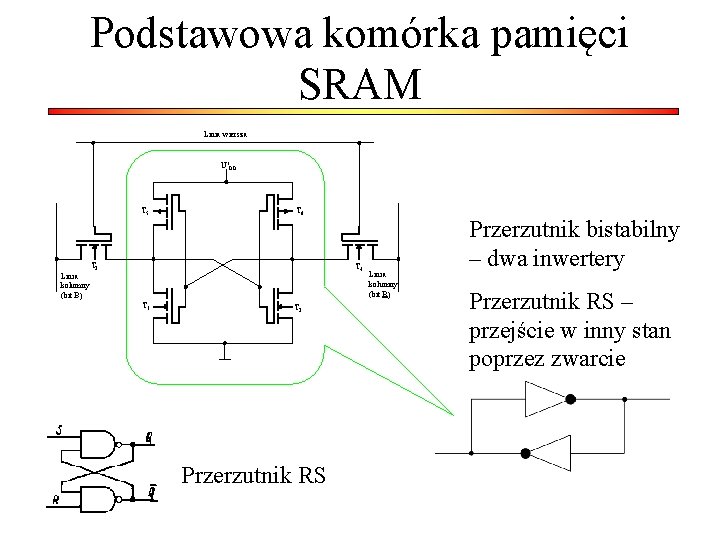

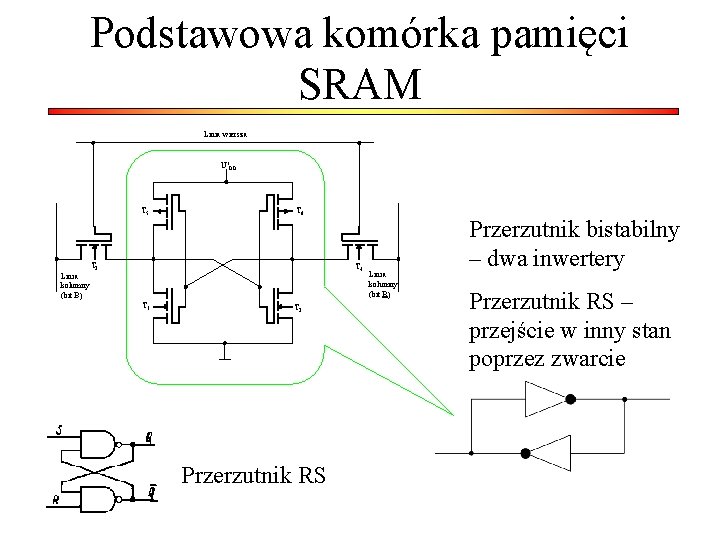

Podstawowa komórka pamięci SRAM Linia wiersza U’DD T 5 T 6 T 3 T 4 Linia kolumny (bit B) T 1 T 2 Przerzutnik RS Linia kolumny (bit B) Przerzutnik bistabilny – dwa inwertery Przerzutnik RS – przejście w inny stan poprzez zwarcie

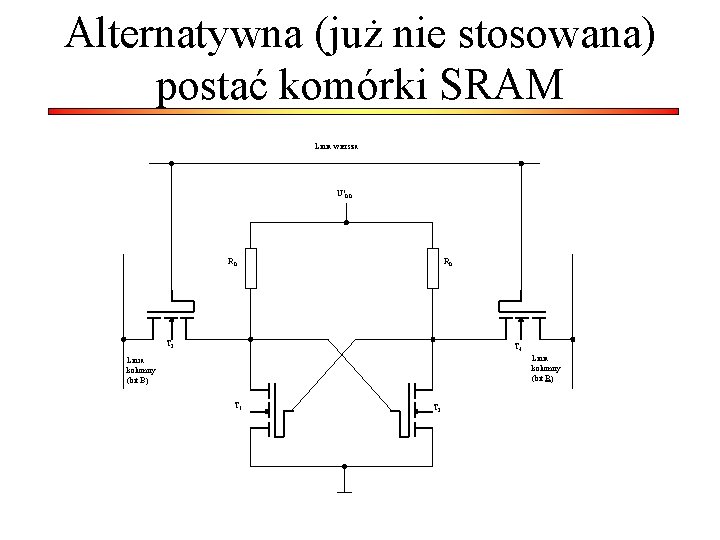

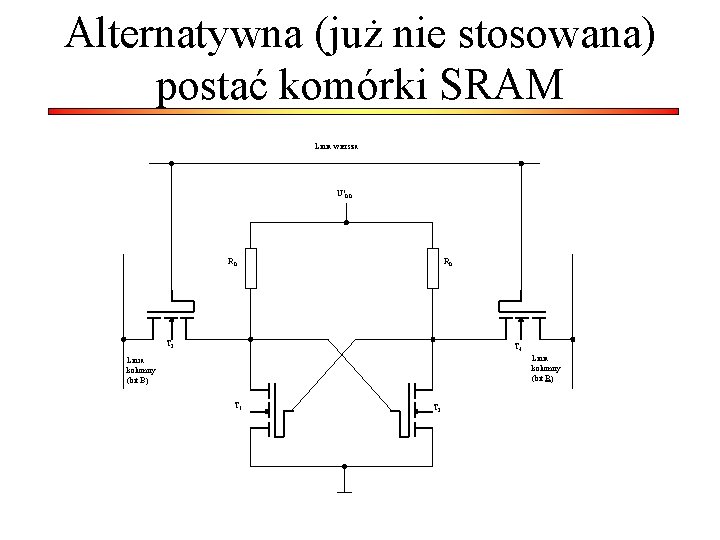

Alternatywna (już nie stosowana) postać komórki SRAM Linia wiersza U’DD RD RD T 3 T 4 Linia kolumny (bit B) T 1 T 2

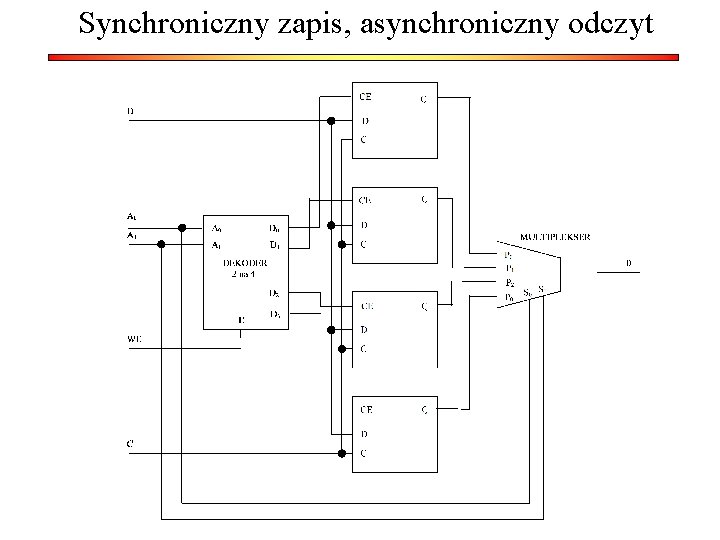

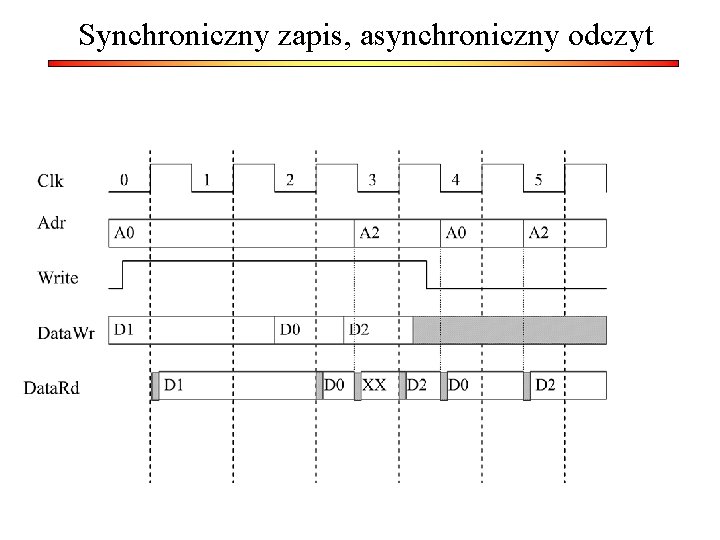

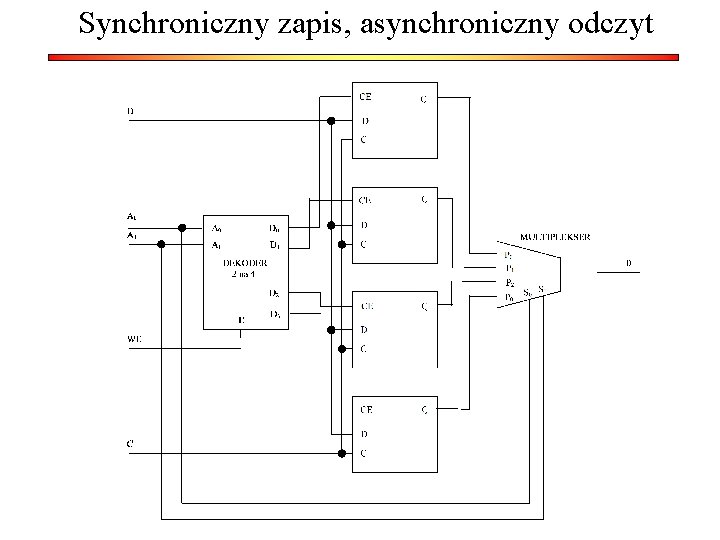

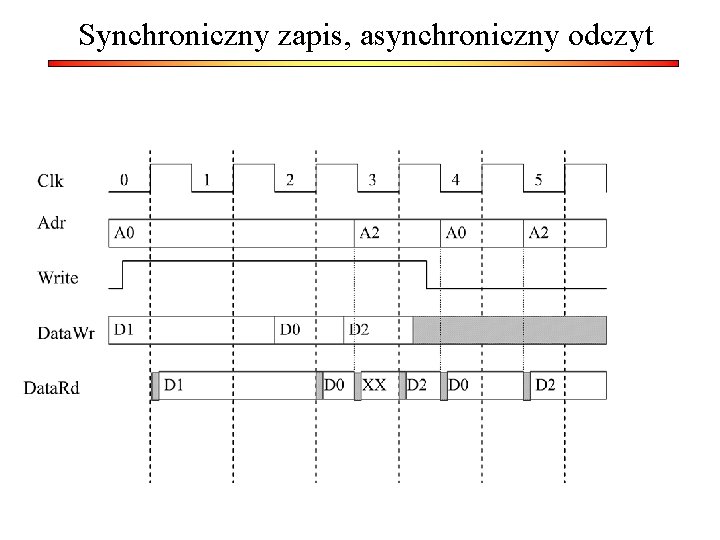

Synchroniczny zapis, asynchroniczny odczyt

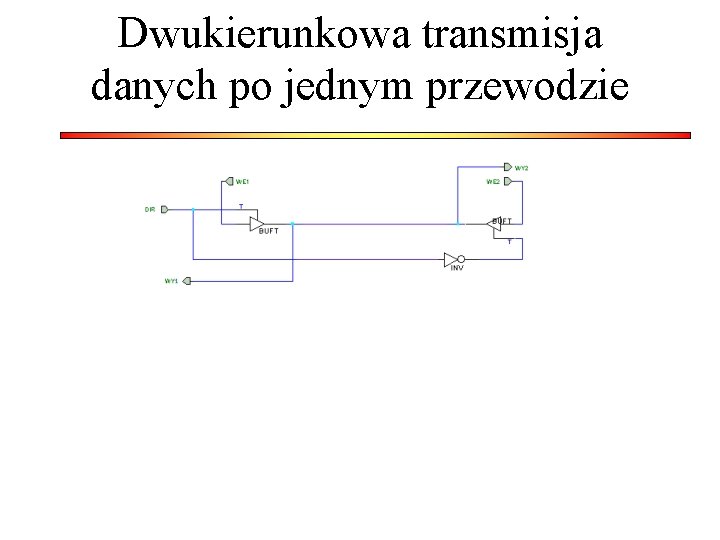

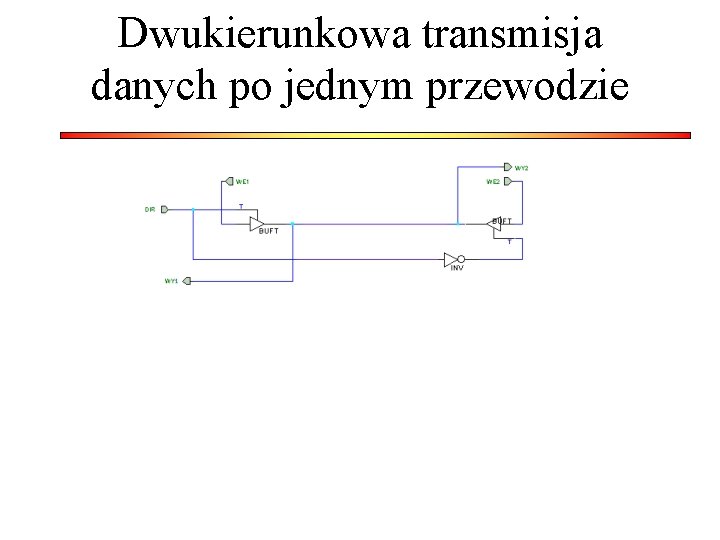

Dwukierunkowa transmisja danych po jednym przewodzie

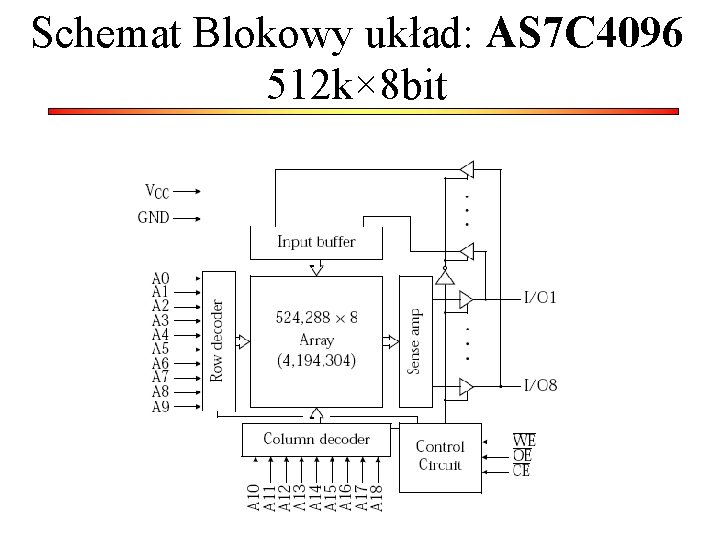

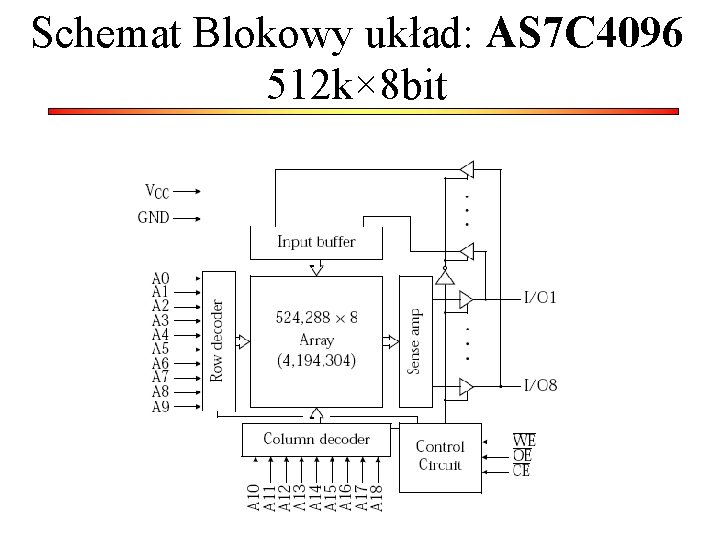

Schemat Blokowy układ: AS 7 C 4096 512 k× 8 bit

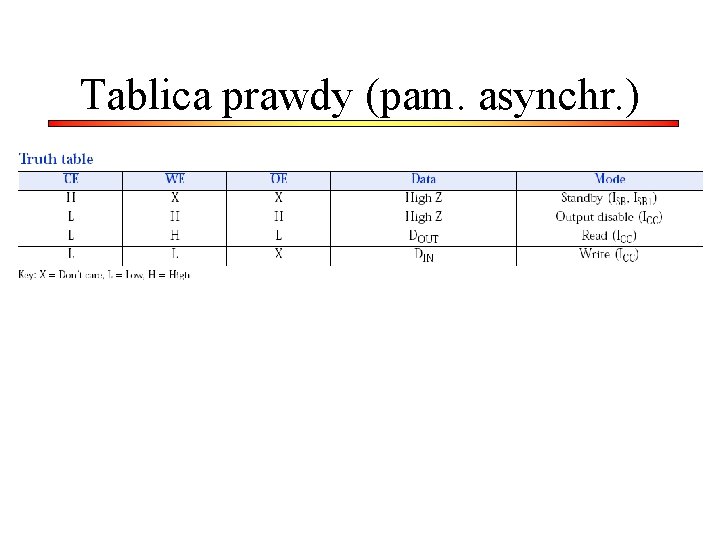

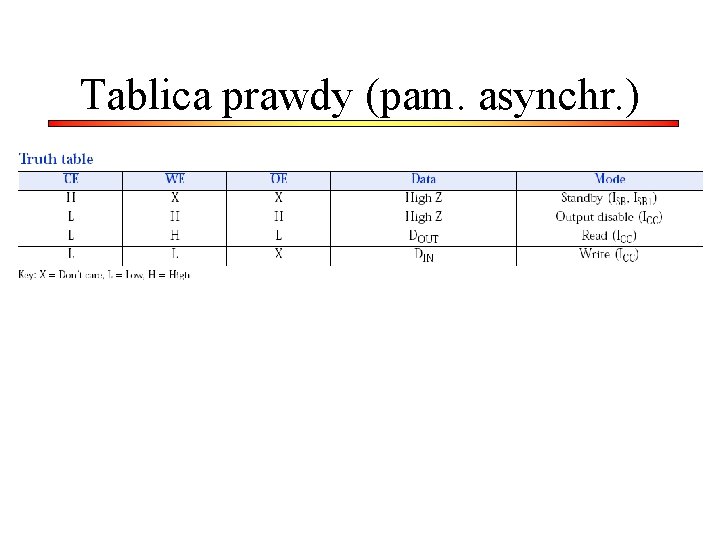

Tablica prawdy (pam. asynchr. )

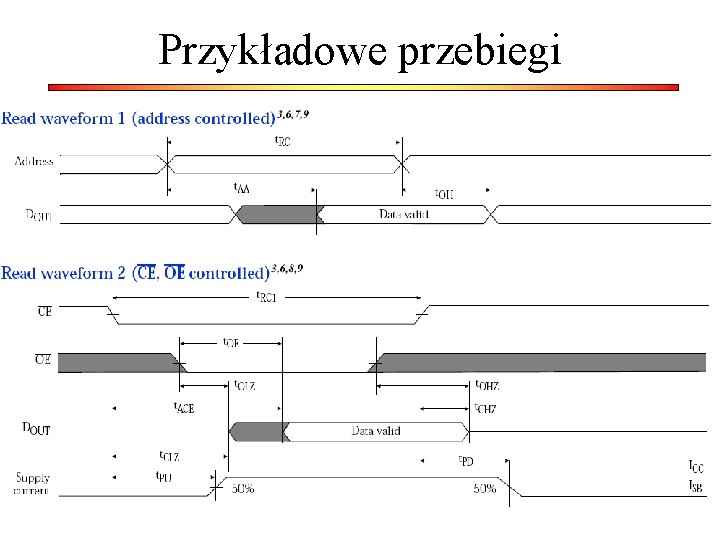

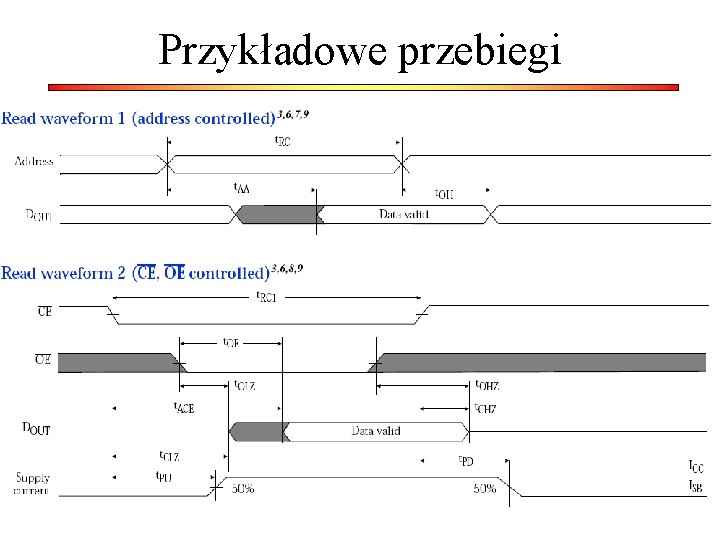

Przykładowe przebiegi

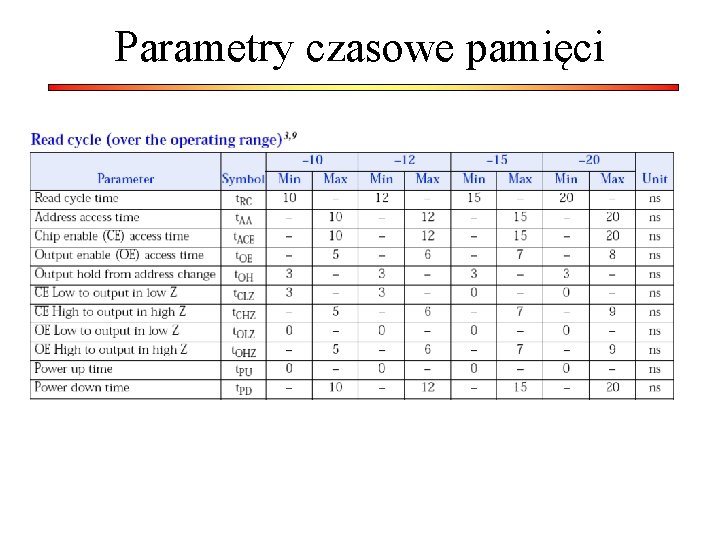

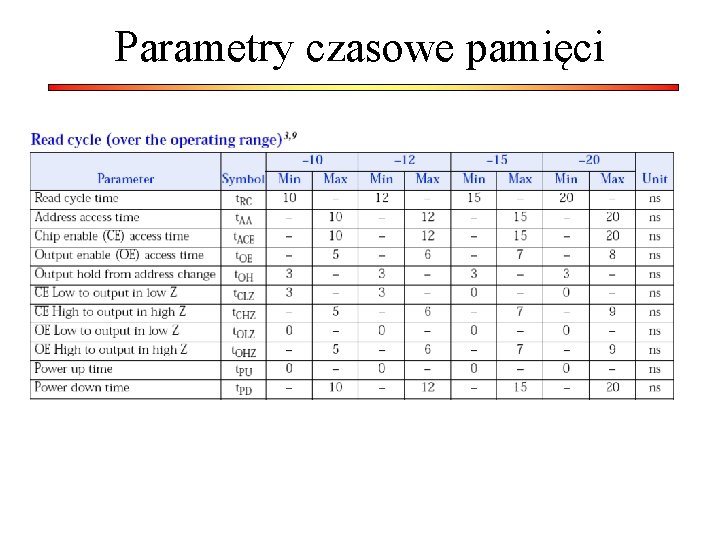

Parametry czasowe pamięci

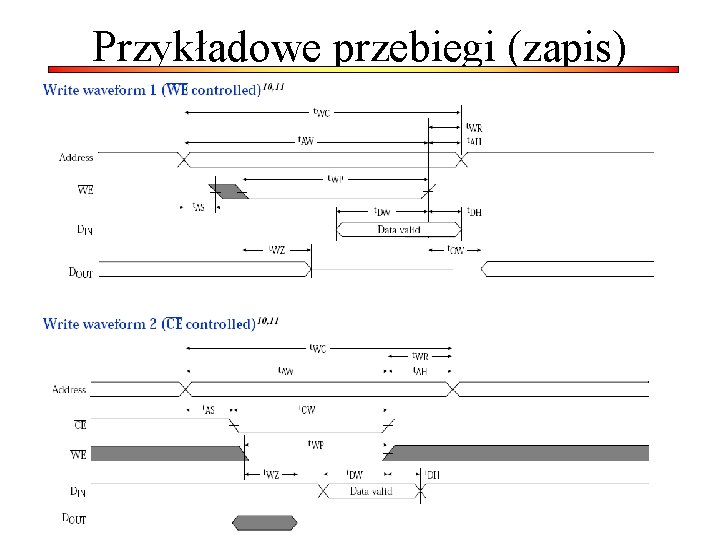

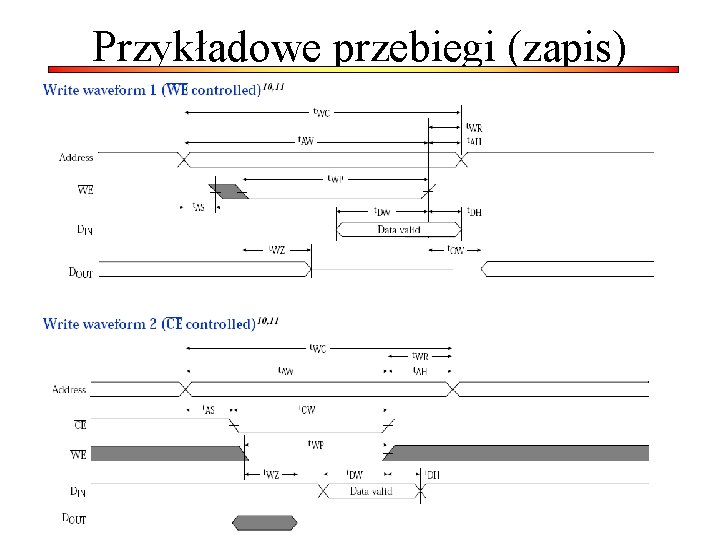

Przykładowe przebiegi (zapis)

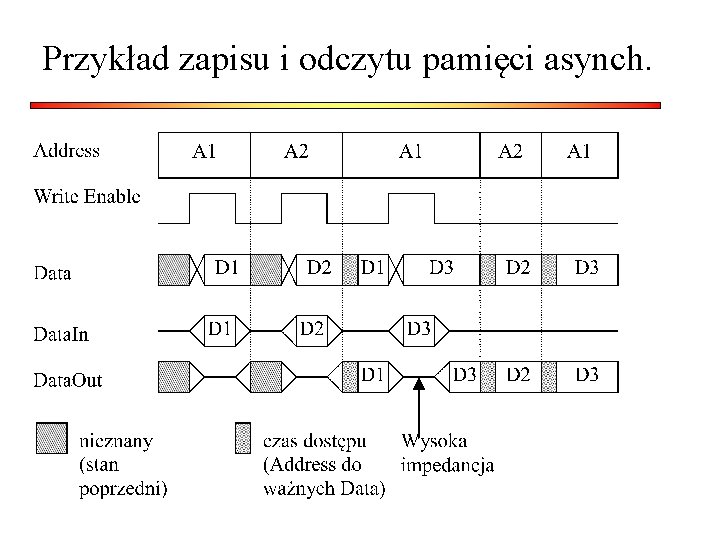

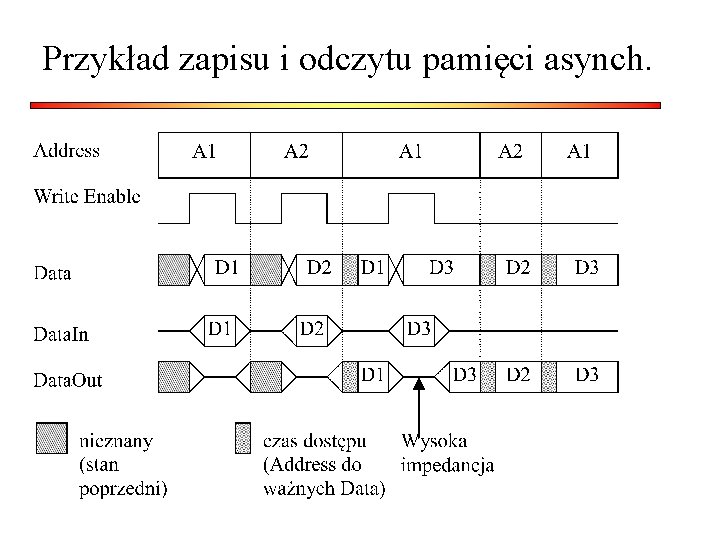

Przykład zapisu i odczytu pamięci asynch.

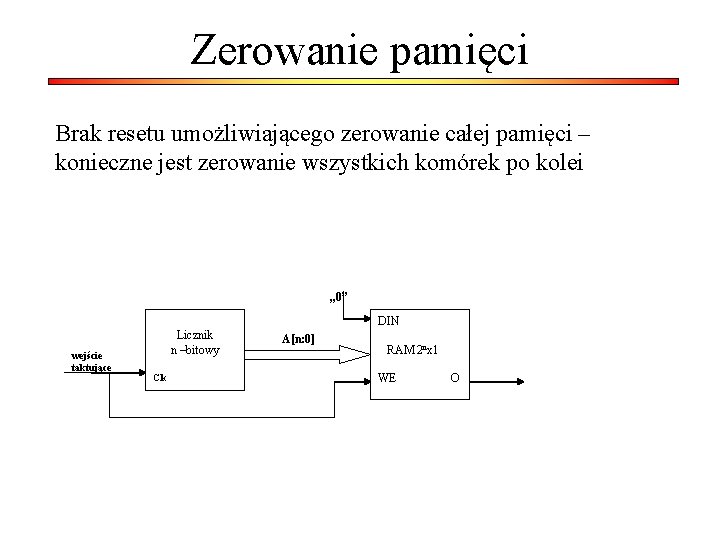

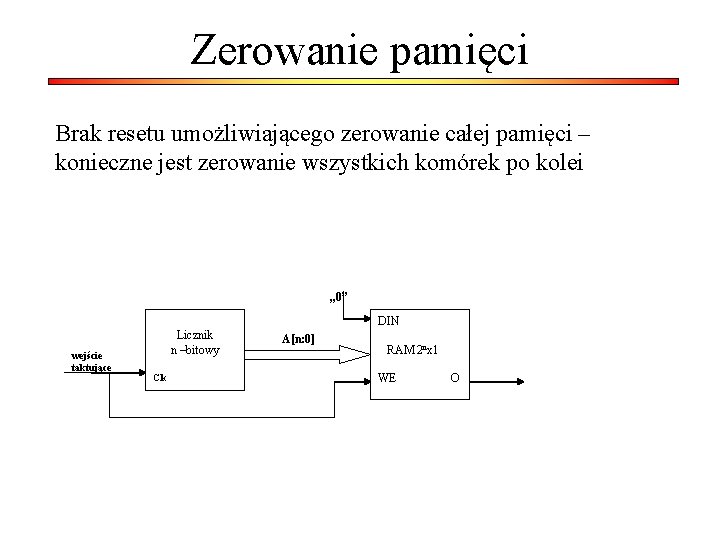

Zerowanie pamięci Brak resetu umożliwiającego zerowanie całej pamięci – konieczne jest zerowanie wszystkich komórek po kolei „ 0” DIN wejście taktujące Licznik n –bitowy Clk A[n: 0] RAM 2 nx 1 WE O

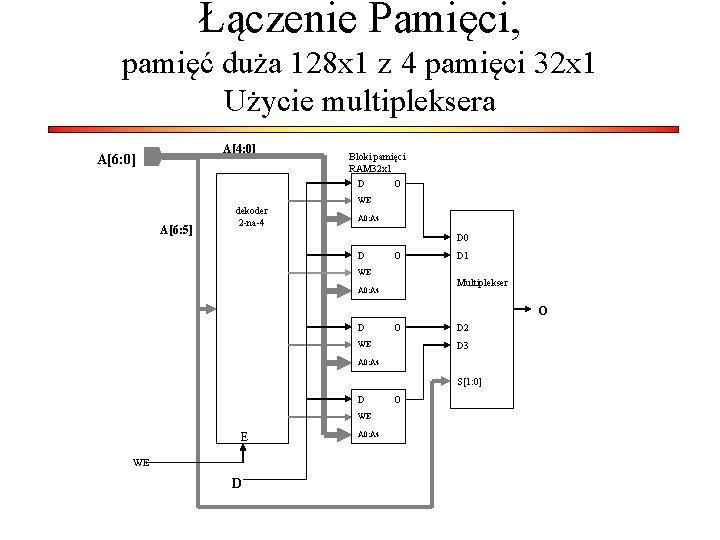

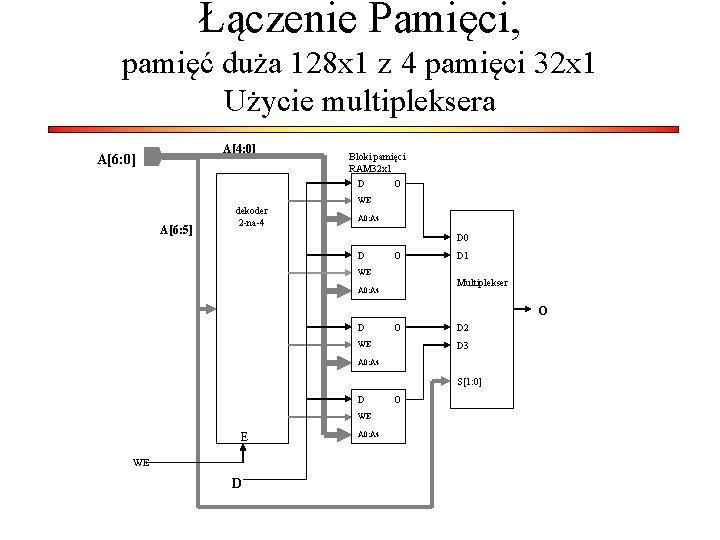

Łączenie Pamięci, pamięć duża 128 x 1 z 4 pamięci 32 x 1 Użycie multipleksera A[4: 0] A[6: 0] Bloki pamięci RAM 32 x 1 D O WE A[6: 5] dekoder 2 -na-4 A 0: A 4 D 0 D O D 1 WE Multiplekser A 0: A 4 O D O WE D 2 D 3 A 0: A 4 S[1: 0] D WE E WE D A 0: A 4 O

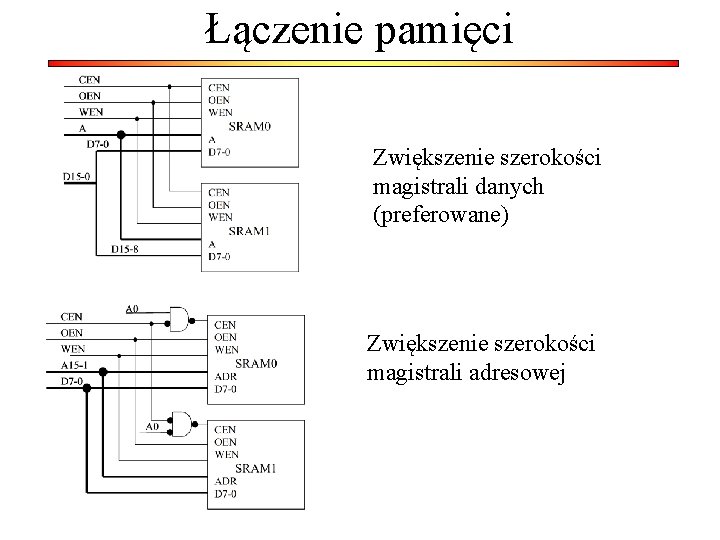

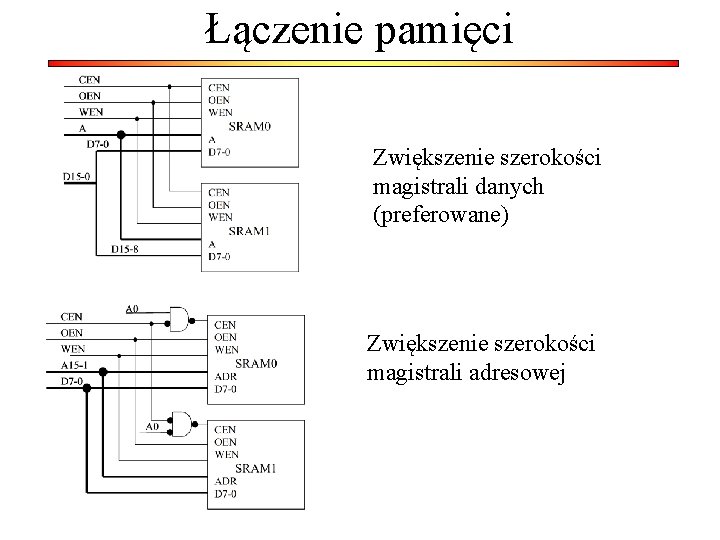

Łączenie pamięci Zwiększenie szerokości magistrali danych (preferowane) Zwiększenie szerokości magistrali adresowej

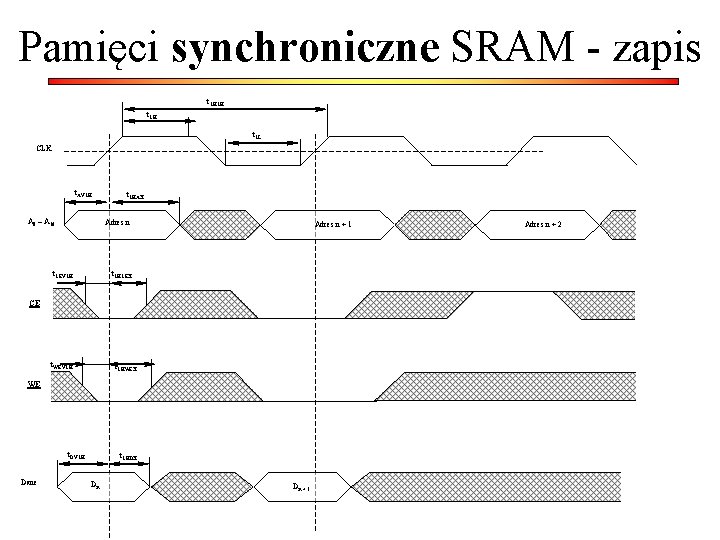

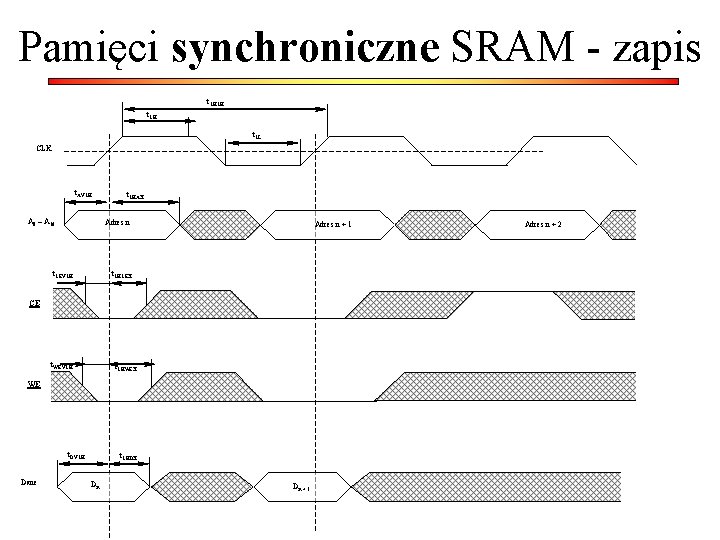

Pamięci synchroniczne SRAM - zapis t. CHCH t. CL CLK t. AVCH A 0 – A 16 t. CHAX Adres n t. CEVCH Adres n + 1 t. CHCEX CE t. WEVCH t. CHWEX WE t. DVCH Dane t. CHDX Dn Dn + 1 Adres n + 2

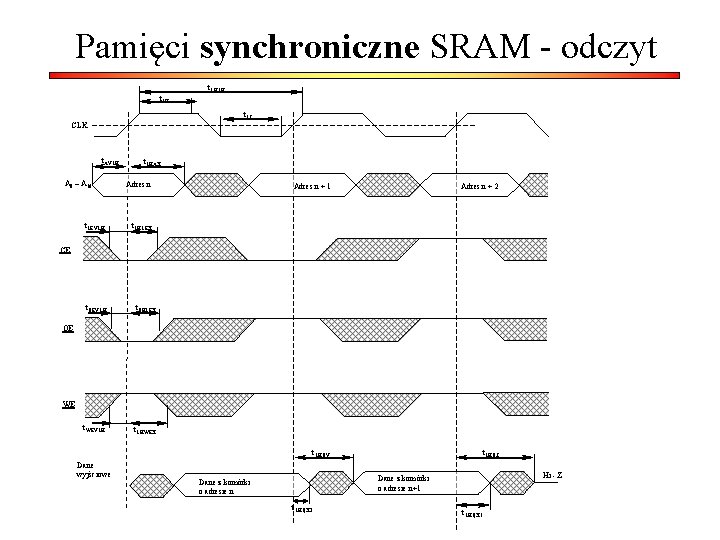

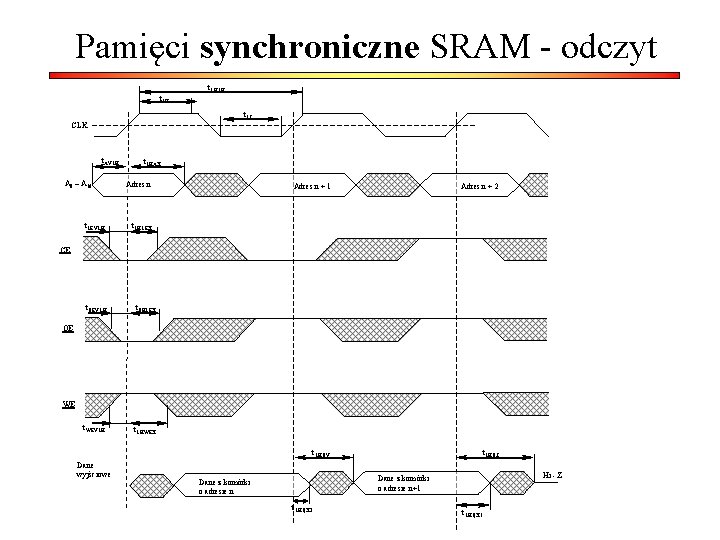

Pamięci synchroniczne SRAM - odczyt t. CHCH t. CL CLK t. AVCH A 0 – A 16 t. CEVCH t. CHAX Adres n + 1 Adres n + 2 t. CHQV t. CHQZ t. CHCEX CE t. OEVCH t. OHCEX t. WEVCH t. CHWEX OE WE Dane wyjściowe Hi - Z Dane z komórki o adresie n+1 Dane z komórki o adresie n t. CHQX 2 t. CHQX 1

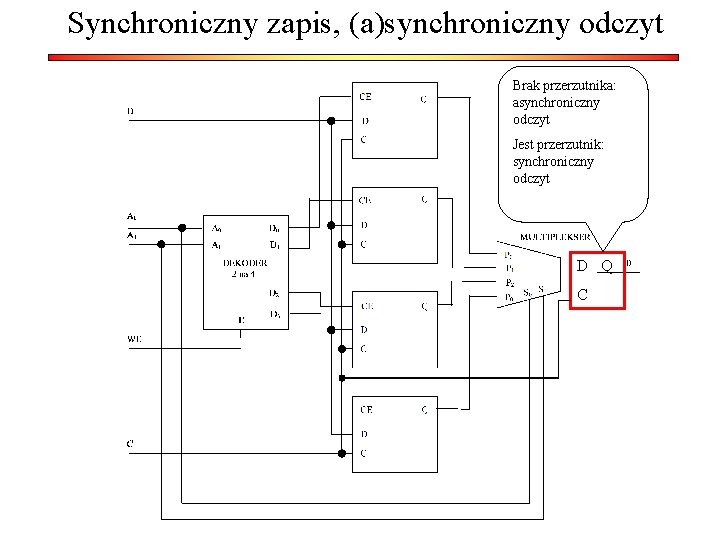

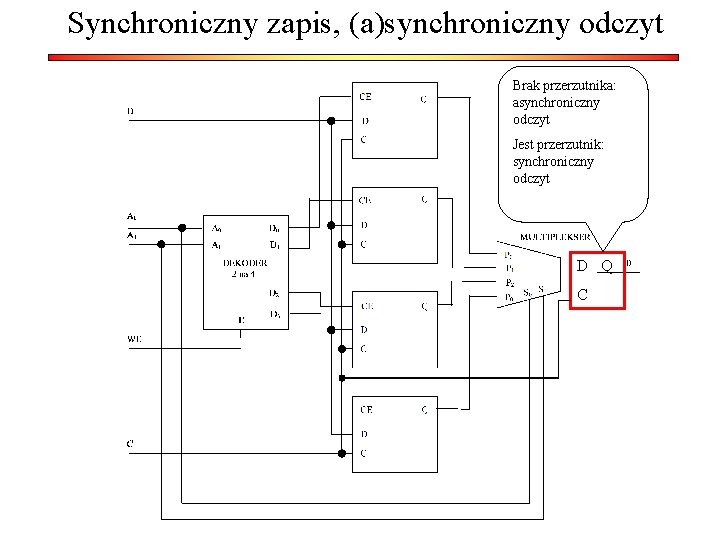

Synchroniczny zapis, (a)synchroniczny odczyt Brak przerzutnika: asynchroniczny odczyt Jest przerzutnik: synchroniczny odczyt D Q C

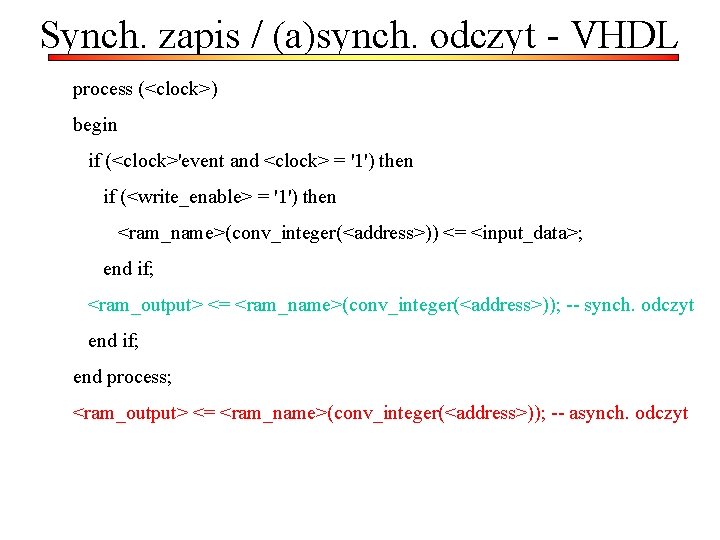

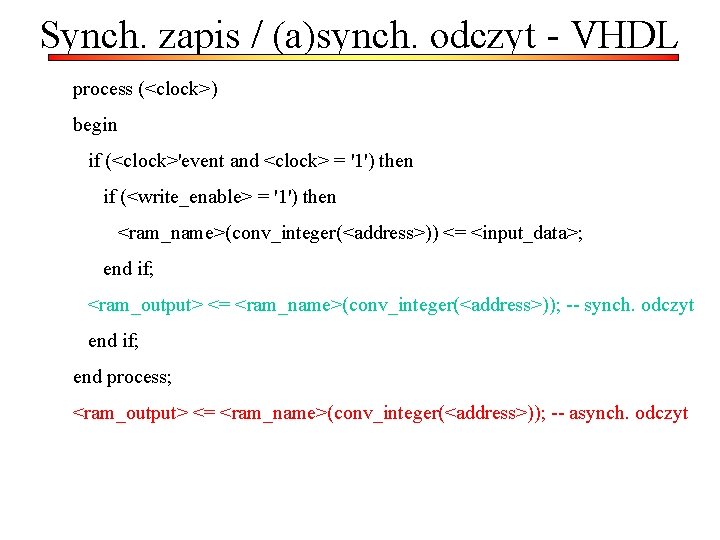

Synch. zapis / (a)synch. odczyt - VHDL process (<clock>) begin if (<clock>'event and <clock> = '1') then if (<write_enable> = '1') then <ram_name>(conv_integer(<address>)) <= <input_data>; end if; <ram_output> <= <ram_name>(conv_integer(<address>)); -- synch. odczyt end if; end process; <ram_output> <= <ram_name>(conv_integer(<address>)); -- asynch. odczyt

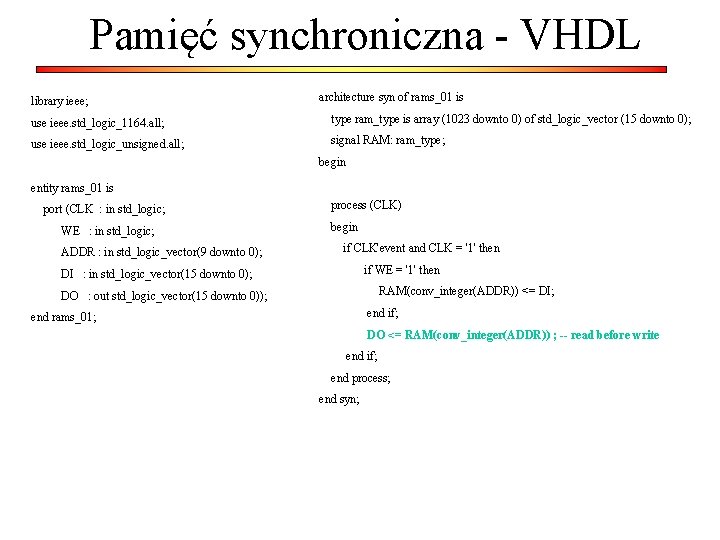

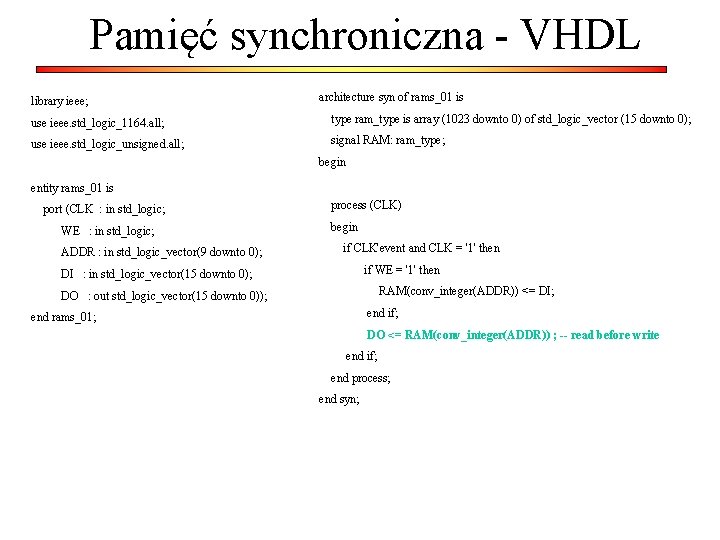

Pamięć synchroniczna - VHDL library ieee; architecture syn of rams_01 is use ieee. std_logic_1164. all; type ram_type is array (1023 downto 0) of std_logic_vector (15 downto 0); use ieee. std_logic_unsigned. all; signal RAM: ram_type; begin entity rams_01 is port (CLK : in std_logic; WE : in std_logic; ADDR : in std_logic_vector(9 downto 0); process (CLK) begin if CLK'event and CLK = '1' then if WE = '1' then DI : in std_logic_vector(15 downto 0); RAM(conv_integer(ADDR)) <= DI; DO : out std_logic_vector(15 downto 0)); end if; end rams_01; DO <= RAM(conv_integer(ADDR)) ; -- read before write end if; end process; end syn;

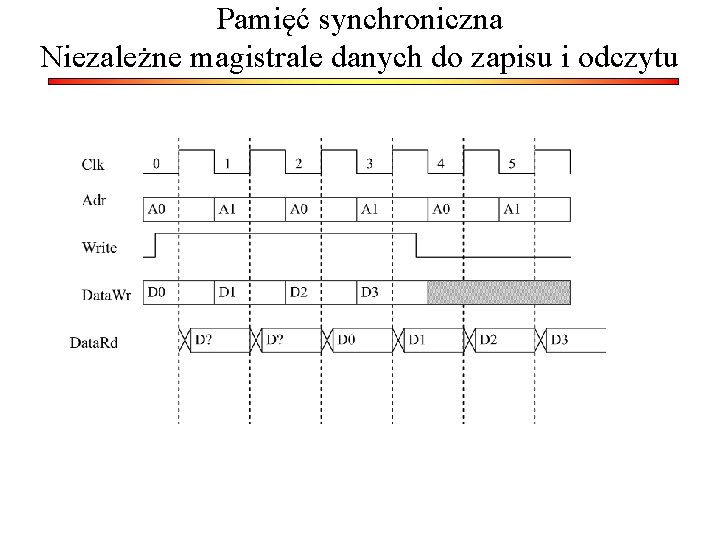

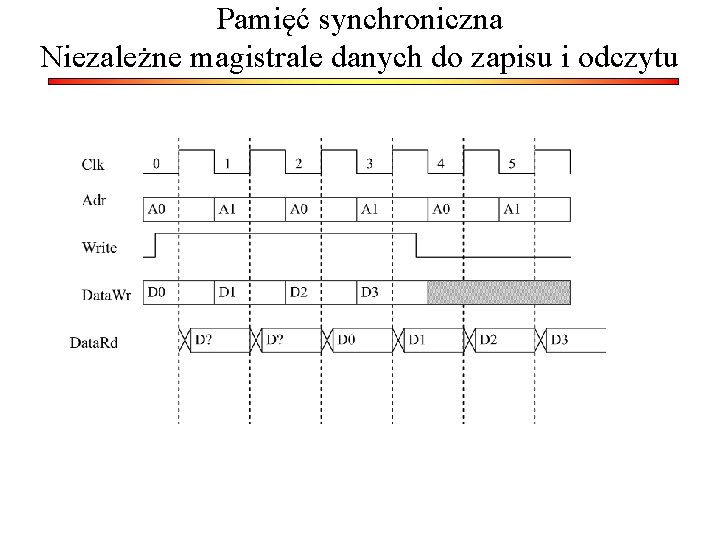

Pamięć synchroniczna Niezależne magistrale danych do zapisu i odczytu

Synchroniczny zapis, asynchroniczny odczyt

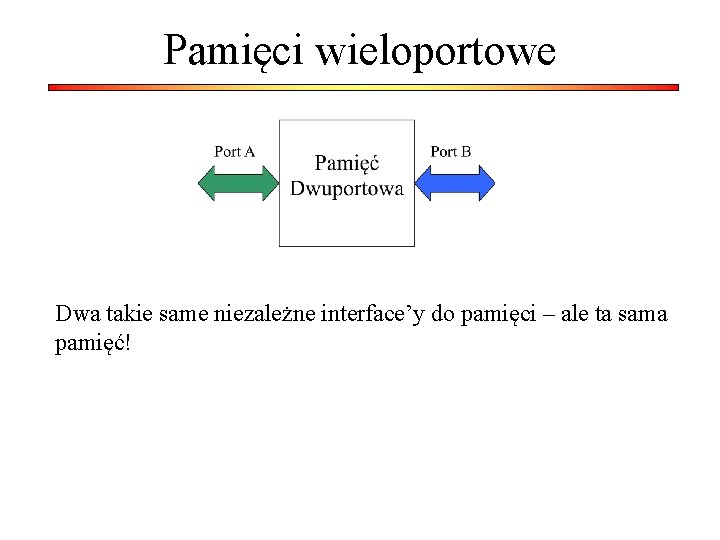

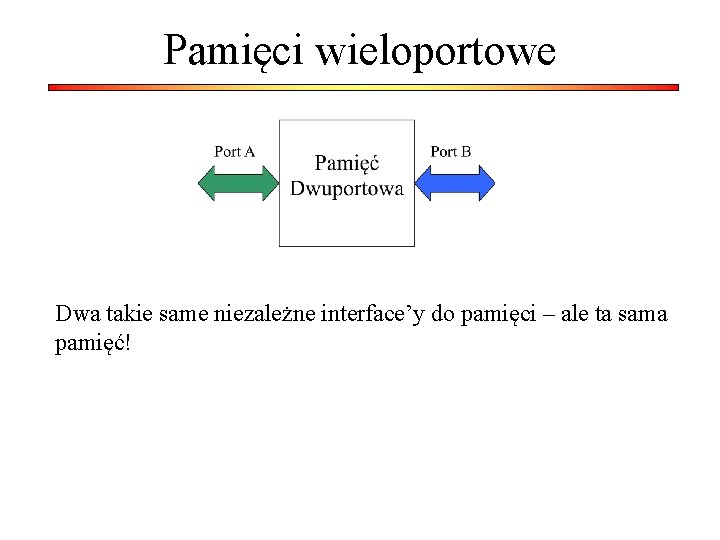

Pamięci wieloportowe Dwa takie same niezależne interface’y do pamięci – ale ta sama pamięć!

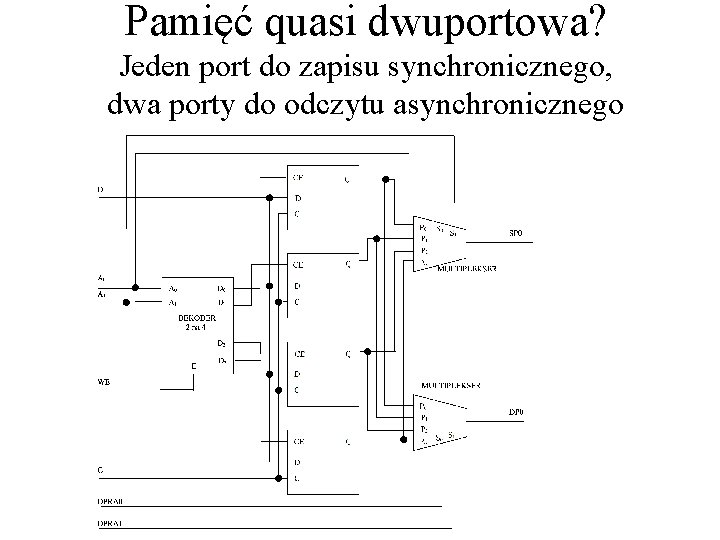

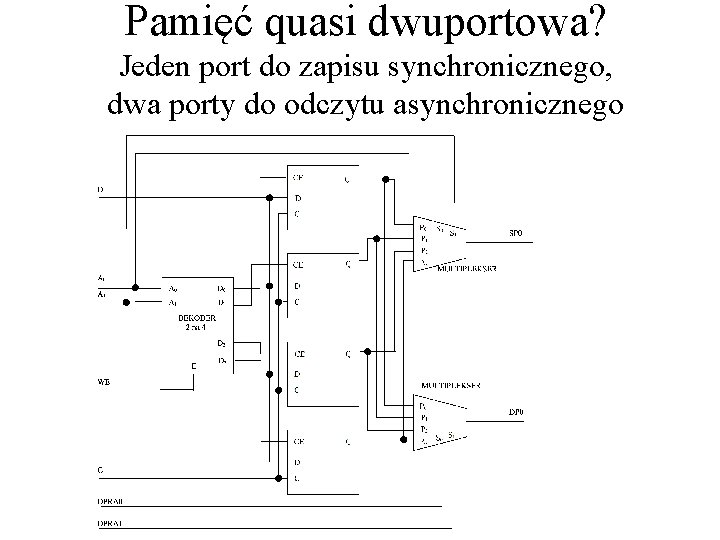

Pamięć quasi dwuportowa? Jeden port do zapisu synchronicznego, dwa porty do odczytu asynchronicznego

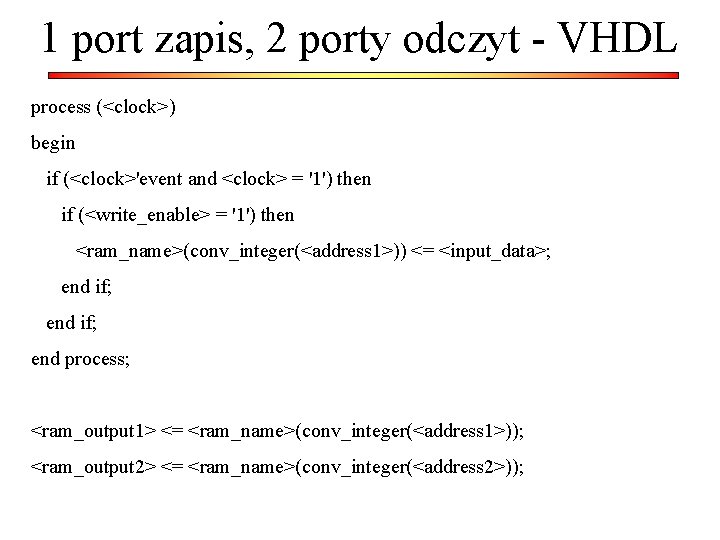

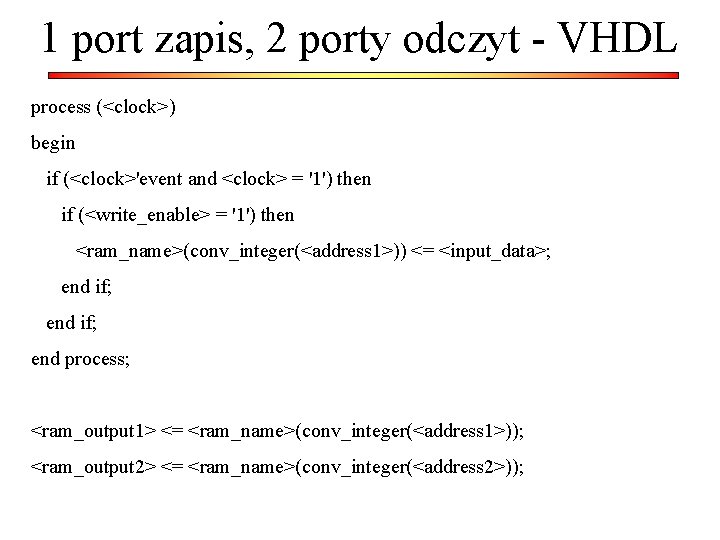

1 port zapis, 2 porty odczyt - VHDL process (<clock>) begin if (<clock>'event and <clock> = '1') then if (<write_enable> = '1') then <ram_name>(conv_integer(<address 1>)) <= <input_data>; end if; end process; <ram_output 1> <= <ram_name>(conv_integer(<address 1>)); <ram_output 2> <= <ram_name>(conv_integer(<address 2>));

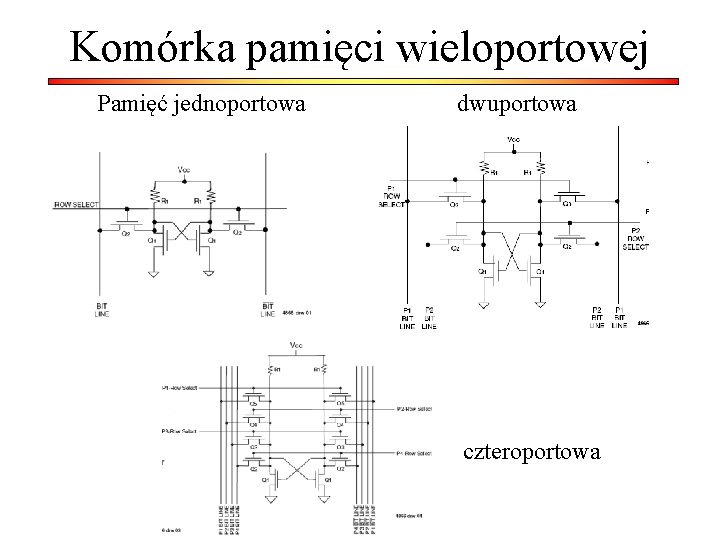

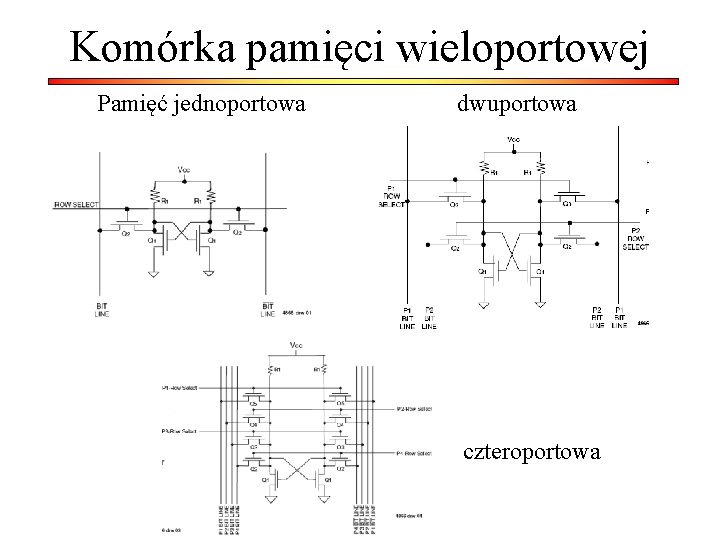

Komórka pamięci wieloportowej Pamięć jednoportowa dwuportowa czteroportowa

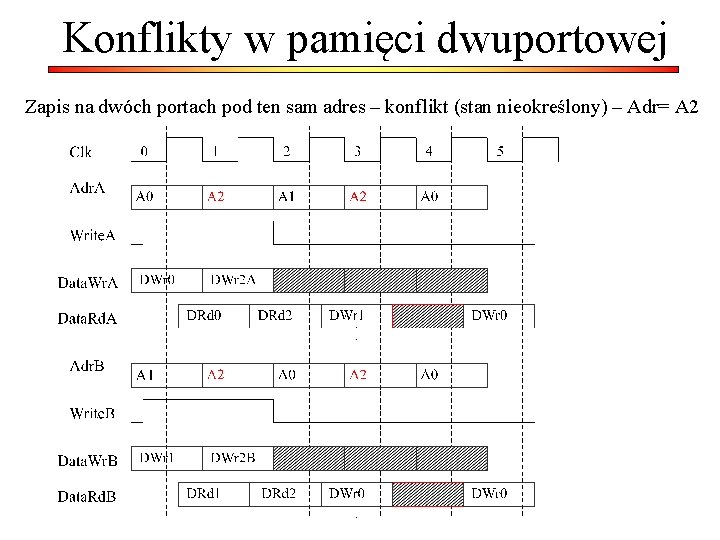

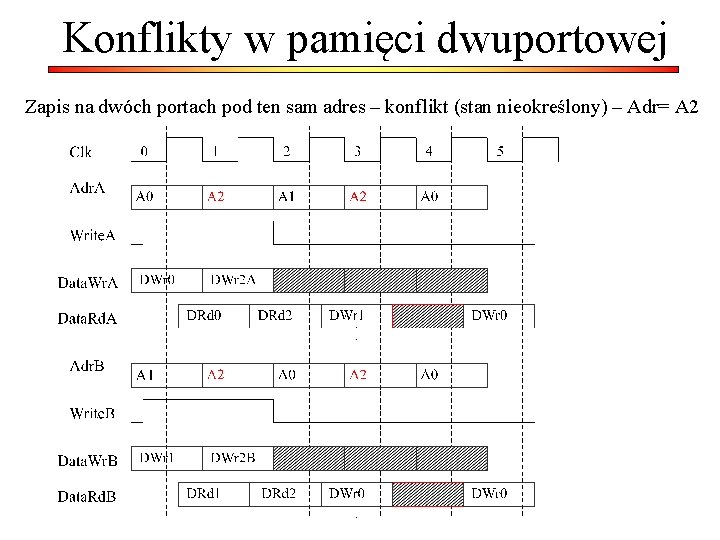

Konflikty w pamięci dwuportowej Zapis na dwóch portach pod ten sam adres – konflikt (stan nieokreślony) – Adr= A 2

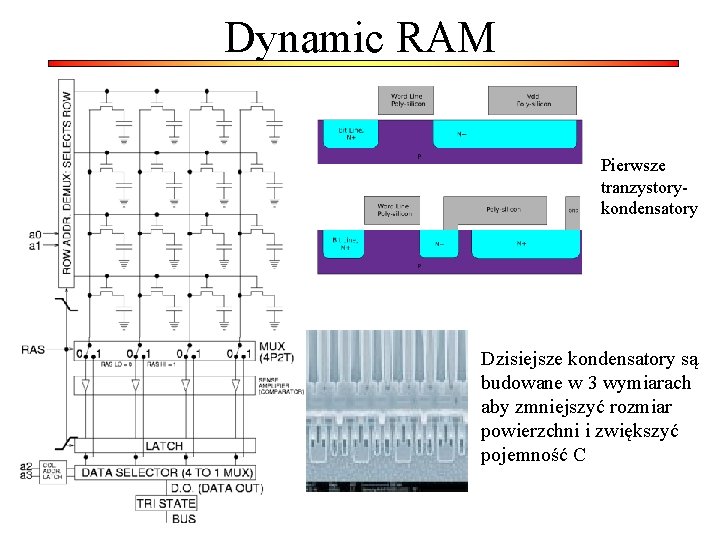

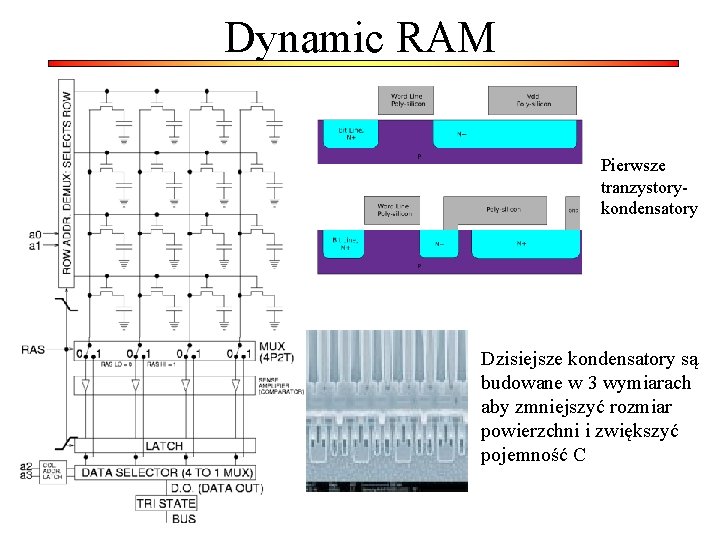

Dynamic RAM Pierwsze tranzystorykondensatory Dzisiejsze kondensatory są budowane w 3 wymiarach aby zmniejszyć rozmiar powierzchni i zwiększyć pojemność C

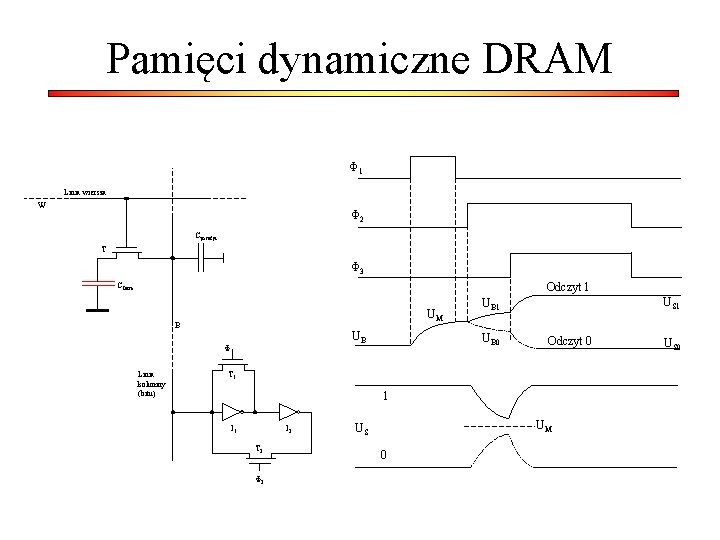

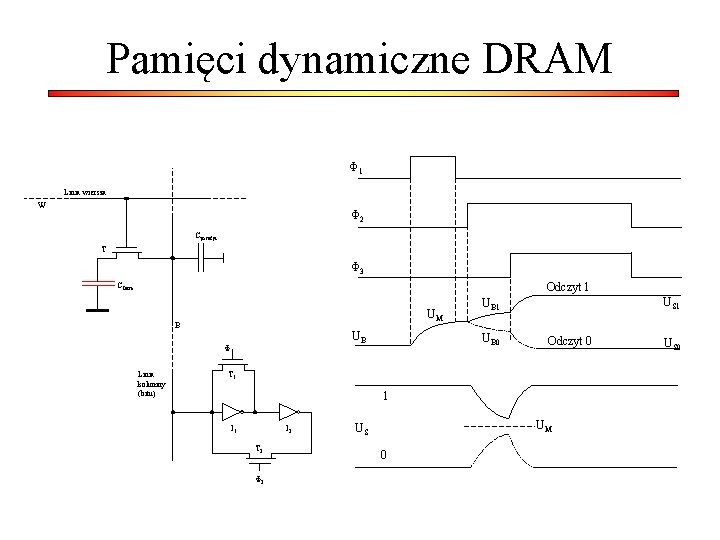

Pamięci dynamiczne DRAM Ф 1 Linia wiersza W Ф 2 Cpasożyt. T Ф 3 Odczyt 1 CStore UM B UB Ф 1 Linia kolumny (bitu) US 1 UB 0 Odczyt 0 T 1 1 I 2 T 2 Ф 3 UM US 0

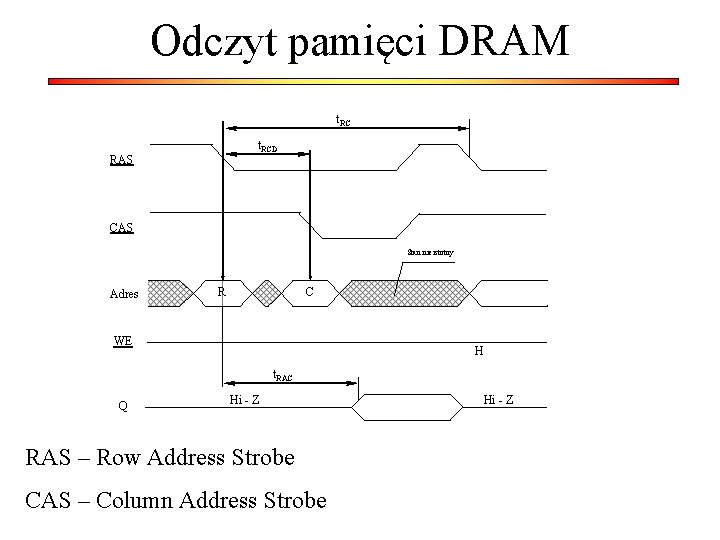

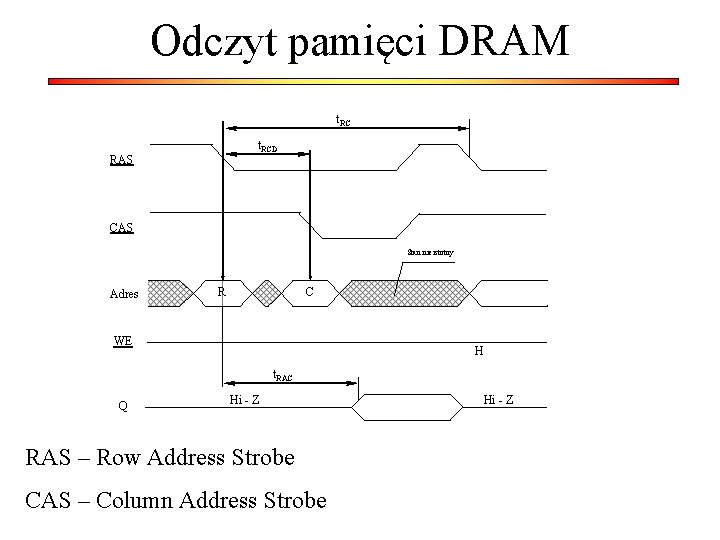

Odczyt pamięci DRAM t. RCD RAS CAS Stan nieistotny Adres R C WE H t. RAC Q Hi - Z RAS – Row Address Strobe CAS – Column Address Strobe Hi - Z

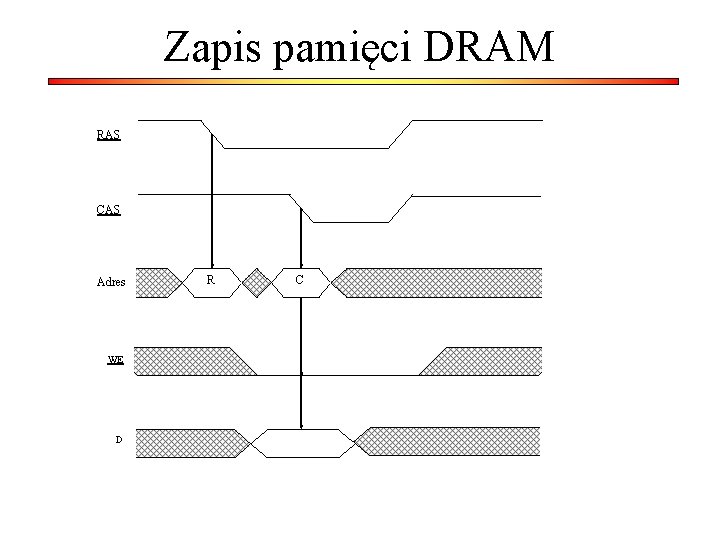

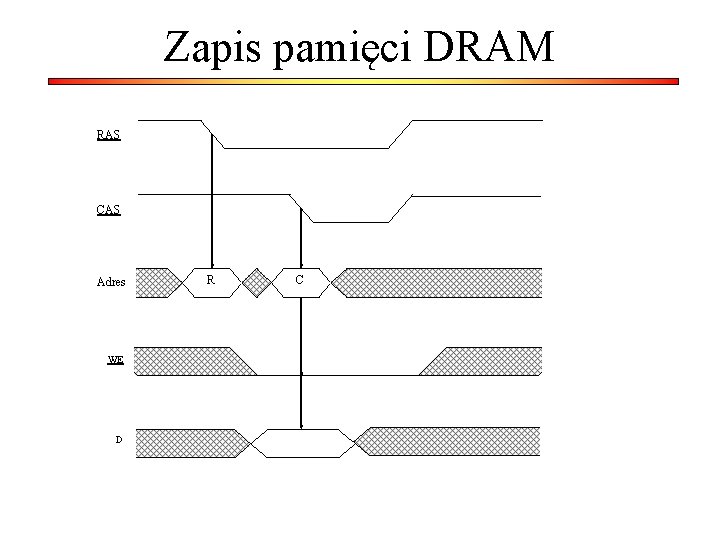

Zapis pamięci DRAM RAS CAS Adres WE D R C

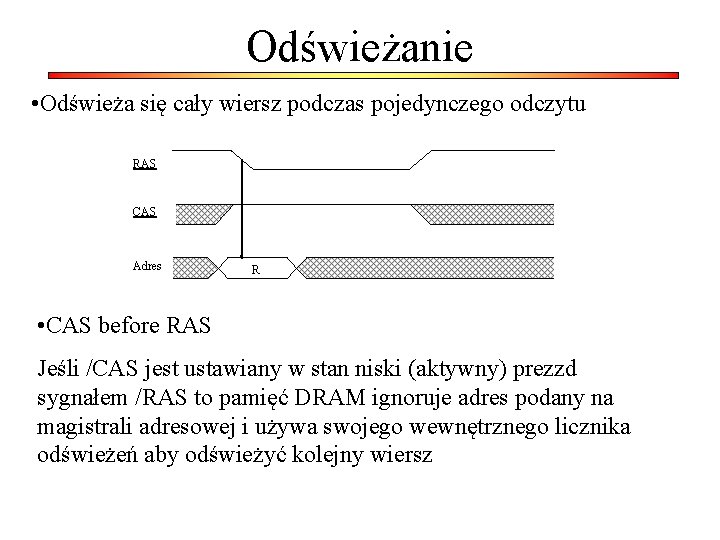

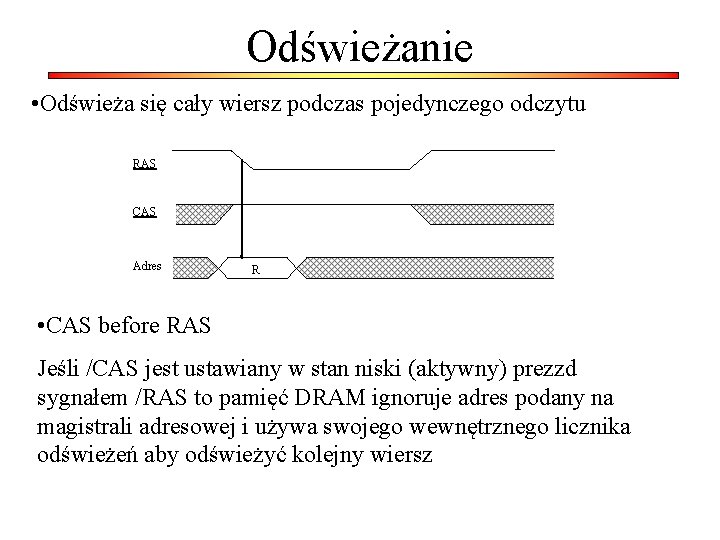

Odświeżanie • Odświeża się cały wiersz podczas pojedynczego odczytu RAS CAS Adres R • CAS before RAS Jeśli /CAS jest ustawiany w stan niski (aktywny) prezzd sygnałem /RAS to pamięć DRAM ignoruje adres podany na magistrali adresowej i używa swojego wewnętrznego licznika odświeżeń aby odświeżyć kolejny wiersz

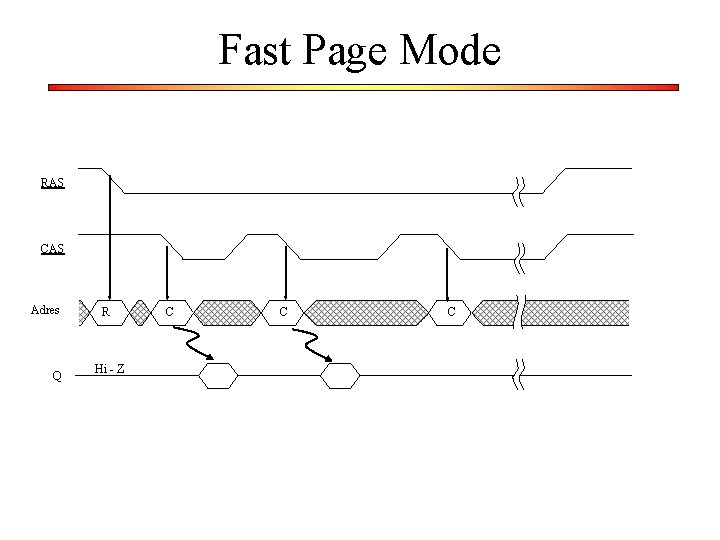

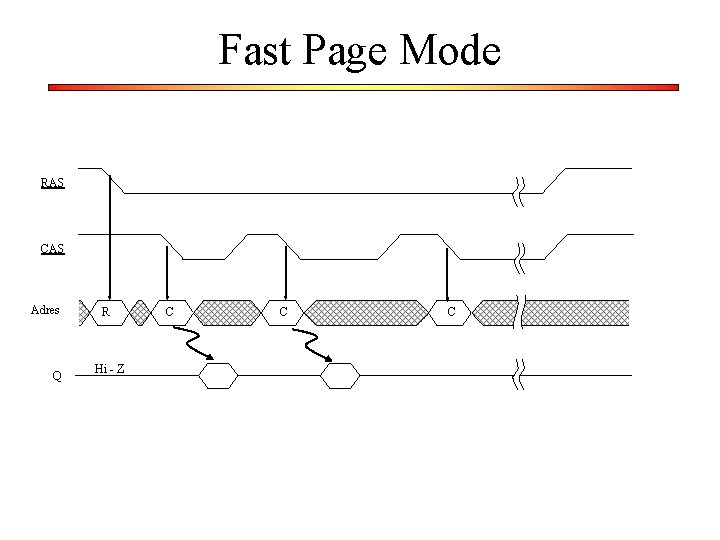

Fast Page Mode RAS CAS Adres Q R Hi - Z C C C

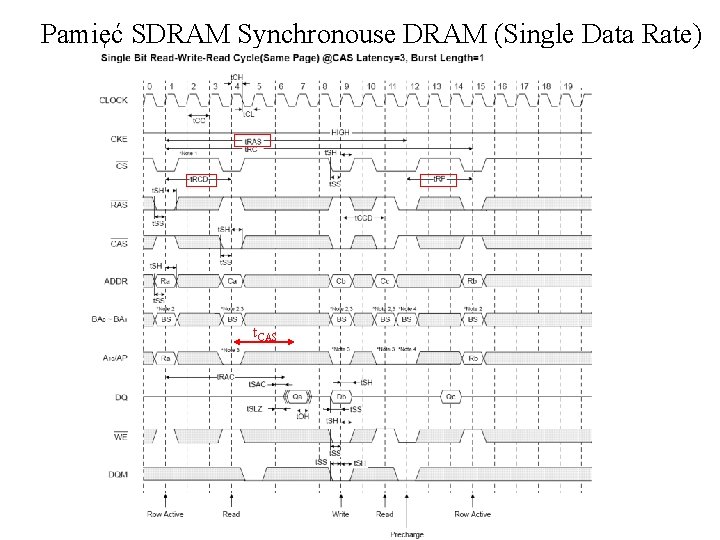

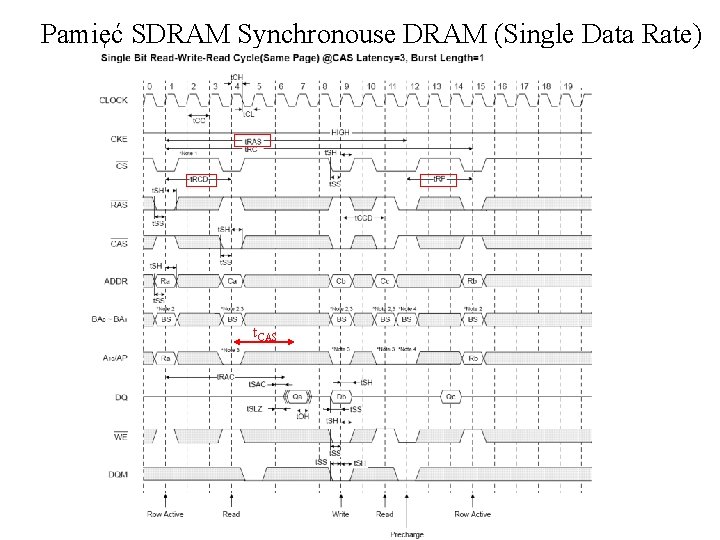

Pamięć SDRAM Synchronouse DRAM (Single Data Rate) t. CAS

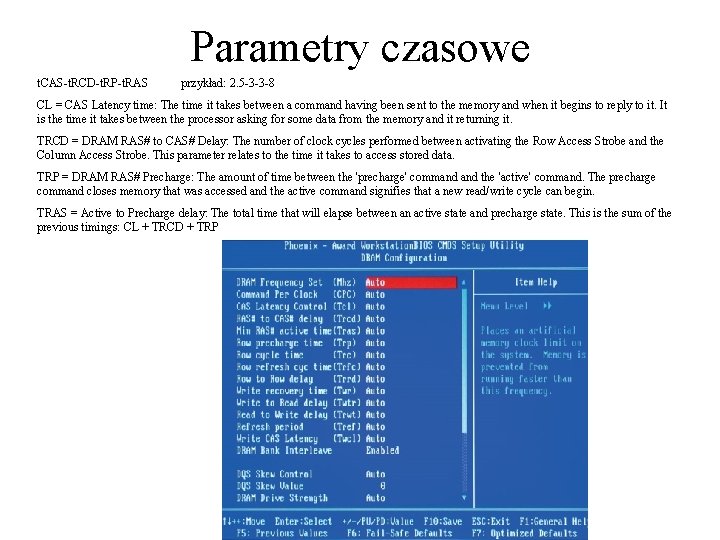

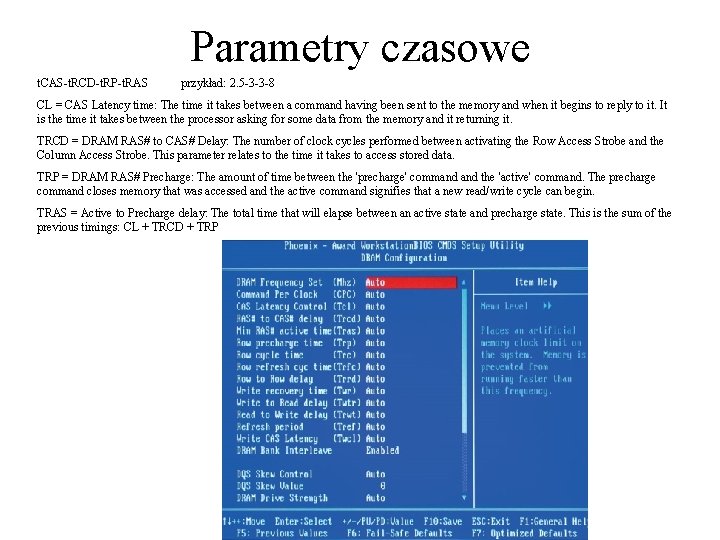

Parametry czasowe t. CAS-t. RCD-t. RP-t. RAS przykład: 2. 5 -3 -3 -8 CL = CAS Latency time: The time it takes between a command having been sent to the memory and when it begins to reply to it. It is the time it takes between the processor asking for some data from the memory and it returning it. TRCD = DRAM RAS# to CAS# Delay: The number of clock cycles performed between activating the Row Access Strobe and the Column Access Strobe. This parameter relates to the time it takes to access stored data. TRP = DRAM RAS# Precharge: The amount of time between the 'precharge' command the 'active' command. The precharge command closes memory that was accessed and the active command signifies that a new read/write cycle can begin. TRAS = Active to Precharge delay: The total time that will elapse between an active state and precharge state. This is the sum of the previous timings: CL + TRCD + TRP

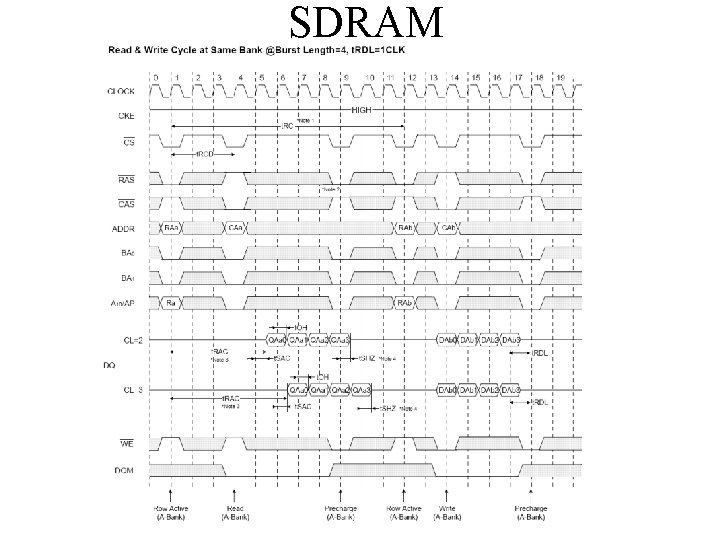

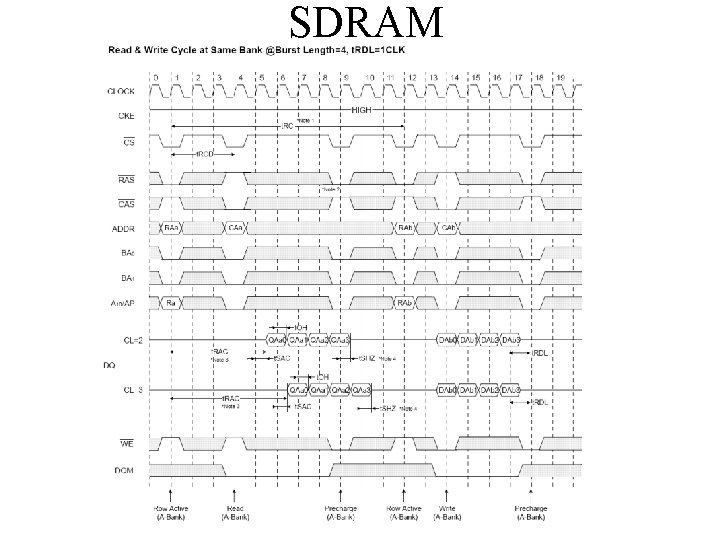

SDRAM

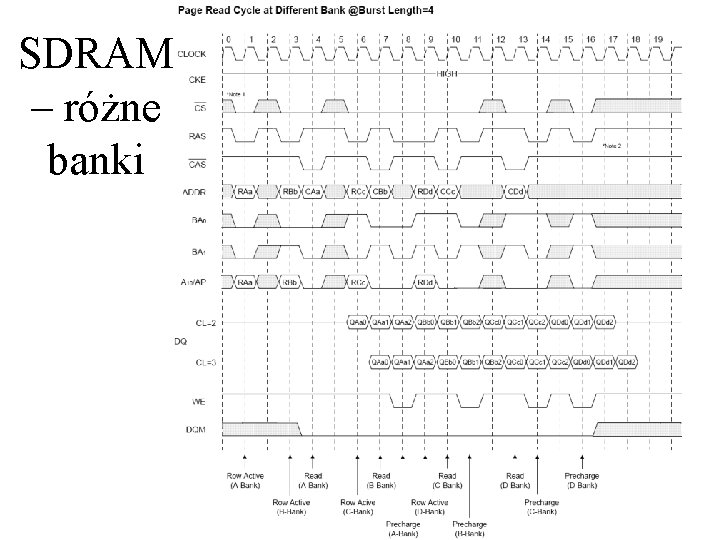

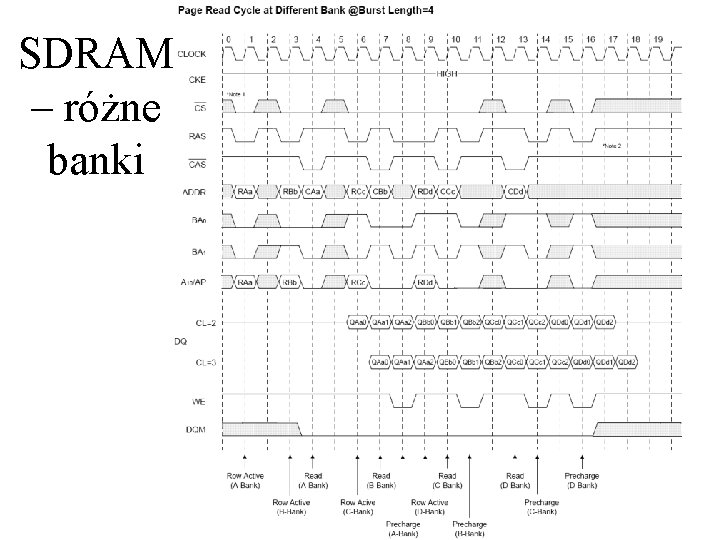

SDRAM – różne banki

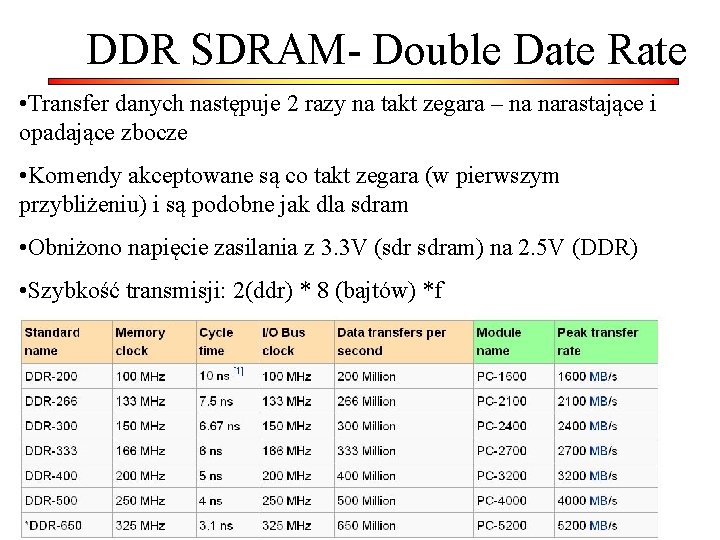

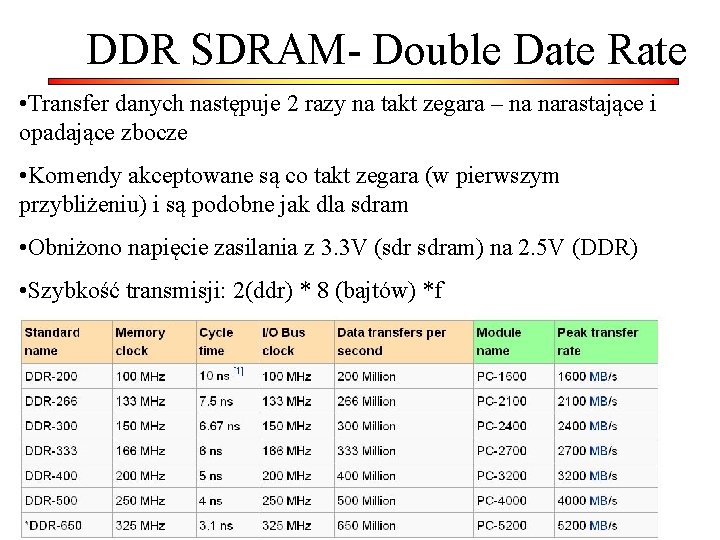

DDR SDRAM- Double Date Rate • Transfer danych następuje 2 razy na takt zegara – na narastające i opadające zbocze • Komendy akceptowane są co takt zegara (w pierwszym przybliżeniu) i są podobne jak dla sdram • Obniżono napięcie zasilania z 3. 3 V (sdr sdram) na 2. 5 V (DDR) • Szybkość transmisji: 2(ddr) * 8 (bajtów) *f

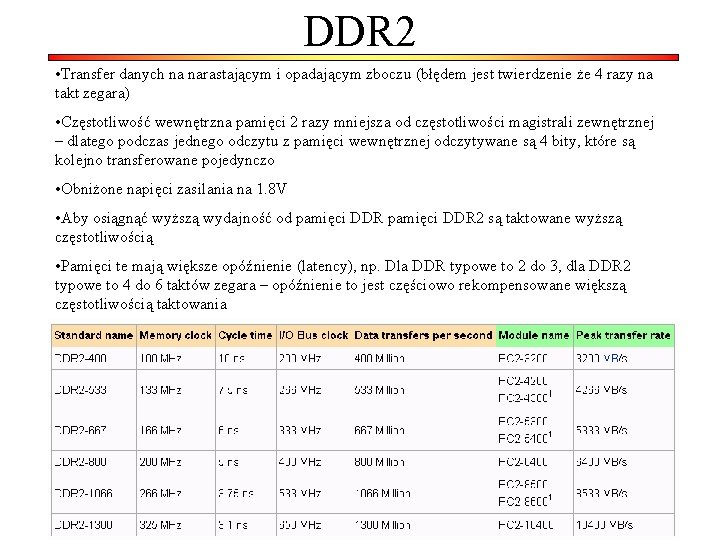

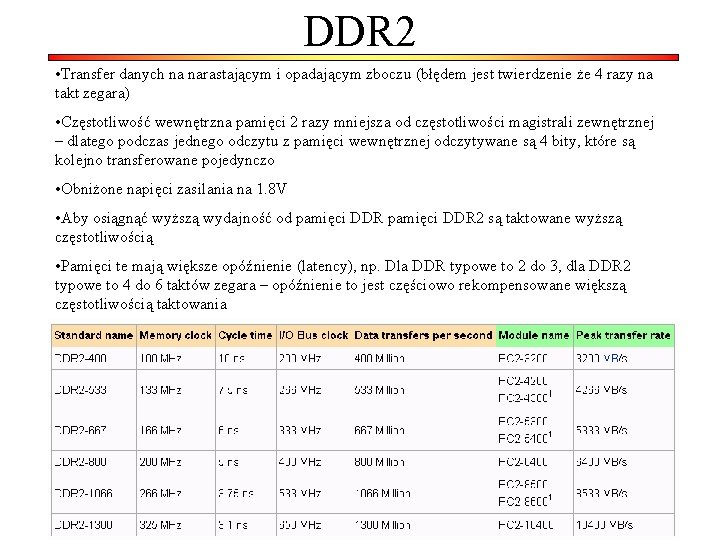

DDR 2 • Transfer danych na narastającym i opadającym zboczu (błędem jest twierdzenie że 4 razy na takt zegara) • Częstotliwość wewnętrzna pamięci 2 razy mniejsza od częstotliwości magistrali zewnętrznej – dlatego podczas jednego odczytu z pamięci wewnętrznej odczytywane są 4 bity, które są kolejno transferowane pojedynczo • Obniżone napięci zasilania na 1. 8 V • Aby osiągnąć wyższą wydajność od pamięci DDR 2 są taktowane wyższą częstotliwością • Pamięci te mają większe opóźnienie (latency), np. Dla DDR typowe to 2 do 3, dla DDR 2 typowe to 4 do 6 taktów zegara – opóźnienie to jest częściowo rekompensowane większą częstotliwością taktowania

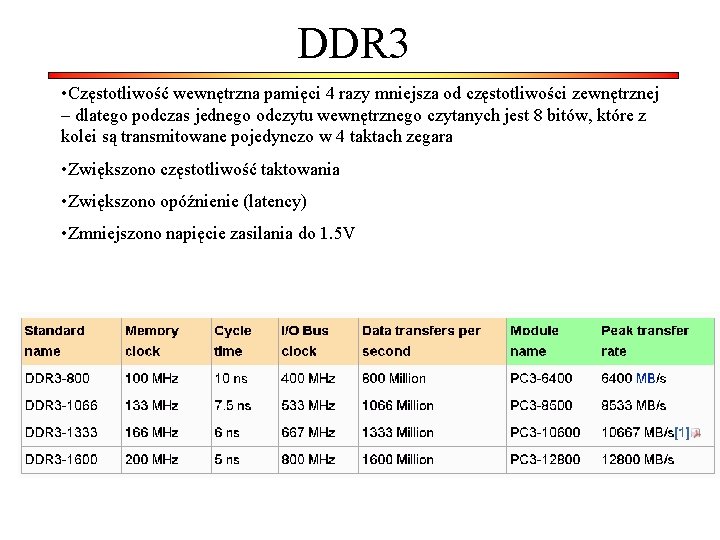

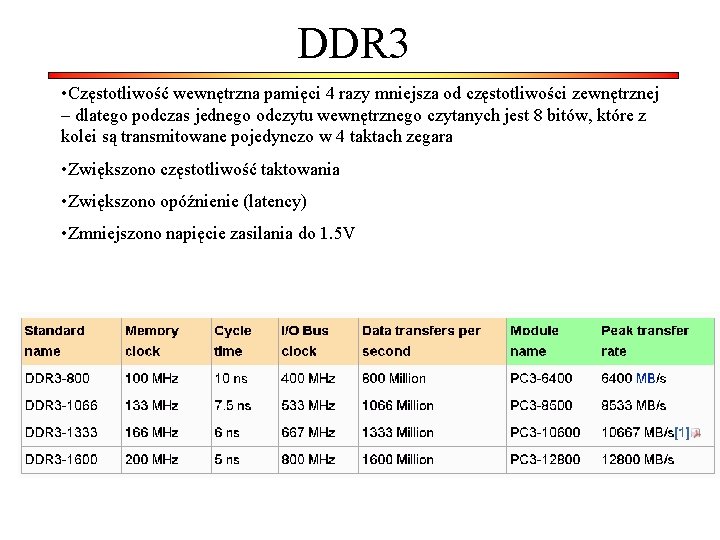

DDR 3 • Częstotliwość wewnętrzna pamięci 4 razy mniejsza od częstotliwości zewnętrznej – dlatego podczas jednego odczytu wewnętrznego czytanych jest 8 bitów, które z kolei są transmitowane pojedynczo w 4 taktach zegara • Zwiększono częstotliwość taktowania • Zwiększono opóźnienie (latency) • Zmniejszono napięcie zasilania do 1. 5 V

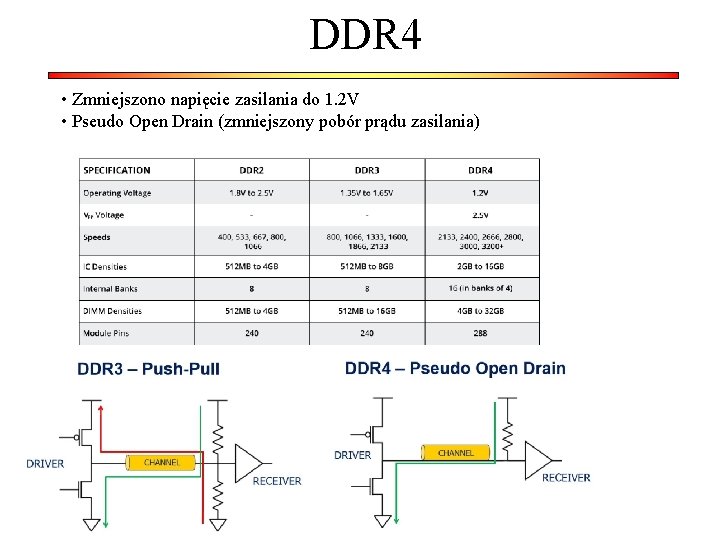

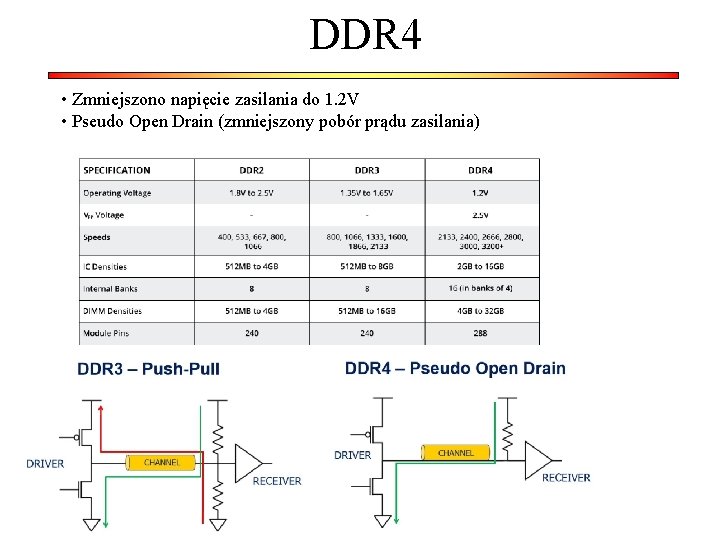

DDR 4 • Zmniejszono napięcie zasilania do 1. 2 V • Pseudo Open Drain (zmniejszony pobór prądu zasilania)

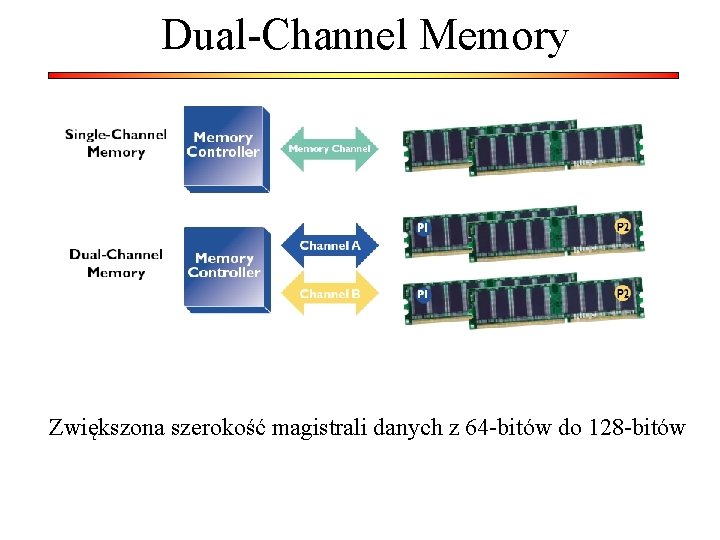

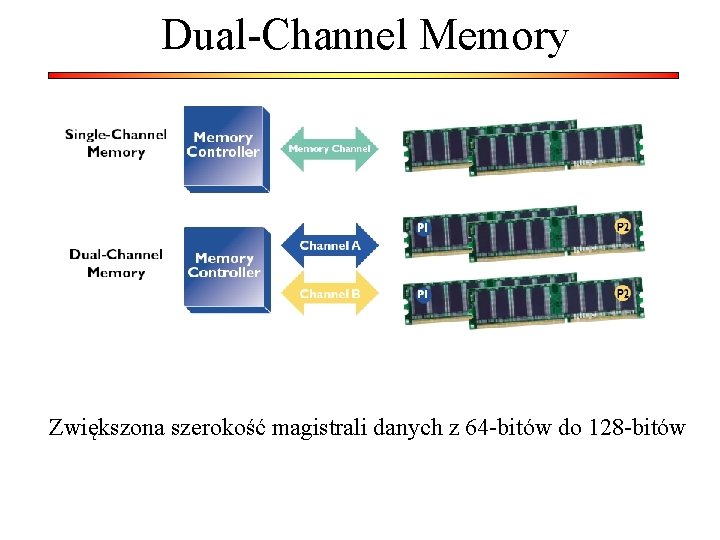

Dual-Channel Memory Zwiększona szerokość magistrali danych z 64 -bitów do 128 -bitów

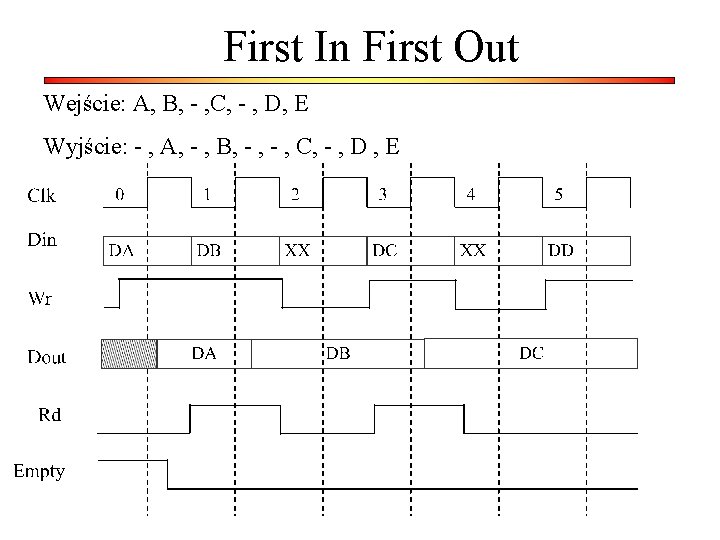

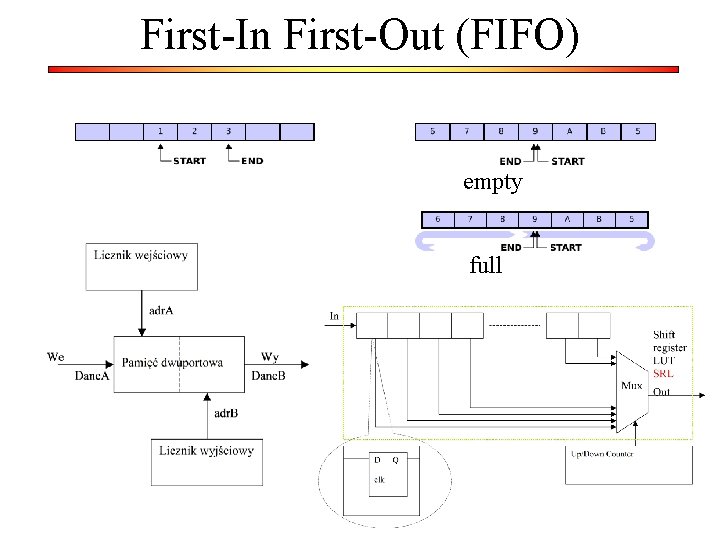

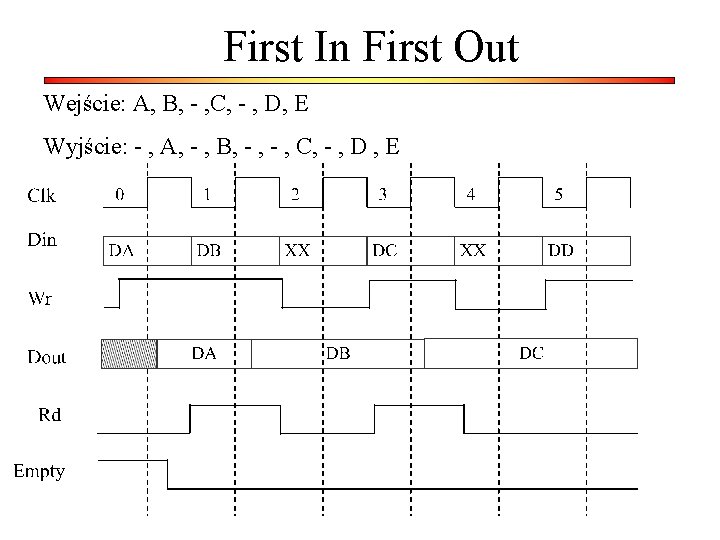

First In First Out Wejście: A, B, - , C, - , D, E Wyjście: - , A, - , B, - , C, - , D , E

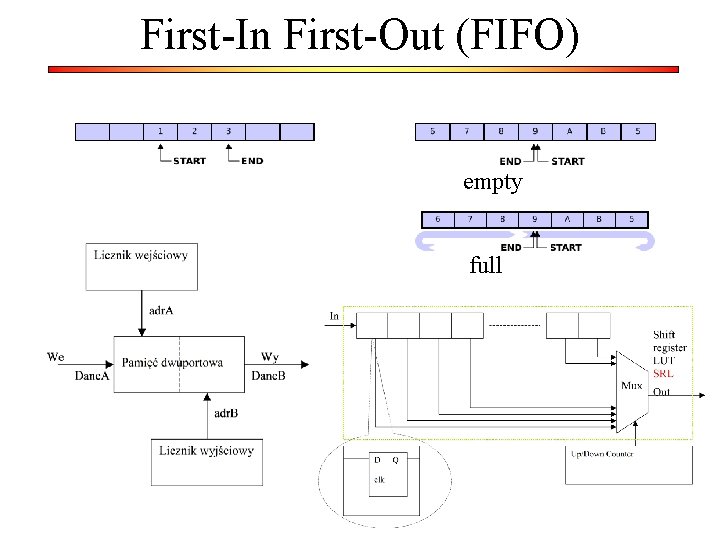

First-In First-Out (FIFO) empty full

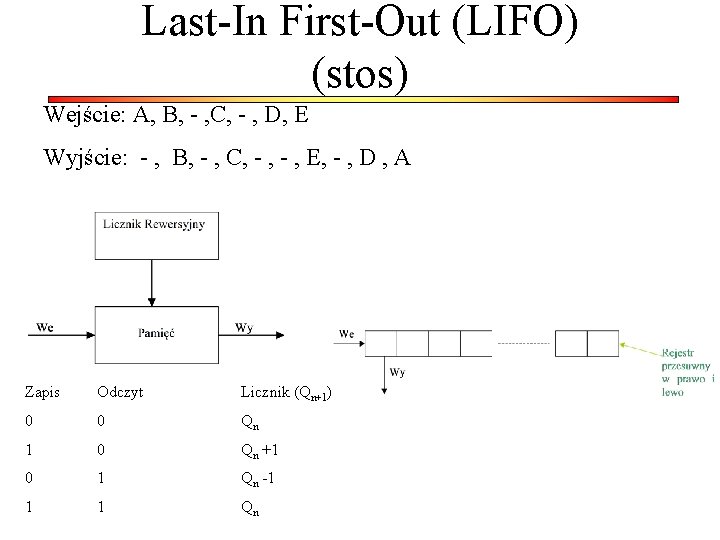

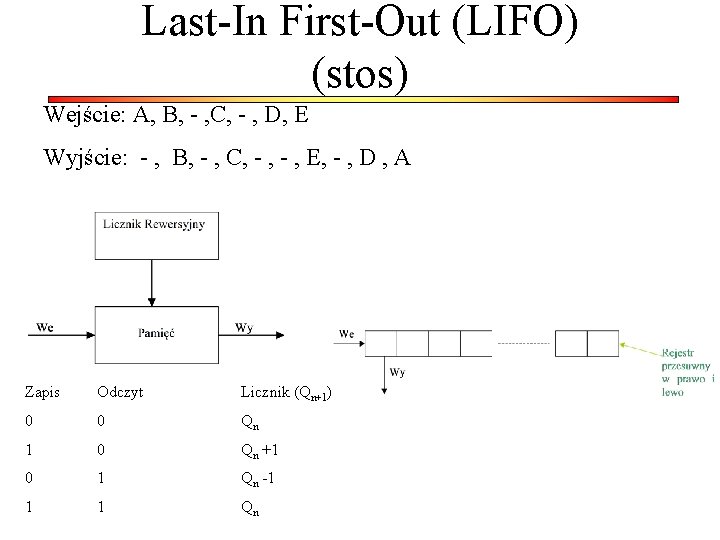

Last-In First-Out (LIFO) (stos) Wejście: A, B, - , C, - , D, E Wyjście: - , B, - , C, - , E, - , D , A Zapis Odczyt Licznik (Qn+1) 0 0 Qn 1 0 Qn +1 0 1 Qn -1 1 1 Qn

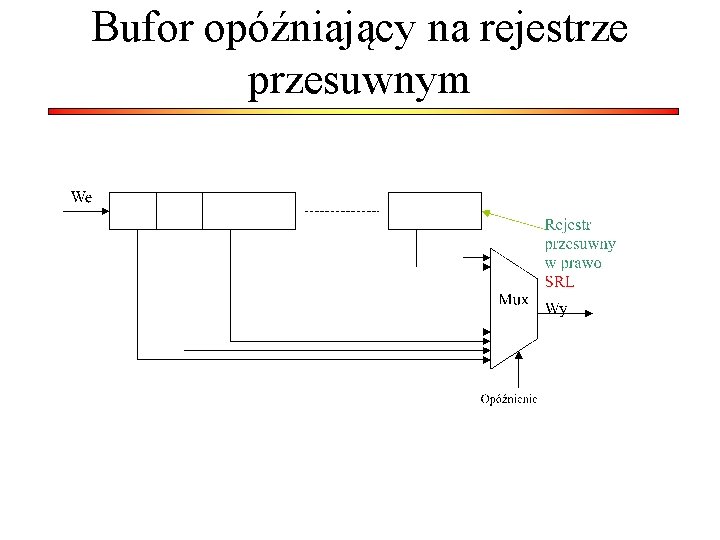

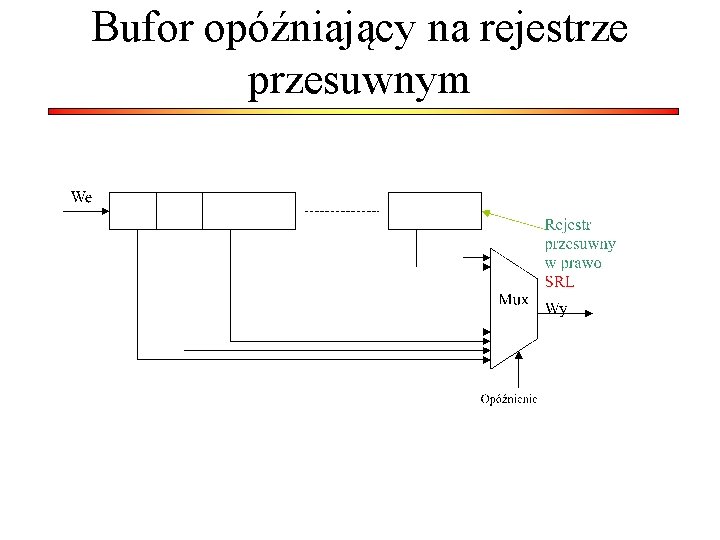

Bufor opóźniający na rejestrze przesuwnym

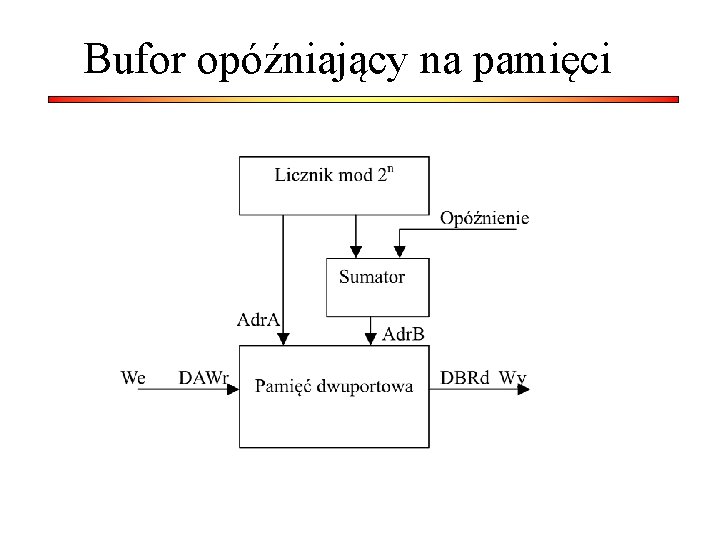

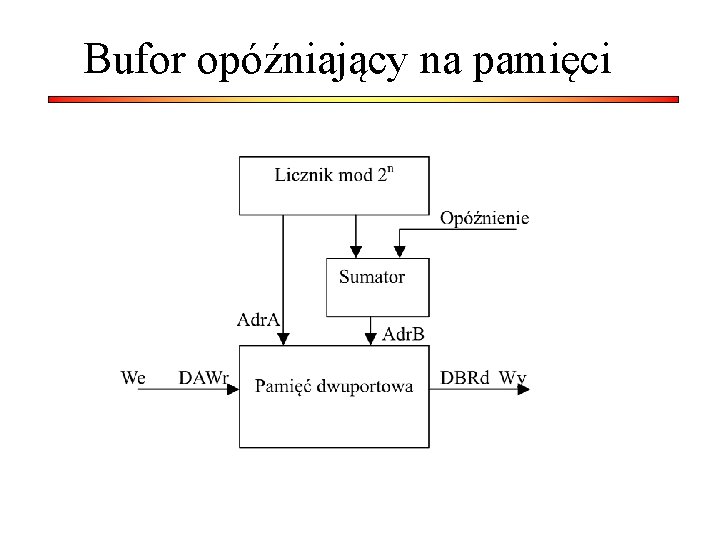

Bufor opóźniający na pamięci

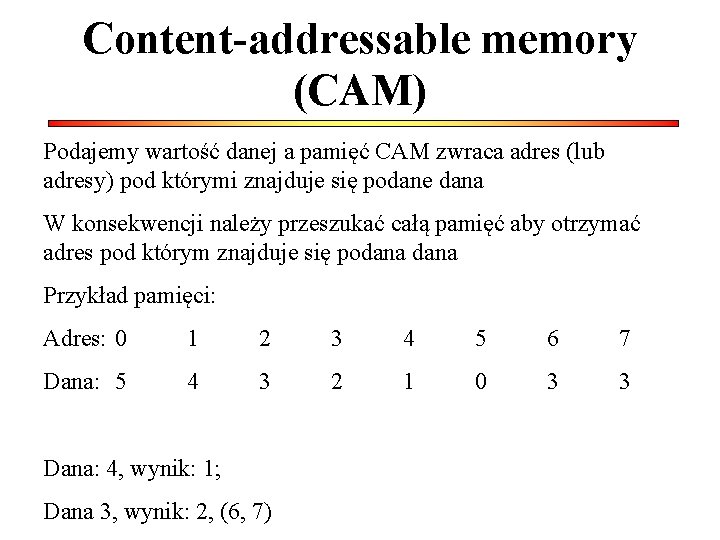

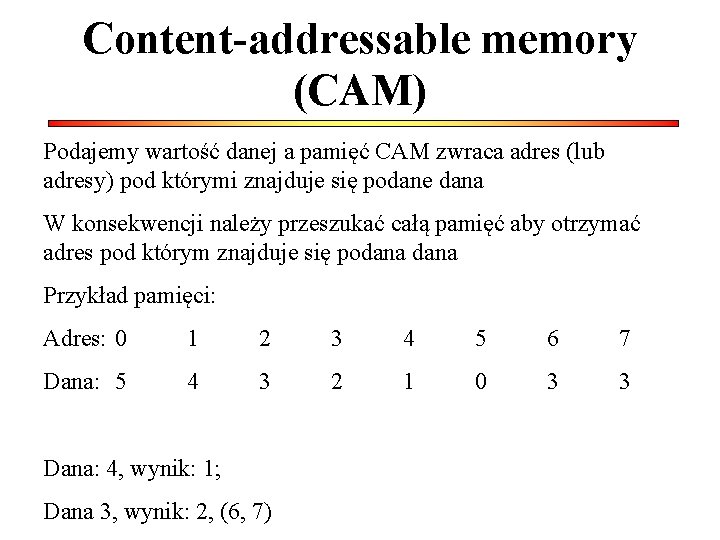

Content-addressable memory (CAM) Podajemy wartość danej a pamięć CAM zwraca adres (lub adresy) pod którymi znajduje się podane dana W konsekwencji należy przeszukać całą pamięć aby otrzymać adres pod którym znajduje się podana Przykład pamięci: Adres: 0 1 2 3 4 5 6 7 Dana: 5 4 3 2 1 0 3 3 Dana: 4, wynik: 1; Dana 3, wynik: 2, (6, 7)

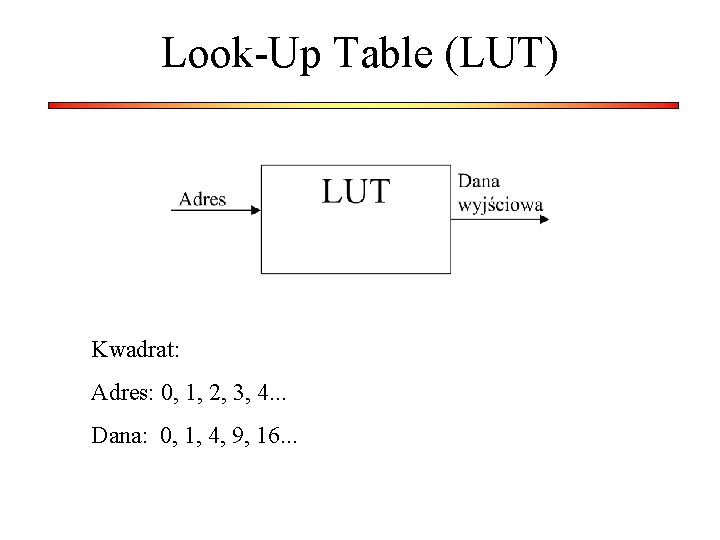

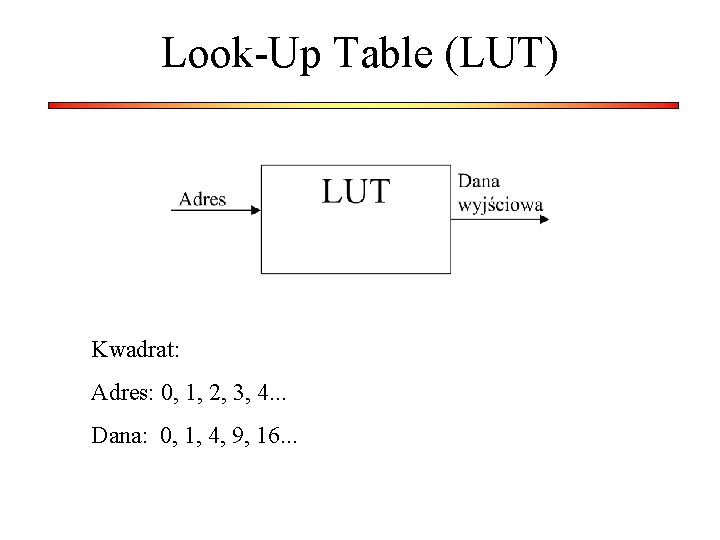

Look-Up Table (LUT) Kwadrat: Adres: 0, 1, 2, 3, 4. . . Dana: 0, 1, 4, 9, 16. . .

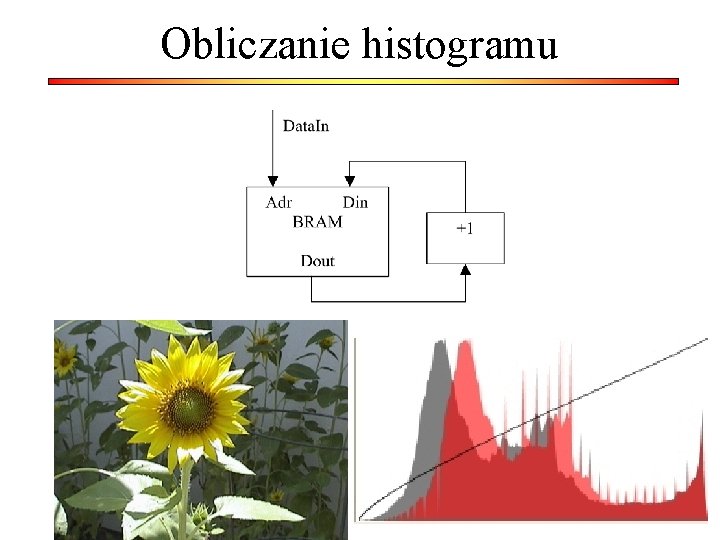

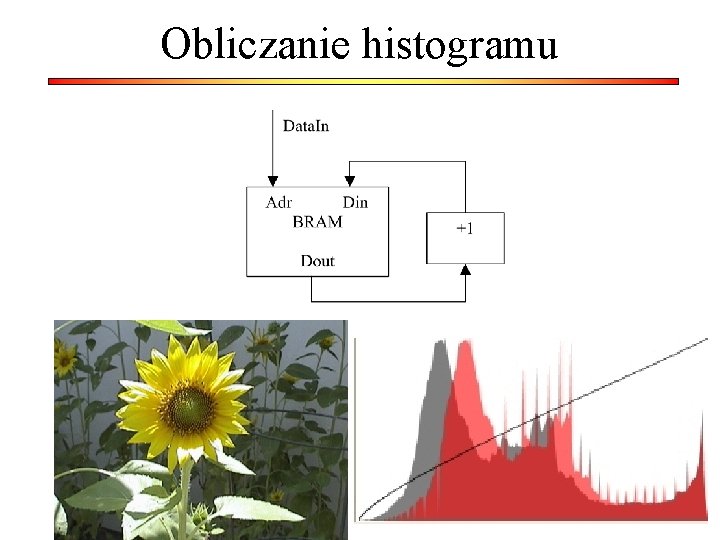

Obliczanie histogramu

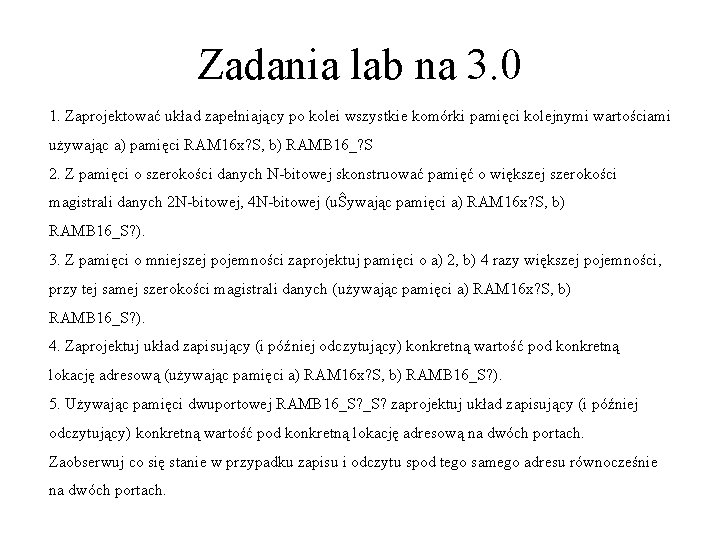

Zadania lab na 3. 0 1. Zaprojektować układ zapełniający po kolei wszystkie komórki pamięci kolejnymi wartościami używając a) pamięci RAM 16 x? S, b) RAMB 16_? S 2. Z pamięci o szerokości danych N-bitowej skonstruować pamięć o większej szerokości magistrali danych 2 N-bitowej, 4 N-bitowej (uŜywając pamięci a) RAM 16 x? S, b) RAMB 16_S? ). 3. Z pamięci o mniejszej pojemności zaprojektuj pamięci o a) 2, b) 4 razy większej pojemności, przy tej samej szerokości magistrali danych (używając pamięci a) RAM 16 x? S, b) RAMB 16_S? ). 4. Zaprojektuj układ zapisujący (i później odczytujący) konkretną wartość pod konkretną lokację adresową (używając pamięci a) RAM 16 x? S, b) RAMB 16_S? ). 5. Używając pamięci dwuportowej RAMB 16_S? zaprojektuj układ zapisujący (i później odczytujący) konkretną wartość pod konkretną lokację adresową na dwóch portach. Zaobserwuj co się stanie w przypadku zapisu i odczytu spod tego samego adresu równocześnie na dwóch portach.

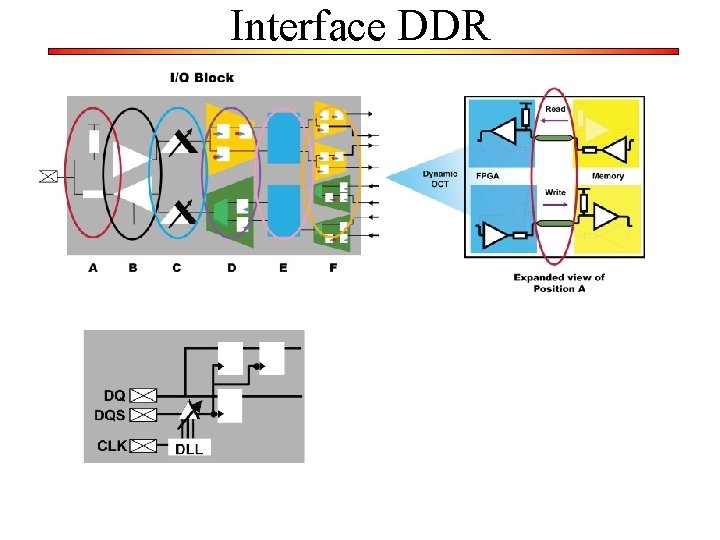

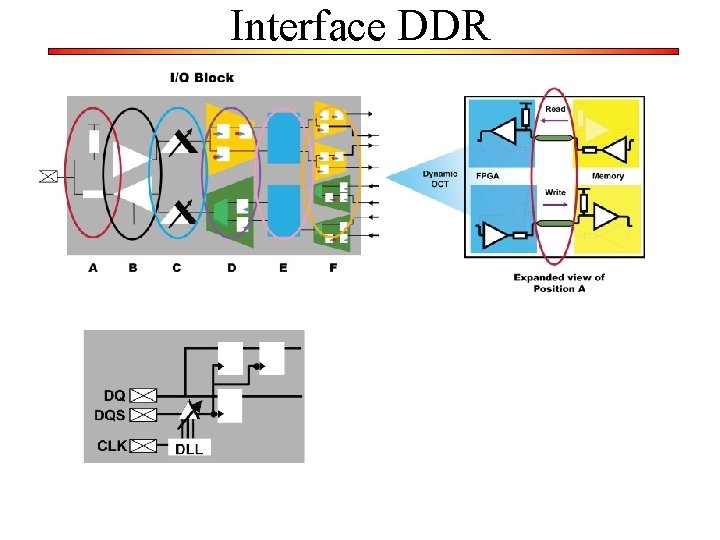

Interface DDR

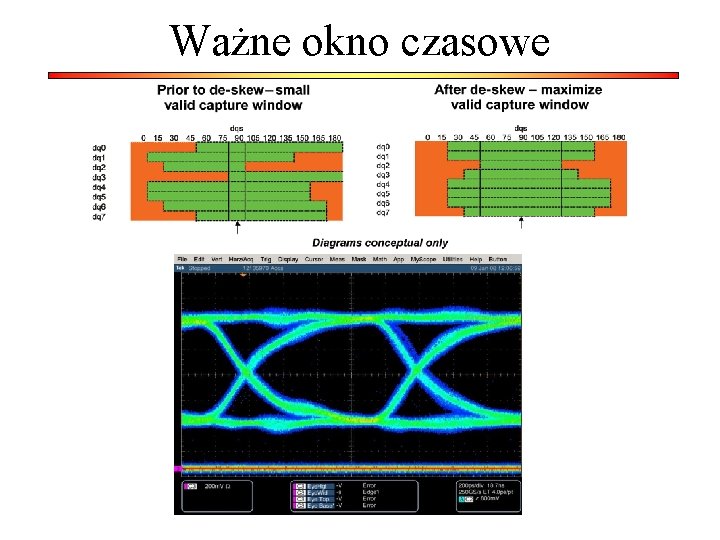

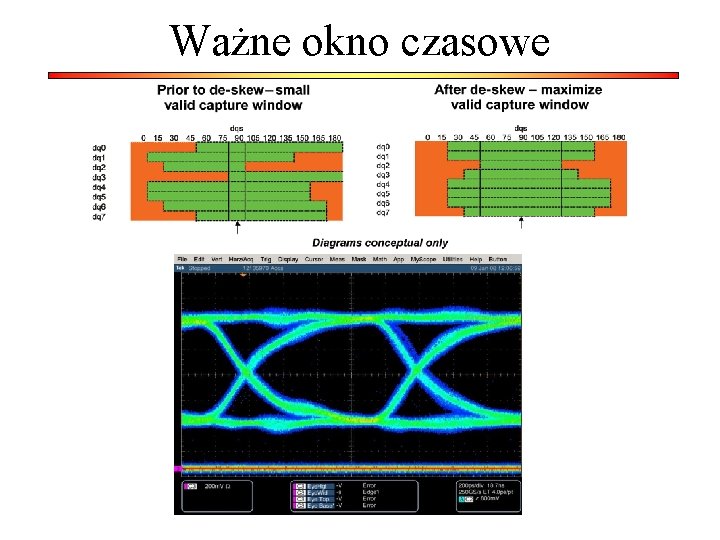

Ważne okno czasowe

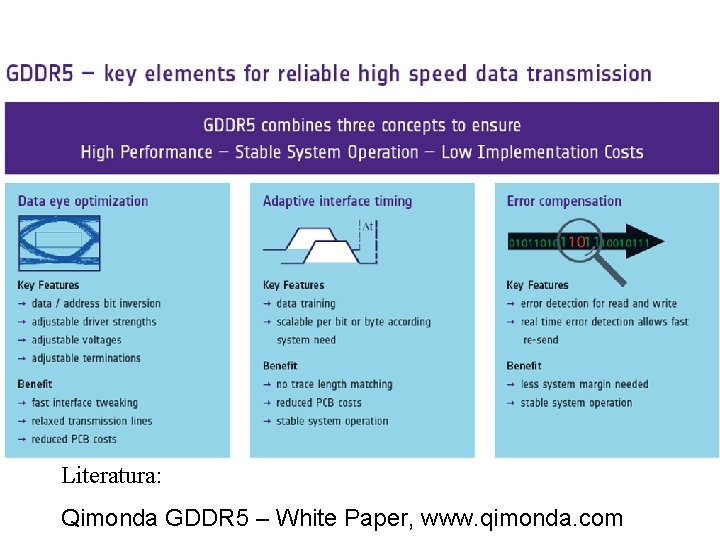

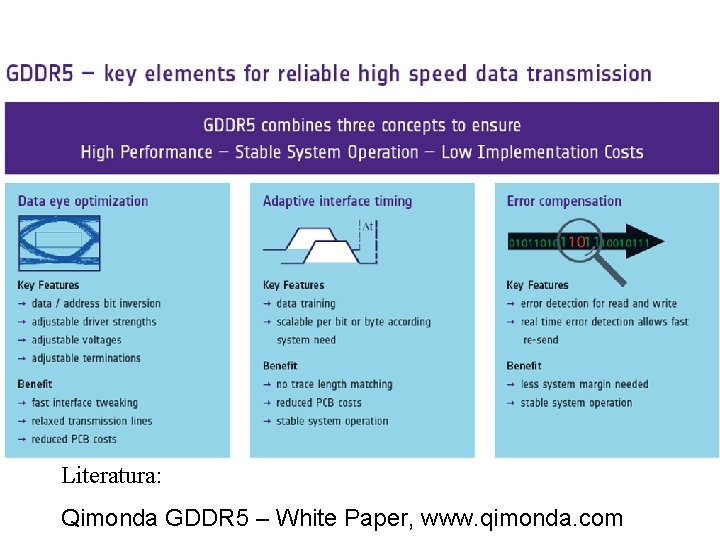

Literatura: Qimonda GDDR 5 – White Paper, www. qimonda. com

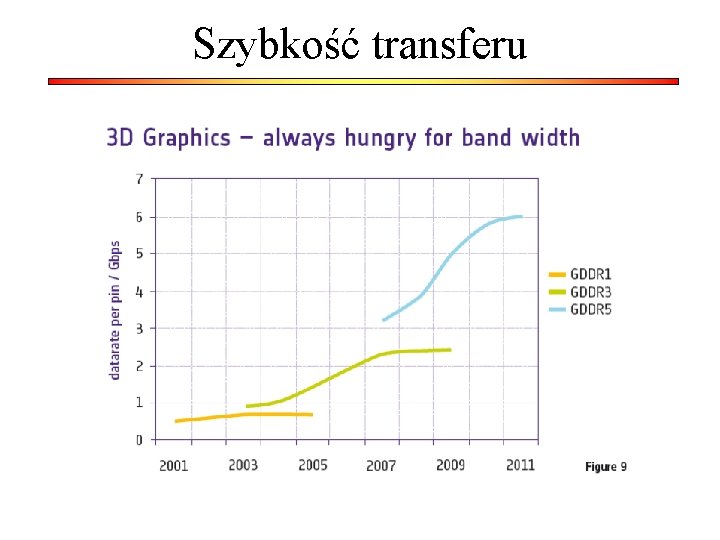

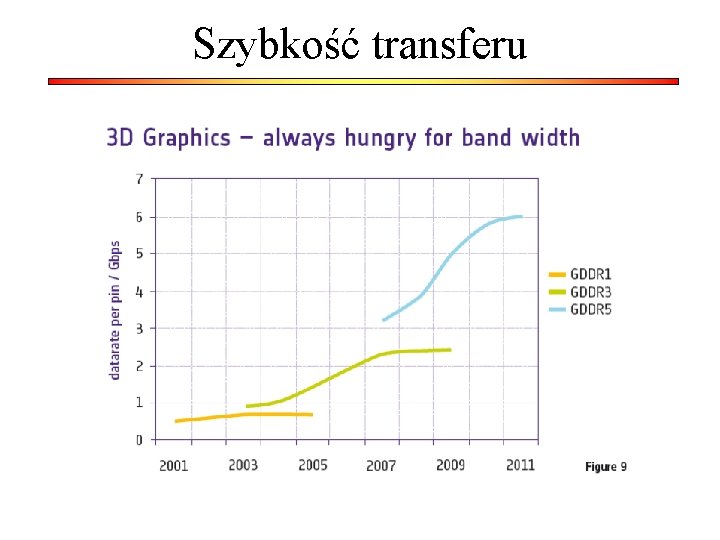

Szybkość transferu

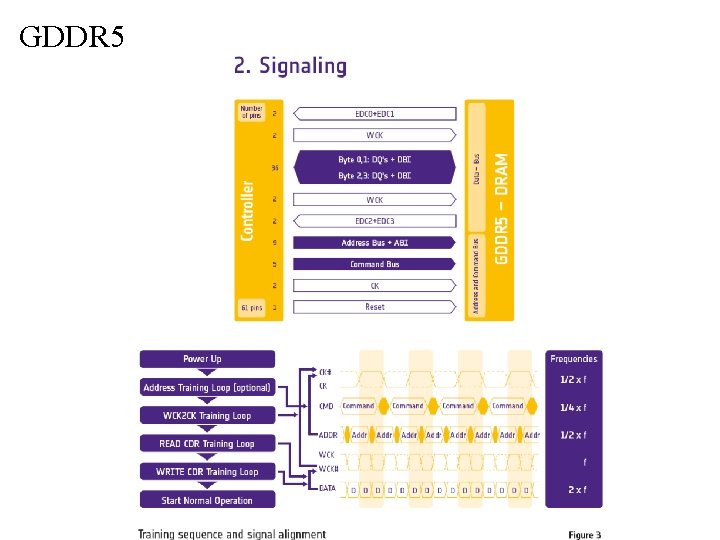

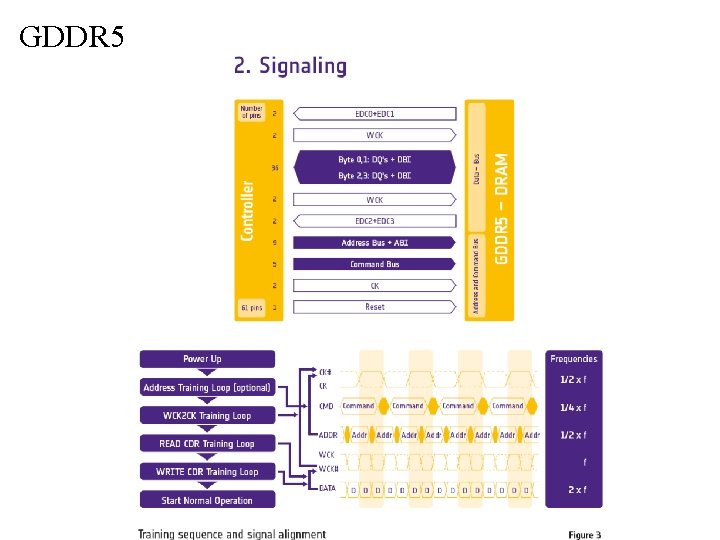

GDDR 5

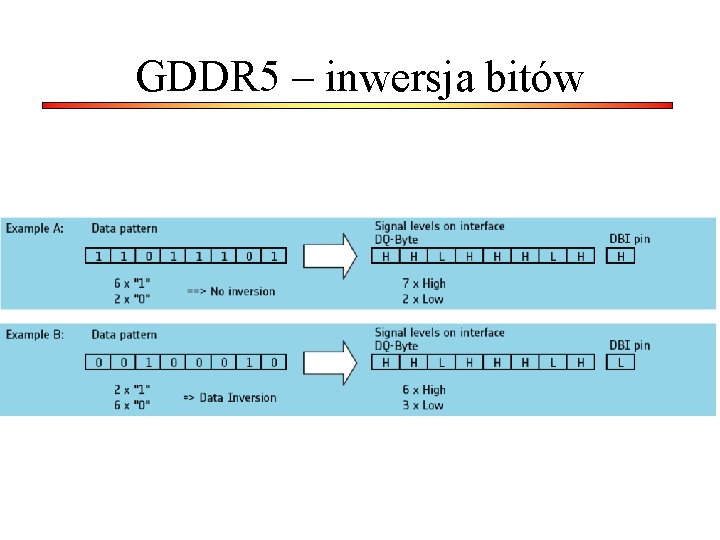

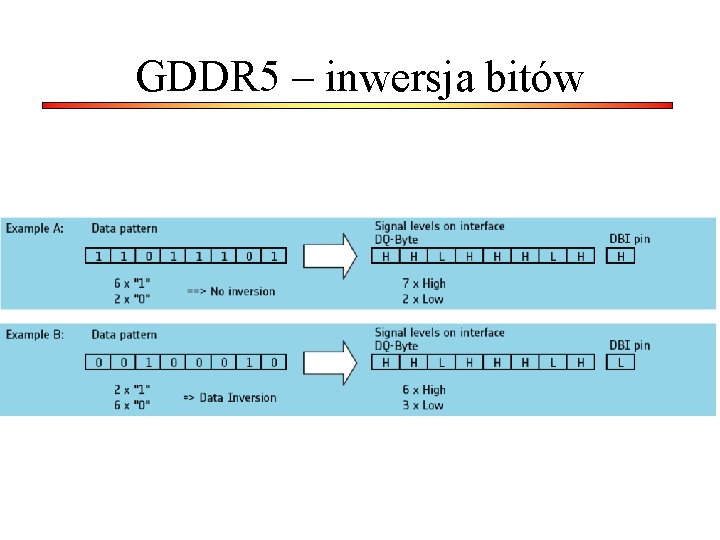

GDDR 5 – inwersja bitów

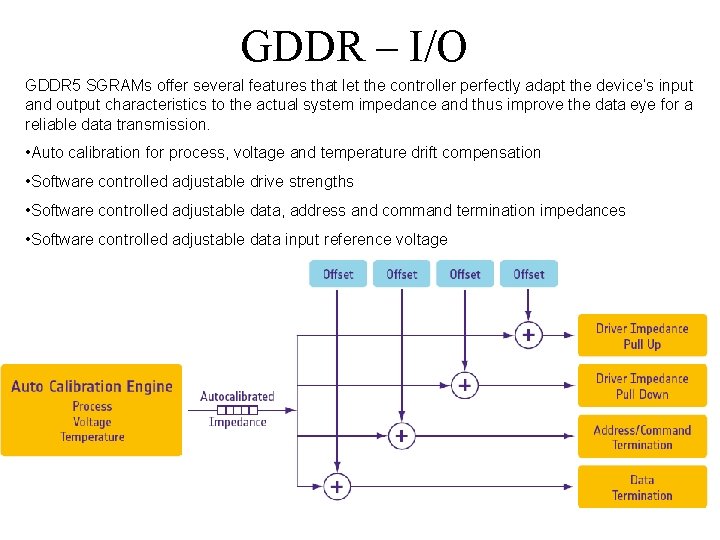

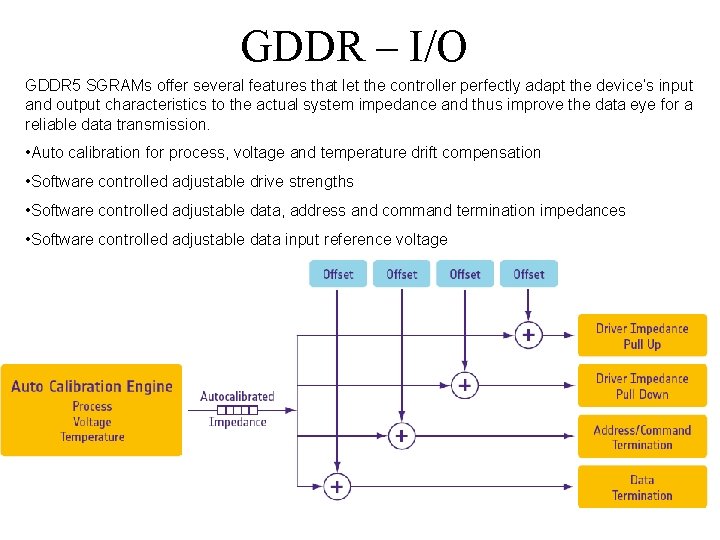

GDDR – I/O GDDR 5 SGRAMs offer several features that let the controller perfectly adapt the device’s input and output characteristics to the actual system impedance and thus improve the data eye for a reliable data transmission. • Auto calibration for process, voltage and temperature drift compensation • Software controlled adjustable drive strengths • Software controlled adjustable data, address and command termination impedances • Software controlled adjustable data input reference voltage

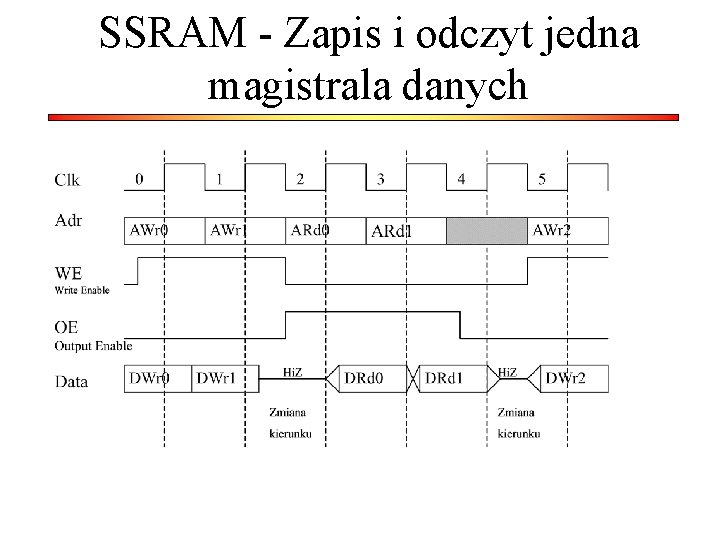

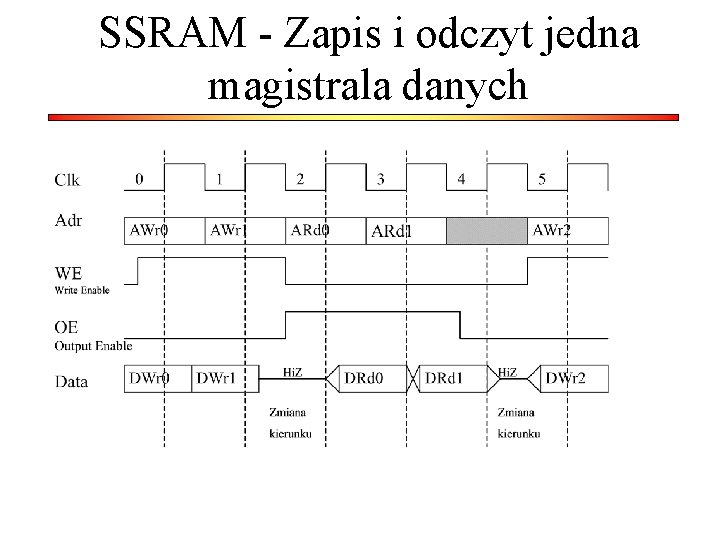

SSRAM - Zapis i odczyt jedna magistrala danych

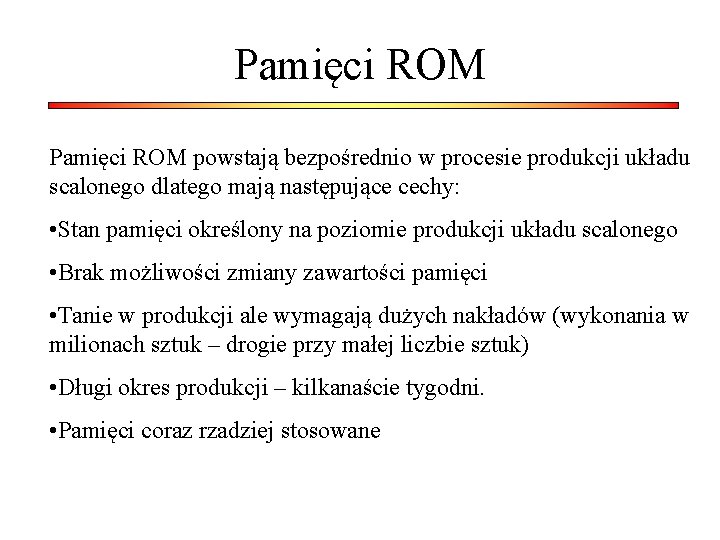

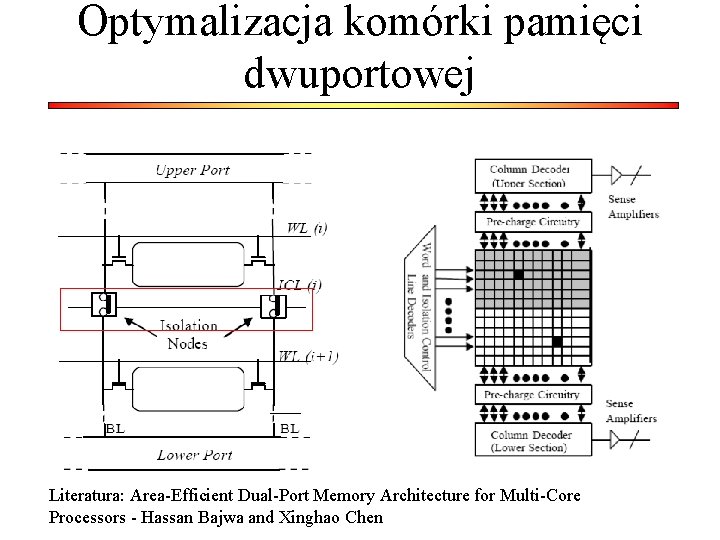

Optymalizacja komórki pamięci dwuportowej Literatura: Area-Efficient Dual-Port Memory Architecture for Multi-Core Processors - Hassan Bajwa and Xinghao Chen