Overview RAM ROM Logic Example 1 Chapter 14

- Slides: 21

Overview RAM ROM Logic - Example 1 Chapter 14 Memories SKEE 1223 Digital Electronics Mun’im/Arif/Izam FKE, Universiti Teknologi Malaysia February 10, 2017 ROM Logic - Example 2

Overview RAM ROM 1 Overview 2 RAM 3 ROM 4 ROM Logic - Example 1 5 ROM Logic - Example 2 ROM Logic - Example 1 ROM Logic - Example 2

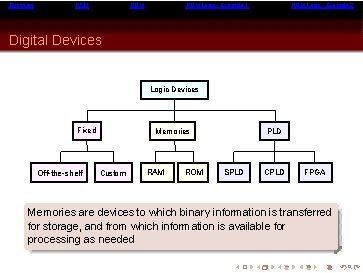

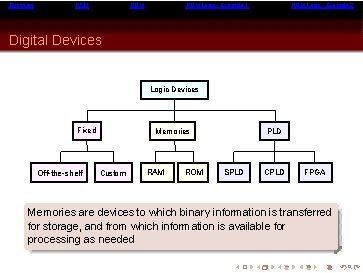

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Digital Devices Logic Devices Fixed Off-the-shelf Memories Custom RAM ROM PLD SPLD CPLD FPGA Memories are devices to which binary information is transferred for storage, and from which information is available for processing as needed

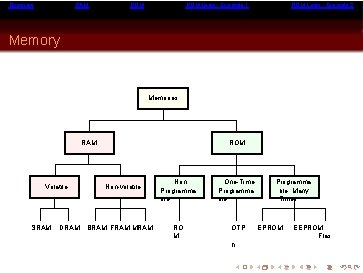

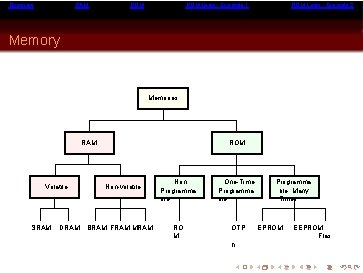

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Memory Memories RAM Volatile SRAM DRAM ROM Non-volatile BRAM FRAM MRAM Non Programma ble One-Time Programma ble RO M OTP h Programma ble Many Times EPROM EEPROM Flas

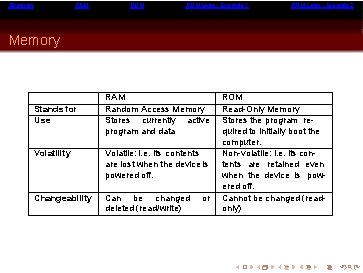

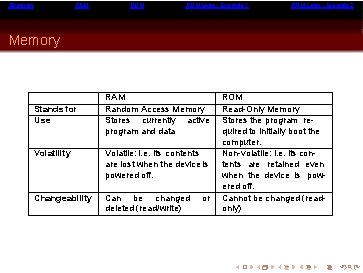

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Memory Stands for Use RAM Random Access Memory Stores currently active program and data Volatility Volatile: i. e. its contents are lost when the device is powered off. Changeability Can be changed deleted (read/write) or ROM Read-Only Memory Stores the program required to initially boot the computer. Non-volatile: i. e. its contents are retained even when the device is powered off. Cannot be changed (readonly)

Overview RAM ROM Logic - Example 1 Memory Simplified Data input lines n Address lines READ WRITE k Memory unit 2 k words n bits/word n Data output lines ROM Logic - Example 2

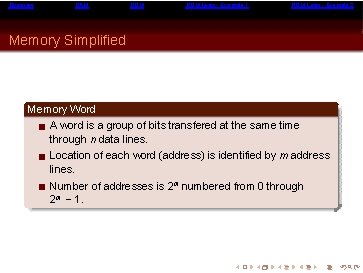

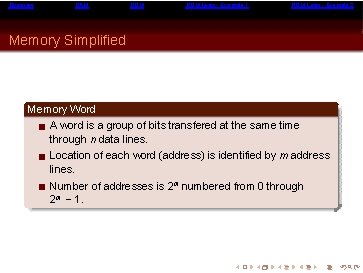

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Memory Simplified Memory Word A word is a group of bits transfered at the same time through n data lines. Location of each word (address) is identified by m address lines. Number of addresses is 2 m numbered from 0 through 2 m − 1.

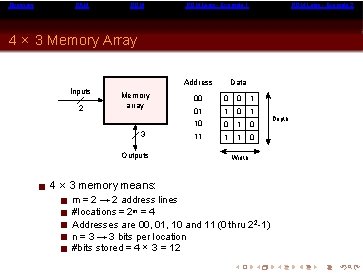

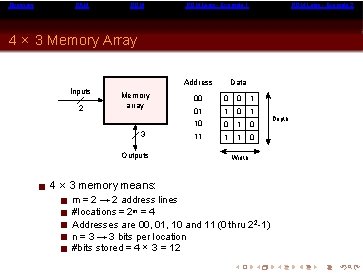

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 4 × 3 Memory Array Address Inputs 2 Memory array 3 Outputs Data 00 0 0 1 01 1 0 1 10 0 11 1 1 0 Width 4 × 3 memory means: m = 2 → 2 address lines #locations = 2 m = 4 Addresses are 00, 01, 10 and 11 (0 thru 22 -1) n = 3 → 3 bits per location #bits stored = 4 × 3 = 12 Depth

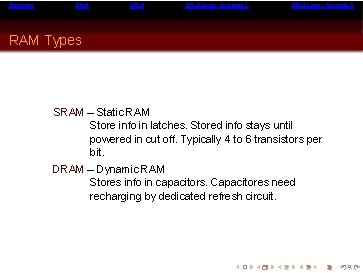

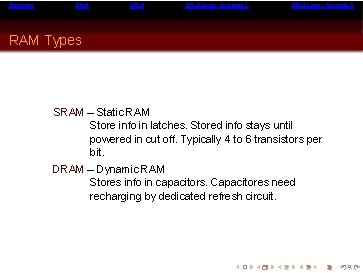

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 RAM Types SRAM – Static RAM Store info in latches. Stored info stays until powered in cut off. Typically 4 to 6 transistors per bit. DRAM – Dynamic RAM Stores info in capacitors. Capacitores need recharging by dedicated refresh circuit.

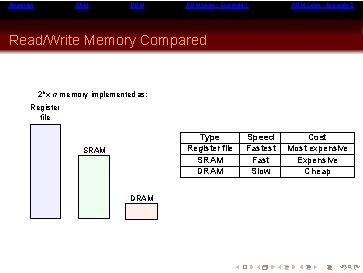

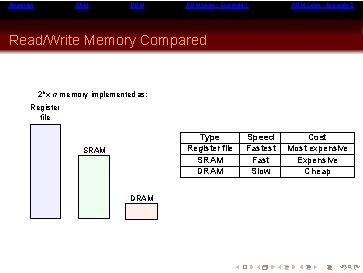

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Read/Write Memory Compared 2 k x n memory implemented as: Register file Type Register file SRAM DRAM Speed Fastest Fast Slow Cost Most expensive Expensive Cheap

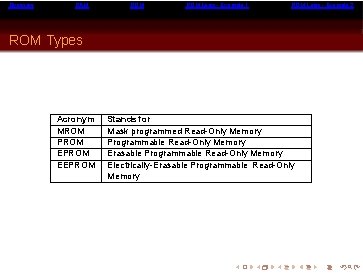

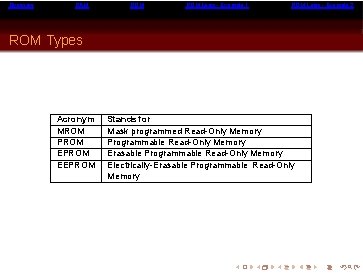

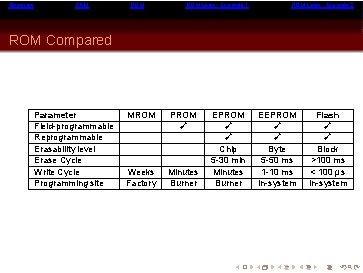

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 ROM Types Acronym MROM PROM EEPROM Stands for Mask programmed Read-Only Memory Programmable Read-Only Memory Erasable Programmable Read-Only Memory Electrically-Erasable Programmable Read-Only Memory

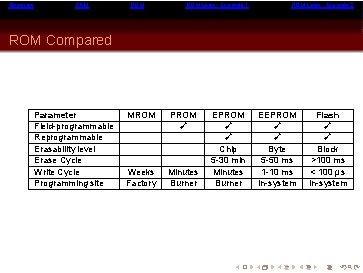

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 ROM Compared Parameter Field-programmable Reprogrammable Erasability level Erase Cycle Write Cycle Programming site MROM PROM ✓ Weeks Factory Minutes Burner EPROM ✓ ✓ Chip 5 -30 min Minutes Burner EEPROM ✓ ✓ Byte 5 -50 ms 1 -10 ms In-system Flash ✓ ✓ Block >100 ms < 100 µs In-system

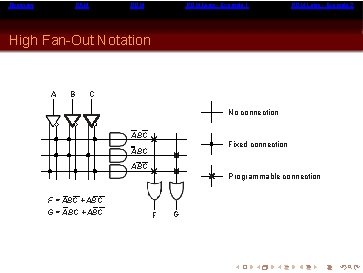

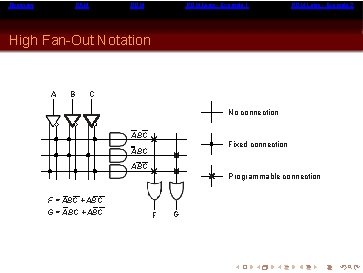

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 High Fan-Out Notation A B C No connection ABC Fixed connection ABC Programmable connection F = ABC + ABC G = ABC + ABC F G

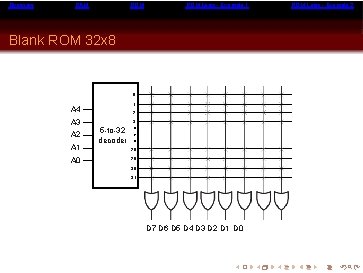

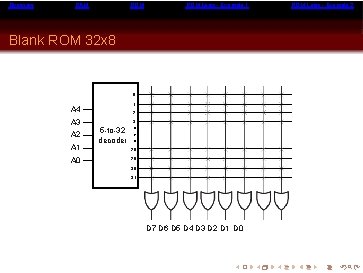

Overview RAM ROM Logic - Example 1 Blank ROM 32 x 8 0 1 A 4 A 3 A 2 A 1 A 0 2 3 5 -to-32 decoder 28 29 30 31 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 ROM Logic - Example 2

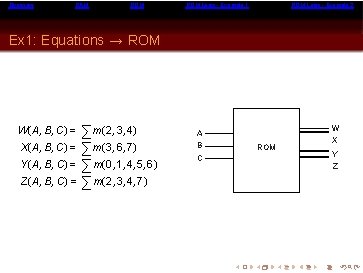

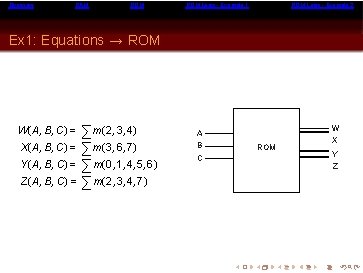

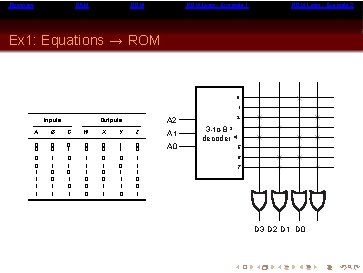

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 1: Equations → ROM ∑ m(2, 3, 4) X (A, B, C) = ∑ m(3, 6, 7) Y (A, B, C) = ∑ m(0, 1, 4, 5, 6) Z (A, B, C) = ∑ m(2, 3, 4, 7) W (A, B, C) = A B C ROM W X Y Z

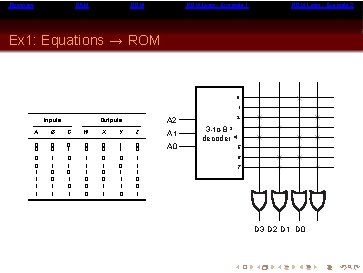

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 1: Equations → ROM Inputs Outputs A B C W X Y Z 0 0 1 1 0 1 0 1 0 0 1 1 1 0 0 0 1 1 1 0 0 1 A A 2 B A 1 C A 0 8 x 4 ROM D 3 W D 2 X D 1 Y D 0 Z

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 1: Equations → ROM 0 1 Inputs A 2 Outputs X Y Z A 1 0 0 1 1 0 0 A 0 1 1 1 0 0 1 1 1 0 0 1 A B C W 0 0 0 1 1 1 0 0 1 1 0 1 0 1 2 3 -to-8 3 decoder 4 5 6 7 D 3 D 2 D 1 D 0

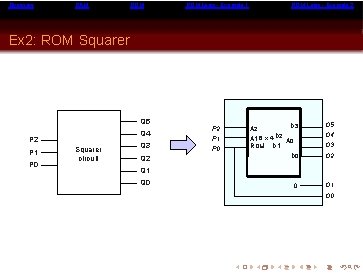

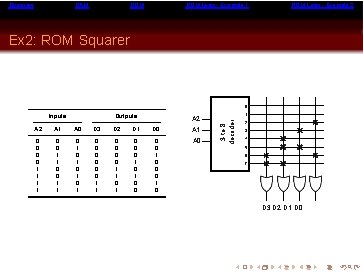

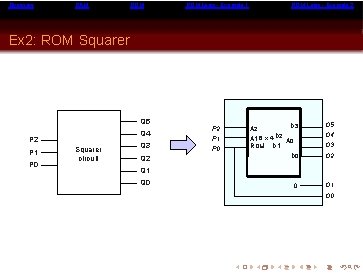

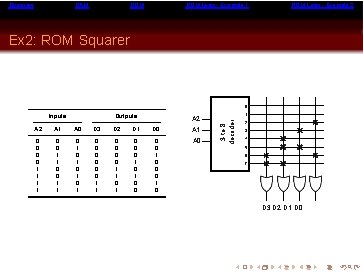

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 2: ROM Squarer Inputs Outputs P 2 P 1 P 0 Q 5 Q 4 Q 3 Q 2 Q 1 Q 0 Decimal 0 0 1 1 0 1 0 1 0 0 0 1 1 0 1 0 0 0 0 0 0 1 0 1 0 1 4 9 16 25 36 49

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 2: ROM Squarer Q 5 Q 4 P 2 P 1 P 0 Squarer circuit Q 3 Q 2 D 3 P 2 A 2 P 1 A 1 8 x 4 D 2 A 0 ROM D 1 P 0 Q 5 Q 4 Q 3 D 0 Q 2 0 Q 1 Q 0

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 Ex 2: ROM Squarer 0 Outputs A 2 A 1 A 0 D 3 D 2 D 1 D 0 A 1 0 0 1 1 0 1 0 1 0 0 0 1 1 0 1 0 0 0 1 0 A 0 1 3 -to-8 decoder Inputs 2 3 4 5 6 7 D 3 D 2 D 1 D 0

Overview RAM ROM Logic - Example 1 ROM Logic - Example 2 SKEE 1223 https: //www. openlearning. com/courses/SKEE 1223 x