Overview of VITA 57 FMC Denis Smetana May

![FMC Signals § 80 Differential Pairs (160 single ended) – LPC [00: 33]; HPC FMC Signals § 80 Differential Pairs (160 single ended) – LPC [00: 33]; HPC](https://slidetodoc.com/presentation_image_h/9dcdad7400931a248dc38a886c26d9a8/image-4.jpg)

- Slides: 13

Overview of VITA 57 - FMC Denis Smetana May 14, 2015

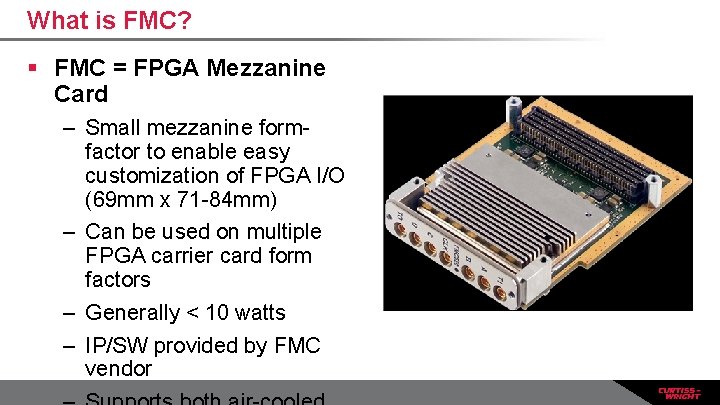

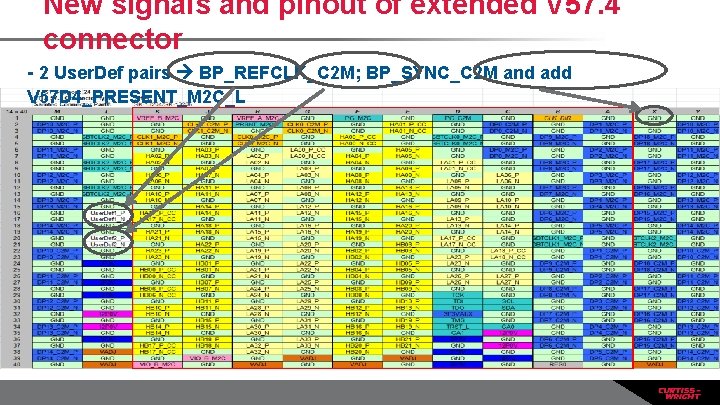

What is FMC? § FMC = FPGA Mezzanine Card – Small mezzanine formfactor to enable easy customization of FPGA I/O (69 mm x 71 -84 mm) – Can be used on multiple FPGA carrier card form factors – Generally < 10 watts – IP/SW provided by FMC vendor

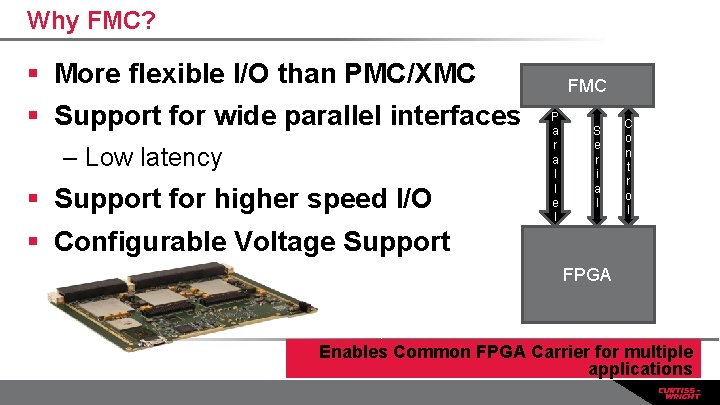

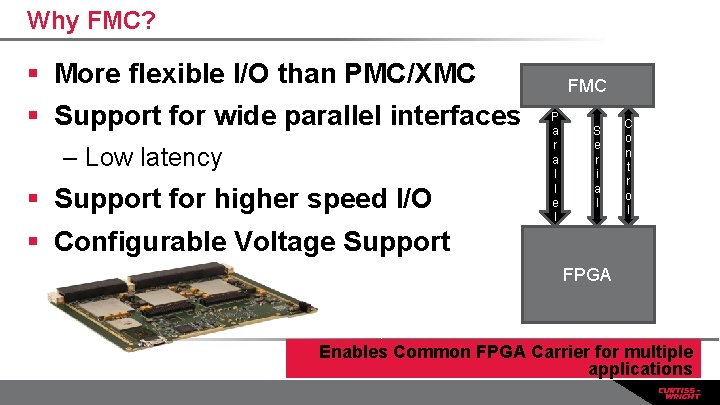

Why FMC? § More flexible I/O than PMC/XMC § Support for wide parallel interfaces – Low latency § Support for higher speed I/O § Configurable Voltage Support FMC P a r a l l e l S e r i a l C o n t r o l FPGA Enables Common FPGA Carrier for multiple applications

![FMC Signals 80 Differential Pairs 160 single ended LPC 00 33 HPC FMC Signals § 80 Differential Pairs (160 single ended) – LPC [00: 33]; HPC](https://slidetodoc.com/presentation_image_h/9dcdad7400931a248dc38a886c26d9a8/image-4.jpg)

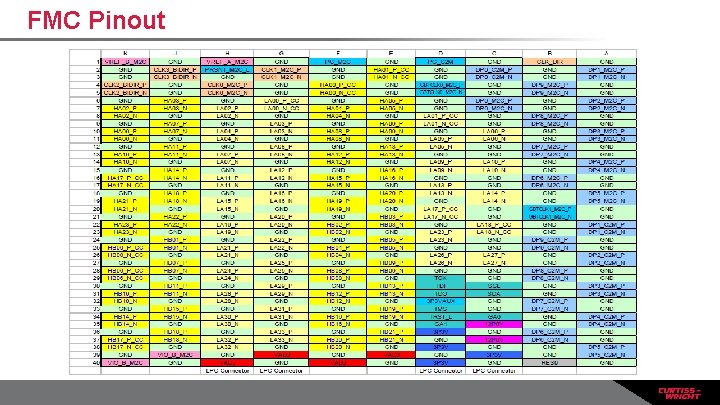

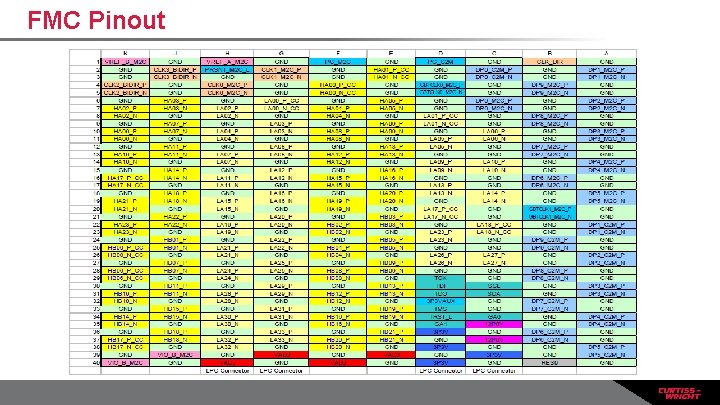

FMC Signals § 80 Differential Pairs (160 single ended) – LPC [00: 33]; HPC (HA[00: 23]; HB[00: 21]) § 4 differential clocks, 2 optionally sourced by carrier § 10 High Speed SERDES, with two SERDES clocks § I 2 C Control Interface § Misc: GA, JTAG, Present, Power Good, Power/GND

FMC Pinout

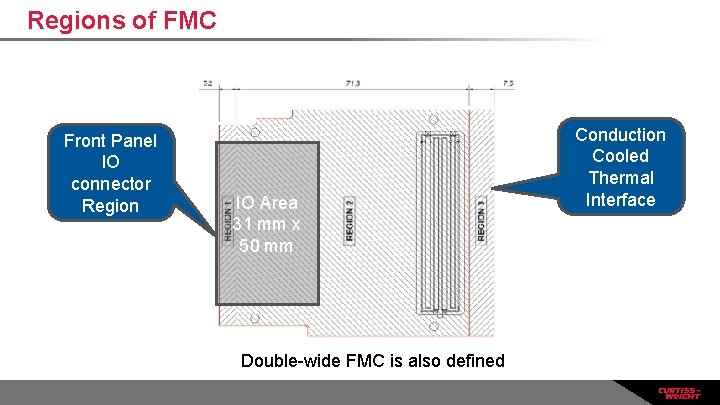

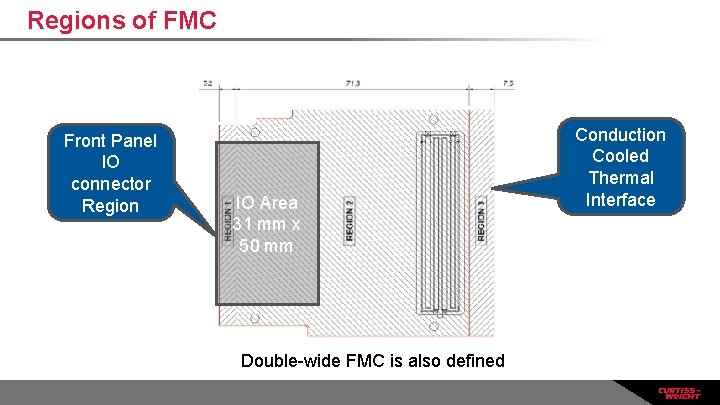

Regions of FMC Front Panel IO connector Region IO Area 31 mm x 50 mm Double-wide FMC is also defined Conduction Cooled Thermal Interface

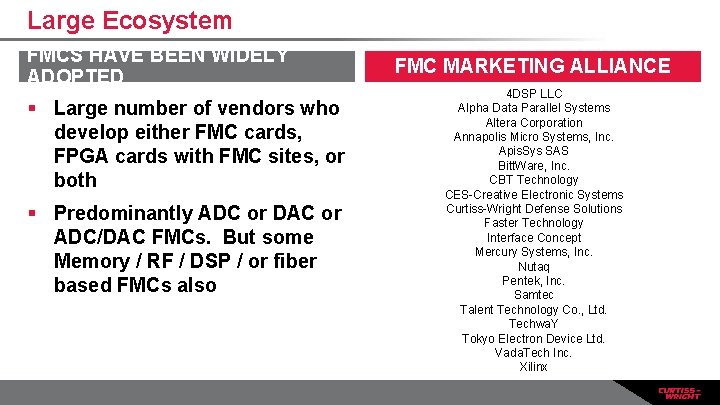

Large Ecosystem FMCS HAVE BEEN WIDELY ADOPTED § Large number of vendors who develop either FMC cards, FPGA cards with FMC sites, or both § Predominantly ADC or DAC or ADC/DAC FMCs. But some Memory / RF / DSP / or fiber based FMCs also FMC MARKETING ALLIANCE 4 DSP LLC Alpha Data Parallel Systems Altera Corporation Annapolis Micro Systems, Inc. Apis. Sys SAS Bitt. Ware, Inc. CBT Technology CES-Creative Electronic Systems Curtiss-Wright Defense Solutions Faster Technology Interface Concept Mercury Systems, Inc. Nutaq Pentek, Inc. Samtec Talent Technology Co. , Ltd. Techwa. Y Tokyo Electron Device Ltd. Vada. Tech Inc. Xilinx

History of VITA 57 § Initial work started in 2005 § ANSI Ratification in 2008 § Updated in 2010 – Minor revisions related to SERDES signals and clocks and some clarifications § New dot specifications underway – VITA 57. 2 – meta-data standard for PROM data (XML) – VITA 57. 3 – logic interfaces for firmware that resides in FPGA – VITA 57. 4 – adding more SERDES support for FMC

VITA 57. 4 Why? § New ADC and DAC devices are going serial (JESD 204 B) § FPGA SERDES continue to increase in quantity and speed § Memories are also going serial (HMC) § Current VITA 47. 1 FMC specification limited to 10 SERDES § ADC/DAC bandwidth can exceed Focus of V 57. 4 FMC is to add SERDES bandwidth

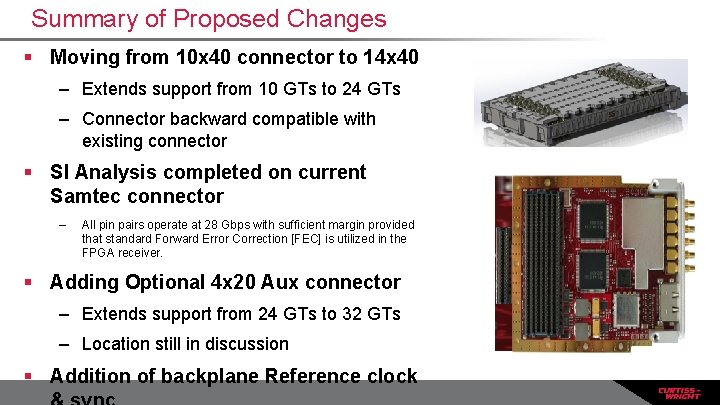

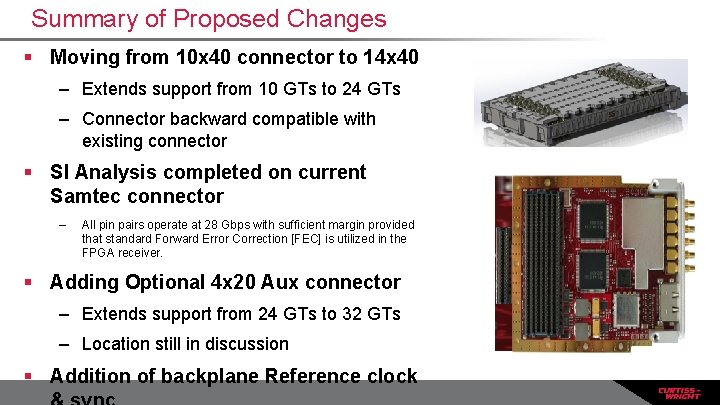

Summary of Proposed Changes § Moving from 10 x 40 connector to 14 x 40 – Extends support from 10 GTs to 24 GTs – Connector backward compatible with existing connector § SI Analysis completed on current Samtec connector – All pin pairs operate at 28 Gbps with sufficient margin provided that standard Forward Error Correction [FEC] is utilized in the FPGA receiver. § Adding Optional 4 x 20 Aux connector – Extends support from 24 GTs to 32 GTs – Location still in discussion § Addition of backplane Reference clock

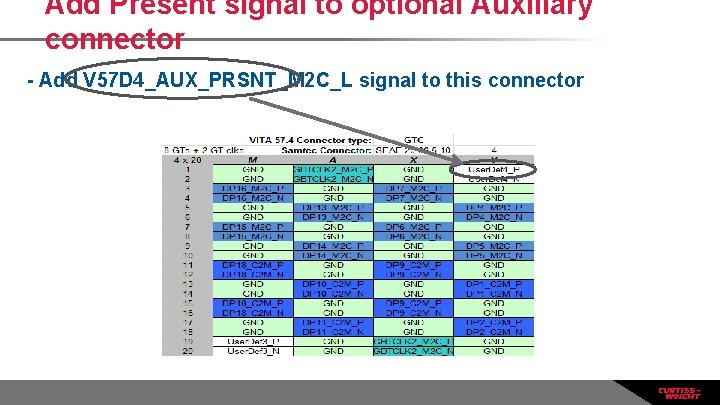

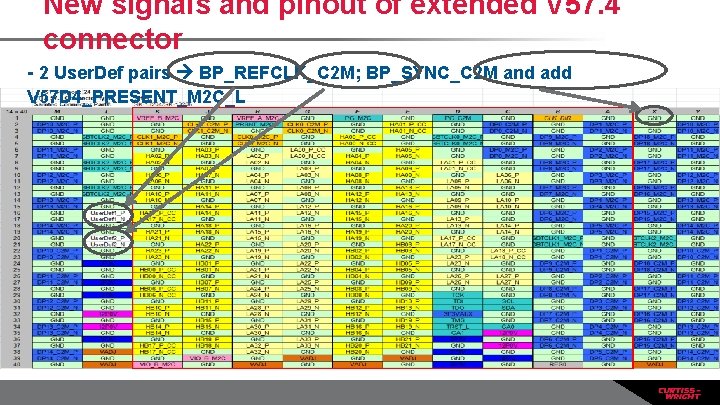

New signals and pinout of extended V 57. 4 connector - 2 User. Def pairs BP_REFCLK_C 2 M; BP_SYNC_C 2 M and add V 57 D 4_PRESENT_M 2 C_L

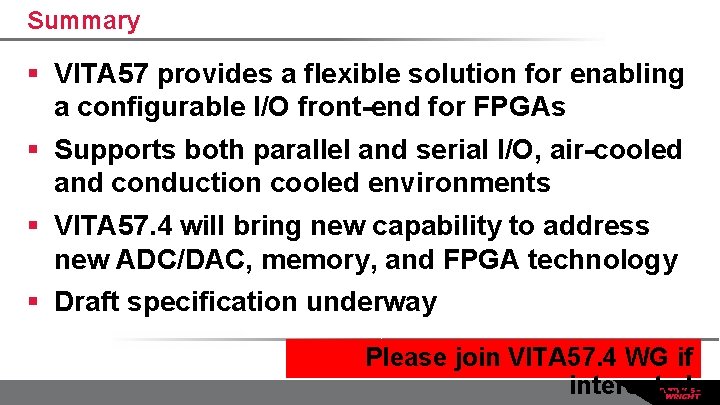

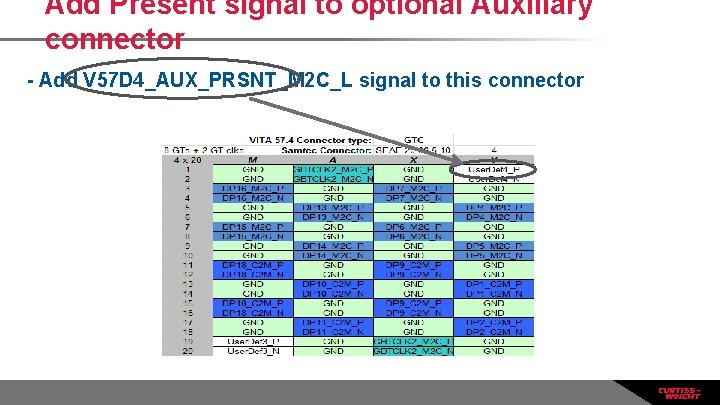

Add Present signal to optional Auxiliary connector - Add V 57 D 4_AUX_PRSNT_M 2 C_L signal to this connector

Summary § VITA 57 provides a flexible solution for enabling a configurable I/O front-end for FPGAs § Supports both parallel and serial I/O, air-cooled and conduction cooled environments § VITA 57. 4 will bring new capability to address new ADC/DAC, memory, and FPGA technology § Draft specification underway Please join VITA 57. 4 WG if interested