Overview of the readout electronics for the TPCs

- Slides: 17

Overview of the read-out electronics for the TPCs at T 2 K ND 280 m P. Baron, D. Calvet, X. De La Broïse, E. Delagnes, F. Druillole, J-L Fallou, J-M. Reymond, E. Virique, E. Zonca DSM/DAPNIA/SEDI, CEA Saclay 91191 Gif-sur-Yvette Cedex, France

Plan • Context • TPC Read-out Architecture • Summary calvet@hep. saclay. cea. fr 2 Paris 12 September 2006

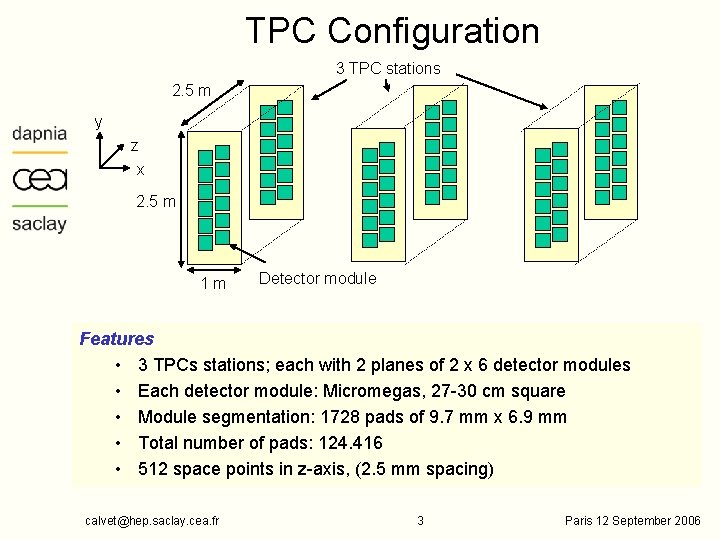

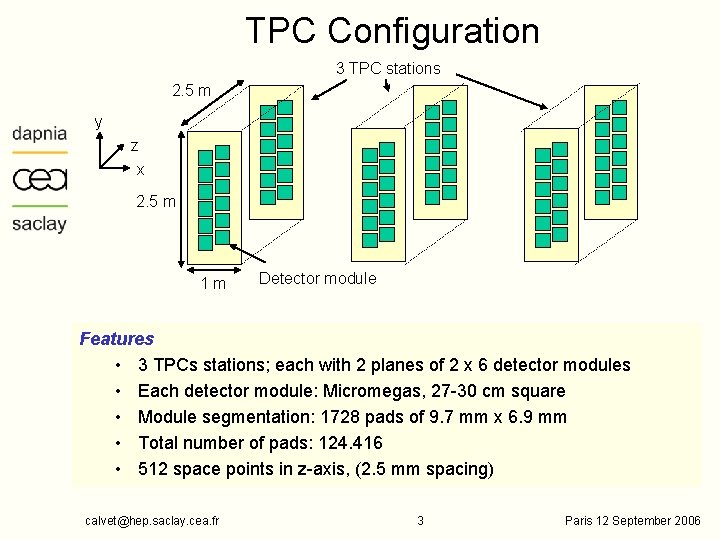

TPC Configuration 3 TPC stations 2. 5 m y z x 2. 5 m 1 m Detector module Features • 3 TPCs stations; each with 2 planes of 2 x 6 detector modules • Each detector module: Micromegas, 27 -30 cm square • Module segmentation: 1728 pads of 9. 7 mm x 6. 9 mm • Total number of pads: 124. 416 • 512 space points in z-axis, (2. 5 mm spacing) calvet@hep. saclay. cea. fr 3 Paris 12 September 2006

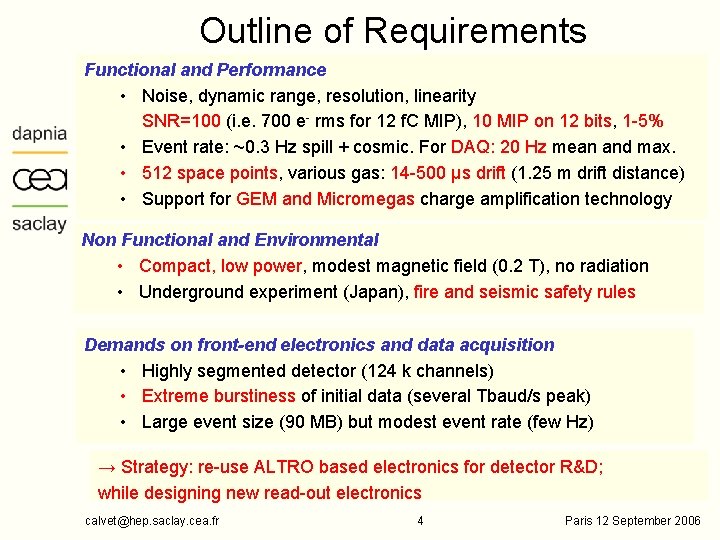

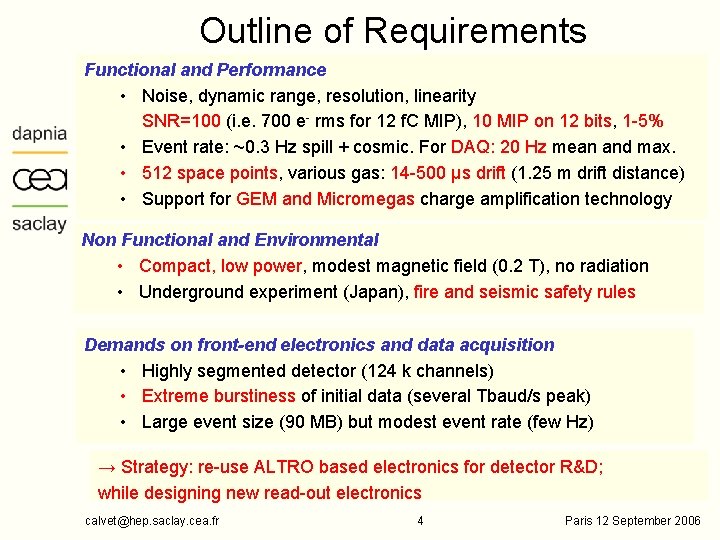

Outline of Requirements Functional and Performance • Noise, dynamic range, resolution, linearity SNR=100 (i. e. 700 e- rms for 12 f. C MIP), 10 MIP on 12 bits, 1 -5% • Event rate: ~0. 3 Hz spill + cosmic. For DAQ: 20 Hz mean and max. • 512 space points, various gas: 14 -500 µs drift (1. 25 m drift distance) • Support for GEM and Micromegas charge amplification technology Non Functional and Environmental • Compact, low power, modest magnetic field (0. 2 T), no radiation • Underground experiment (Japan), fire and seismic safety rules Demands on front-end electronics and data acquisition • Highly segmented detector (124 k channels) • Extreme burstiness of initial data (several Tbaud/s peak) • Large event size (90 MB) but modest event rate (few Hz) → Strategy: re-use ALTRO based electronics for detector R&D; while designing new read-out electronics calvet@hep. saclay. cea. fr 4 Paris 12 September 2006

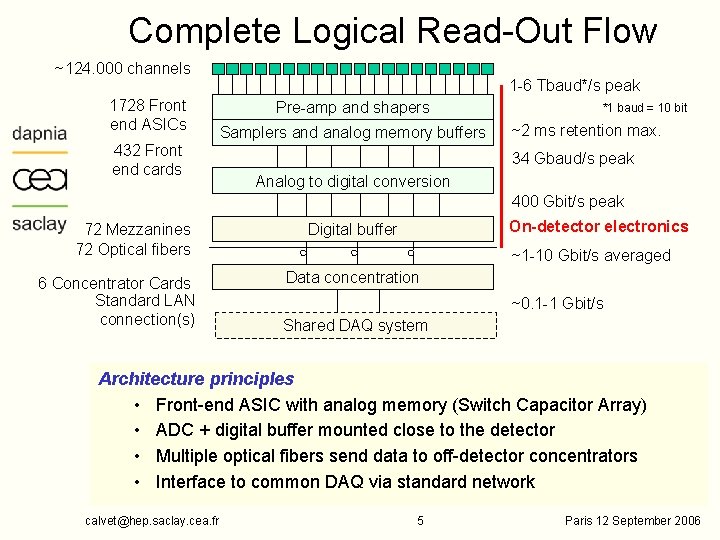

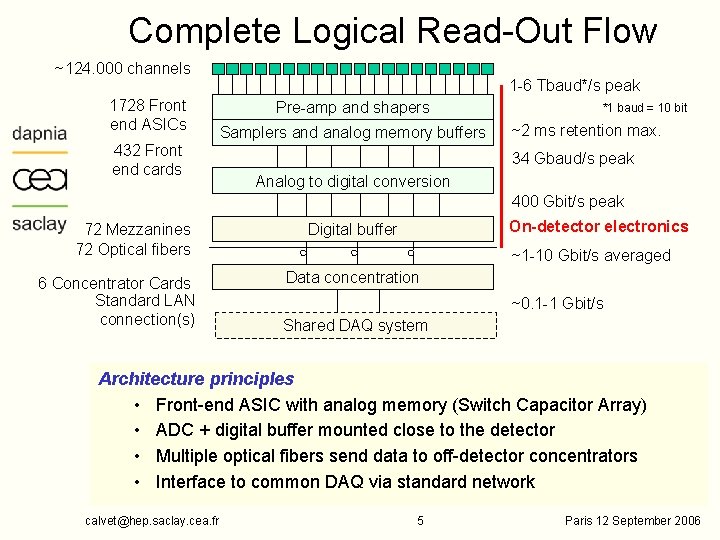

Complete Logical Read-Out Flow ~124. 000 channels 1728 Front end ASICs 432 Front end cards 1 -6 Tbaud*/s peak Pre-amp and shapers Samplers and analog memory buffers *1 baud = 10 bit ~2 ms retention max. 34 Gbaud/s peak Analog to digital conversion 400 Gbit/s peak 72 Mezzanines 72 Optical fibers 6 Concentrator Cards Standard LAN connection(s) On-detector electronics Digital buffer ~1 -10 Gbit/s averaged Data concentration ~0. 1 -1 Gbit/s Shared DAQ system Architecture principles • Front-end ASIC with analog memory (Switch Capacitor Array) • ADC + digital buffer mounted close to the detector • Multiple optical fibers send data to off-detector concentrators • Interface to common DAQ via standard network calvet@hep. saclay. cea. fr 5 Paris 12 September 2006

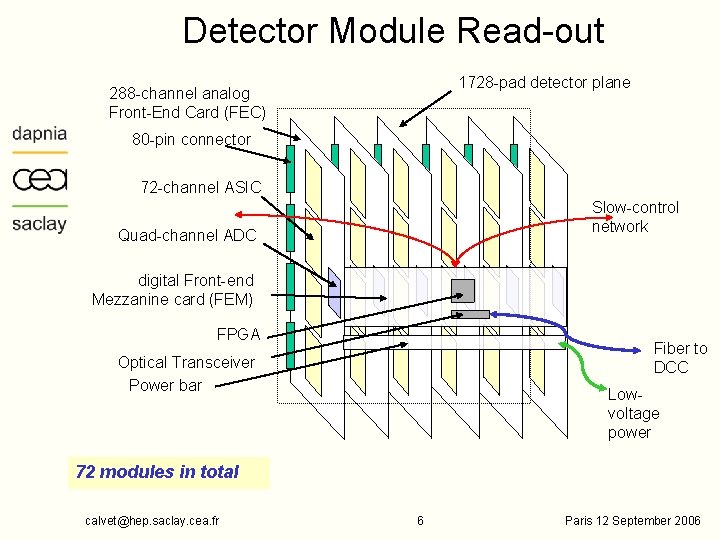

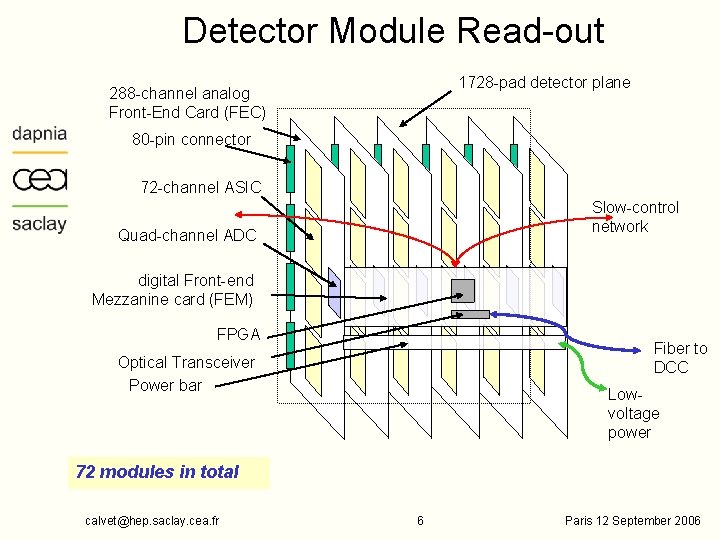

Detector Module Read-out 1728 -pad detector plane 288 -channel analog Front-End Card (FEC) 80 -pin connector 72 -channel ASIC Slow-control network Quad-channel ADC digital Front-end Mezzanine card (FEM) FPGA Fiber to DCC Optical Transceiver Power bar Lowvoltage power 72 modules in total calvet@hep. saclay. cea. fr 6 Paris 12 September 2006

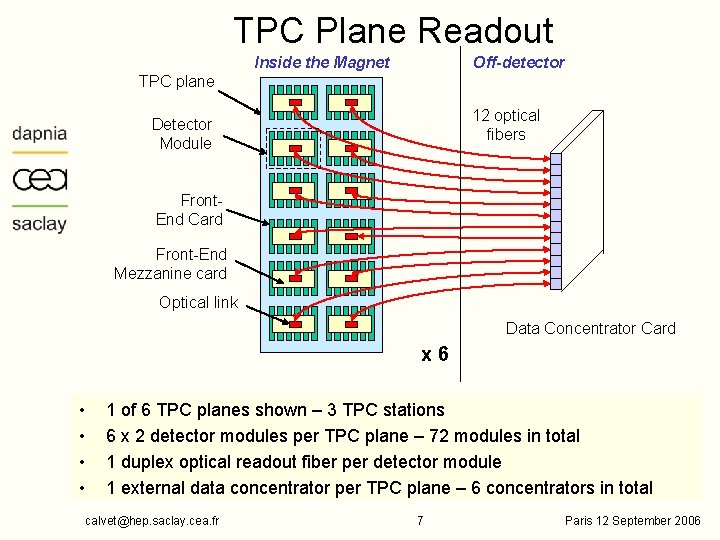

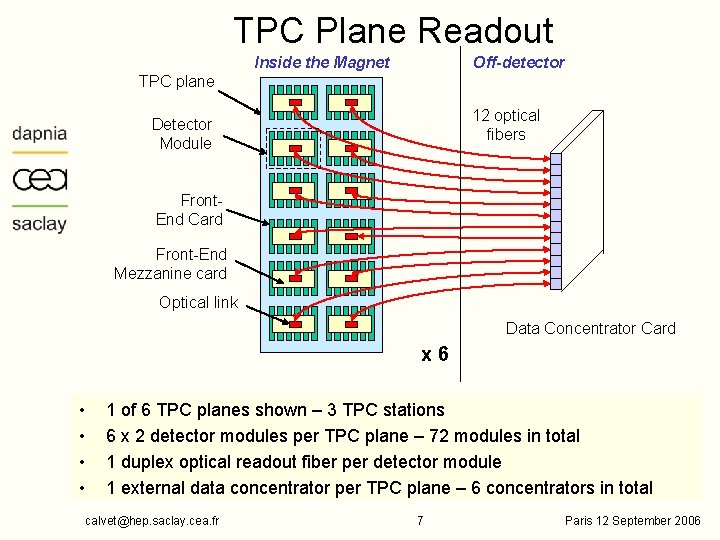

TPC Plane Readout Inside the Magnet Off-detector TPC plane 12 optical fibers Detector Module Front. End Card Front-End Mezzanine card Optical link Data Concentrator Card x 6 • • 1 of 6 TPC planes shown – 3 TPC stations 6 x 2 detector modules per TPC plane – 72 modules in total 1 duplex optical readout fiber per detector module 1 external data concentrator per TPC plane – 6 concentrators in total calvet@hep. saclay. cea. fr 7 Paris 12 September 2006

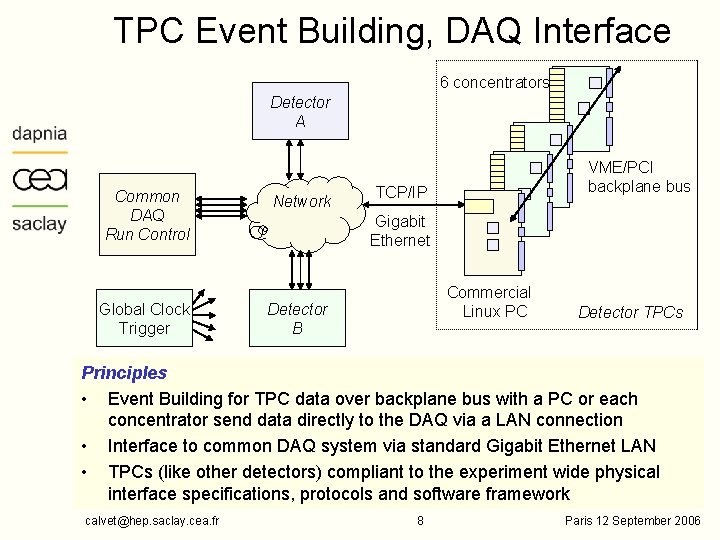

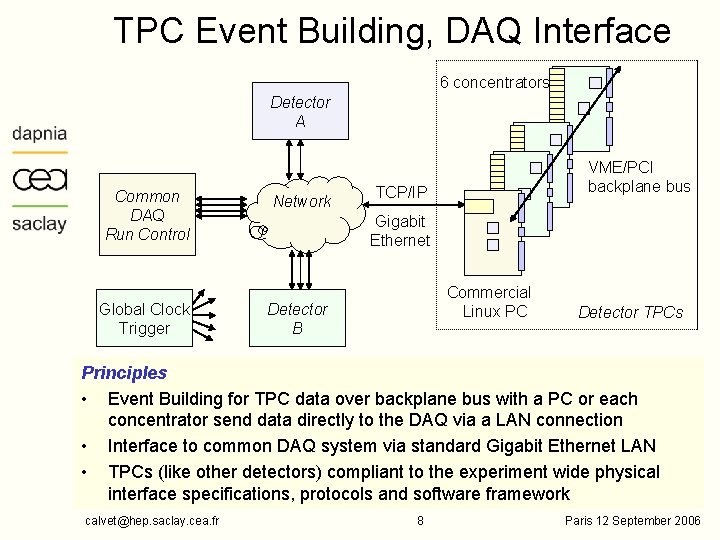

TPC Event Building, DAQ Interface 6 concentrators Detector A Common DAQ Run Control Global Clock Trigger Network VME/PCI backplane bus TCP/IP Gigabit Ethernet Commercial Linux PC Detector B Detector TPCs Principles • Event Building for TPC data over backplane bus with a PC or each concentrator send data directly to the DAQ via a LAN connection • Interface to common DAQ system via standard Gigabit Ethernet LAN • TPCs (like other detectors) compliant to the experiment wide physical interface specifications, protocols and software framework calvet@hep. saclay. cea. fr 8 Paris 12 September 2006

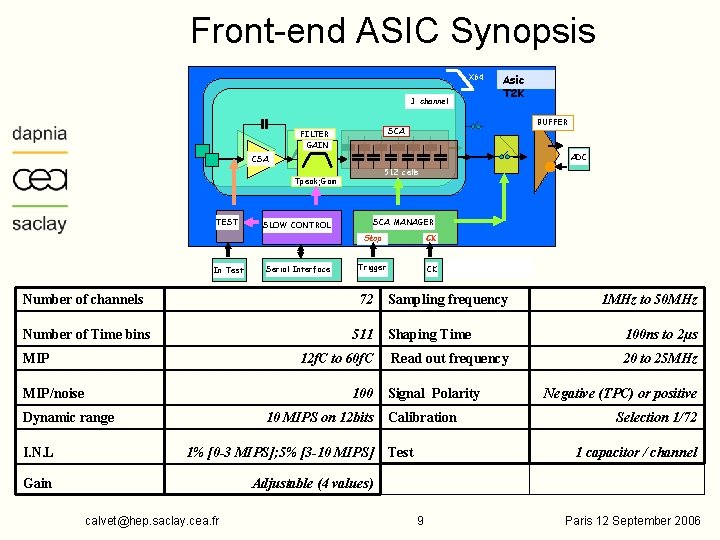

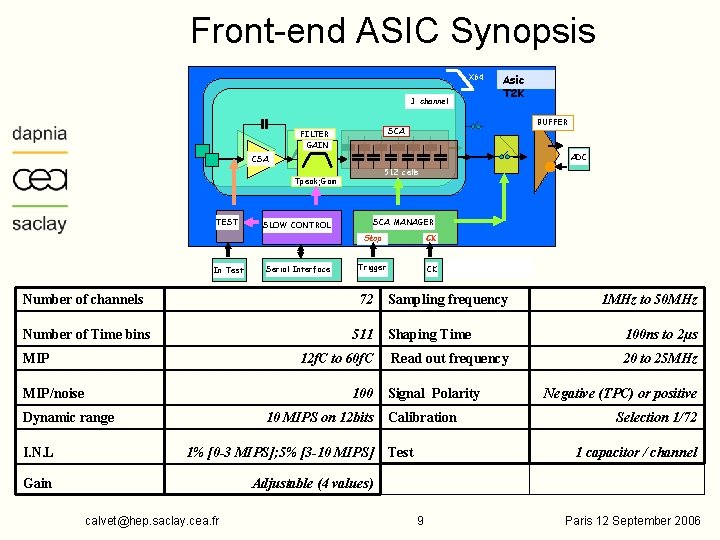

Front-end ASIC Synopsis X 64 1 channel Asic T 2 K BUFFER SCA FILTER GAIN ADC CSA 512 cells Tpeak; Gain TEST In Test SLOW CONTROL Serial Interface SCA MANAGER Stop CK Trigger CK Number of channels 72 Number of Time bins 511 MIP 12 f. C to 60 f. C MIP/noise 100 Dynamic range 10 MIPS on 12 bits I. N. L 1% [0 -3 MIPS]; 5% [3 -10 MIPS] Gain Adjustable (4 values) calvet@hep. saclay. cea. fr Sampling frequency Shaping Time Read out frequency Signal Polarity Calibration Test 1 MHz to 50 MHz 100 ns to 2µs 20 to 25 MHz Negative (TPC) or positive Selection 1/72 1 capacitor / channel 9 Paris 12 September 2006

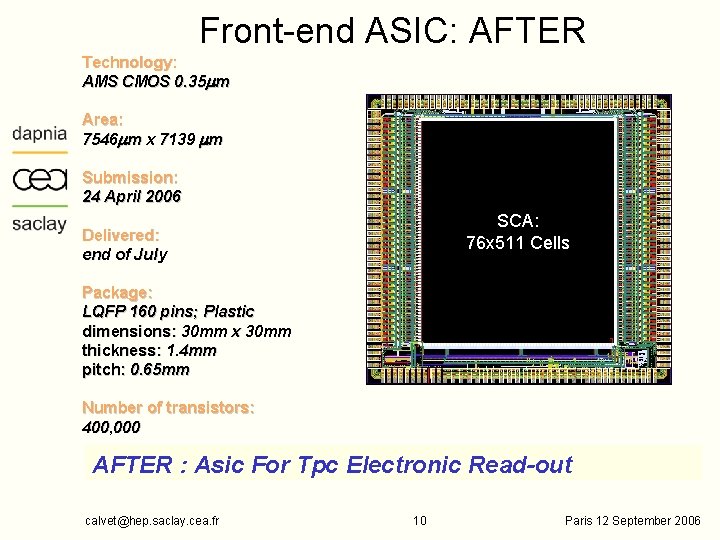

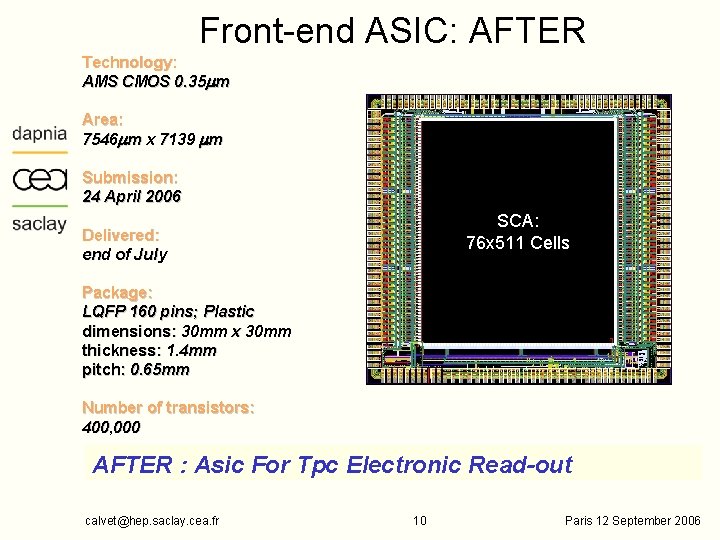

Front-end ASIC: AFTER Technology: AMS CMOS 0. 35 mm Area: 7546 mm x 7139 mm Submission: 24 April 2006 SCA: 76 x 511 Cells Delivered: end of July Package: LQFP 160 pins; Plastic dimensions: 30 mm x 30 mm thickness: 1. 4 mm pitch: 0. 65 mm Number of transistors: 400, 000 AFTER : Asic For Tpc Electronic Read-out calvet@hep. saclay. cea. fr 10 Paris 12 September 2006

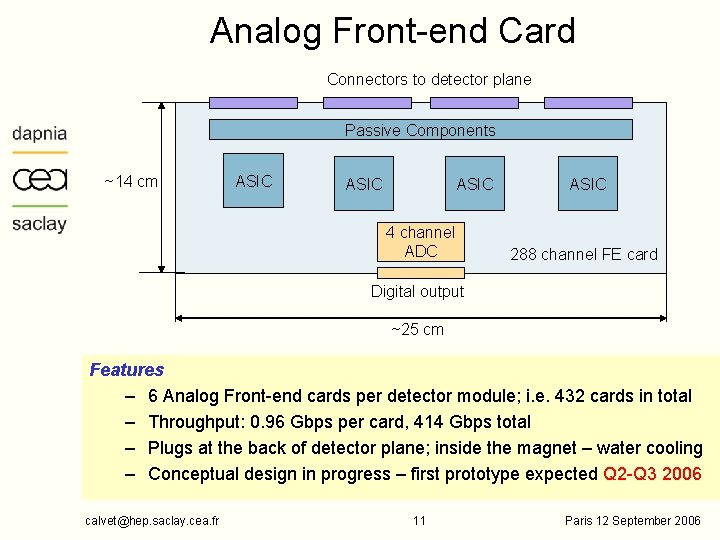

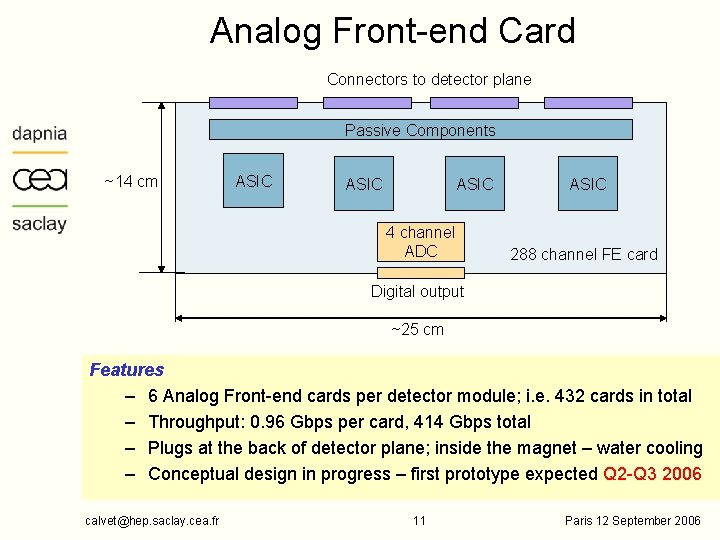

Analog Front-end Card Connectors to detector plane Passive Components ~14 cm ASIC 4 channel ADC ASIC 288 channel FE card Digital output ~25 cm Features – 6 Analog Front-end cards per detector module; i. e. 432 cards in total – Throughput: 0. 96 Gbps per card, 414 Gbps total – Plugs at the back of detector plane; inside the magnet – water cooling – Conceptual design in progress – first prototype expected Q 2 -Q 3 2006 calvet@hep. saclay. cea. fr 11 Paris 12 September 2006

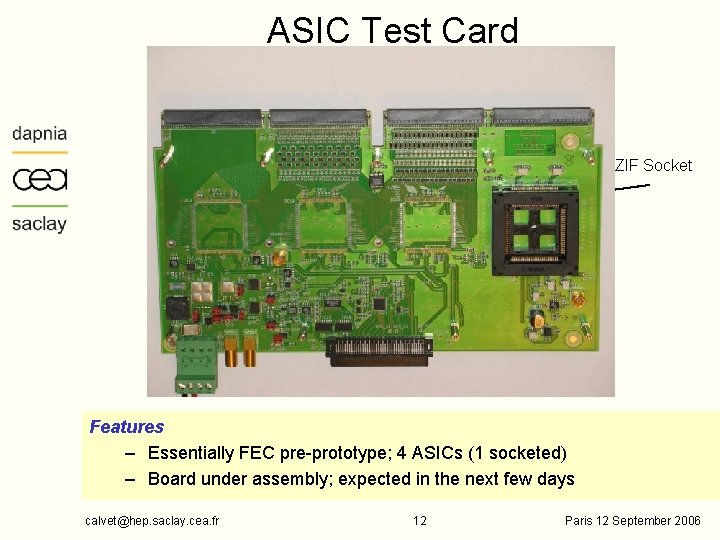

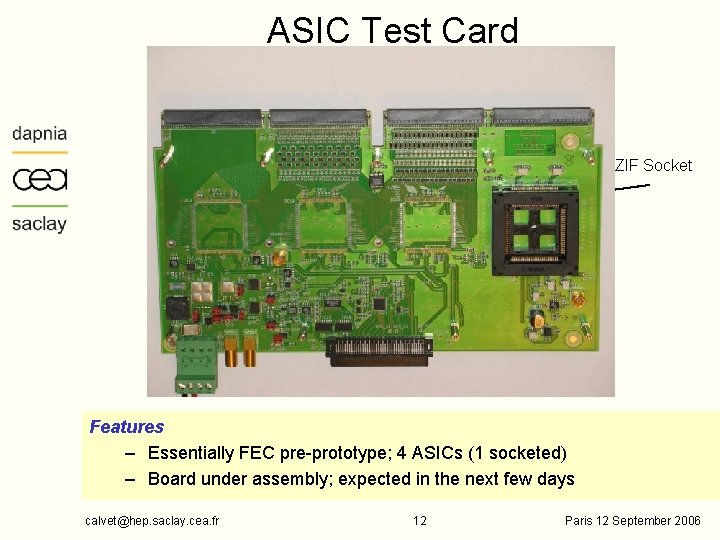

ASIC Test Card ZIF Socket Interface connector to FEM Features – Essentially FEC pre-prototype; 4 ASICs (1 socketed) – Board under assembly; expected in the next few days calvet@hep. saclay. cea. fr 12 Paris 12 September 2006

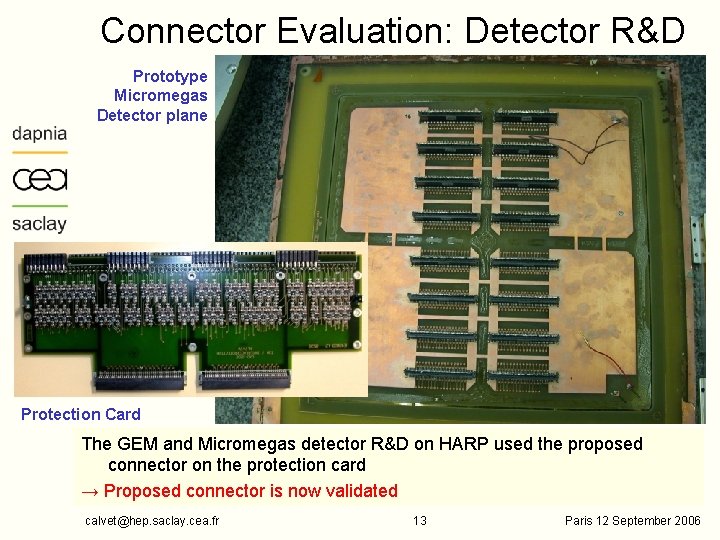

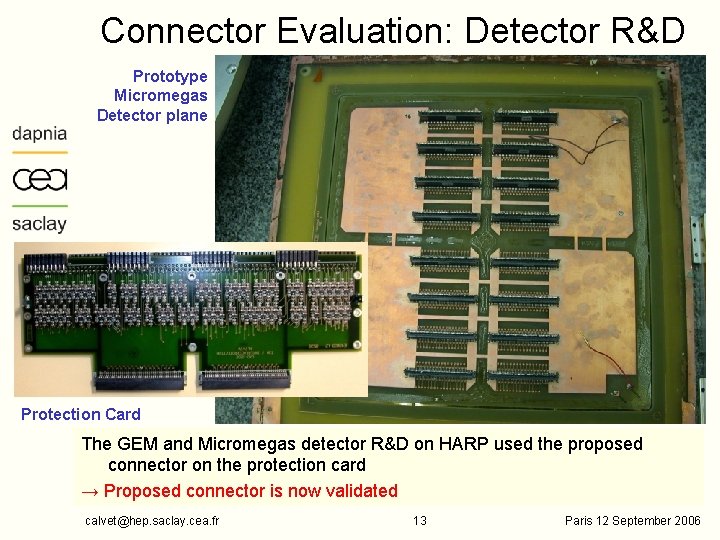

Connector Evaluation: Detector R&D Prototype Micromegas Detector plane Protection Card The GEM and Micromegas detector R&D on HARP used the proposed connector on the protection card → Proposed connector is now validated calvet@hep. saclay. cea. fr 13 Paris 12 September 2006

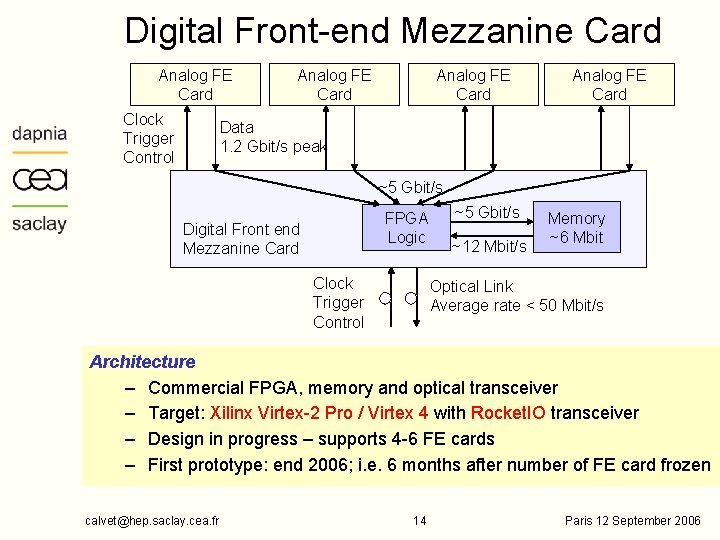

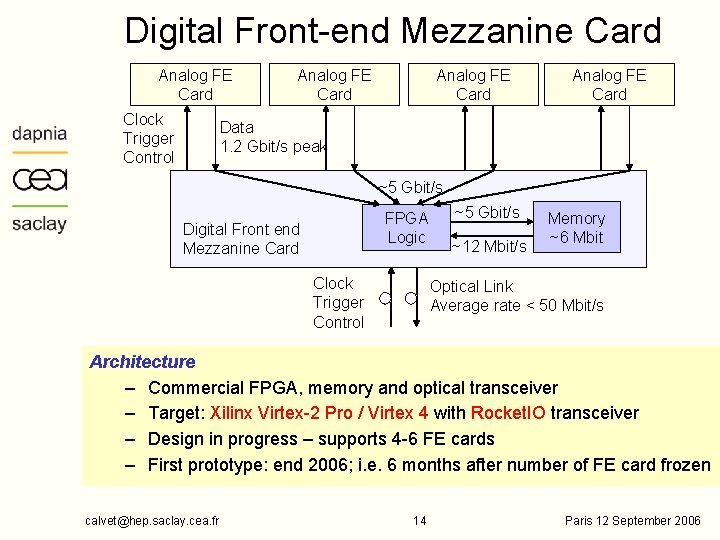

Digital Front-end Mezzanine Card Analog FE Card Clock Trigger Control Analog FE Card Data 1. 2 Gbit/s peak ~5 Gbit/s FPGA Logic Digital Front end Mezzanine Card Clock Trigger Control ~5 Gbit/s ~12 Mbit/s Memory ~6 Mbit Optical Link Average rate < 50 Mbit/s Architecture – Commercial FPGA, memory and optical transceiver – Target: Xilinx Virtex-2 Pro / Virtex 4 with Rocket. IO transceiver – Design in progress – supports 4 -6 FE cards – First prototype: end 2006; i. e. 6 months after number of FE card frozen calvet@hep. saclay. cea. fr 14 Paris 12 September 2006

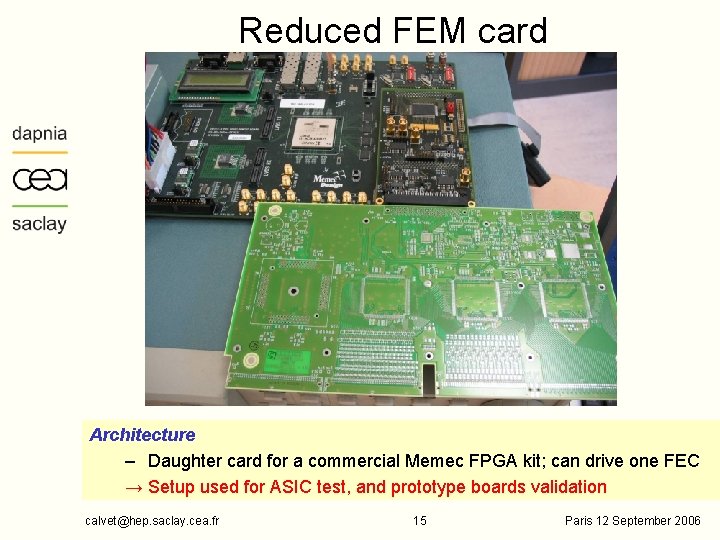

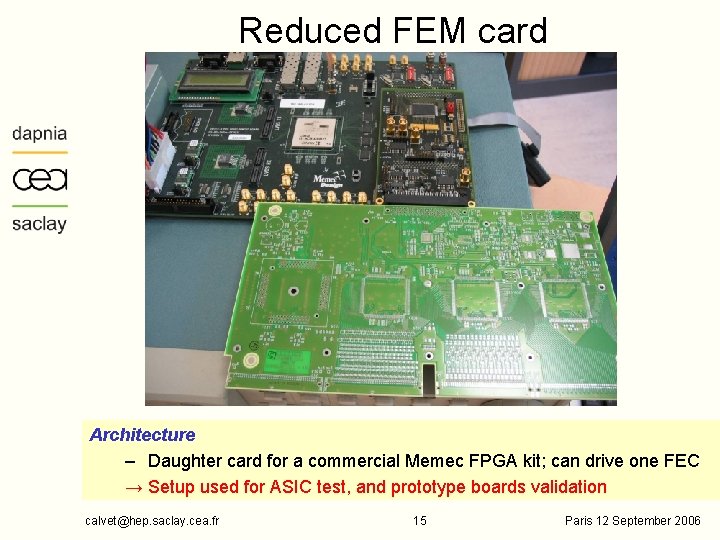

Reduced FEM card Architecture – Daughter card for a commercial Memec FPGA kit; can drive one FEC → Setup used for ASIC test, and prototype boards validation calvet@hep. saclay. cea. fr 15 Paris 12 September 2006

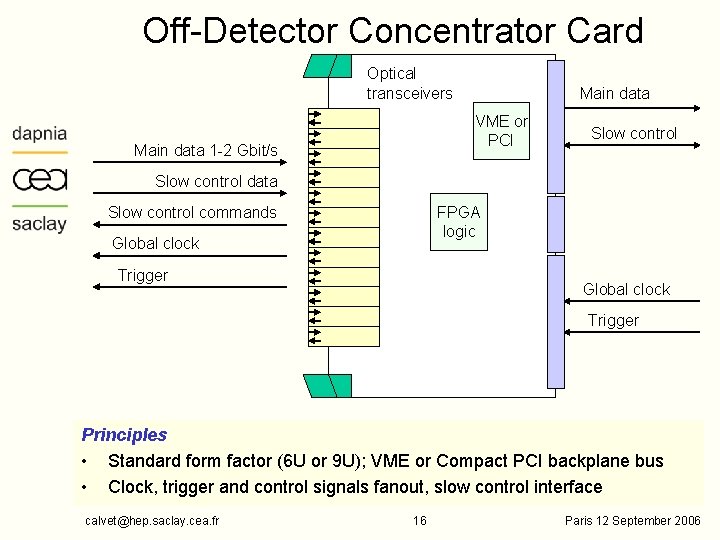

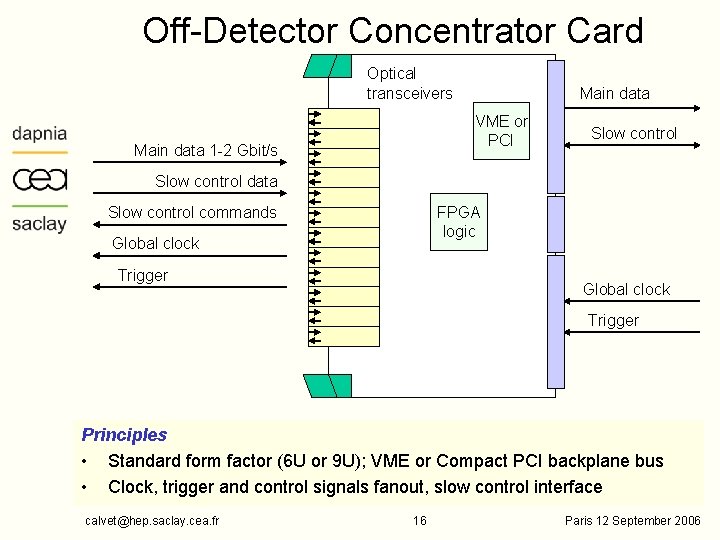

Off-Detector Concentrator Card Optical transceivers Main data VME or PCI Main data 1 -2 Gbit/s Slow control data FPGA logic Slow control commands Global clock Trigger Principles • Standard form factor (6 U or 9 U); VME or Compact PCI backplane bus • Clock, trigger and control signals fanout, slow control interface calvet@hep. saclay. cea. fr 16 Paris 12 September 2006

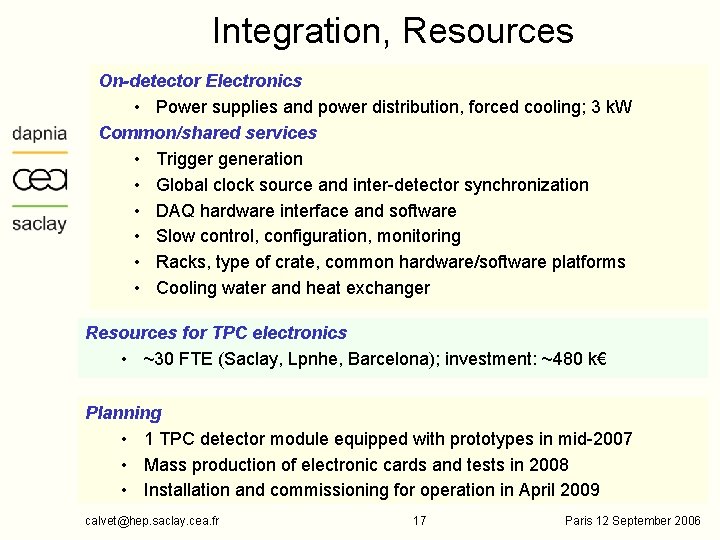

Integration, Resources On-detector Electronics • Power supplies and power distribution, forced cooling; 3 k. W Common/shared services • Trigger generation • Global clock source and inter-detector synchronization • DAQ hardware interface and software • Slow control, configuration, monitoring • Racks, type of crate, common hardware/software platforms • Cooling water and heat exchanger Resources for TPC electronics • ~30 FTE (Saclay, Lpnhe, Barcelona); investment: ~480 k€ Planning • 1 TPC detector module equipped with prototypes in mid-2007 • Mass production of electronic cards and tests in 2008 • Installation and commissioning for operation in April 2009 calvet@hep. saclay. cea. fr 17 Paris 12 September 2006