Overview of the CSC Phase I Upgrade plans

- Slides: 20

Overview of the CSC Phase I Upgrade plans • ME 4/2 upgrade: 72 new large chambers • for high-luminosity triggering in h 1. 1 -1. 8 • Flash ADC board for cathode digitization • ME 1/1 to handle high rates • ME 1/1 to restore trigger and improve reconstruction for h 2. 1 -2. 4 • Upgrade ME 1/1 associated TMB and DMB boards • Schedule and “to-do” list RPC Upscope Meeting Jay Hauser 05 Feb 2010 1/11

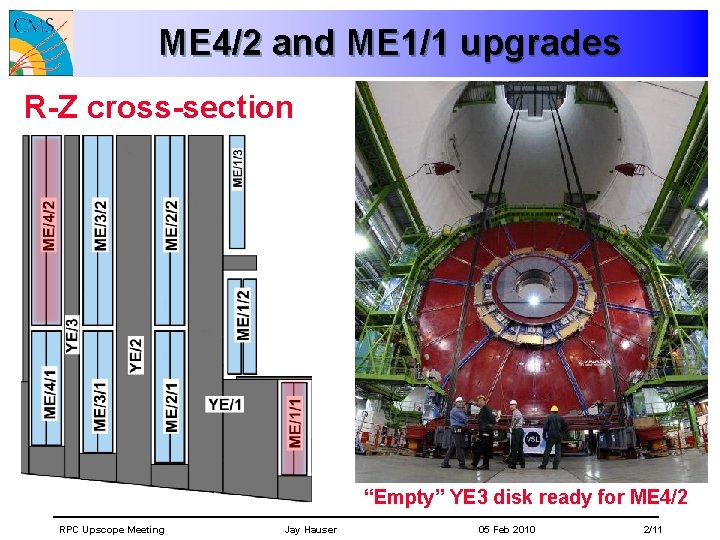

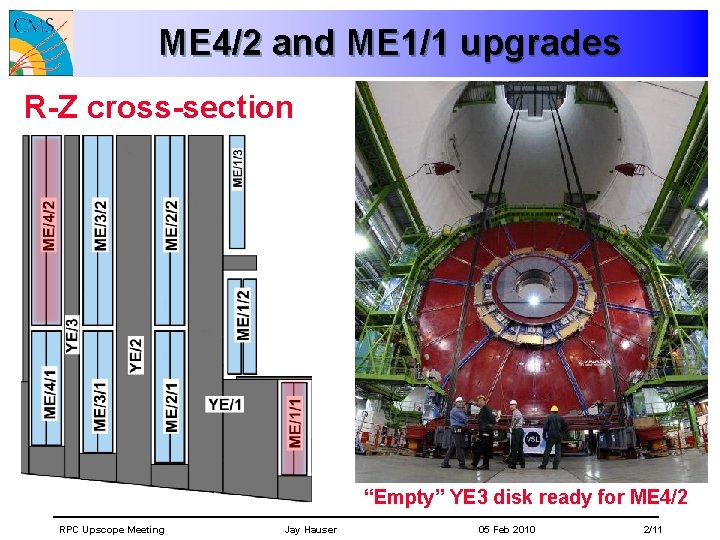

ME 4/2 and ME 1/1 upgrades R-Z cross-section “Empty” YE 3 disk ready for ME 4/2 RPC Upscope Meeting Jay Hauser 05 Feb 2010 2/11

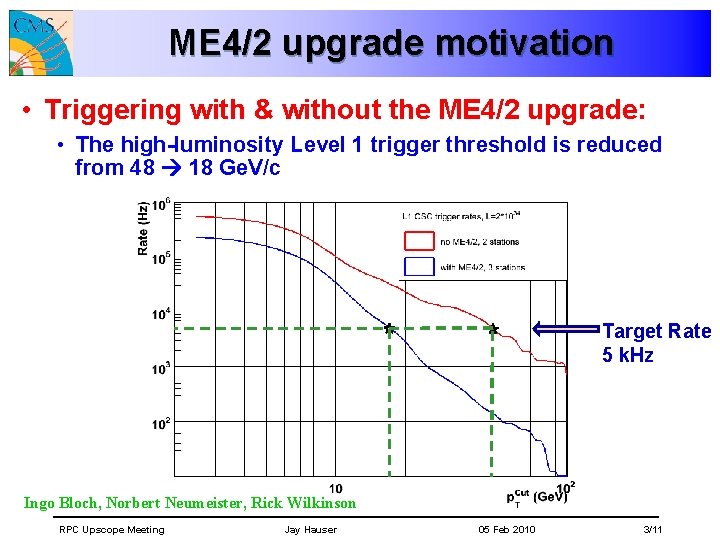

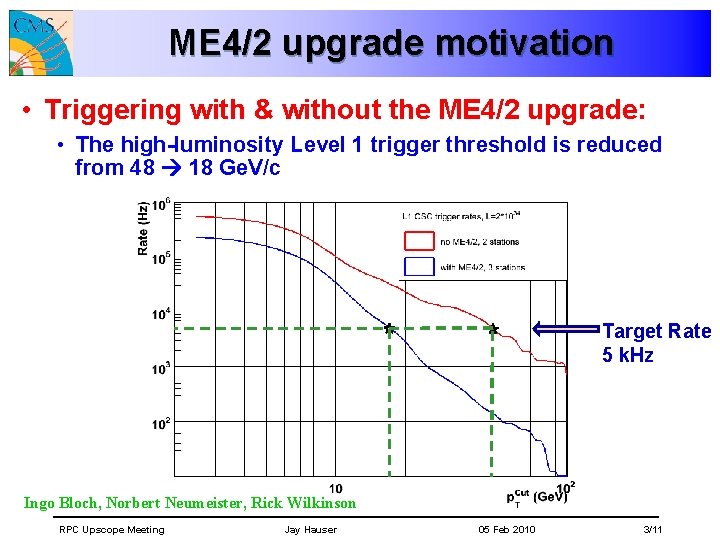

ME 4/2 upgrade motivation • Triggering with & without the ME 4/2 upgrade: • The high-luminosity Level 1 trigger threshold is reduced from 48 18 Ge. V/c Target Rate 5 k. Hz Ingo Bloch, Norbert Neumeister, Rick Wilkinson RPC Upscope Meeting Jay Hauser 05 Feb 2010 3/11

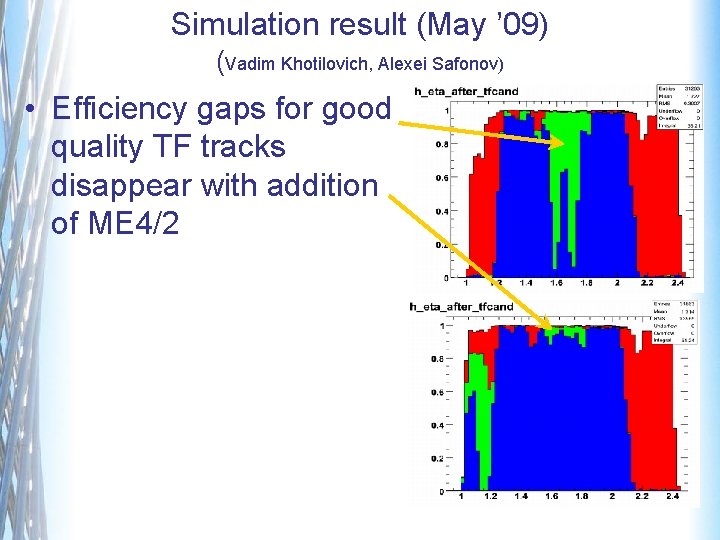

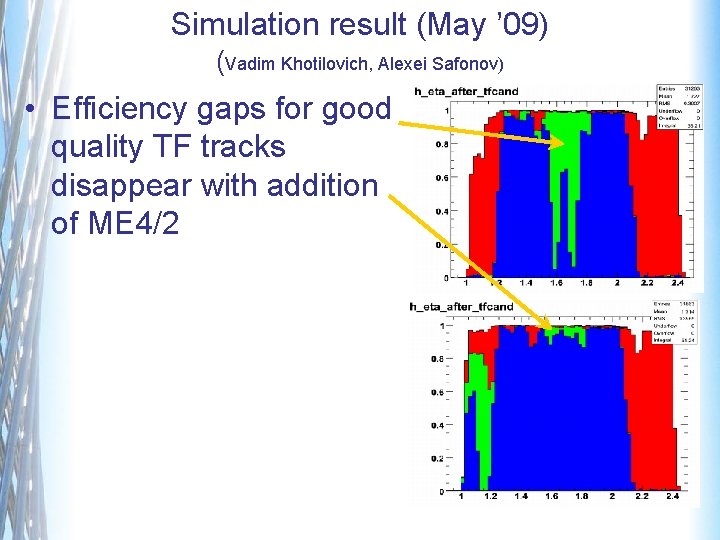

Simulation result (May ’ 09) (Vadim Khotilovich, Alexei Safonov) • Efficiency gaps for good quality TF tracks disappear with addition of ME 4/2

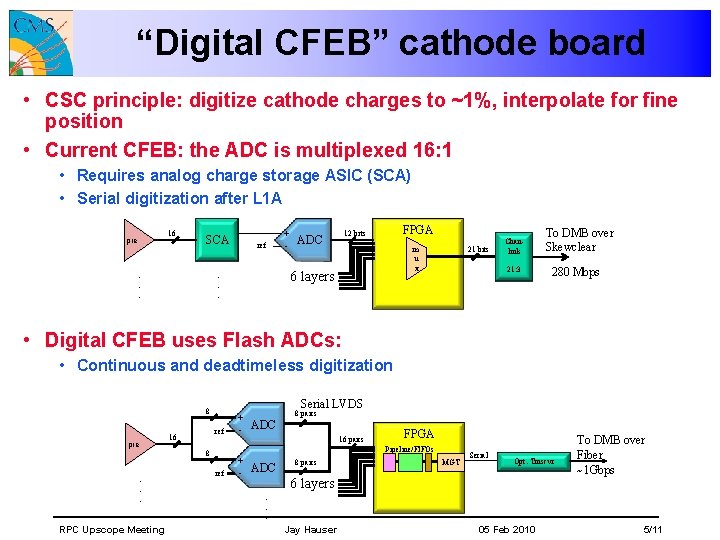

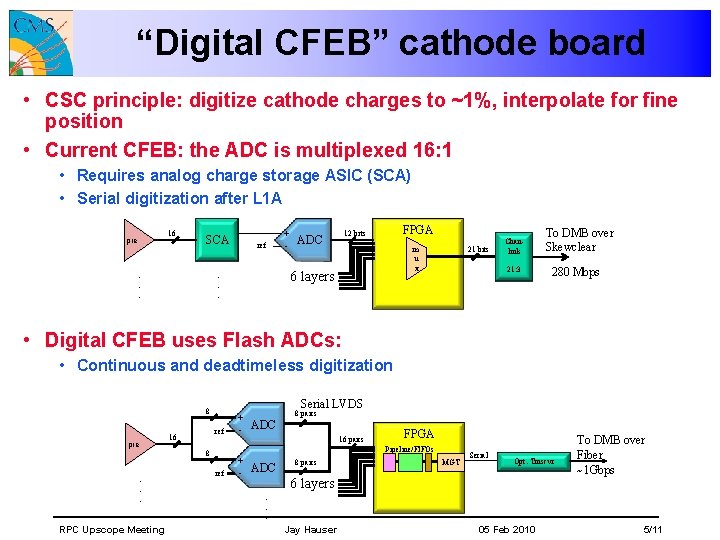

“Digital CFEB” cathode board • CSC principle: digitize cathode charges to ~1%, interpolate for fine position • Current CFEB: the ADC is multiplexed 16: 1 • Requires analog charge storage ASIC (SCA) • Serial digitization after L 1 A 16 pre SCA . . . ref + - FPGA 12 bits ADC m u x 6 layers . . . 21 bits Chanlink 21: 3 To DMB over Skewclear 280 Mbps • Digital CFEB uses Flash ADCs: • Continuous and deadtimeless digitization Serial LVDS 8 pre ref 16 RPC Upscope Meeting ADC 8 pairs 16 pairs FPGA Pipeline/FIFOs 8. . . + - ref + - ADC 8 pairs MGT Serial Opt. Trnscvr 6 layers To DMB over Fiber ~1 Gbps . . . Jay Hauser 05 Feb 2010 5/11

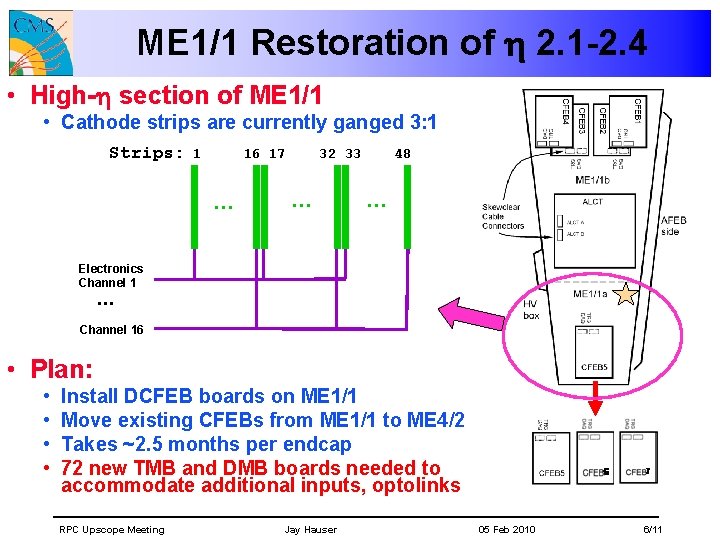

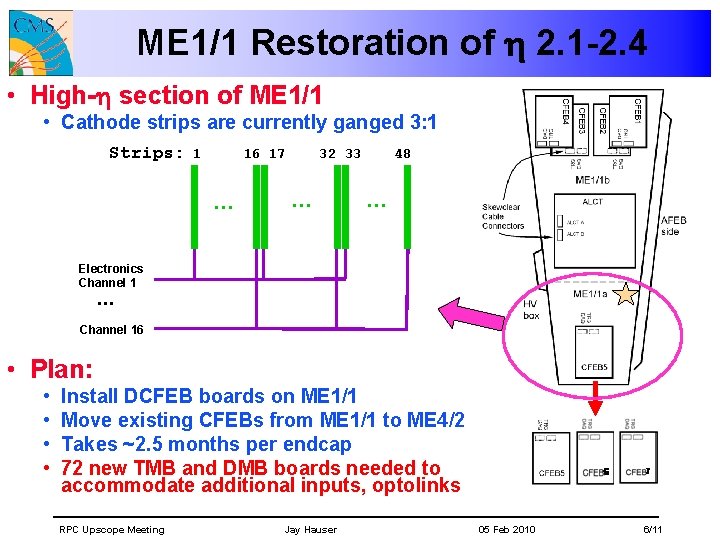

ME 1/1 Restoration of h 2. 1 -2. 4 • High-h section of ME 1/1 • Cathode strips are currently ganged 3: 1 Strips: 1 16 17 … 32 33 … 48 … Electronics Channel 1 … Channel 16 • Plan: • • Install DCFEB boards on ME 1/1 Move existing CFEBs from ME 1/1 to ME 4/2 Takes ~2. 5 months per endcap 72 new TMB and DMB boards needed to accommodate additional inputs, optolinks RPC Upscope Meeting Jay Hauser 05 Feb 2010 6/11

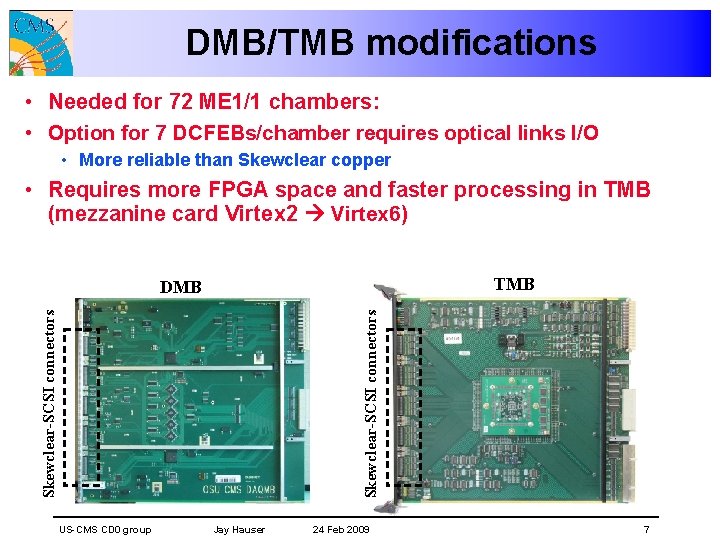

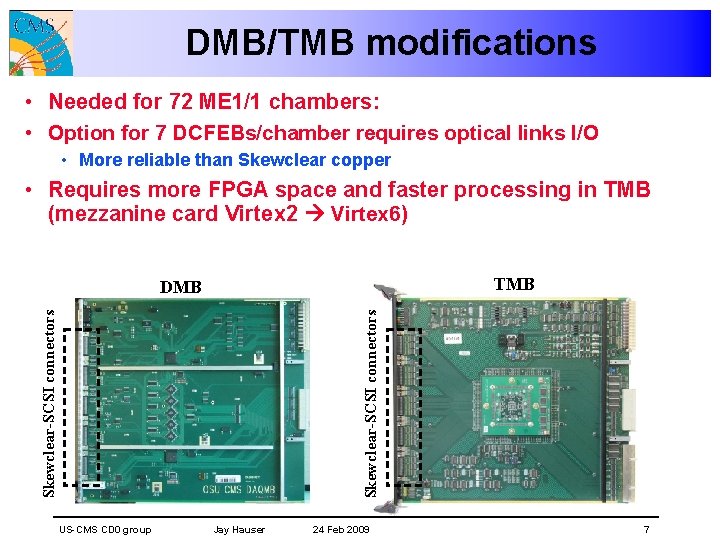

DMB/TMB modifications • Needed for 72 ME 1/1 chambers: • Option for 7 DCFEBs/chamber requires optical links I/O • More reliable than Skewclear copper • Requires more FPGA space and faster processing in TMB (mezzanine card Virtex 2 Virtex 6) TMB Skewclear-SCSI connectors DMB US-CMS CD 0 group Jay Hauser 24 Feb 2009 7

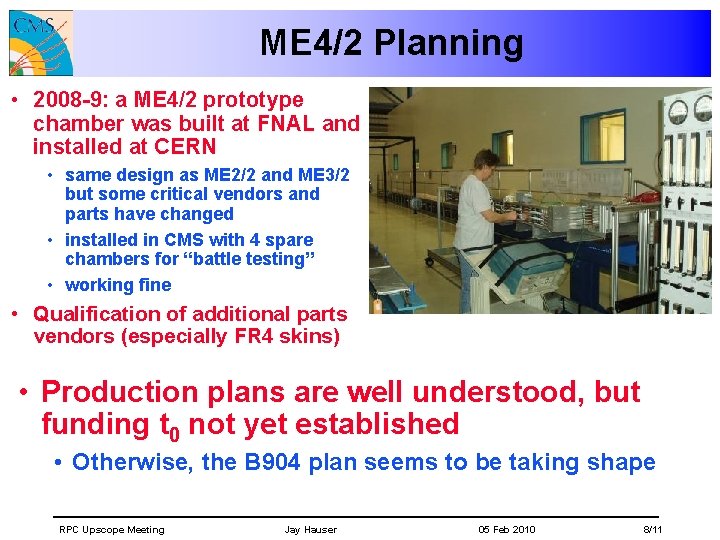

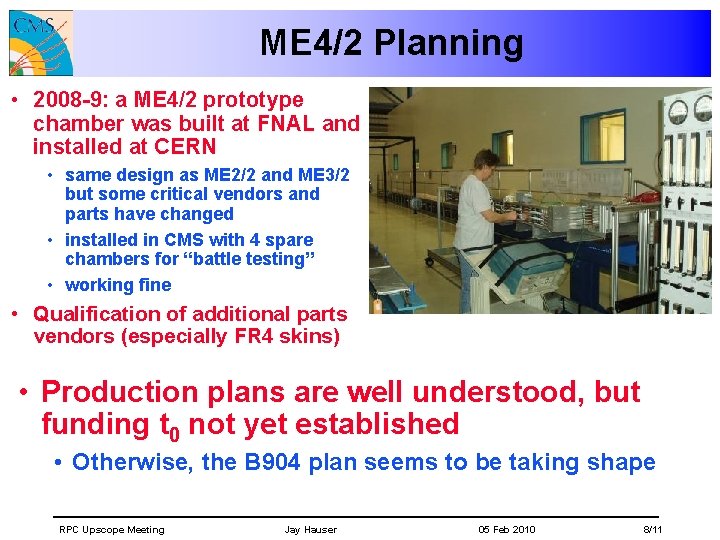

ME 4/2 Planning • 2008 -9: a ME 4/2 prototype chamber was built at FNAL and installed at CERN • same design as ME 2/2 and ME 3/2 but some critical vendors and parts have changed • installed in CMS with 4 spare chambers for “battle testing” • working fine • Qualification of additional parts vendors (especially FR 4 skins) • Production plans are well understood, but funding t 0 not yet established • Otherwise, the B 904 plan seems to be taking shape RPC Upscope Meeting Jay Hauser 05 Feb 2010 8/11

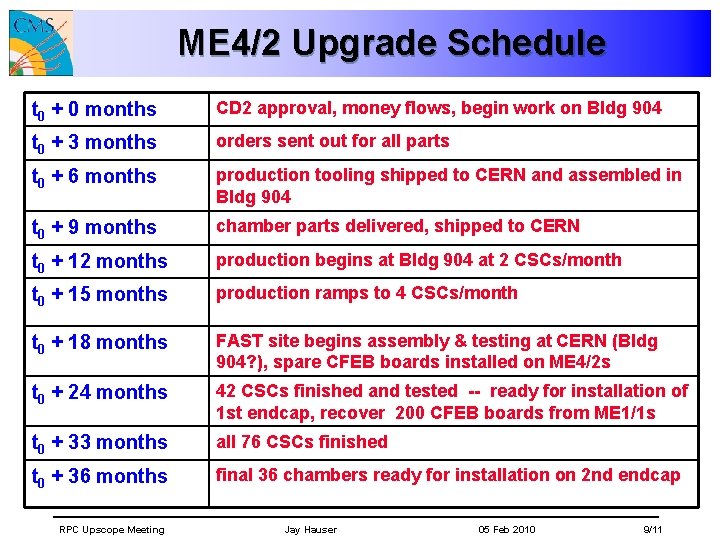

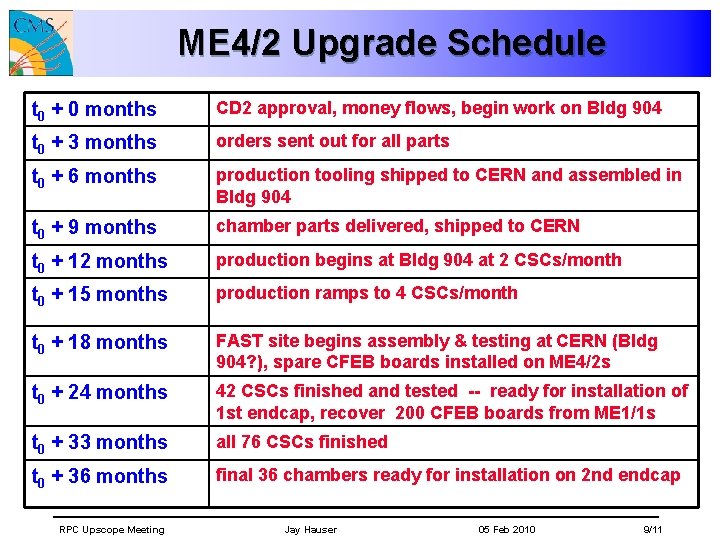

ME 4/2 Upgrade Schedule t 0 + 0 months CD 2 approval, money flows, begin work on Bldg 904 t 0 + 3 months orders sent out for all parts t 0 + 6 months production tooling shipped to CERN and assembled in Bldg 904 t 0 + 9 months chamber parts delivered, shipped to CERN t 0 + 12 months production begins at Bldg 904 at 2 CSCs/month t 0 + 15 months production ramps to 4 CSCs/month t 0 + 18 months FAST site begins assembly & testing at CERN (Bldg 904? ), spare CFEB boards installed on ME 4/2 s t 0 + 24 months 42 CSCs finished and tested -- ready for installation of 1 st endcap, recover 200 CFEB boards from ME 1/1 s t 0 + 33 months all 76 CSCs finished t 0 + 36 months final 36 chambers ready for installation on 2 nd endcap RPC Upscope Meeting Jay Hauser 05 Feb 2010 9/11

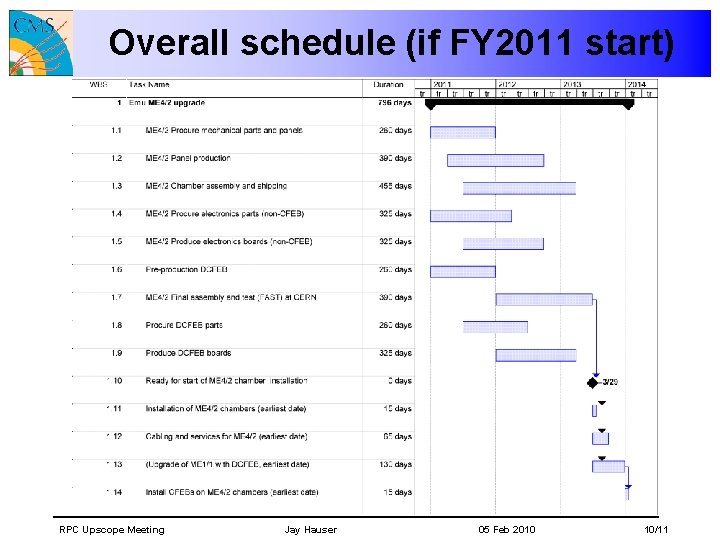

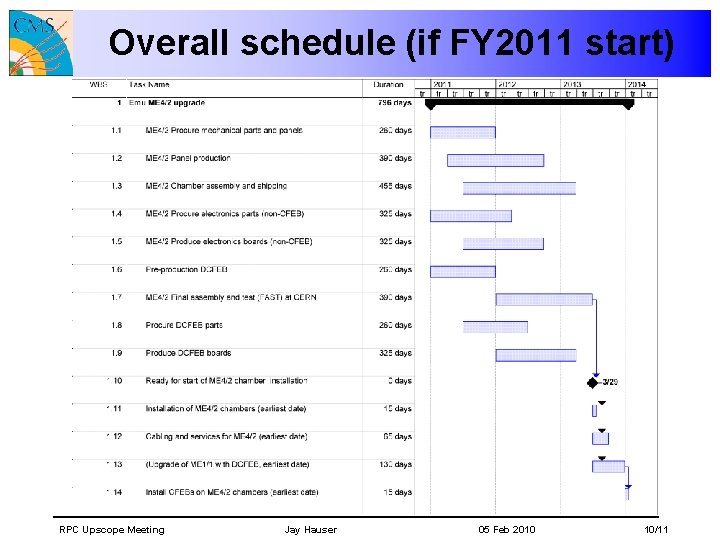

Overall schedule (if FY 2011 start) RPC Upscope Meeting Jay Hauser 05 Feb 2010 10/11

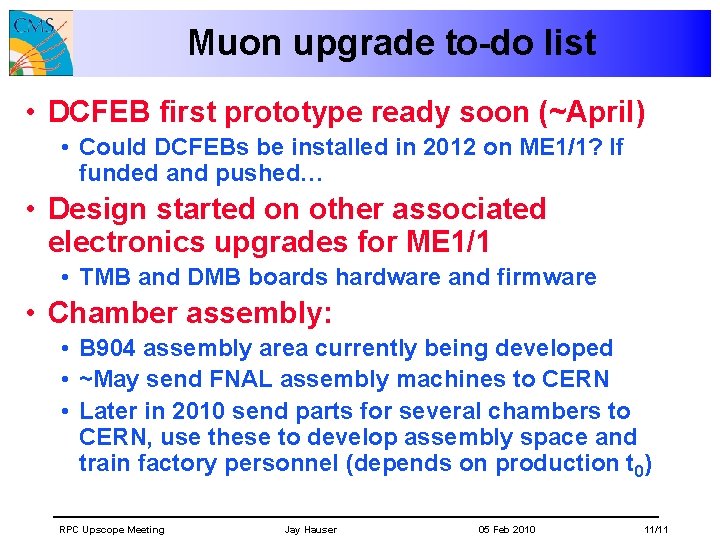

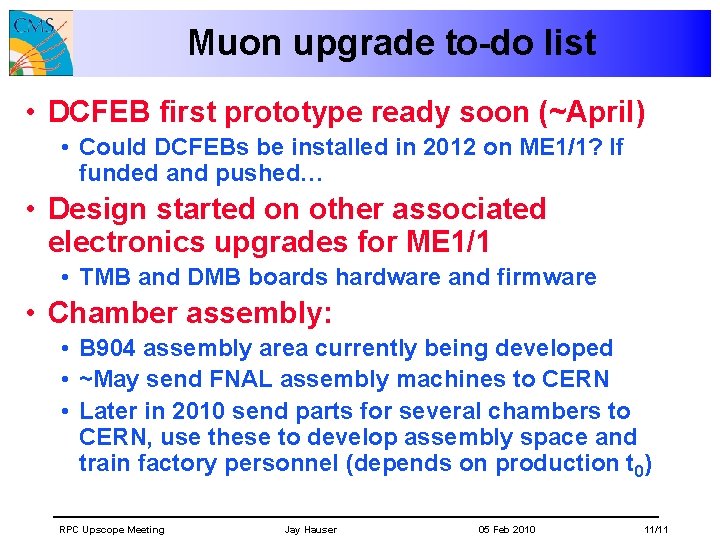

Muon upgrade to-do list • DCFEB first prototype ready soon (~April) • Could DCFEBs be installed in 2012 on ME 1/1? If funded and pushed… • Design started on other associated electronics upgrades for ME 1/1 • TMB and DMB boards hardware and firmware • Chamber assembly: • B 904 assembly area currently being developed • ~May send FNAL assembly machines to CERN • Later in 2010 send parts for several chambers to CERN, use these to develop assembly space and train factory personnel (depends on production t 0) RPC Upscope Meeting Jay Hauser 05 Feb 2010 11/11

Backup Slides RPC Upscope Meeting Jay Hauser 05 Feb 2010 12/11

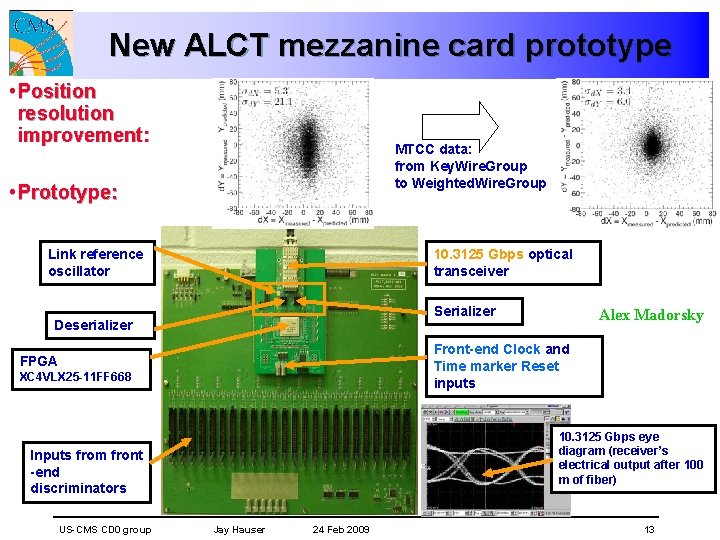

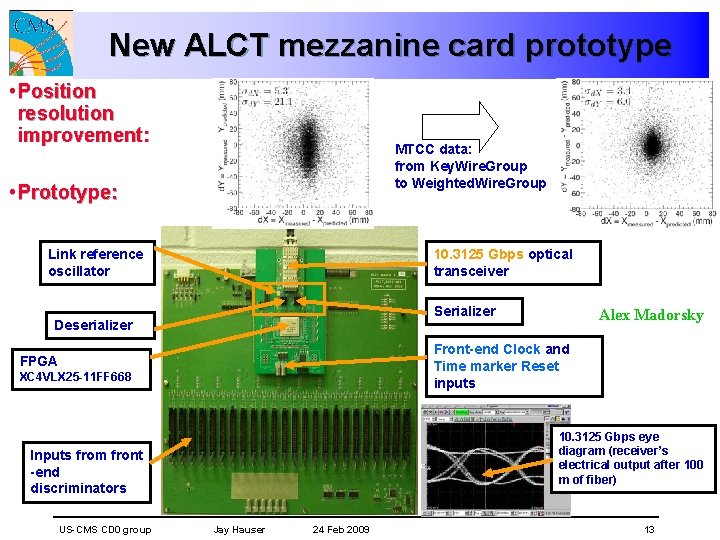

New ALCT mezzanine card prototype • Position resolution improvement: MTCC data: from Key. Wire. Group to Weighted. Wire. Group • Prototype: 10. 3125 Gbps optical transceiver Link reference oscillator Serializer Deserializer Front-end Clock and Time marker Reset inputs FPGA XC 4 VLX 25 -11 FF 668 10. 3125 Gbps eye diagram (receiver’s electrical output after 100 m of fiber) Inputs from front -end discriminators US-CMS CD 0 group Alex Madorsky Jay Hauser 24 Feb 2009 13

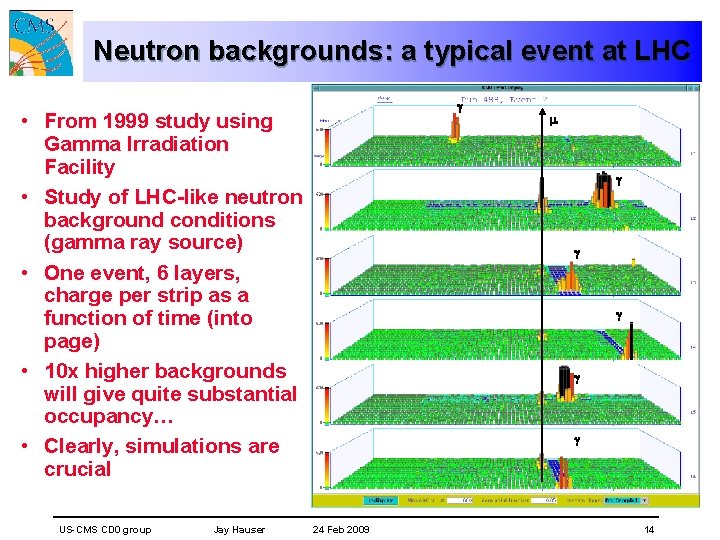

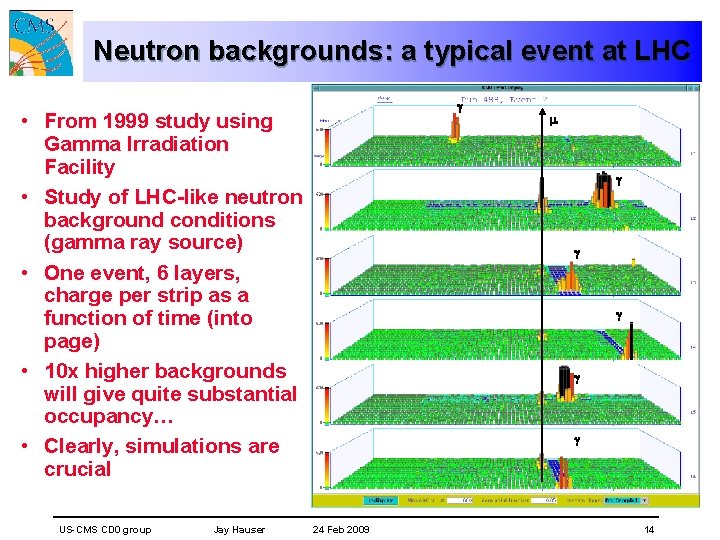

Neutron backgrounds: a typical event at LHC g • From 1999 study using Gamma Irradiation Facility • Study of LHC-like neutron background conditions (gamma ray source) • One event, 6 layers, charge per strip as a function of time (into page) • 10 x higher backgrounds will give quite substantial occupancy… • Clearly, simulations are crucial US-CMS CD 0 group Jay Hauser m g g g 24 Feb 2009 14

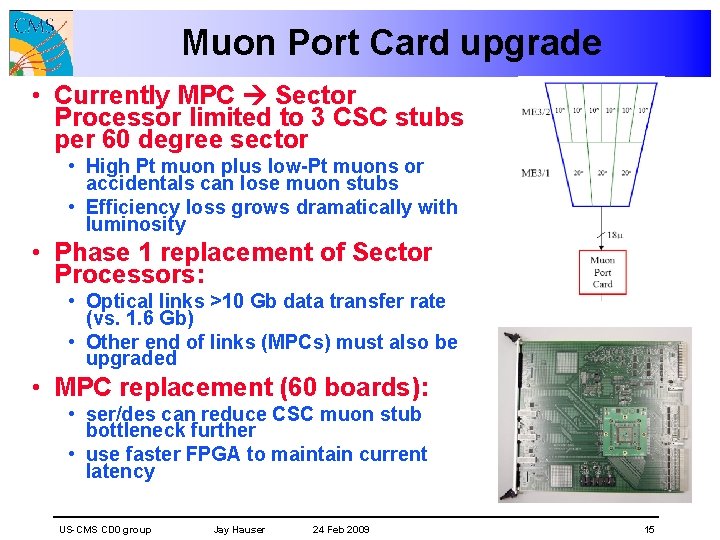

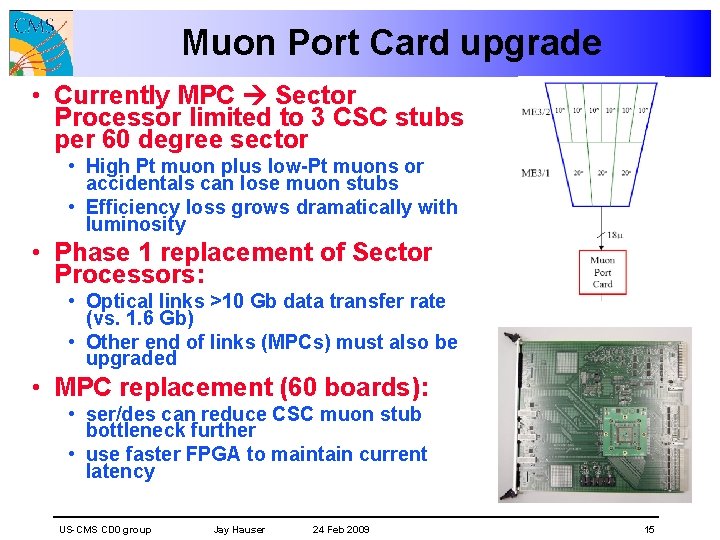

Muon Port Card upgrade • Currently MPC Sector Processor limited to 3 CSC stubs per 60 degree sector • High Pt muon plus low-Pt muons or accidentals can lose muon stubs • Efficiency loss grows dramatically with luminosity • Phase 1 replacement of Sector Processors: • Optical links >10 Gb data transfer rate (vs. 1. 6 Gb) • Other end of links (MPCs) must also be upgraded • MPC replacement (60 boards): • ser/des can reduce CSC muon stub bottleneck further • use faster FPGA to maintain current latency US-CMS CD 0 group Jay Hauser 24 Feb 2009 15

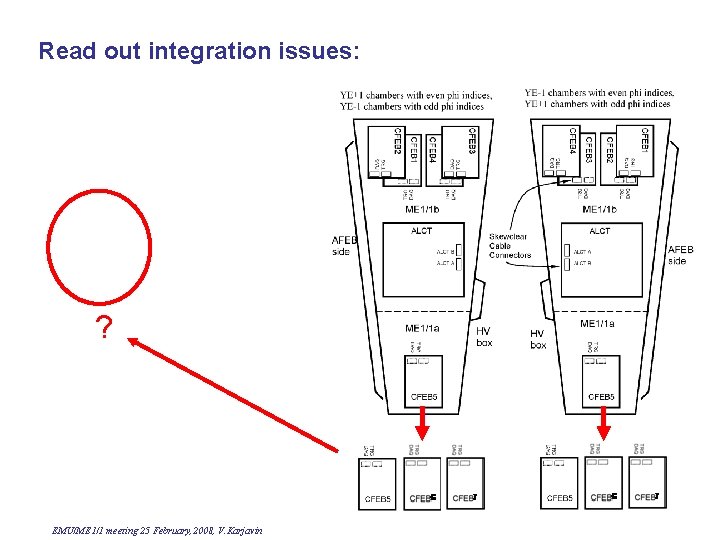

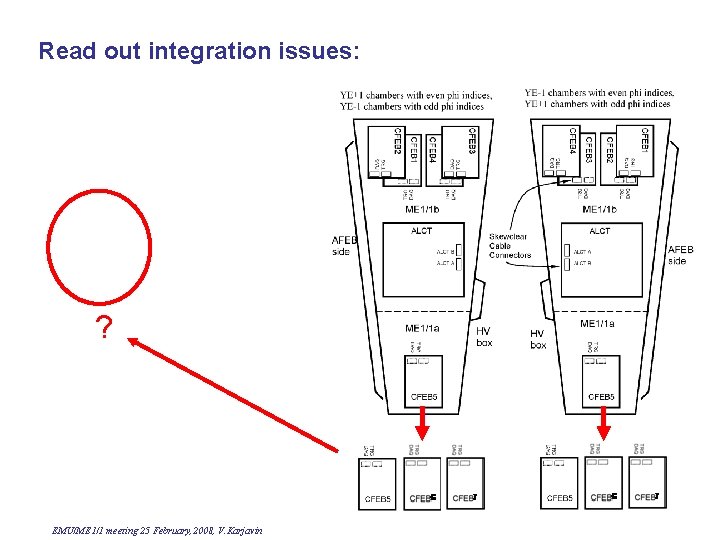

Read out integration issues: ? EMU/ME 1/1 meeting 25 February, 2008, V. Karjavin

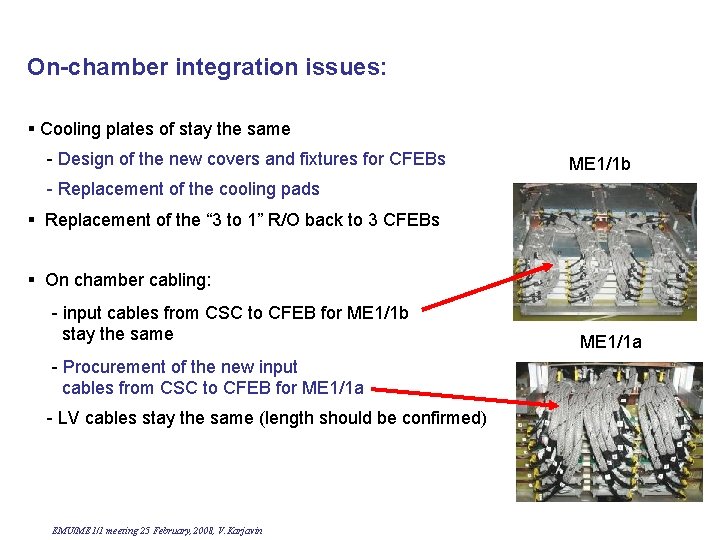

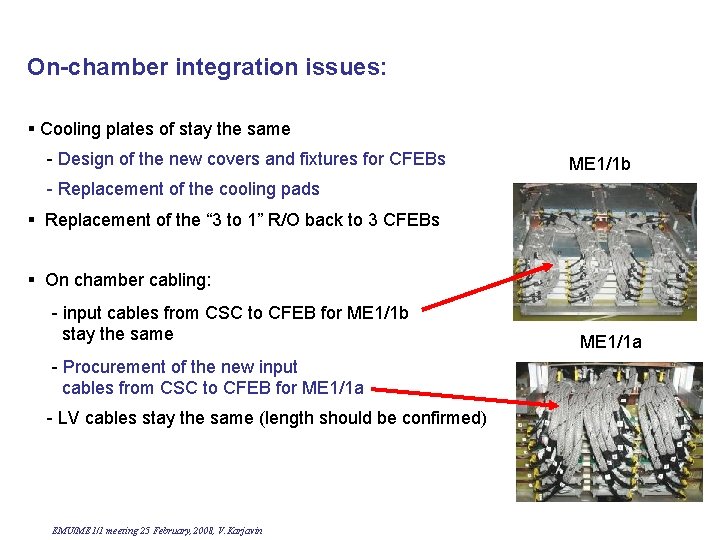

On-chamber integration issues: § Cooling plates of stay the same - Design of the new covers and fixtures for CFEBs ME 1/1 b - Replacement of the cooling pads § Replacement of the “ 3 to 1” R/O back to 3 CFEBs § On chamber cabling: - input cables from CSC to CFEB for ME 1/1 b stay the same - Procurement of the new input cables from CSC to CFEB for ME 1/1 a - LV cables stay the same (length should be confirmed) EMU/ME 1/1 meeting 25 February, 2008, V. Karjavin ME 1/1 a

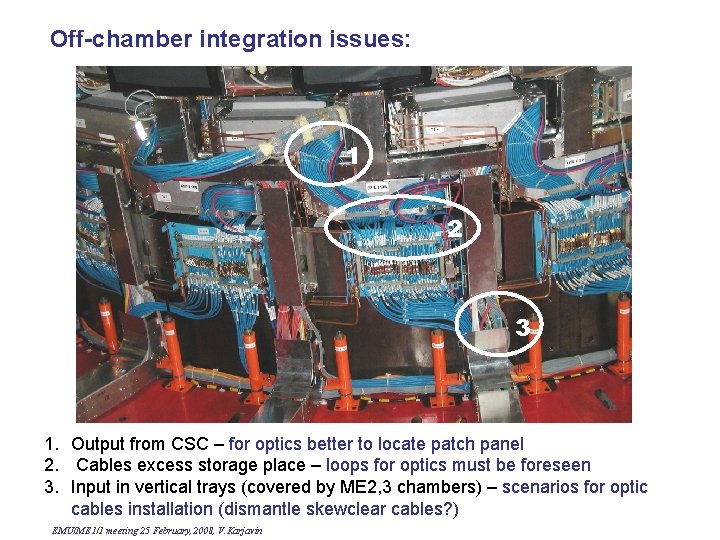

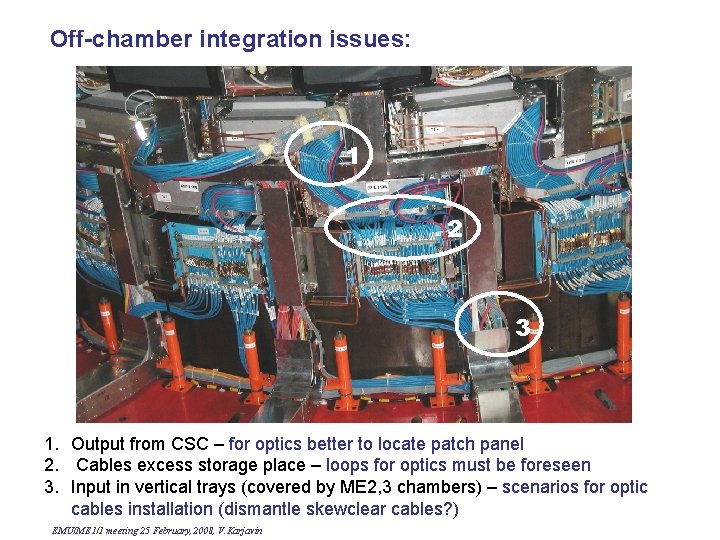

Off-chamber integration issues: 1 2 3 1. Output from CSC – for optics better to locate patch panel 2. Cables excess storage place – loops for optics must be foreseen 3. Input in vertical trays (covered by ME 2, 3 chambers) – scenarios for optic cables installation (dismantle skewclear cables? ) EMU/ME 1/1 meeting 25 February, 2008, V. Karjavin

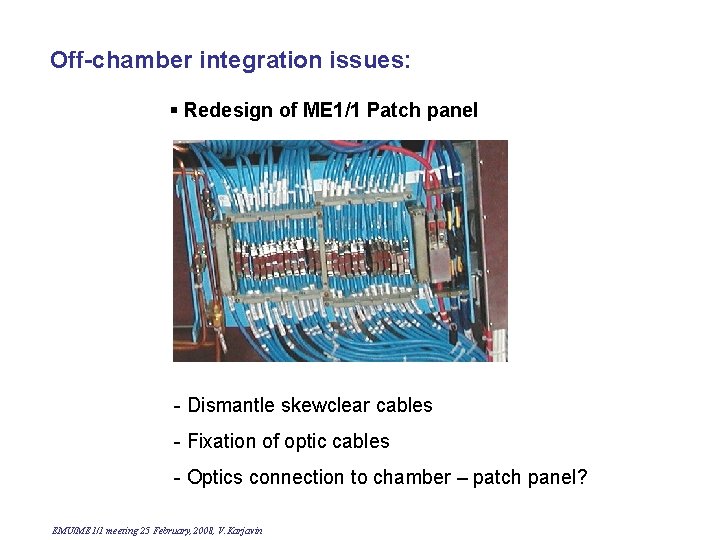

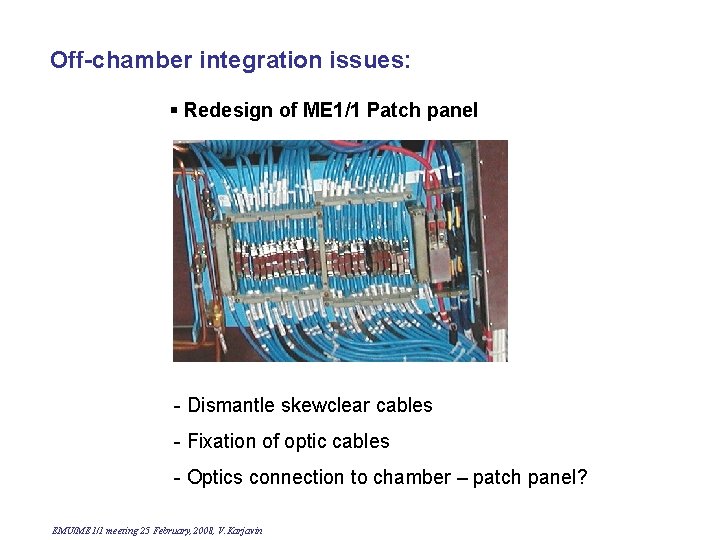

Off-chamber integration issues: § Redesign of ME 1/1 Patch panel - Dismantle skewclear cables - Fixation of optic cables - Optics connection to chamber – patch panel? EMU/ME 1/1 meeting 25 February, 2008, V. Karjavin

Phase 2 upgrade To-Do items • Understand background rates from real data • Understand implications of backgrounds: • Trigger rates, data bottlenecks, performance degradation • SEU rates • Electronics radiation hardness • Understand implications of track trigger upgrade • Understand benefits of better trigger primitive resolution RPC Upscope Meeting Jay Hauser 05 Feb 2010 20/11