Overview of SLB ASIC Introduction SLB Internal Structure

Overview of SLB ASIC Introduction SLB Internal Structure Evaluation for Radiation Tolerance Inspection procedure in the production Plan for Mass-Production March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 1

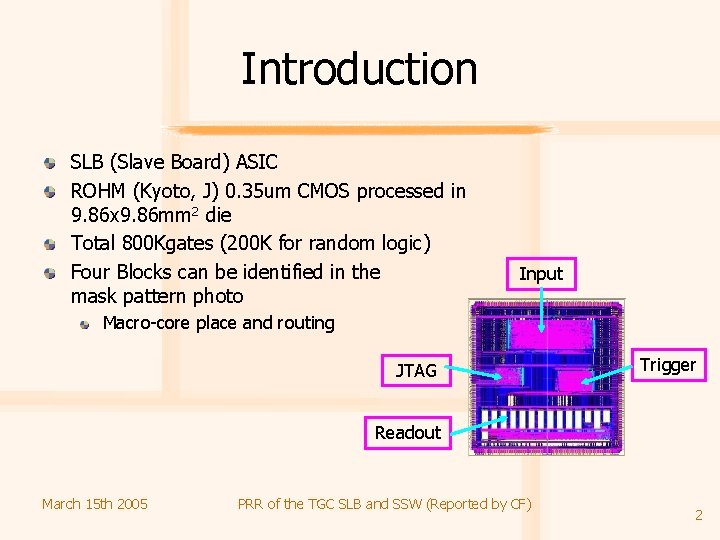

Introduction SLB (Slave Board) ASIC ROHM (Kyoto, J) 0. 35 um CMOS processed in 9. 86 x 9. 86 mm 2 die Total 800 Kgates (200 K for random logic) Four Blocks can be identified in the mask pattern photo Input Macro-core place and routing JTAG Trigger Readout March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 2

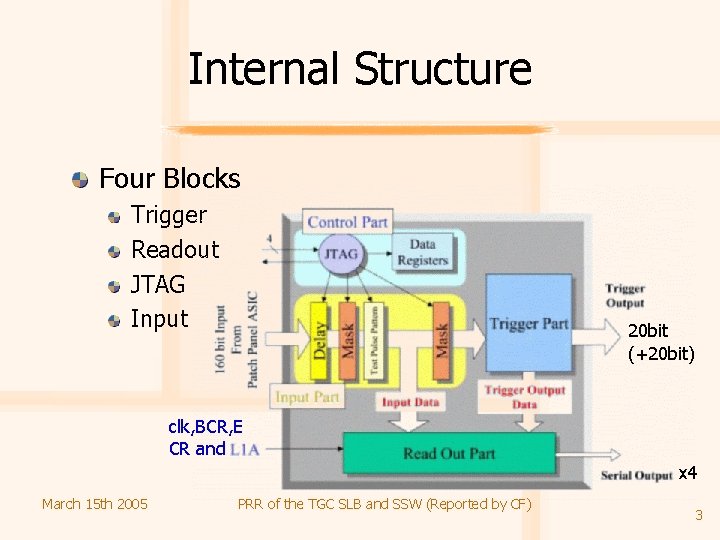

Internal Structure Four Blocks Trigger Readout JTAG Input 20 bit (+20 bit) clk, BCR, E CR and x 4 March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 3

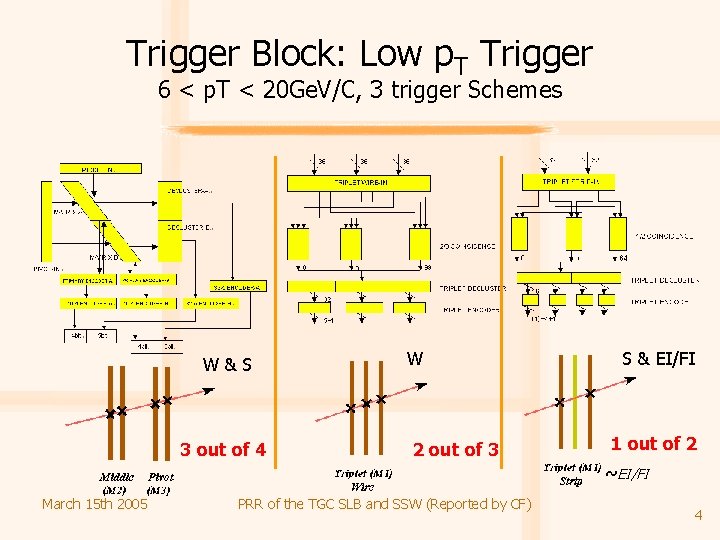

Trigger Block: Low p. T Trigger 6 < p. T < 20 Ge. V/C, 3 trigger Schemes W&S 3 out of 4 W 2 out of 3 S & EI/FI 1 out of 2 ~EI/FI March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 4

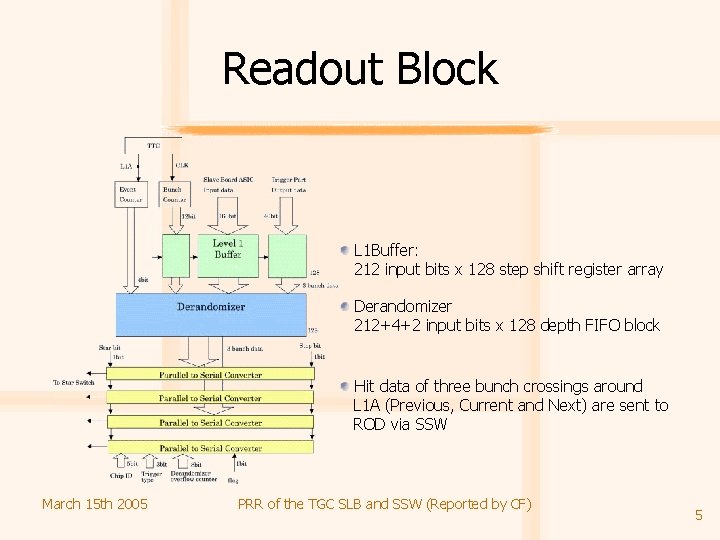

Readout Block L 1 Buffer: 212 input bits x 128 step shift register array Derandomizer 212+4+2 input bits x 128 depth FIFO block Hit data of three bunch crossings around L 1 A (Previous, Current and Next) are sent to ROD via SSW March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 5

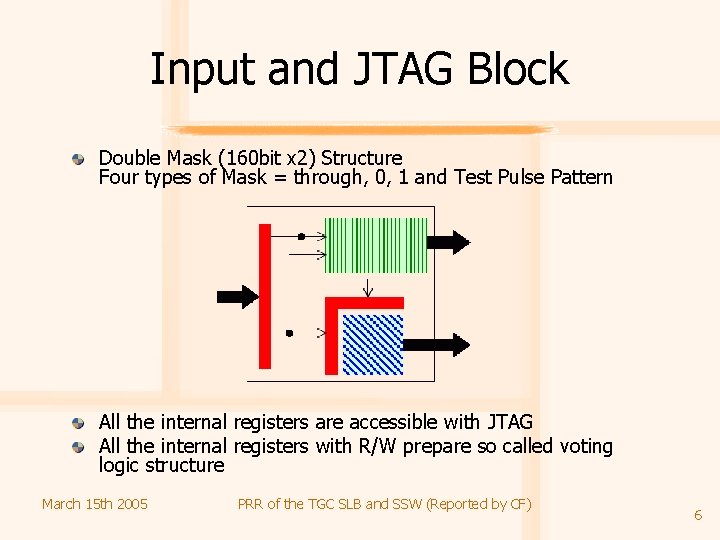

Input and JTAG Block Double Mask (160 bit x 2) Structure Four types of Mask = through, 0, 1 and Test Pulse Pattern All the internal registers are accessible with JTAG All the internal registers with R/W prepare so called voting logic structure March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 6

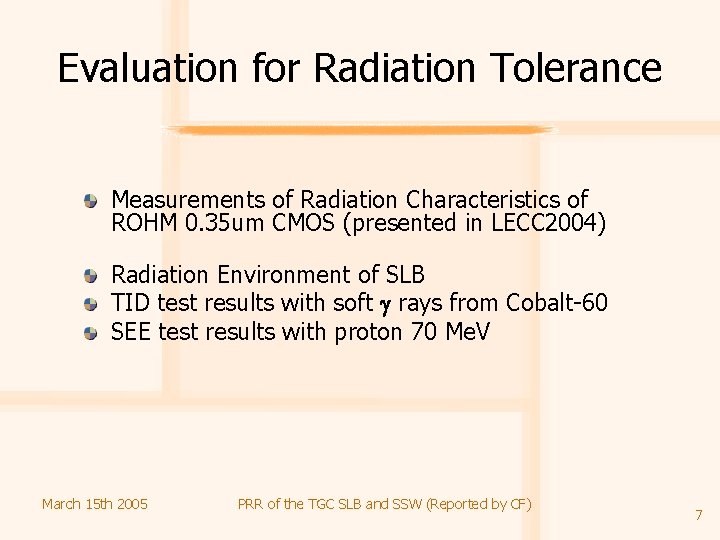

Evaluation for Radiation Tolerance Measurements of Radiation Characteristics of ROHM 0. 35 um CMOS (presented in LECC 2004) Radiation Environment of SLB TID test results with soft g rays from Cobalt-60 SEE test results with proton 70 Me. V March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 7

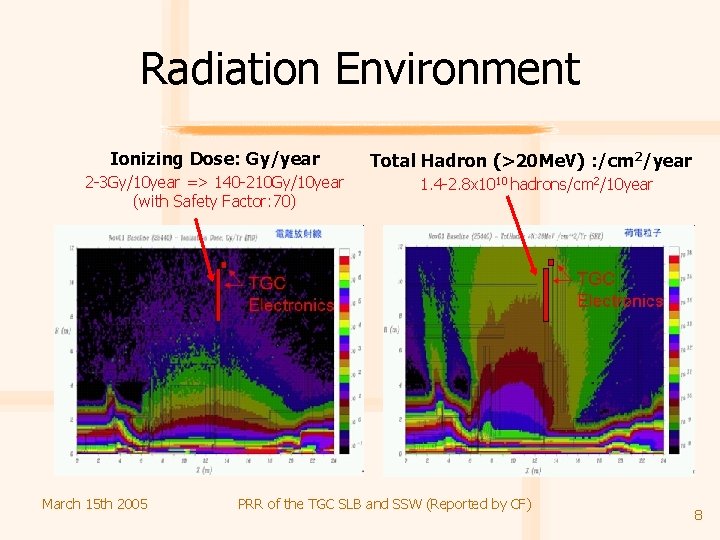

Radiation Environment Ionizing Dose: Gy/year 2 -3 Gy/10 year => 140 -210 Gy/10 year (with Safety Factor: 70) March 15 th 2005 Total Hadron (>20 Me. V) : /cm 2/year 1. 4 -2. 8 x 1010 hadrons/cm 2/10 year PRR of the TGC SLB and SSW (Reported by CF) 8

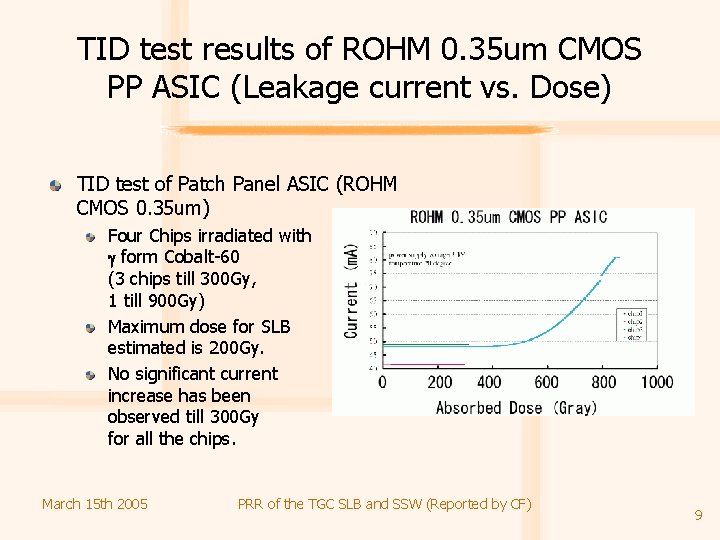

TID test results of ROHM 0. 35 um CMOS PP ASIC (Leakage current vs. Dose) TID test of Patch Panel ASIC (ROHM CMOS 0. 35 um) Four Chips irradiated with g form Cobalt-60 (3 chips till 300 Gy, 1 till 900 Gy) Maximum dose for SLB estimated is 200 Gy. No significant current increase has been observed till 300 Gy for all the chips. March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 9

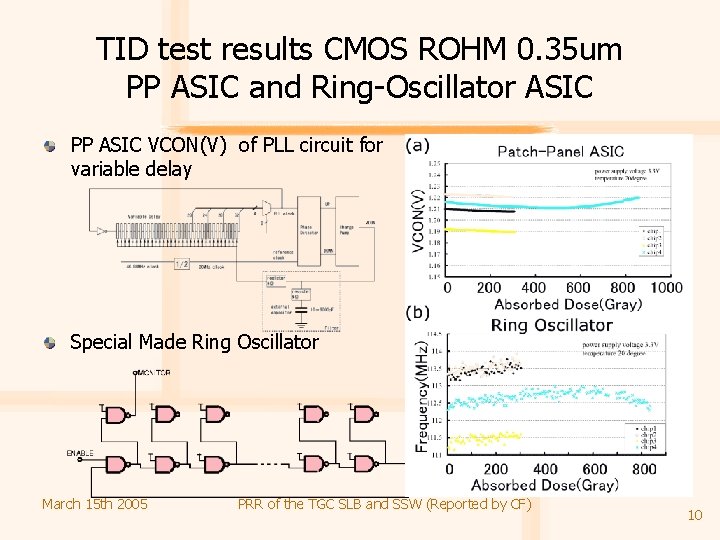

TID test results CMOS ROHM 0. 35 um PP ASIC and Ring-Oscillator ASIC PP ASIC VCON(V) of PLL circuit for variable delay Special Made Ring Oscillator March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 10

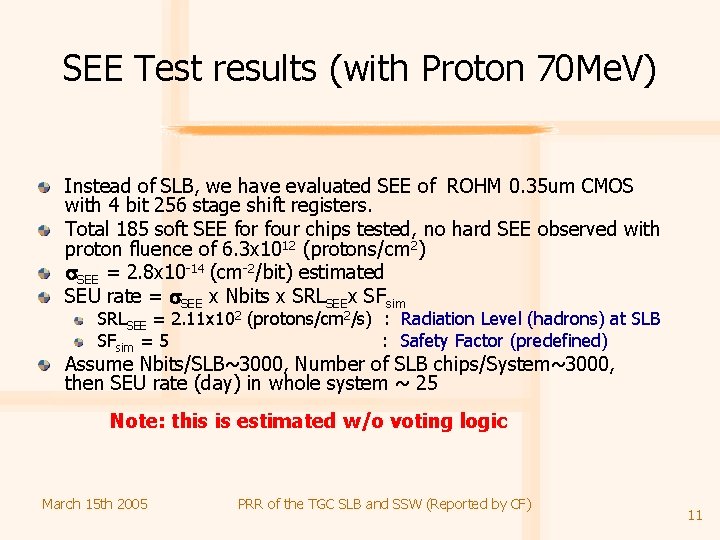

SEE Test results (with Proton 70 Me. V) Instead of SLB, we have evaluated SEE of ROHM 0. 35 um CMOS with 4 bit 256 stage shift registers. Total 185 soft SEE for four chips tested, no hard SEE observed with proton fluence of 6. 3 x 1012 (protons/cm 2) s. SEE = 2. 8 x 10 -14 (cm-2/bit) estimated SEU rate = s. SEE x Nbits x SRLSEEx SFsim SRLSEE = 2. 11 x 102 (protons/cm 2/s) : Radiation Level (hadrons) at SLB SFsim = 5 : Safety Factor (predefined) Assume Nbits/SLB~3000, Number of SLB chips/System~3000, then SEU rate (day) in whole system ~ 25 Note: this is estimated w/o voting logic March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 11

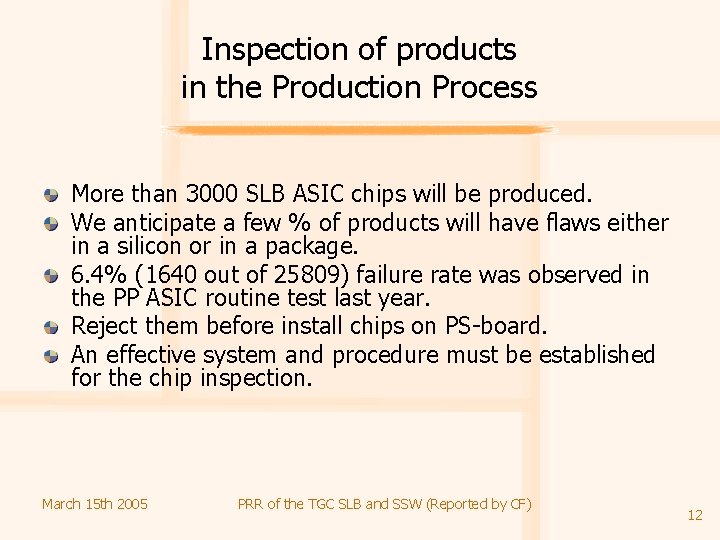

Inspection of products in the Production Process More than 3000 SLB ASIC chips will be produced. We anticipate a few % of products will have flaws either in a silicon or in a package. 6. 4% (1640 out of 25809) failure rate was observed in the PP ASIC routine test last year. Reject them before install chips on PS-board. An effective system and procedure must be established for the chip inspection. March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 12

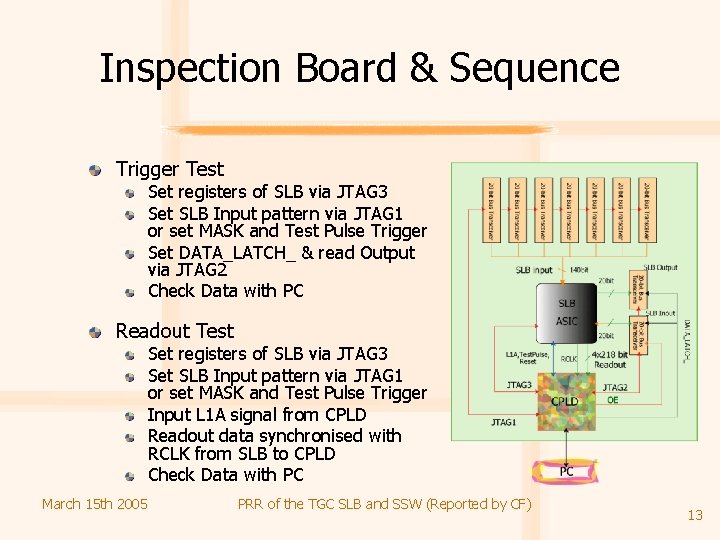

Inspection Board & Sequence Trigger Test Set registers of SLB via JTAG 3 Set SLB Input pattern via JTAG 1 or set MASK and Test Pulse Trigger Set DATA_LATCH_ & read Output via JTAG 2 Check Data with PC Readout Test Set registers of SLB via JTAG 3 Set SLB Input pattern via JTAG 1 or set MASK and Test Pulse Trigger Input L 1 A signal from CPLD Readout data synchronised with RCLK from SLB to CPLD Check Data with PC March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 13

Inspection Procedure Inspection must be done by routine-operators for all chips delivered. The Test procedure planned is as follows: Standard power-on test (current measurement) Check of SLB register access (R/W) Trigger output check with five different types (WD, WT, SD, ST and EI/FI) With Different delay values With Different coincidence conditions Using SLB input or mask set with test pulse trigger Readout data during the test by inputting L 1 A in appropriate timing, and check of data consistency. The test frequency will be suitably determined but lower than 40 MHz. March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 14

Plan for mass-production We have now one working version of SLB (version so called 4 ECO 2). In the end of March 2005 (next week), version 6 will be delivered. We then check this one, and determine which will be used for the production if version 6 works fine. If every part of version 6 works fine, this must be selected for the production. We will make this decision in the middle of April. We will order ROHM for production immediately. The production takes 1. 5 -2 months. We will get products early in June at latest. The inspection will take a month subsequently. We complete SLB production in the beginning of August. Overall costs for production including inspection takes 15 M ~ SFr 150 K March 15 th 2005 PRR of the TGC SLB and SSW (Reported by CF) 15

- Slides: 15