Overview of SHARC processor ADSP2106 X Memory Operations

![Example code // Global array long int array[4] = {2, 3, 4, 5}; // Example code // Global array long int array[4] = {2, 3, 4, 5}; //](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-12.jpg)

![Example code -- INVALID. section/dm seg_dmda; . GLOBAL _array; . var _array[ ] = Example code -- INVALID. section/dm seg_dmda; . GLOBAL _array; . var _array[ ] =](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-17.jpg)

![Example code -- INVALID temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 = Example code -- INVALID temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 =](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-18.jpg)

- Slides: 24

Overview of SHARC processor ADSP-2106 X Memory Operations M. R. Smith, Electrical and Computer Engineering, University of Calgary, Alberta, Canada smithmr @ ucalgary. ca

To be tackled today n n Reference sources Memory configuration and operations Sample instructions Some warnings of expected errors n Code review and code review standards 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 2

Reference Sources n n n ADSP-2106 x SHARC User’s Manual 2 nd edition, Analog Devices -- provided to everybody ENCM 515 SHARC Reference card ENCM 515 Course, Reference and Laboratory Notes n n n Check web-pages for links to Visual. DSP++, Compiler, Assembler, Linker and other tools Also see ECE-ADI-Project (link from Dr. Smith Home Page) SHARC Navigator Tutorial Tool See January 2004 web pages for link – shows basic assembly language operations using simple animation 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 3

Picture Source n SHARC Navigator Tutorial Tool T. Alukaidey@herts. ac. uk Talik Alukaidey Dept. of EEE Uninversity of Hertfordshire, Hatfield, U. K. 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 4

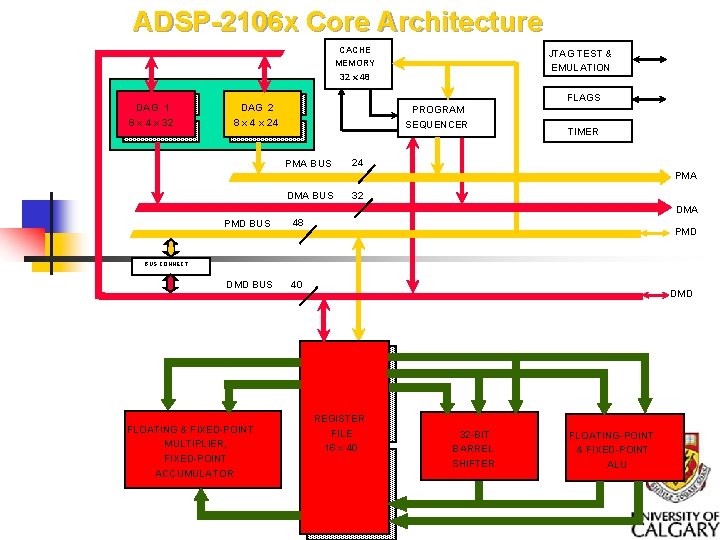

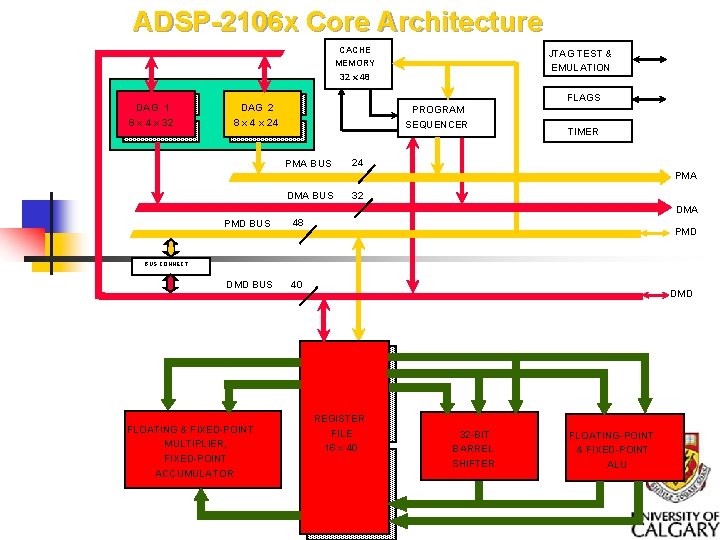

ADSP-2106 x Core Architecture CACHE MEMORY 32 x 48 DAG 1 8 x 4 x 32 JTAG TEST & EMULATION FLAGS DAG 2 8 x 4 x 24 PROGRAM SEQUENCER PMA BUS TIMER 24 PMA DMA BUS 32 DMA PMD BUS 48 DMD BUS 40 PMD BUS CONNECT FLOATING & FIXED-POINT MULTIPLIER, FIXED-POINT ACCUMULATOR DMD REGISTER FILE 16 x 40 32 -BIT BARREL SHIFTER FLOATING-POINT & FIXED-POINT ALU

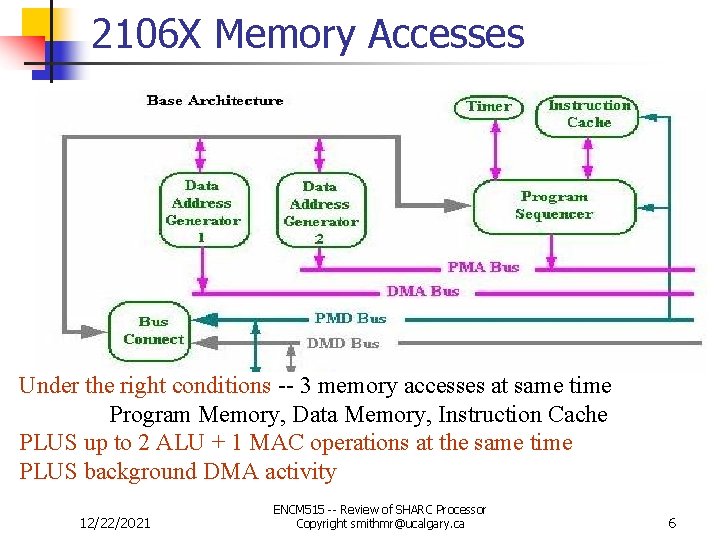

2106 X Memory Accesses Under the right conditions -- 3 memory accesses at same time Program Memory, Data Memory, Instruction Cache PLUS up to 2 ALU + 1 MAC operations at the same time PLUS background DMA activity 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 6

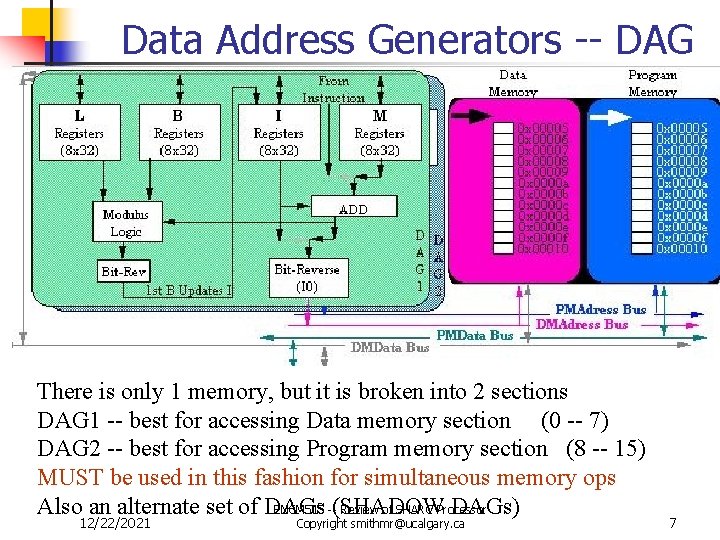

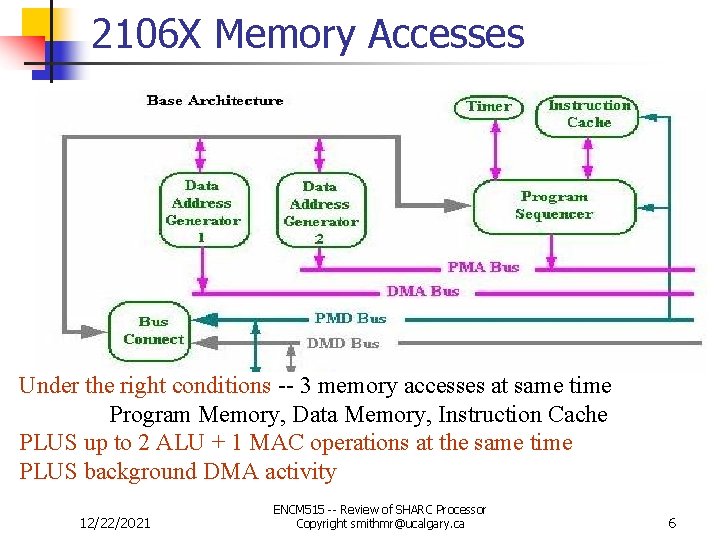

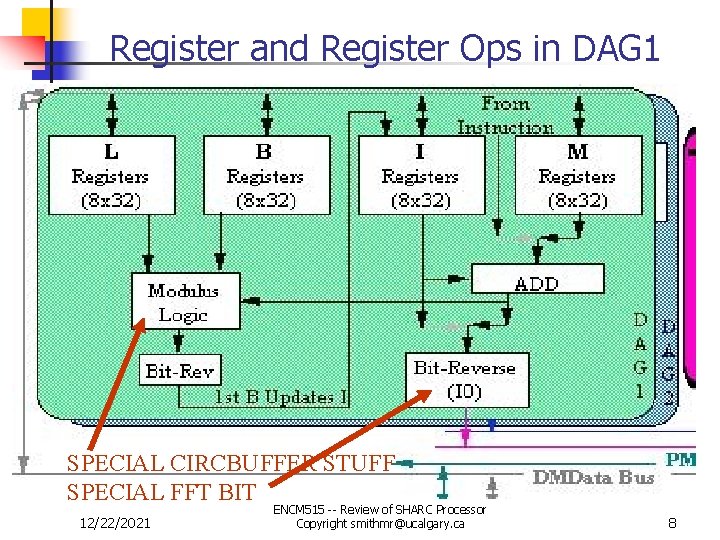

Data Address Generators -- DAG There is only 1 memory, but it is broken into 2 sections DAG 1 -- best for accessing Data memory section (0 -- 7) DAG 2 -- best for accessing Program memory section (8 -- 15) MUST be used in this fashion for simultaneous memory ops ENCM 515 --(SHADOW Review of SHARC Processor Also an alternate set of DAGs) 12/22/2021 Copyright smithmr@ucalgary. ca 7

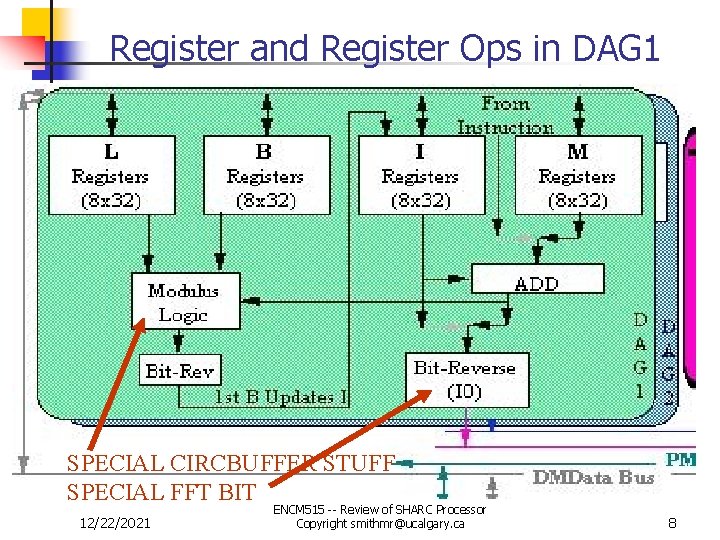

Register and Register Ops in DAG 1 SPECIAL CIRCBUFFER STUFF SPECIAL FFT BIT 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 8

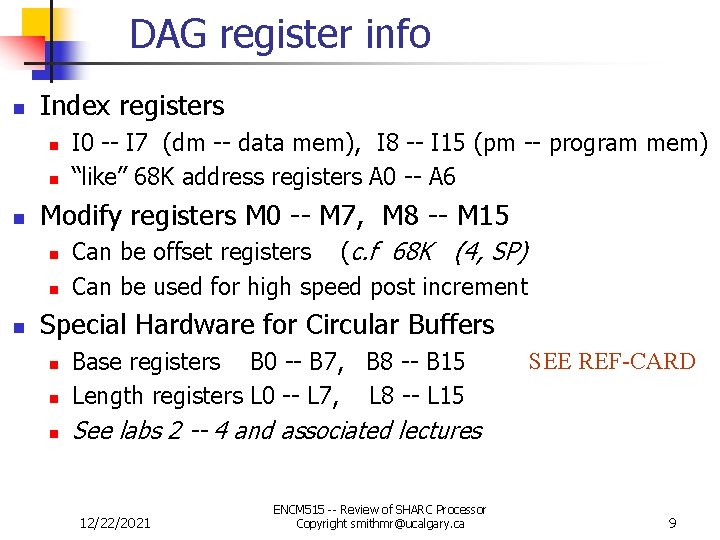

DAG register info n Index registers n n n Modify registers M 0 -- M 7, M 8 -- M 15 n n n I 0 -- I 7 (dm -- data mem), I 8 -- I 15 (pm -- program mem) “like” 68 K address registers A 0 -- A 6 Can be offset registers (c. f 68 K (4, SP) Can be used for high speed post increment Special Hardware for Circular Buffers n Base registers B 0 -- B 7, B 8 -- B 15 Length registers L 0 -- L 7, L 8 -- L 15 n See labs 2 -- 4 and associated lectures n 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca SEE REF-CARD 9

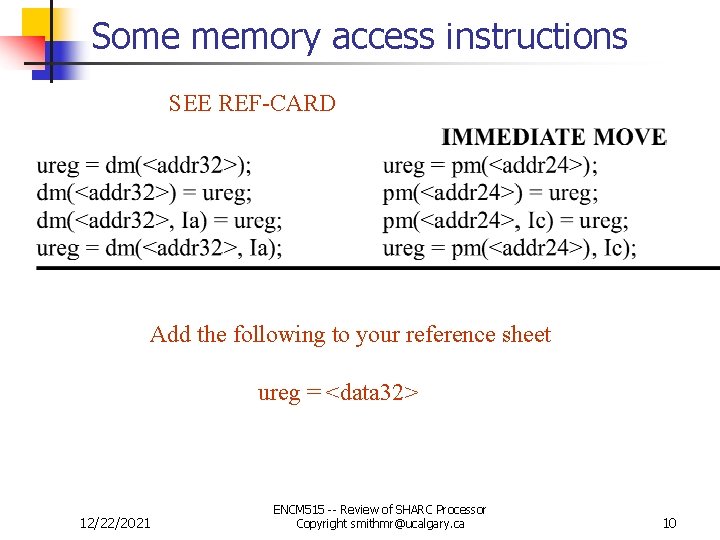

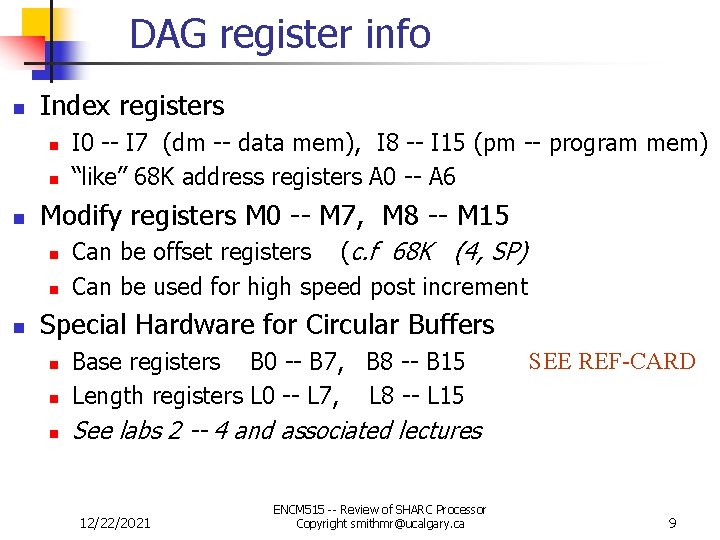

Some memory access instructions SEE REF-CARD Add the following to your reference sheet ureg = <data 32> 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 10

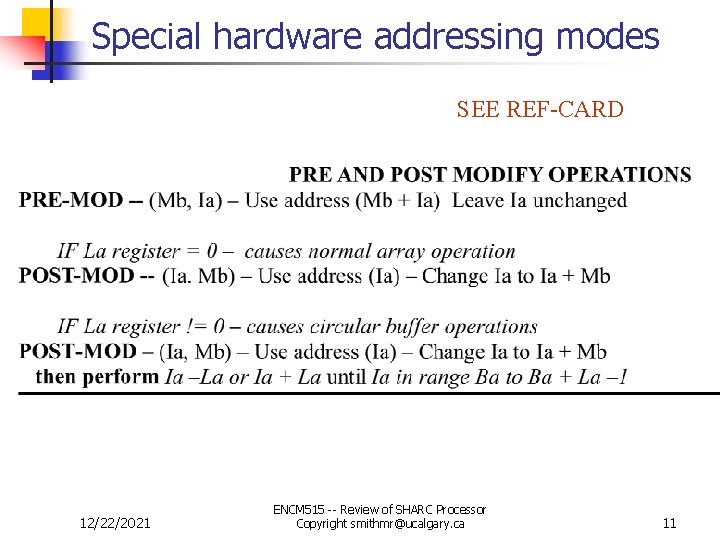

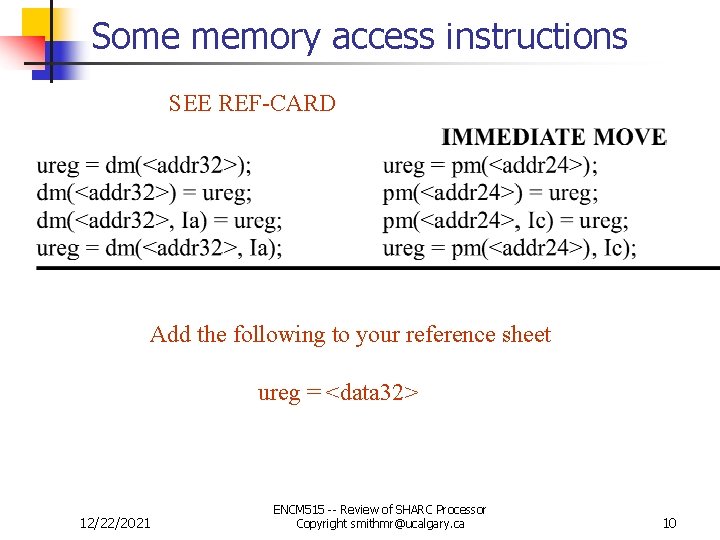

Special hardware addressing modes SEE REF-CARD 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 11

![Example code Global array long int array4 2 3 4 5 Example code // Global array long int array[4] = {2, 3, 4, 5}; //](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-12.jpg)

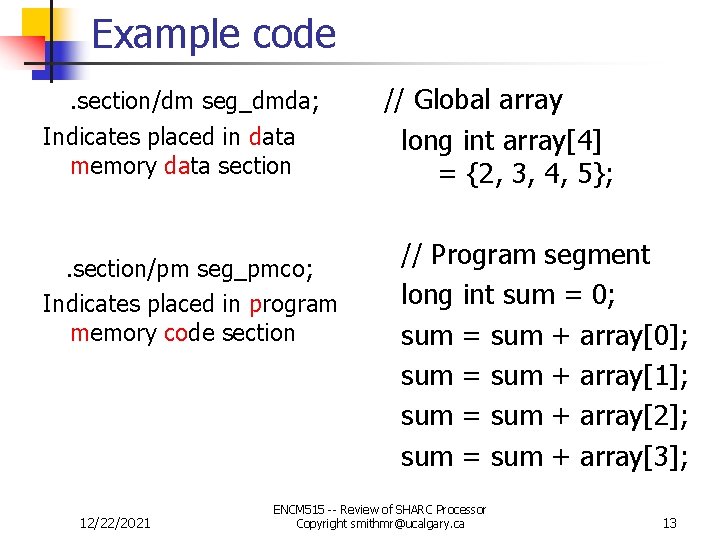

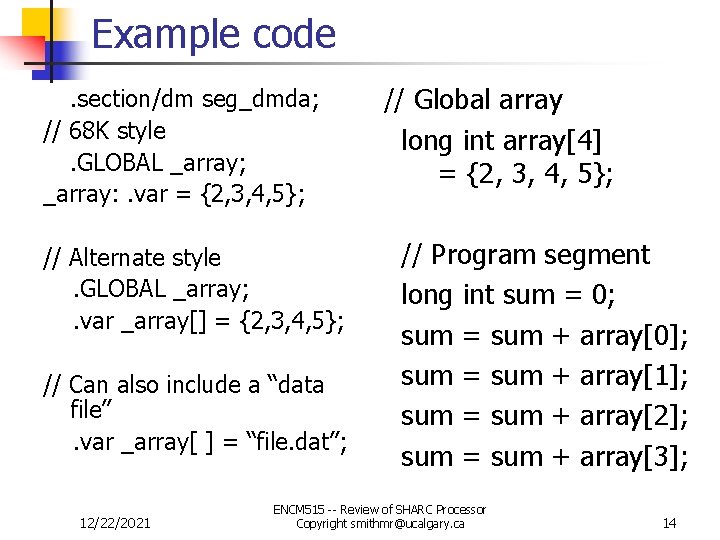

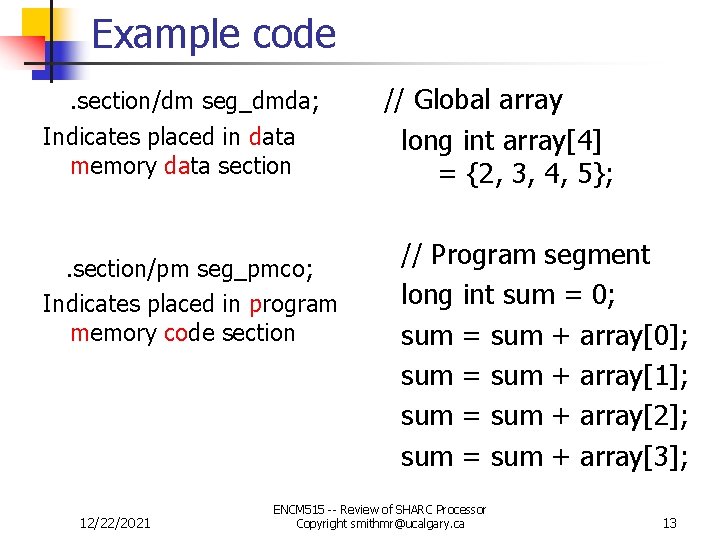

Example code // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 12

Example code. section/dm seg_dmda; Indicates placed in data memory data section . section/pm seg_pmco; Indicates placed in program memory code section 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 13

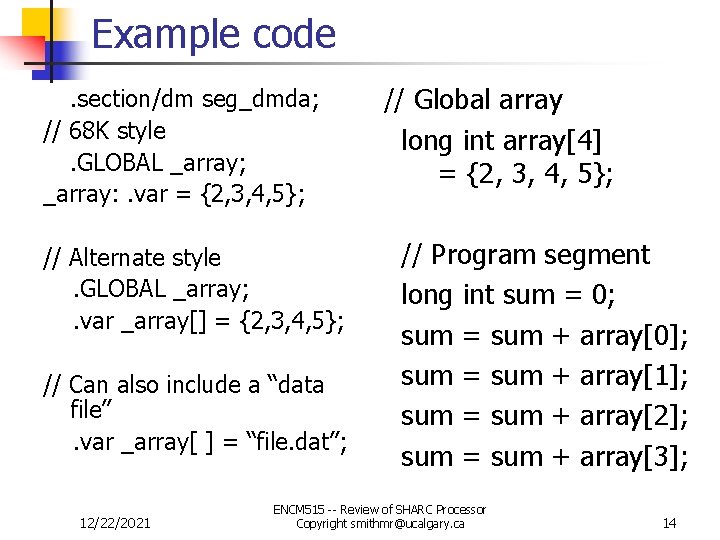

Example code. section/dm seg_dmda; // 68 K style. GLOBAL _array; _array: . var = {2, 3, 4, 5}; // Alternate style. GLOBAL _array; . var _array[] = {2, 3, 4, 5}; // Can also include a “data file”. var _array[ ] = “file. dat”; 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 14

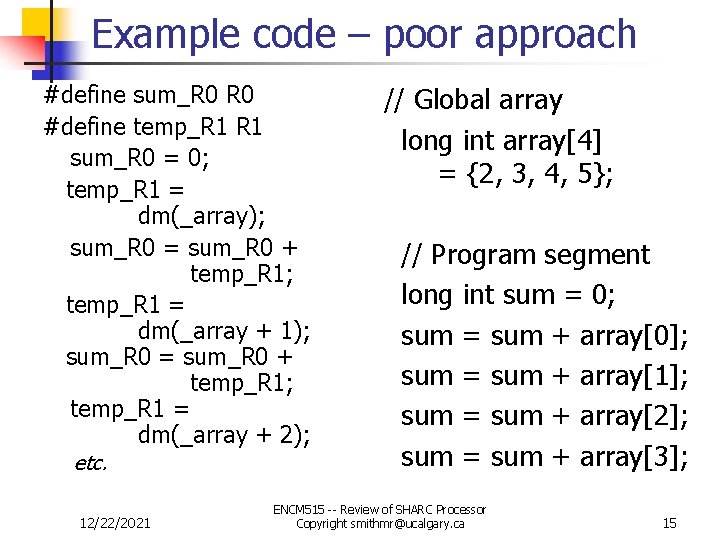

Example code – poor approach #define sum_R 0 #define temp_R 1 sum_R 0 = 0; temp_R 1 = dm(_array); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(_array + 1); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(_array + 2); etc. 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 15

Example code – correct, but poor. section/dm seg_dmda; . GLOBAL _array; . var _array[ ] = {2, 3, 4, 5}; . section/pm seg_pmco; #define sum_R 0 #define temp_R 1 #define array_pt_I 4 sum_R 0 = 0; array_pt_I 4 = _array; temp_R 1 = dm(0, array_pt_I 4); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(1, array_pt_I 4); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(2, array_pt_I 4); sum_R 0 = sum_R 0 + temp_R 1; 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 16

![Example code INVALID sectiondm segdmda GLOBAL array var array Example code -- INVALID. section/dm seg_dmda; . GLOBAL _array; . var _array[ ] =](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-17.jpg)

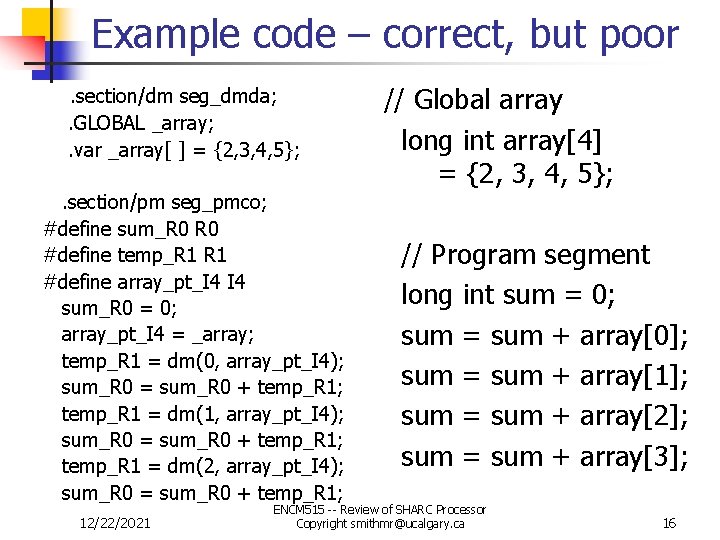

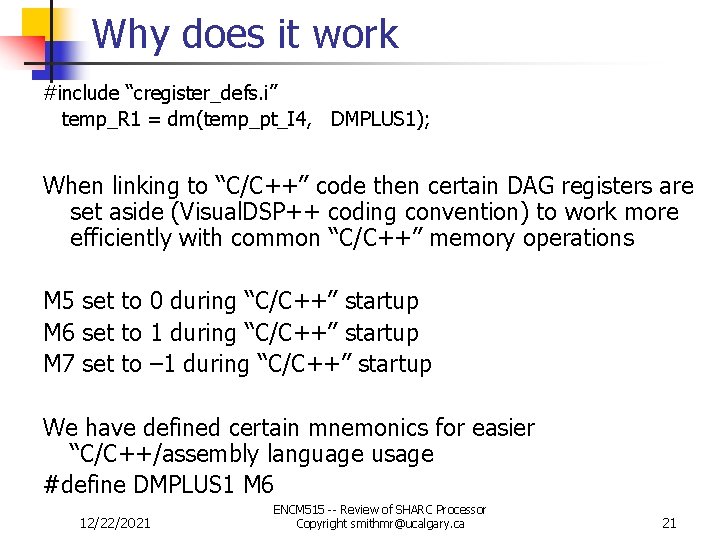

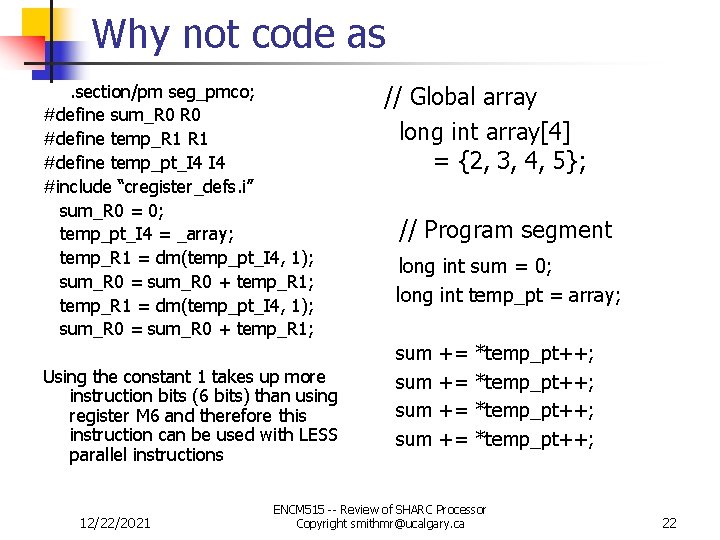

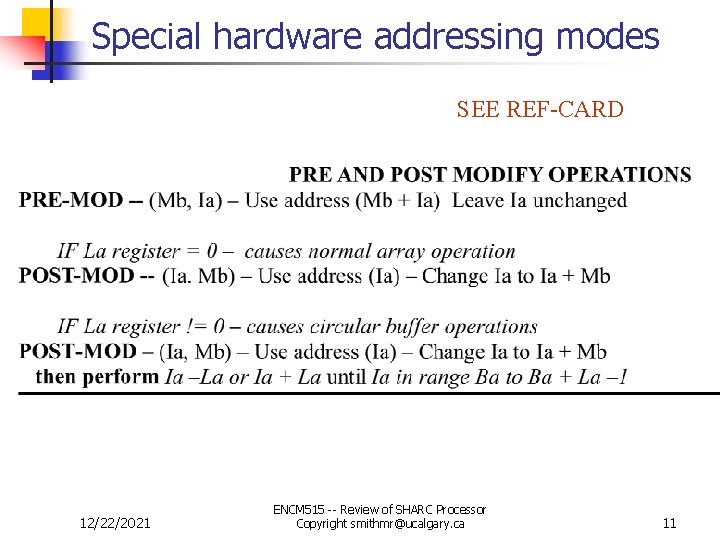

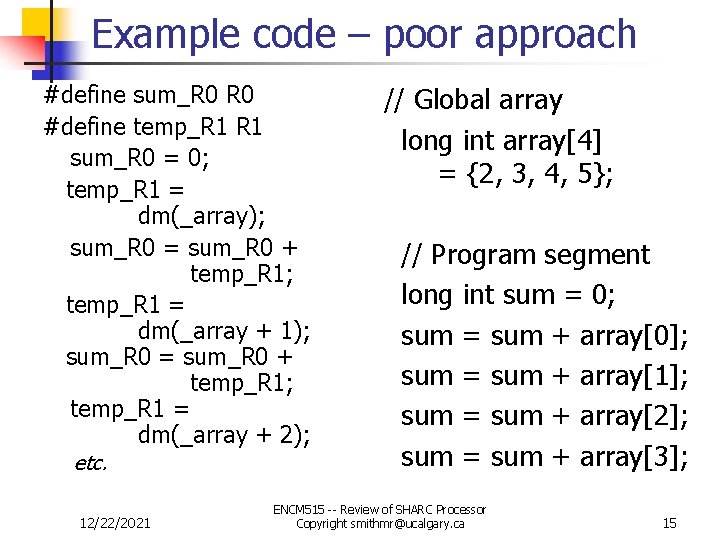

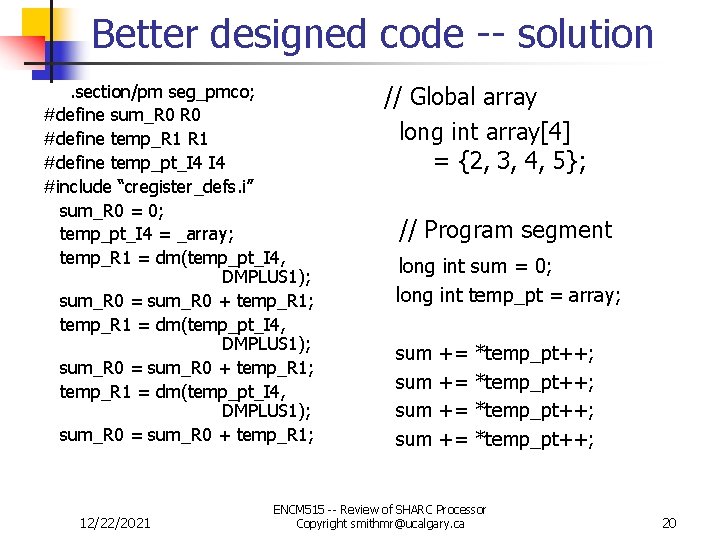

Example code -- INVALID. section/dm seg_dmda; . GLOBAL _array; . var _array[ ] = {2, 3, 4, 5}; . section/pm seg_pmco; #define sum_R 0 #define temp_R 1 #define array_pt_I 4 sum_R 0 = 0; array_pt_I 4 = _array; temp_R 1 = dm(array_pt_I 4, 0); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(array_pt_I 4, 1); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(array_pt_I 4, 2); sum_R 0 = sum_R 0 + temp_R 1; 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 17

![Example code INVALID tempR 1 Data MEMarrayptI 4 Then arrayptI 4 Example code -- INVALID temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 =](https://slidetodoc.com/presentation_image_h2/25698701122a48685f4fd063b7a301f7/image-18.jpg)

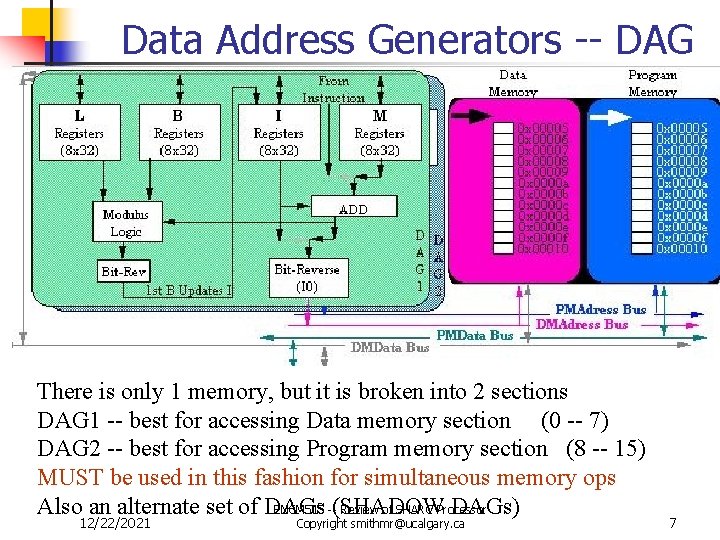

Example code -- INVALID temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 = array_pt_I 4 + 0; sum_R 0 = 0; array_pt_I 4 = _array; temp_R 1 = dm(array_pt_I 4, 0); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(array_pt_I 4, 1); sum_R 0 = sum_R 0 + temp_R 1; temp_R 1 = dm(array_pt_I 4, 2); sum_R 0 = sum_R 0 + temp_R 1; POST-MODIFY OPERATIONS SIMILAR TO 68 K increment MOVE. L (A 0)+, D 1 12/22/2021 temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 = array_pt_I 4 + 1; temp_R 1 = Data. MEM[array_pt_I 4]; Then array_pt_I 4 = array_pt_I 4 + 2; Sum of locations 0, 0, 1 with Pointer left at location 3 of array ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 18

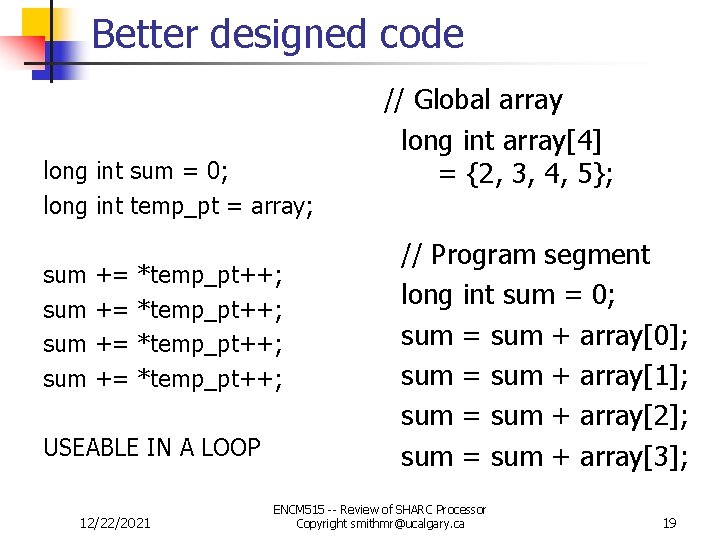

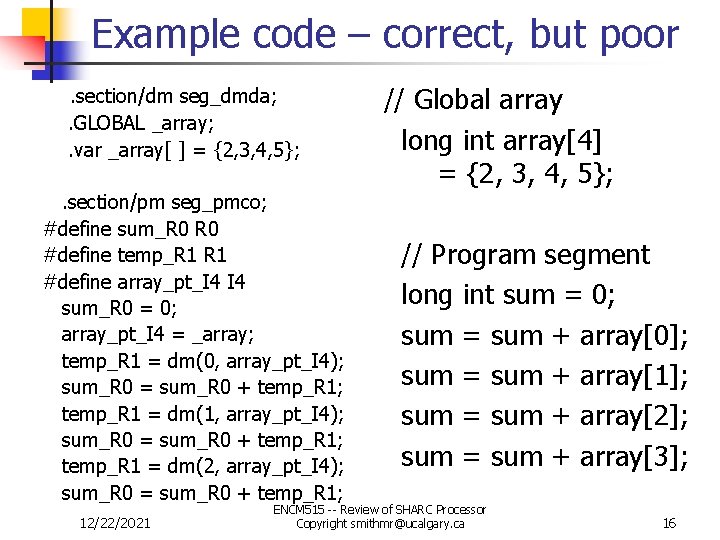

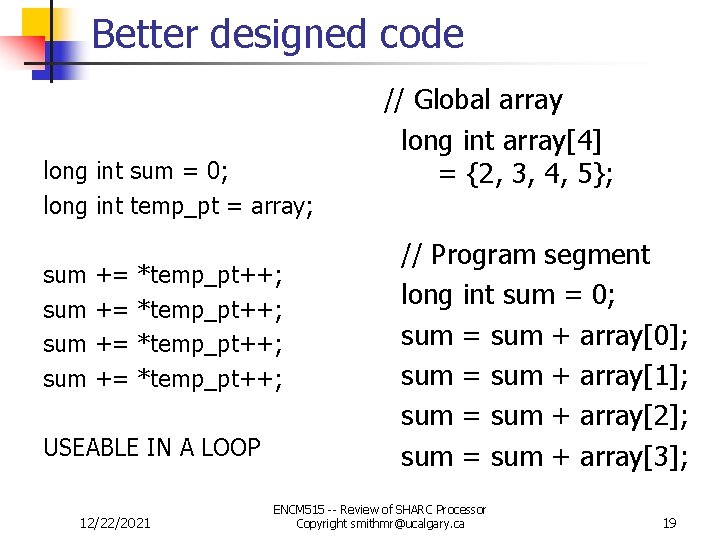

Better designed code long int sum = 0; long int temp_pt = array; sum sum += += *temp_pt++; USEABLE IN A LOOP 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 19

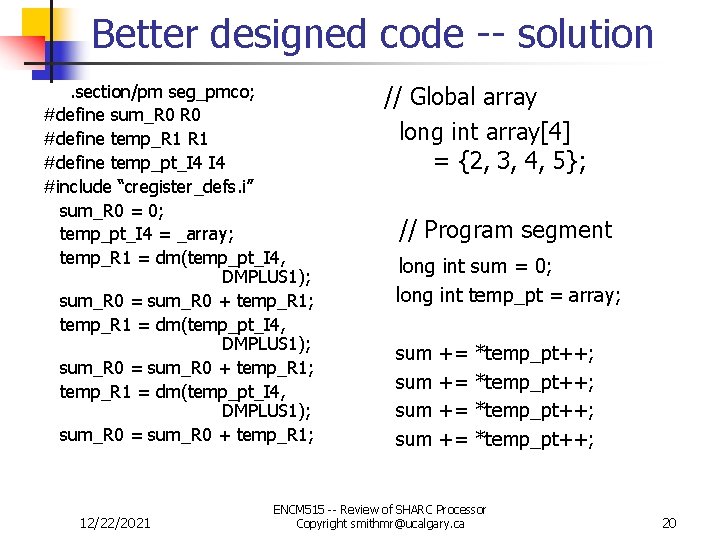

Better designed code -- solution. section/pm seg_pmco; #define sum_R 0 #define temp_R 1 #define temp_pt_I 4 #include “cregister_defs. i” sum_R 0 = 0; temp_pt_I 4 = _array; temp_R 1 = dm(temp_pt_I 4, DMPLUS 1); sum_R 0 = sum_R 0 + temp_R 1; 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; long int temp_pt = array; sum sum += += *temp_pt++; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 20

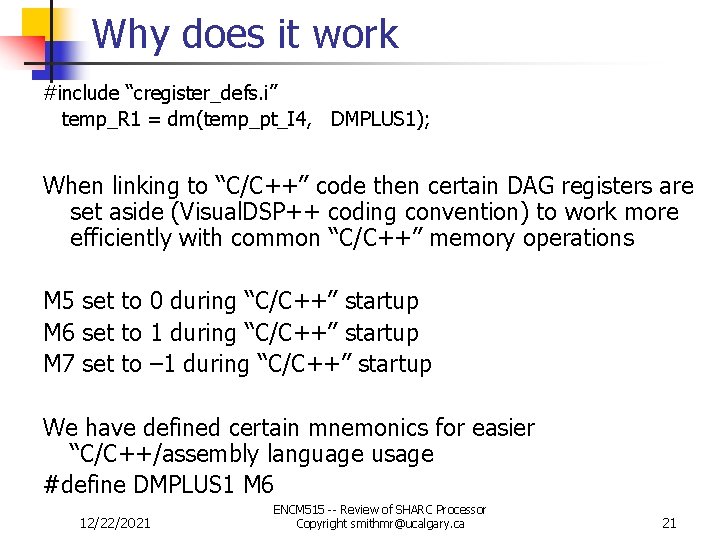

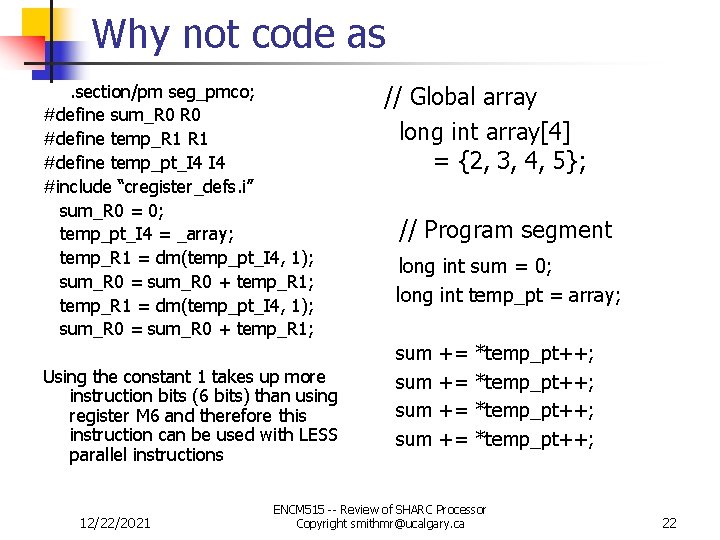

Why does it work #include “cregister_defs. i” temp_R 1 = dm(temp_pt_I 4, DMPLUS 1); When linking to “C/C++” code then certain DAG registers are set aside (Visual. DSP++ coding convention) to work more efficiently with common “C/C++” memory operations M 5 set to 0 during “C/C++” startup M 6 set to 1 during “C/C++” startup M 7 set to – 1 during “C/C++” startup We have defined certain mnemonics for easier “C/C++/assembly language usage #define DMPLUS 1 M 6 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 21

Why not code as. section/pm seg_pmco; #define sum_R 0 #define temp_R 1 #define temp_pt_I 4 #include “cregister_defs. i” sum_R 0 = 0; temp_pt_I 4 = _array; temp_R 1 = dm(temp_pt_I 4, 1); sum_R 0 = sum_R 0 + temp_R 1; Using the constant 1 takes up more instruction bits (6 bits) than using register M 6 and therefore this instruction can be used with LESS parallel instructions 12/22/2021 // Global array long int array[4] = {2, 3, 4, 5}; // Program segment long int sum = 0; long int temp_pt = array; sum sum += += *temp_pt++; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 22

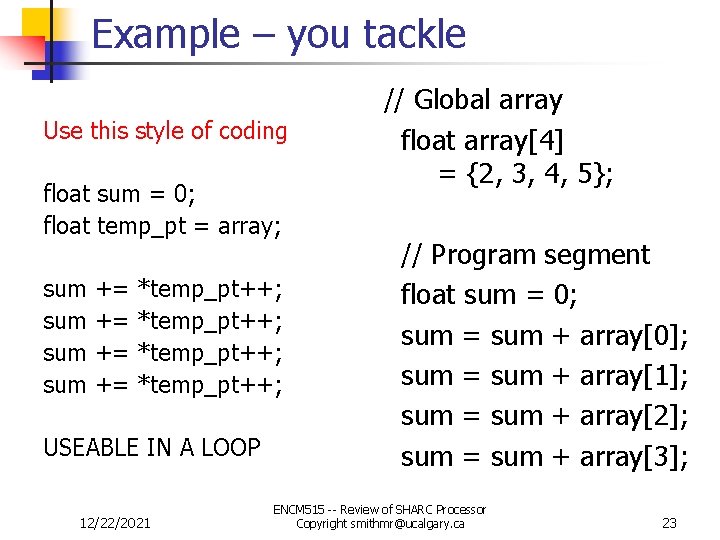

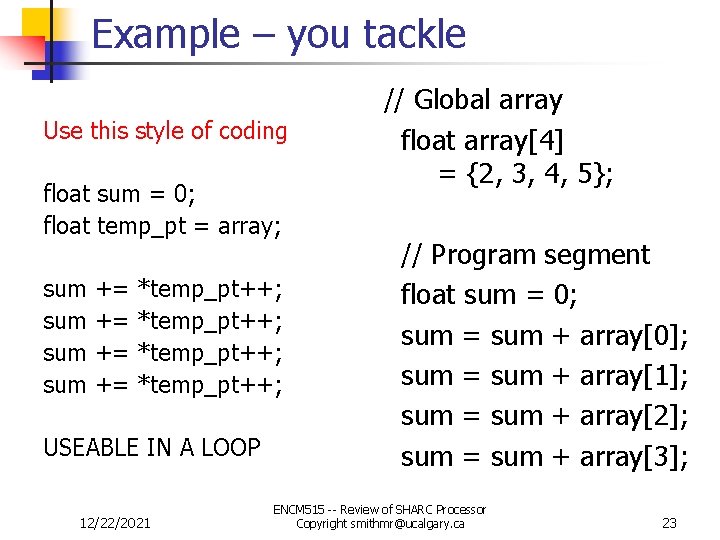

Example – you tackle Use this style of coding float sum = 0; float temp_pt = array; sum sum += += *temp_pt++; USEABLE IN A LOOP 12/22/2021 // Global array float array[4] = {2, 3, 4, 5}; // Program segment float sum = 0; sum = sum + array[0]; sum = sum + array[1]; sum = sum + array[2]; sum = sum + array[3]; ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 23

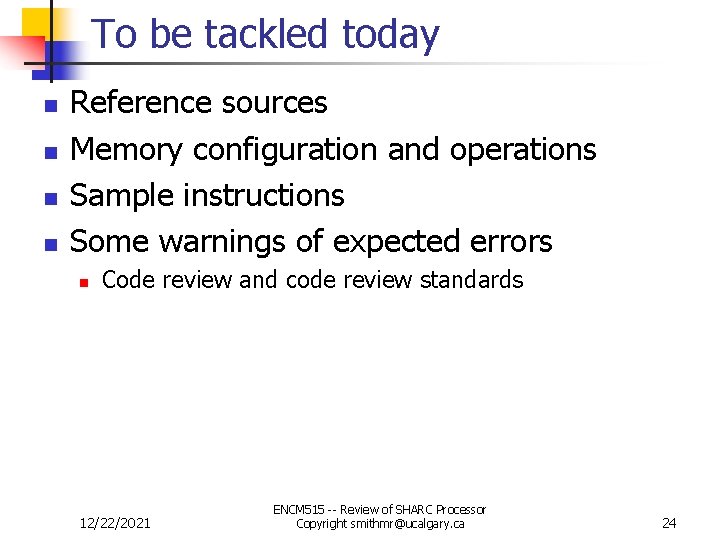

To be tackled today n n Reference sources Memory configuration and operations Sample instructions Some warnings of expected errors n Code review and code review standards 12/22/2021 ENCM 515 -- Review of SHARC Processor Copyright smithmr@ucalgary. ca 24