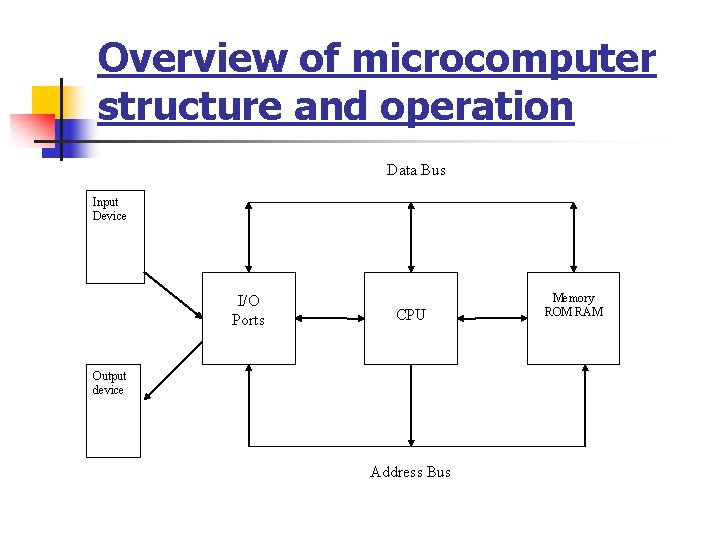

Overview of microcomputer structure and operation Data Bus

Overview of microcomputer structure and operation Data Bus Input Device I/O Ports CPU Output device Address Bus Memory ROM RAM

Major Parts: n n CPU Memory Input / Output circuitry Buses: • Address bus • Data bus • Control bus

Memory: n n n It stores the binary codes for the sequences of instructions It stores binary coded data Example: ROM, RAM, magnetic / optical disks

Input / Output: n n n They are used to take in data from outside world or send data to the outside world I/O devices are connected with microprocessor through I/O ports Example: Keyboards, video display terminals, printers, modems

Central Processing Unit: n n n It controls the operation of computer The CPU fetches binary-coded instructions from memory Decodes the instructions into a series of simple actions Carries out these actions in a sequence of steps Important components: IP, General purpose register and control bus signal generating circuits

Address Bus: n n n It consists of 16, 20, 24, 32 or 36 parallel unidirectional signal lines On these lines the CPU sends out the address of the memory location or I/O port that is to be written to or read from The number of locations that the CPU can address is determined by the number of address lines

Data Bus: Data bus consists of 8, 16, 32 parallel bidirectional signal lines n Many devices in the system will have their output connected to data bus, but only one device at a time will have its output enabled n

Control Bus: n n n The control bus consists of 4 to 10 parallel signal lines The CPU sends out signals on the control bus to enable the outputs of addressed memory devices or port devices Example of control signals: Memory read, Memory write

How to read a byte of data: n n The CPU sends the address of the desired byte on the address bus Then sends out a memory read signal on the control bus Memory read signal enables the addressed memory device to output a data word on the data bus The data word from memory travels along the data bus to the CPU

Memory Organization: n n n Processor memory Primary or main memory Secondary memory

Processor Memory: n n n It refers to the microprocessor registers which are used to hold temporary results when computation is in progress No speed disparity between these registers and microprocessor because they are fabricated using the same technology Costly

Primary Memory: n n This is the storage area in which all programs are executed The microprocessor can directly access only those items that are stored in primary memory All programs and data must be within the primary memory prior to execution Example: ROM, RAM

Secondary Memory: n n It stores program and data in excess of main memory Microprocessor can not directly execute programs which are stored in secondary memory In order to execute these programs, the microprocessor must transfer them to its main memory by a system program called operating system Example: Floppy disk, Hard disk, CD etc.

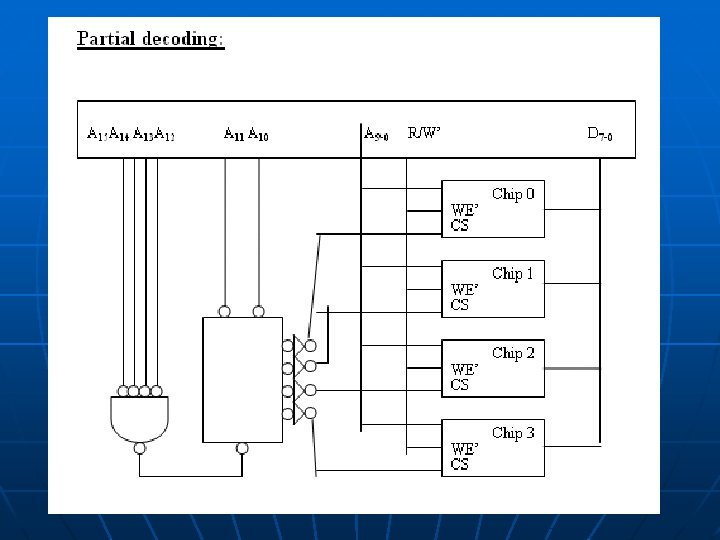

Main memory array design: Large capacity memory is realized by interconnecting several small sized memory blocks. Three techniques are frequently used. Linear decoding n Partial decoding n Full decoding n

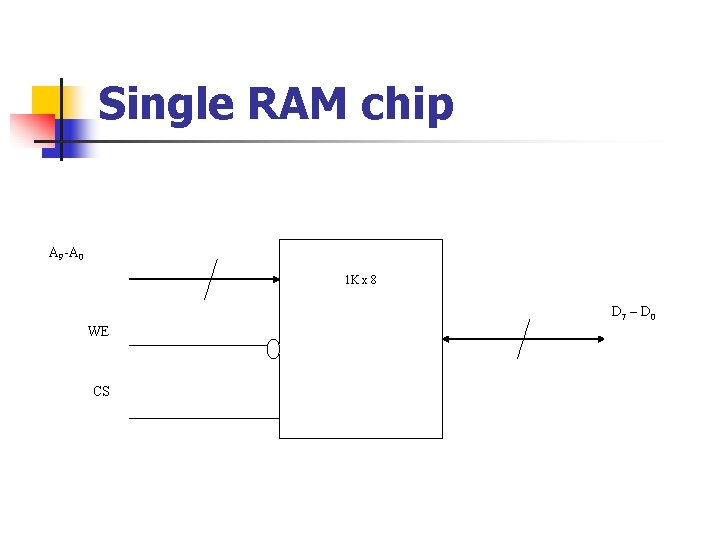

Single RAM chip A 9 -A 0 1 K x 8 D 7 – D 0 WE CS

Single RAM chip n n n Memory is organized as 1024 words with 8 bits / word. Each word has specific address and this is specified on 10 bit address lines A 9 – A 0 The inputs and outputs are routed through 8 bit bidirectional data lines The operation of this chip is governed by two control inputs WE’ (write enable) and CS (chip select)

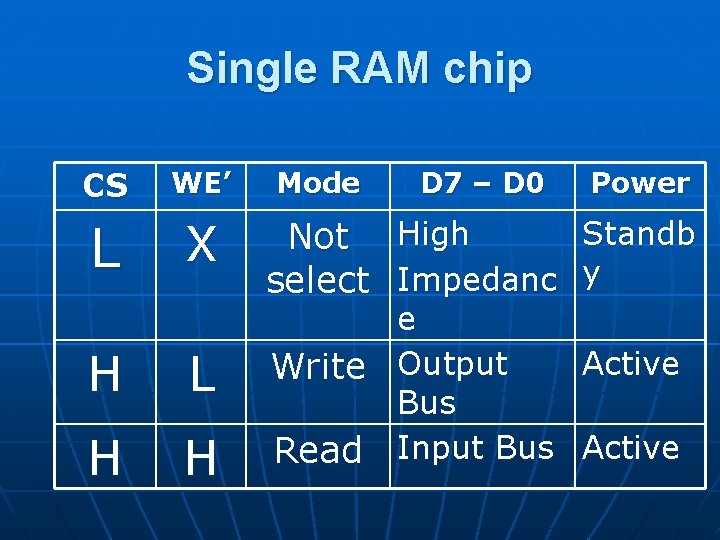

Single RAM chip CS WE’ L X H L H H Mode D 7 – D 0 Power Standb Not High select Impedanc y e Write Output Bus Read Input Bus Active

Linear decoding: n This technique uses the unused address lines of the microprocessor as chip selects for the memory chip. This method is used for small systems.

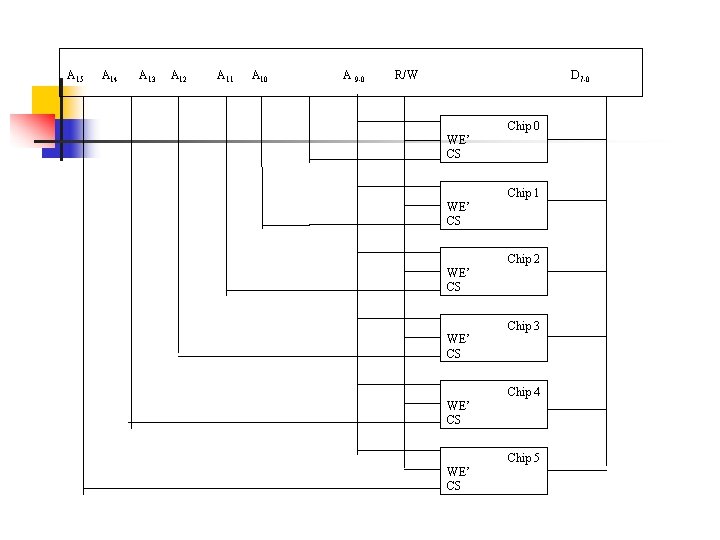

A 15 A 14 A 13 A 12 A 11 A 10 A 9 -0 R/W D 7 -0 Chip 0 WE’ CS Chip 1 WE’ CS Chip 2 WE’ CS Chip 3 WE’ CS Chip 4 WE’ CS Chip 5 WE’ CS

Disadvantage: n n Wastage of address space Address map is not contiguous Bus conflict may occur. (If more than one chips are selected at a time) Foldback (If all unused address lines are not connected as chip select)

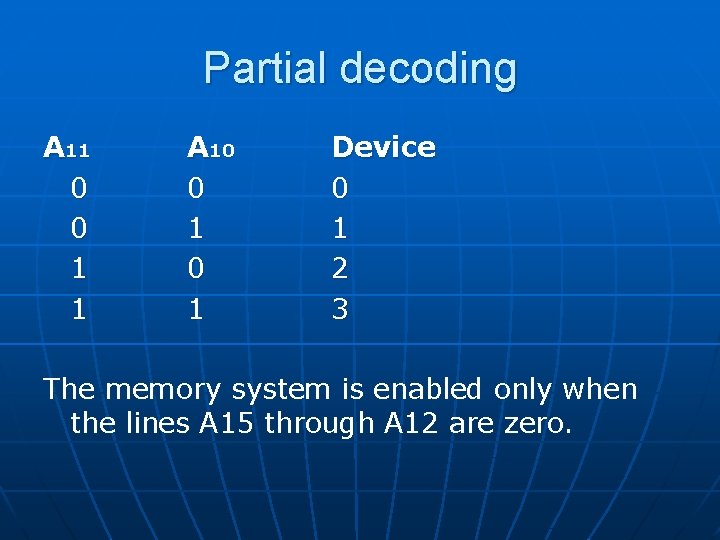

Partial decoding A 11 0 0 1 1 A 10 0 1 Device 0 1 2 3 The memory system is enabled only when the lines A 15 through A 12 are zero.

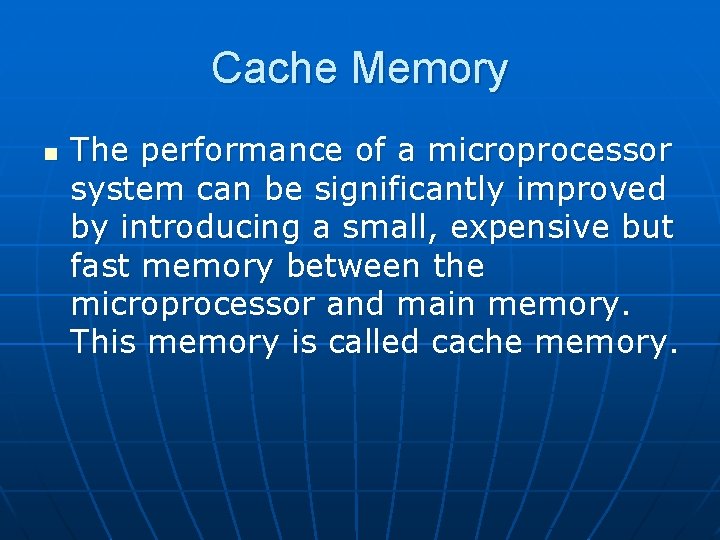

Cache Memory n The performance of a microprocessor system can be significantly improved by introducing a small, expensive but fast memory between the microprocessor and main memory. This memory is called cache memory.

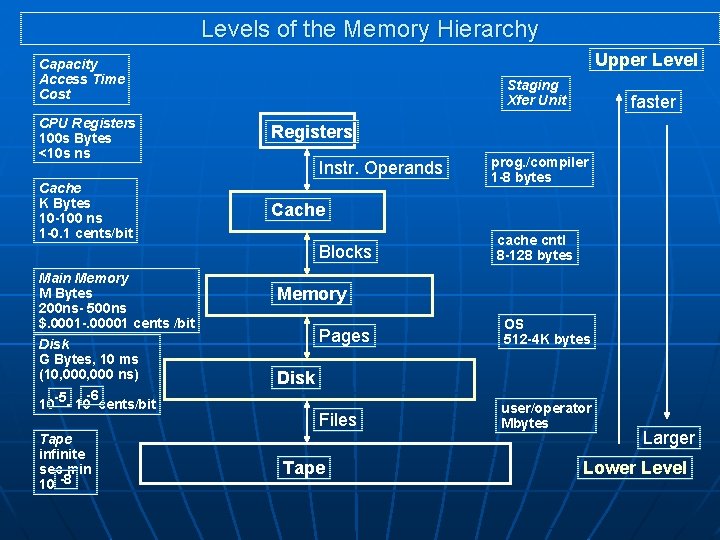

Levels of the Memory Hierarchy Upper Level Capacity Access Time Cost Staging Xfer Unit CPU Registers 100 s Bytes <10 s ns Registers Cache K Bytes 10 -100 ns 1 -0. 1 cents/bit Cache Instr. Operands Blocks Main Memory M Bytes 200 ns- 500 ns $. 0001 -. 00001 cents /bit Disk G Bytes, 10 ms (10, 000 ns) -5 -6 10 - 10 cents/bit Tape infinite sec-min 10 -8 faster prog. /compiler 1 -8 bytes cache cntl 8 -128 bytes Memory Pages OS 512 -4 K bytes Files user/operator Mbytes Disk Tape Larger Lower Level

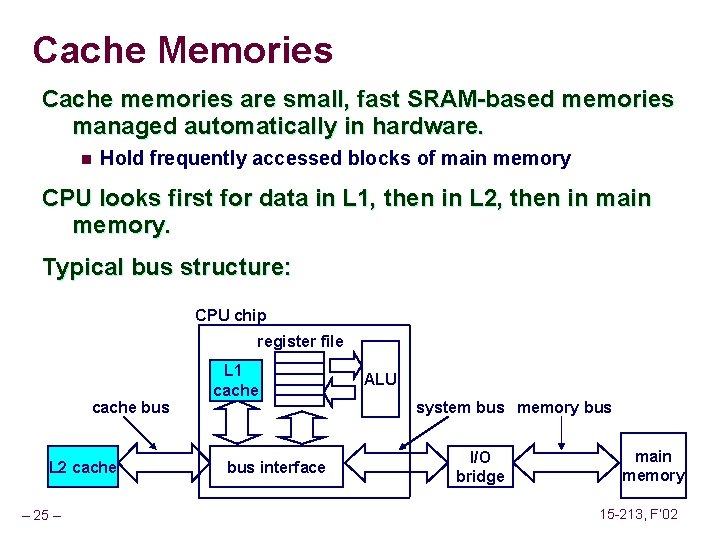

Cache Memories Cache memories are small, fast SRAM-based memories managed automatically in hardware. n Hold frequently accessed blocks of main memory CPU looks first for data in L 1, then in L 2, then in main memory. Typical bus structure: CPU chip register file cache bus L 2 cache – 25 – L 1 cache bus interface ALU system bus memory bus I/O bridge main memory 15 -213, F’ 02

Cache memory n n An on chip cache memory was first implemented in Intel 80486 microprocessor. Intel 80386 does not have any onchip cache memory but external cache memory can be interfaced.

Locality of Reference n n n A typical program spends most of its execution times in loops This means that the address generated by a microprocessor have a tendency to cluster around a small region in the main memory. This phenomenon is known as locality of reference.

Cache Hit n Cache hit means that the reference is found in the cache and the data pertaining to the microprocessor reference is transferred to the microprocessor from cache.

Cash Miss If the reference is not found in the cache, it is called Cash Miss n When there is a cache miss, the main memory is accessed by the microprocessor and the data are transferred to the microprocessor from the main memory. n

- Slides: 29