Overhead analysis of Discrete Event models execution by

Overhead analysis of Discrete Event models execution by Ezequiel Glinsky Research Assistant, University of Buenos Aires, Argentina Supervisor: Prof. Gabriel A. Wainer SCE, Carleton University ESG Seminars Thursday, November 15 th, 2001

Seminar topics will include. . . l Introduction to DEVS formalism l Performance analysis of different DEVS tools l RT-DEVS extension to the formalism l Development of enhancements (work -in-progress)

DEVS Modeling & Simulation Framework (Introduction) • DEVS = Discrete Event System Specification • Provides sound formal M&S framework • Supports full range of dynamic system representation capability • Supports hierarchical, modular model development (Zeigler, 1976/84/90/00)

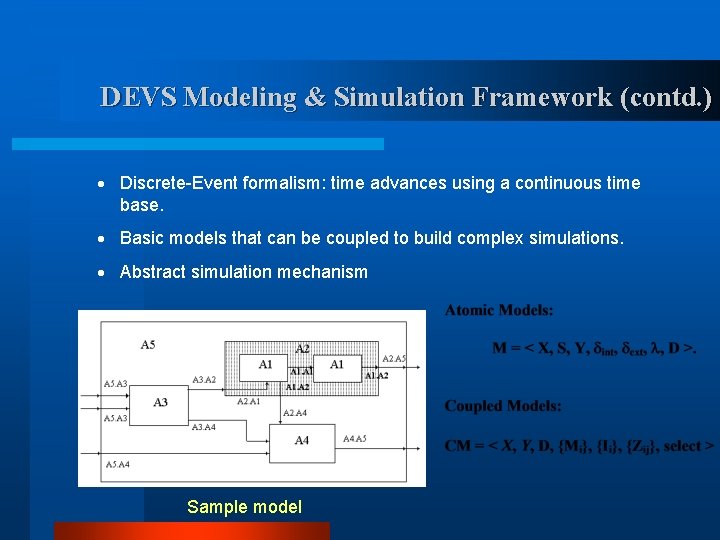

DEVS Modeling & Simulation Framework (contd. ) · Discrete-Event formalism: time advances using a continuous time base. · Basic models that can be coupled to build complex simulations. · Abstract simulation mechanism Sample model

Testing & Performance Analysis “Performance analysis of different DEVS environments” We need a synthetic model generator to represent different possible model configurations Why do we need a Model Generator? l Detect bottlenecks l Characterize tool’s overhead l Test automatically and thoroughly l Appreciate current overhead and therefore consider the possibility of RT simulation execution

A model generator (contd. ) Available parameters: l Depth l Width l Dhrystone code in transition functions l Model type

A model generator (contd. ) Available parameters: l Depth l Width l Dhrystone code in transition functions l Model type Number of levels of the modeling hierarchy.

A model generator (contd. ) Available parameters: l Depth l Width l Dhrystone code in transition functions l Model type Number of children belonging to each intermediate coupled component.

A model generator (contd. ) Available parameters: l Depth l Width l Dhrystone code in transition functions l Model type Allows us to execute time-consuming code inside both the internal and external transition functions.

A model generator (contd. ) Available parameters: l Depth l Width l Dhrystone code in transition functions l Model type Different types of models can be generated, with different behavior, coupling and interconnections.

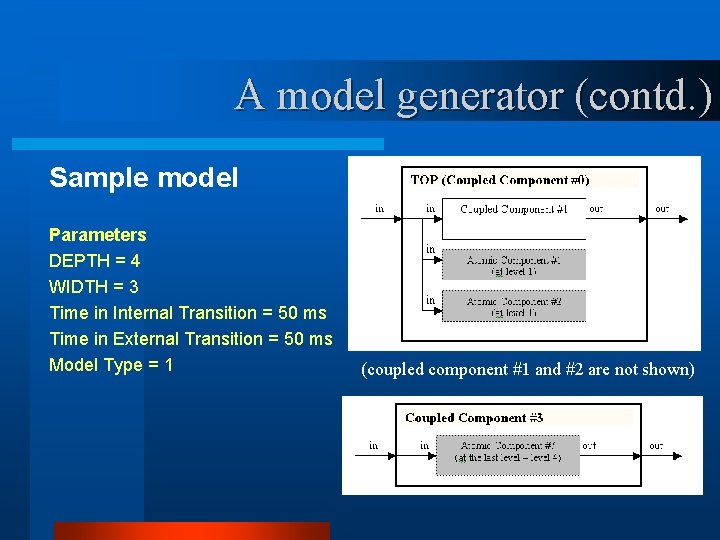

A model generator (contd. ) Sample model Parameters DEPTH = 4 WIDTH = 3 Time in Internal Transition = 50 ms Time in External Transition = 50 ms Model Type = 1 (coupled component #1 and #2 are not shown)

Testing & Performance Analysis Available environments: Original CD++ simulator l Parallel CD++ with No. Time kernel l Parallel CD++ with Time. Warp kernel l Real-Time CD++ l

Testing & Performance Analysis Available environments: Original CD++ simulator l Parallel CD++ with No. Time kernel l Parallel CD++ with Time. Warp kernel l Real-Time CD++ l Only provides stand-alone simulation. Doesn’t need to relay on any intermediate layer.

Testing & Performance Analysis Available environments: Original CD++ simulator l Parallel CD++ with No. Time kernel l Parallel CD++ with Time. Warp kernel l Real-Time CD++ l Uses a middle-ware to allow parallel simulation. No. Time: Unsynchronized kernel

Testing & Performance Analysis Available environments: Original CD++ simulator l Parallel CD++ with No. Time kernel l Parallel CD++ with Time. Warp kernel l Real-Time CD++ l Uses a middle-ware to allow parallel simulation. Time. Warp: Optimistic approach

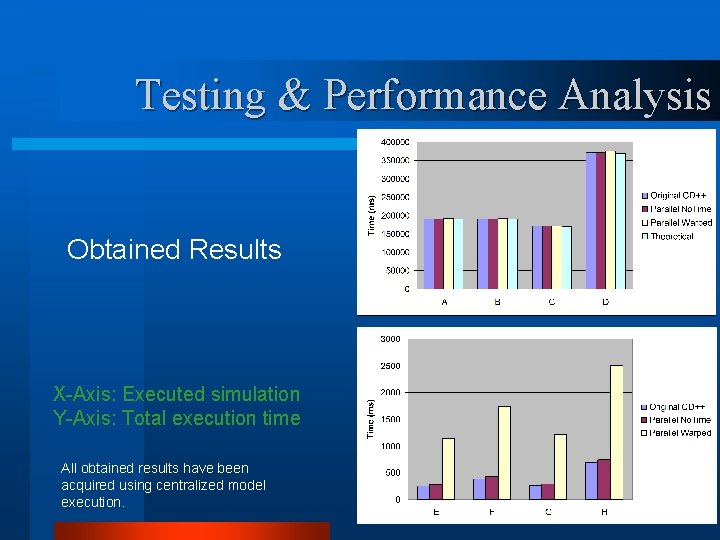

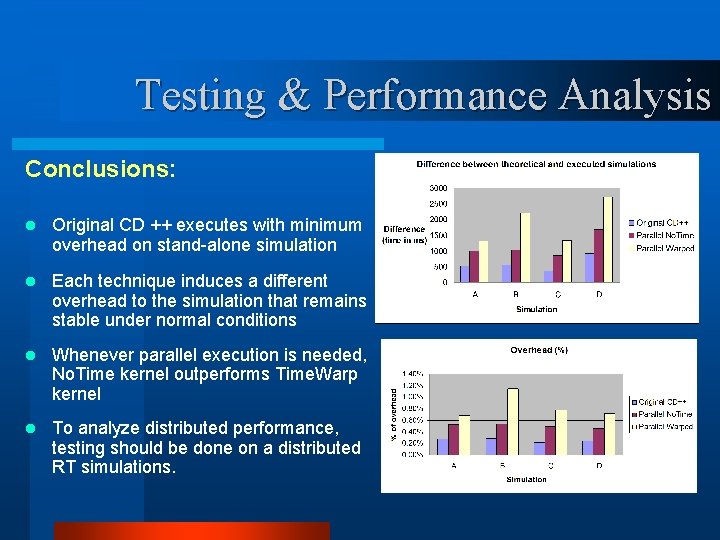

Testing & Performance Analysis Obtained Results X-Axis: Executed simulation Y-Axis: Total execution time All obtained results have been acquired using centralized model execution.

Testing & Performance Analysis Conclusions: l Original CD ++ executes with minimum overhead on stand-alone simulation l Each technique induces a different overhead to the simulation that remains stable under normal conditions l Whenever parallel execution is needed, No. Time kernel outperforms Time. Warp kernel l To analyze distributed performance, testing should be done on a distributed RT simulations.

Real-time DEVS (RT-DEVS) What is RT-DEVS? l RT-DEVS is an extension to the DEVS formalism Why do we need RTDEVS? To run models interacting in a real-time environment l To study real-time performance with the designed models l

RT-DEVS (contd. ) Main differences between usual approach and RT-DEVS Usual approach Time is not linked to a clock at all. Instead, virtual time is used (logical clock). l No timing constraints l RT-DEVS Time advance is linked to the wall-clock all along the simulation. ² Timing constraints are checked against the wallclock on some given checkpoints ²

RT-DEVS (contd. ) What do we measure when executing RTDEVS? Why? Worst-case response time l # of missed deadlines l Besides. . . – log provides detailed information about the message passing – output results show most important timing information briefly: (wall-clock time, deadline, port, output value)

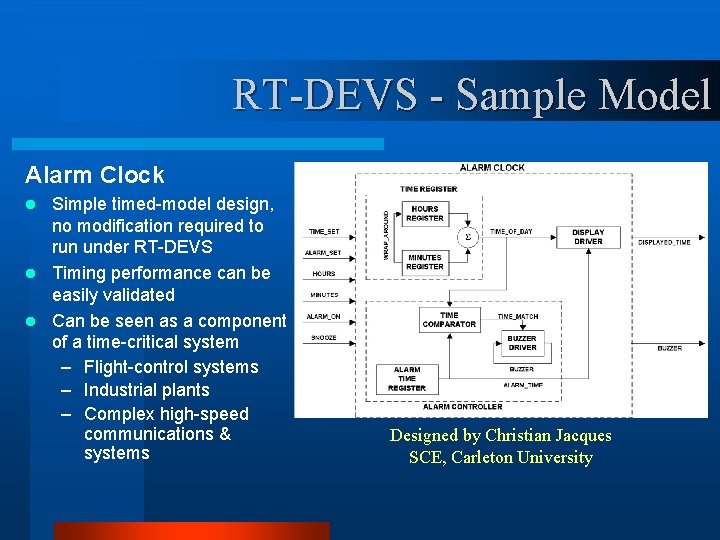

RT-DEVS - Sample Model Alarm Clock Simple timed-model design, no modification required to run under RT-DEVS l Timing performance can be easily validated l Can be seen as a component of a time-critical system – Flight-control systems – Industrial plants – Complex high-speed communications & systems l Designed by Christian Jacques SCE, Carleton University

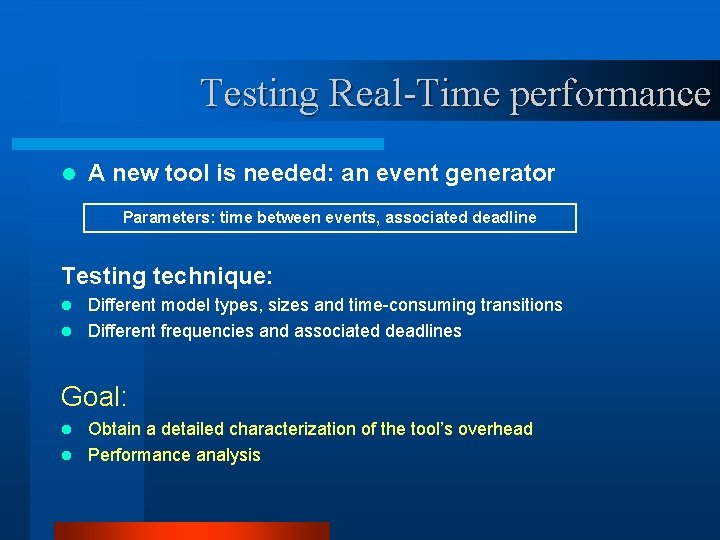

Testing Real-Time performance l A new tool is needed: an event generator Parameters: time between events, associated deadline Testing technique: Different model types, sizes and time-consuming transitions l Different frequencies and associated deadlines l Goal: Obtain a detailed characterization of the tool’s overhead l Performance analysis l

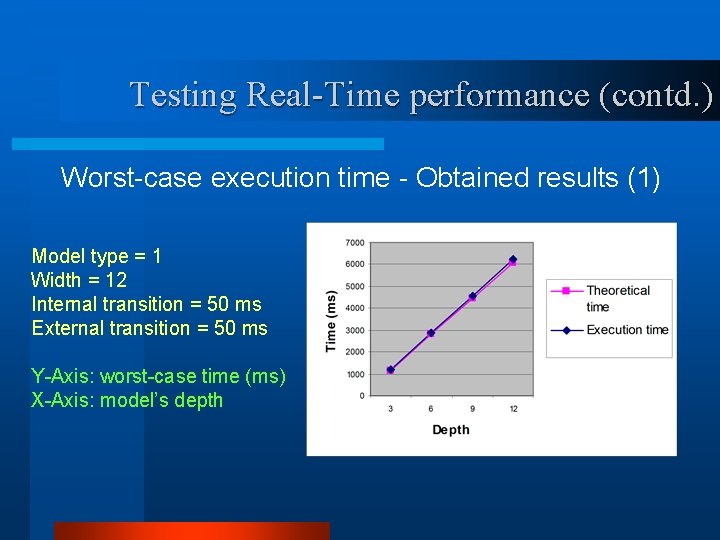

Testing Real-Time performance (contd. ) Worst-case execution time - Obtained results (1) Model type = 1 Width = 12 Internal transition = 50 ms External transition = 50 ms Y-Axis: worst-case time (ms) X-Axis: model’s depth

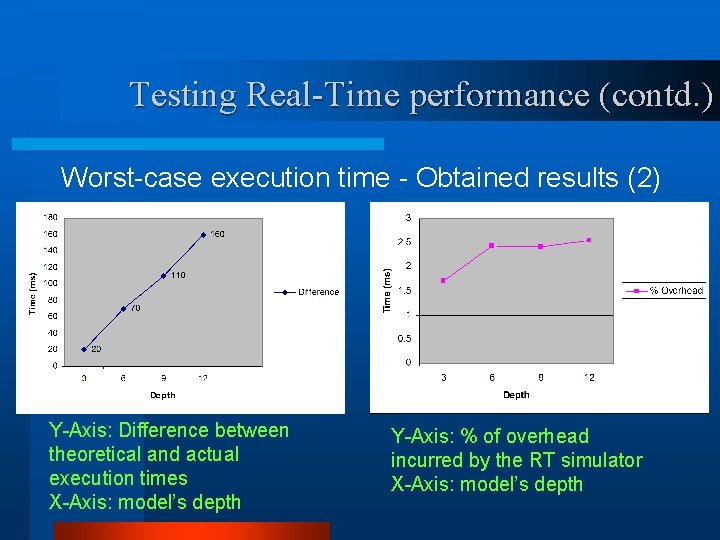

Testing Real-Time performance (contd. ) Worst-case execution time - Obtained results (2) Y-Axis: Difference between theoretical and actual execution times X-Axis: model’s depth Y-Axis: % of overhead incurred by the RT simulator X-Axis: model’s depth

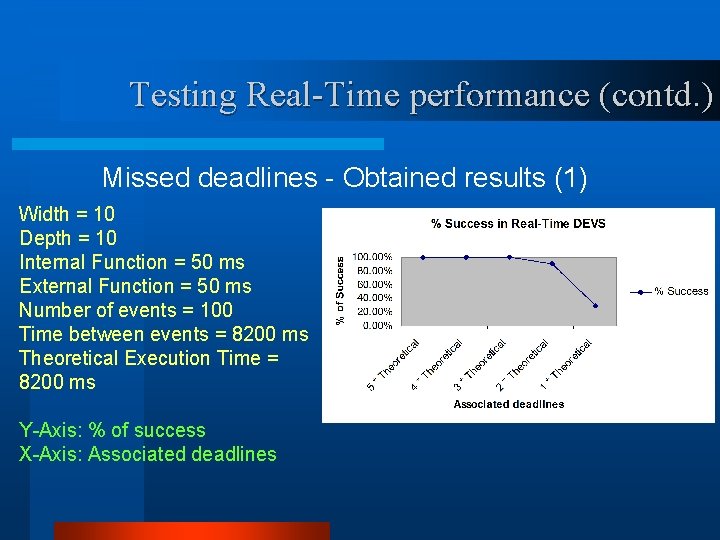

Testing Real-Time performance (contd. ) Missed deadlines - Obtained results (1) Width = 10 Depth = 10 Internal Function = 50 ms External Function = 50 ms Number of events = 100 Time between events = 8200 ms Theoretical Execution Time = 8200 ms Y-Axis: % of success X-Axis: Associated deadlines

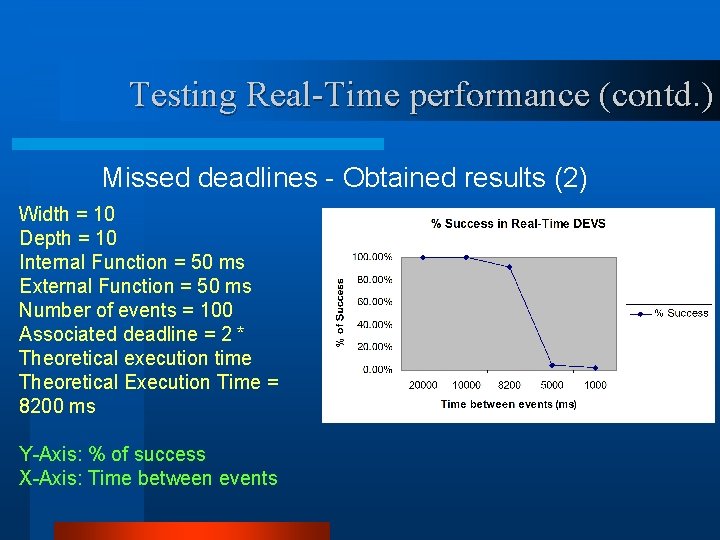

Testing Real-Time performance (contd. ) Missed deadlines - Obtained results (2) Width = 10 Depth = 10 Internal Function = 50 ms External Function = 50 ms Number of events = 100 Associated deadline = 2 * Theoretical execution time Theoretical Execution Time = 8200 ms Y-Axis: % of success X-Axis: Time between events

Testing Real-Time performance (contd. ) Conclusions Increasing complexity Increasing response times l Nevertheless, percentages of overhead remains nearly stable simulations can be carried out properly l Bottom line: After thorough testing, we can say the real-time simulator is able to execute simulations properly even under difficult conditions (high workload and mid to large-scale models)

Flattened Simulator Why do we need a flattened simulator? To increase tool’s performance and simulate successfully even more complex models with higher workload (Work-in-progress)

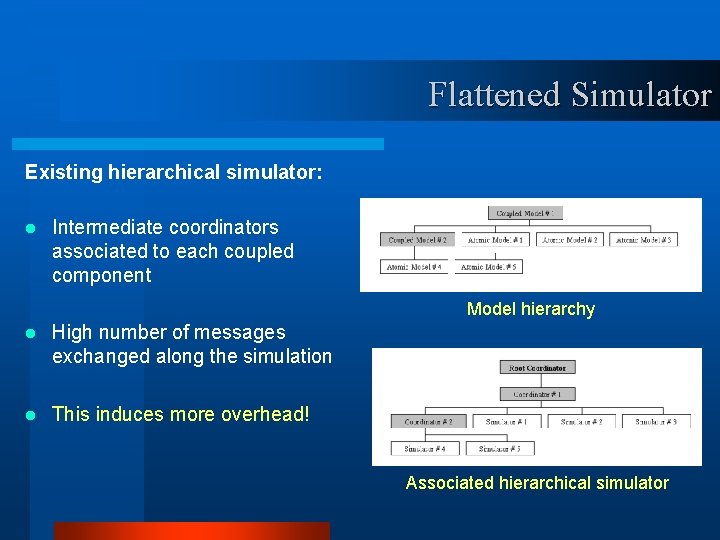

Flattened Simulator Existing hierarchical simulator: l Intermediate coordinators associated to each coupled component Model hierarchy l High number of messages exchanged along the simulation l This induces more overhead! Associated hierarchical simulator

Flattened Simulator Proposed flattened simulator: l Must keep separation between model and actual simulator l Reduce number of intermediate coordinators l Simplify hierarchy and reduced message exchange along the simulation l Less overhead expected!

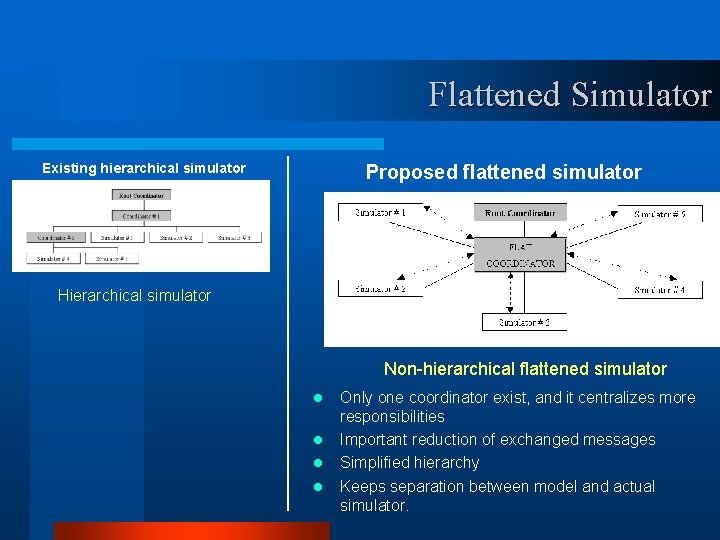

Flattened Simulator Existing hierarchical simulator Proposed flattened simulator Hierarchical simulator Non-hierarchical flattened simulator l l Only one coordinator exist, and it centralizes more responsibilities Important reduction of exchanged messages Simplified hierarchy Keeps separation between model and actual simulator.

Further work Finish the Flattened simulator’s design and development l Execute overhead and performance analysis using the new flattened simulator l More information: http: //www. sce. carleton. ca/faculty/wainer/wbgraf/index. html

Overhead analysis of Discrete Event models execution Questions? by Ezequiel Glinsky Research Assistant, University of Buenos Aires, Argentina Thursday, November 15 th, 2001 Supervisor: Prof. Gabriel A. Wainer SCE, Carleton University

- Slides: 33