Overcoming the Gap Between Design at Electronic System

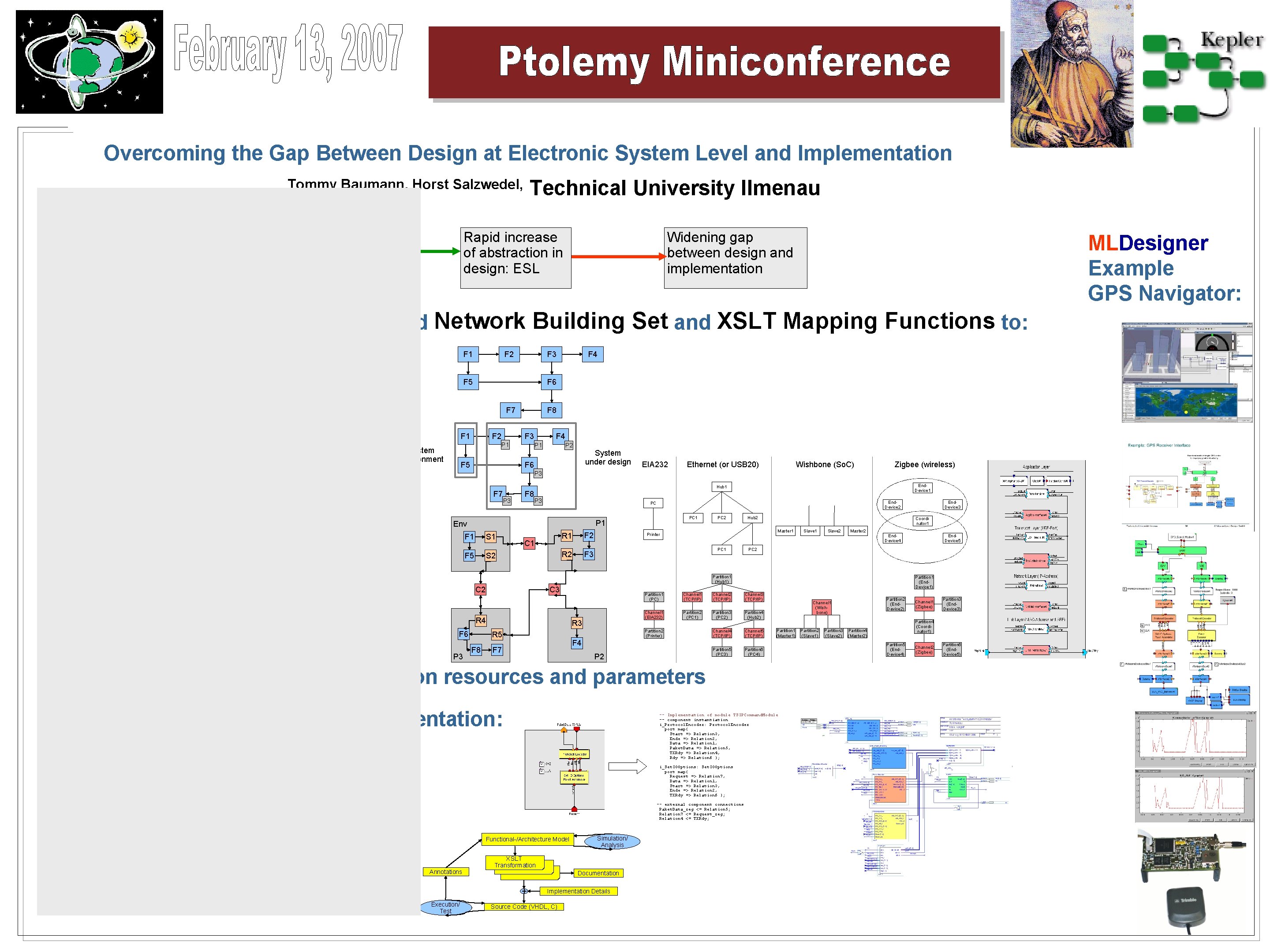

Overcoming the Gap Between Design at Electronic System Level and Implementation Technical University Ilmenau Tommy Baumann, Horst Salzwedel, The Problem: Exponentially rising system complexity Rapid increase of abstraction in design: ESL Widening gap between design and implementation MLDesigner Example GPS Navigator: The Solution: Develop standardized Network Building Set and XSLT Mapping Functions to: (1) Create Beahavioral Model: F 1 F 2 F 3 F 5 F 6 F 7 (2) Annotate Behavioral Model: F 1 F 2 F 8 F 3 F 4 P 1 System environment F 4 F 5 P 1 P 2 System under design F 6 EIA 232 Ethernet (or USB 20) Wishbone (So. C) Zigbee (wireless) P 3 End. Device 1 Hub 1 F 7 (3) Map into Architecture: P 3 F 8 P 3 End. Device 2 PC PC 1 P 1 Env F 1 S 1 F 5 C 1 S 2 R 1 F 2 R 2 F 3 PC 2 Hub 2 Coordinator 1 Master 1 Printer PC 1 Slave 2 Master 2 End. Device 4 C 3 R 4 F 6 P 3 R 3 F 8 Channel 1 (TCP/IP) Channel 2 (TCP/IP) Channel 3 (TCP/IP) Channel 1 (EIA 232) Partition 2 (PC 1) Partition 3 (PC 2) Partition 4 (Hub 2) Channel 4 (TCP/IP) Channel 5 (TCP/IP) Partition 5 (PC 3) Partition 6 (PC 4) F 4 F 7 Partition 1 (End. Device 1) Partition 1 (PC) Partition 2 (Printer) R 5 P 2 Partition 1 (Master 1) -- Implementation of module TSIPCommand. Module -- component instantiation i_Protocol. Encoder: Protocol. Encoder port map( Start => Relation 3, Ende => Relation 2, Data => Relation 1, Paket. Data => Relation 5, TXRdy => Relation 4, Rdy => Relation 6 ); i_Set. IOOptions: Set. IOOptions port map( Request => Relation 7, Data => Relation 1, Start => Relation 3, Ende => Relation 2, TXRdy => Relation 6 ); -- external component connections Paket. Data_reg <= Relation 5; Relation 7 <= Request_reg; Relation 4 <= TXRdy; (6) Test and validate prototype: Functional-/Architecture Model Annotations XSLT Transformation Documentation + Execution/ Test Simulation/ Analysis Implementation Details Source Code (VHDL, C) Partition 2 (End. Device 2) Channel 1 (Wishbone) (4) Performance analysis: Iterate on resources and parameters (5) Synthesize model into implementation: End. Device 5 PC 2 Partition 1 (Hub 1) C 2 End. Device 3 Partition 2 (Slave 1) Partition 3 (Slave 2) Channel 1 (Zigbee) Partition 3 (End. Device 3) Partition 4 (Coordinator 1) Partition 4 (Master 2) Partition 5 (End. Device 4) Channel 2 (Zigbee) Partition 6 (End. Device 5)

- Slides: 1