Over Voltage Protection Module for Power Supply System

![Over. Voltage Protection control 6 input bits of the multiplexer address A[5: 0]; 1 Over. Voltage Protection control 6 input bits of the multiplexer address A[5: 0]; 1](https://slidetodoc.com/presentation_image_h2/bc9aead4cd563736f345027b837861ed/image-20.jpg)

- Slides: 32

Over. Voltage Protection Module for Power Supply System - overview – functionality main components architecture of OVP module communication with MCU (microcontroller) summary – time schedule 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 1

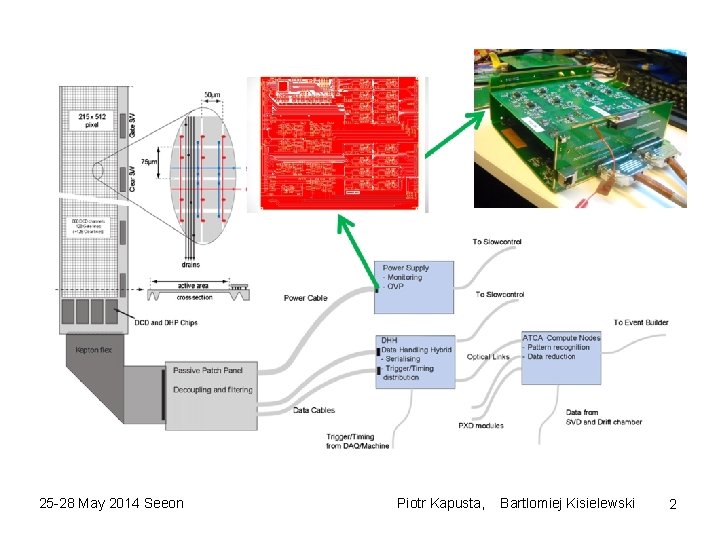

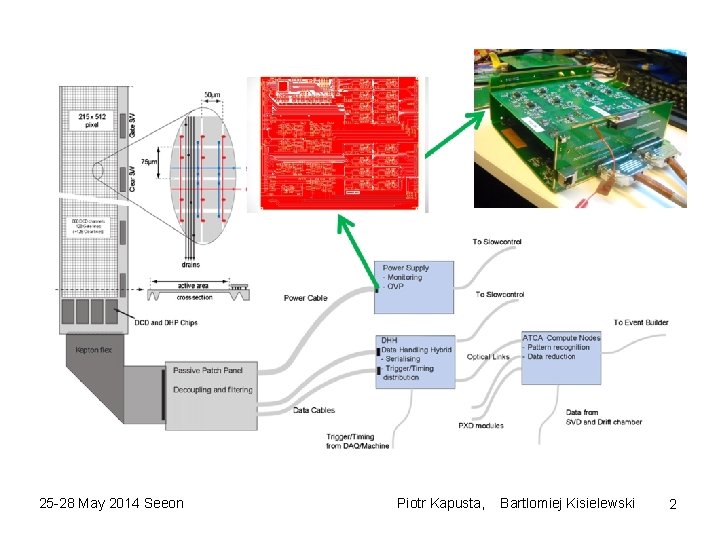

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 2

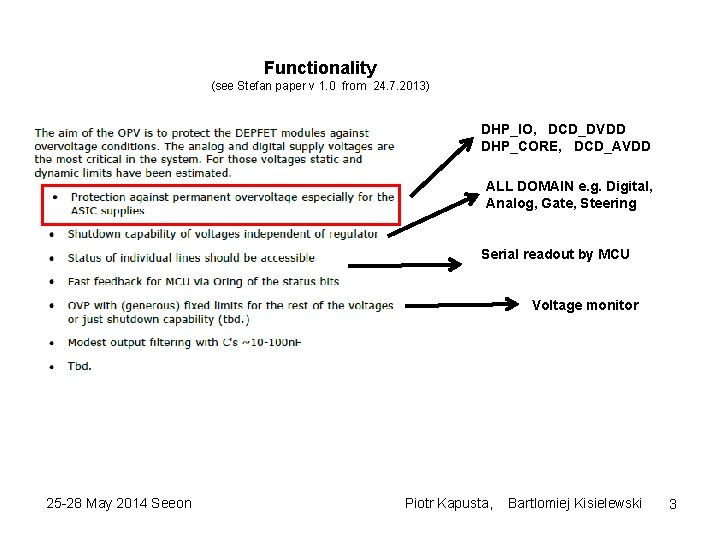

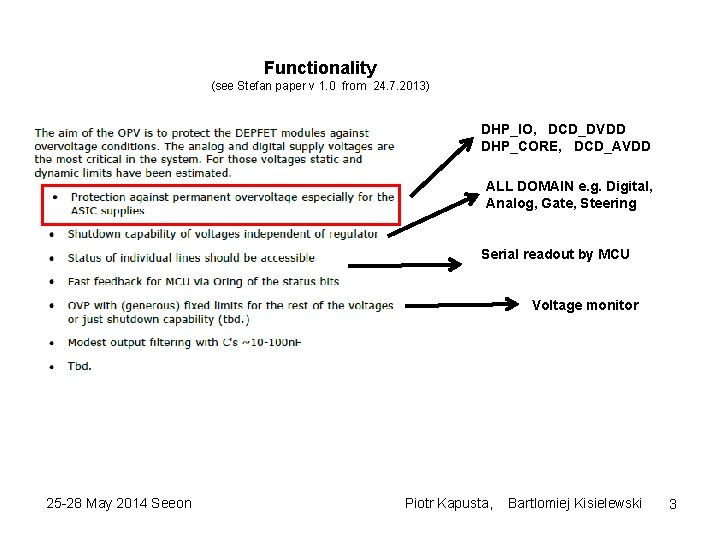

Functionality (see Stefan paper v 1. 0 from 24. 7. 2013) DHP_IO, DCD_DVDD DHP_CORE, DCD_AVDD ALL DOMAIN e. g. Digital, Analog, Gate, Steering Serial readout by MCU Voltage monitor 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 3

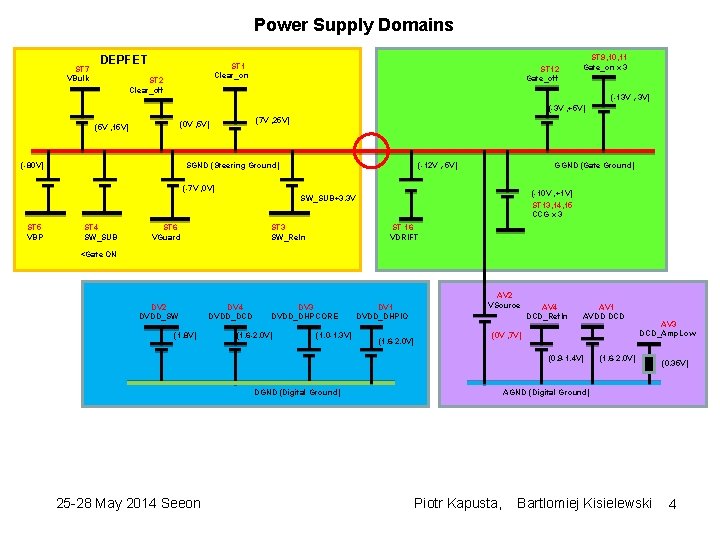

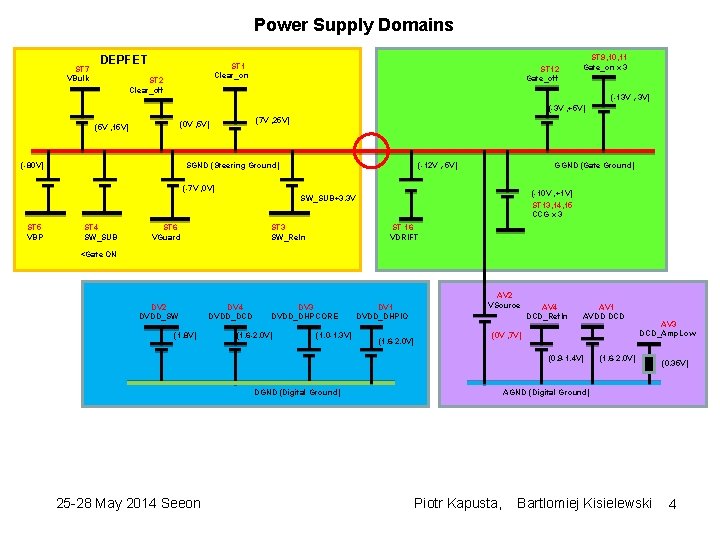

Power Supply Domains ST 7 VBulk DEPFET ST 1 Clear_on ST 2 Clear_off ST 12 Gate_off ST 9, 10, 11 Gate_on x 3 (-13 V , -3 V) (-3 V , +5 V) (7 V , 25 V) (0 V , 5 V) (5 V , 15 V) (-80 V) SGND (Steering Ground) (-12 V , -5 V) GGND (Gate Ground) (-7 V , 0 V) (-10 V , +1 V) ST 13, 14, 15 CCG x 3 SW_SUB+3. 3 V ST 5 VBP ST 4 SW_SUB ST 6 VGuard ST 3 SW_Re. In ST 16 VDRIFT <Gate ON DV 2 DVDD_SW (1. 8 V) DV 4 DVDD_DCD DV 3 DVDD_DHPCORE (1. 6 -2. 0 V) (1. 0 -1. 3 V) DV 1 DVDD_DHPIO (1. 6 -2. 0 V) AV 2 VSource AV 4 DCD_Ref. In AV 1 AVDD DCD (0 V , 7 V) (0. 9 -1. 4 V) DGND (Digital Ground) 25 -28 May 2014 Seeon AV 3 DCD_Amp. Low (1. 6 -2. 0 V) (0. 35 V) AGND (Digital Ground) Piotr Kapusta, Bartlomiej Kisielewski 4

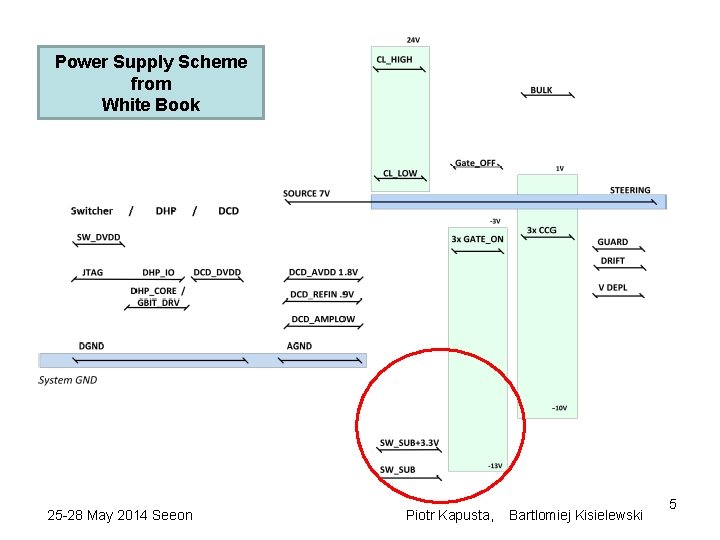

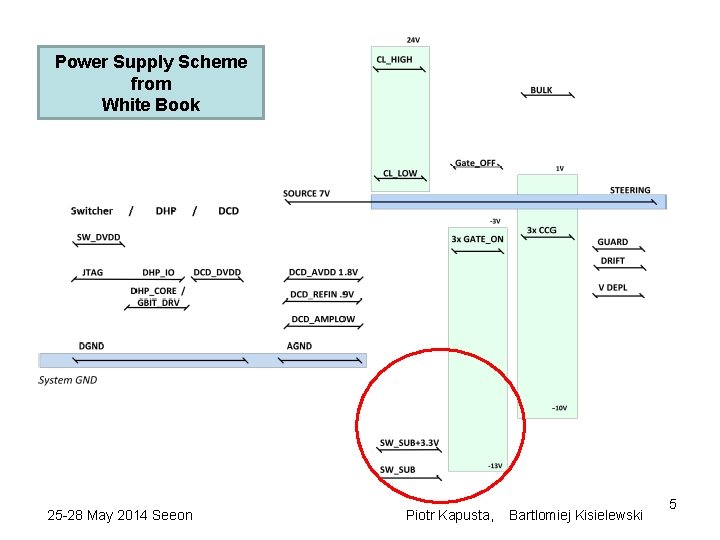

Power Supply Scheme from White Book 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 5

All voltages will be fixed by resistor networks !!! OVP range > nominal range Gate Domain Digital Domain 25 -28 May 2014 Seeon Piotr Kapusta, 6 Bartlomiej Kisielewski

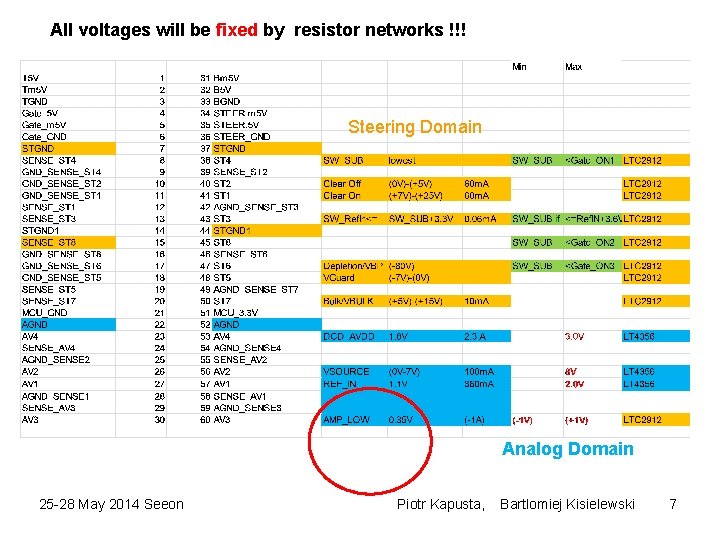

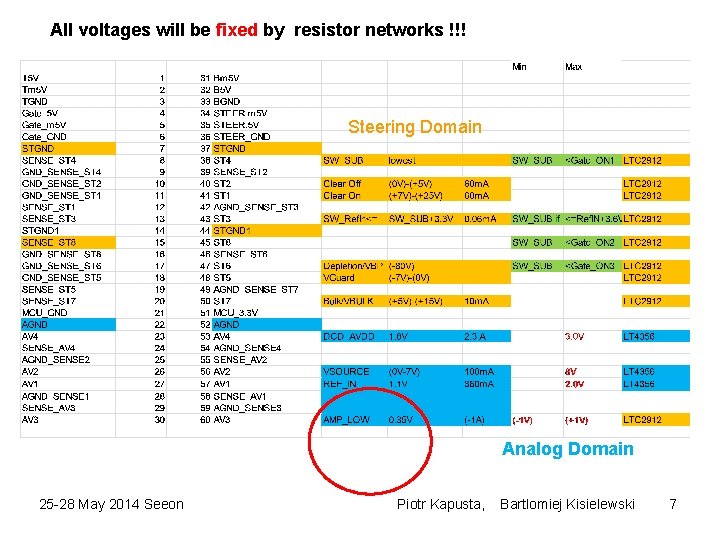

All voltages will be fixed by resistor networks !!! Steering Domain Analog Domain 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 7

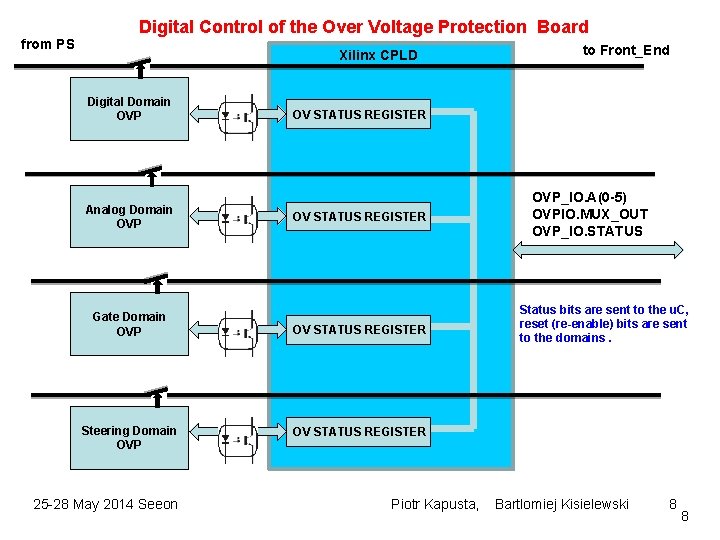

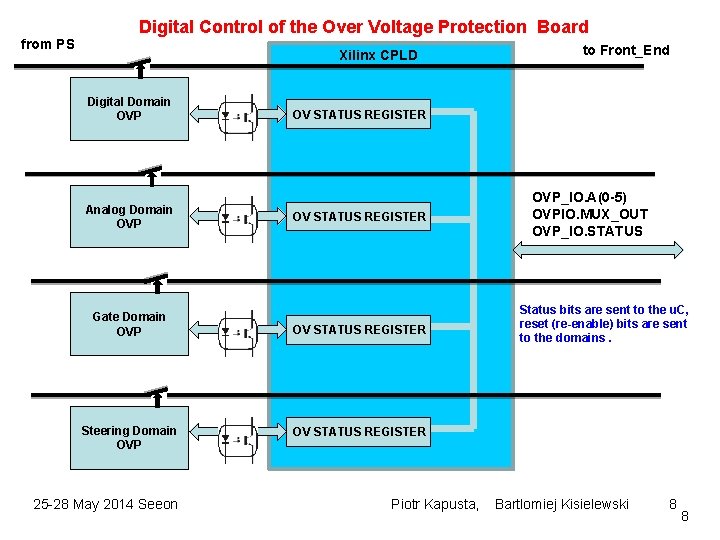

from PS Digital Control of the Over Voltage Protection Board Xilinx CPLD Digital Domain OVP Analog Domain OVP OV STATUS REGISTER Gate Domain OVP OV STATUS REGISTER Steering Domain OVP OV STATUS REGISTER 25 -28 May 2014 Seeon to Front_End Piotr Kapusta, OVP_IO. A(0 -5) OVPIO. MUX_OUT OVP_IO. STATUS Status bits are sent to the u. C, reset (re-enable) bits are sent to the domains. Bartlomiej Kisielewski 8 8

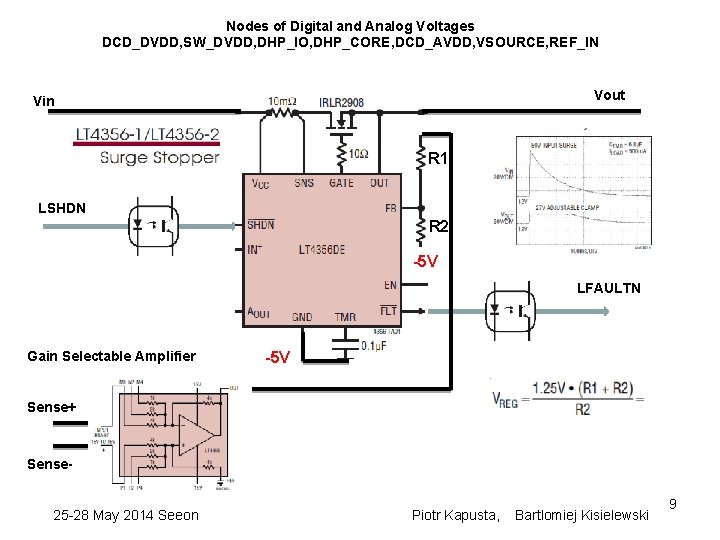

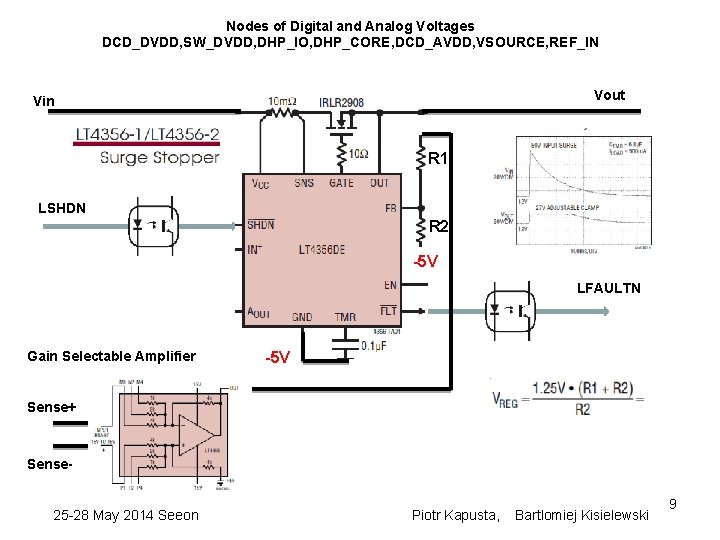

Nodes of Digital and Analog Voltages DCD_DVDD, SW_DVDD, DHP_IO, DHP_CORE, DCD_AVDD, VSOURCE, REF_IN Vout Vin R 1 LSHDN R 2 -5 V LFAULTN Gain Selectable Amplifier -5 V Sense+ Sense- 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 9

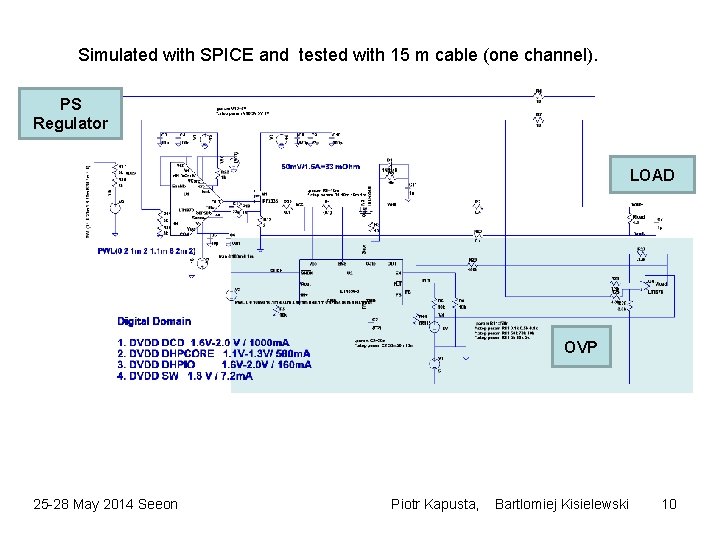

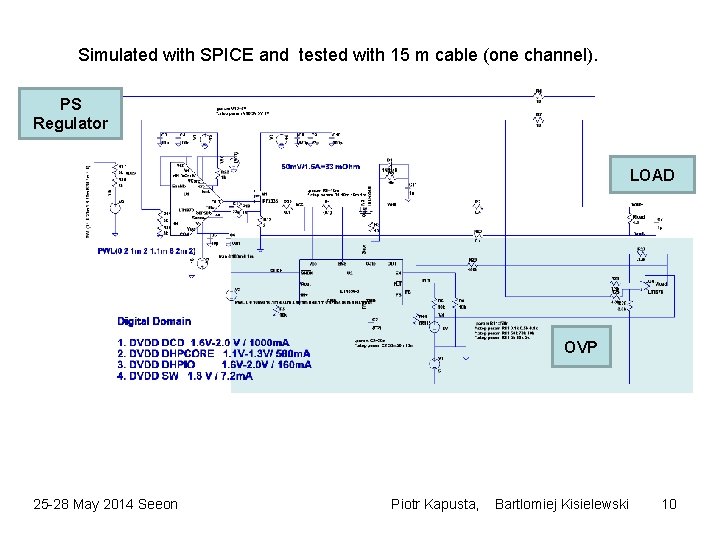

Simulated with SPICE and tested with 15 m cable (one channel). PS Regulator LOAD OVP 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 10

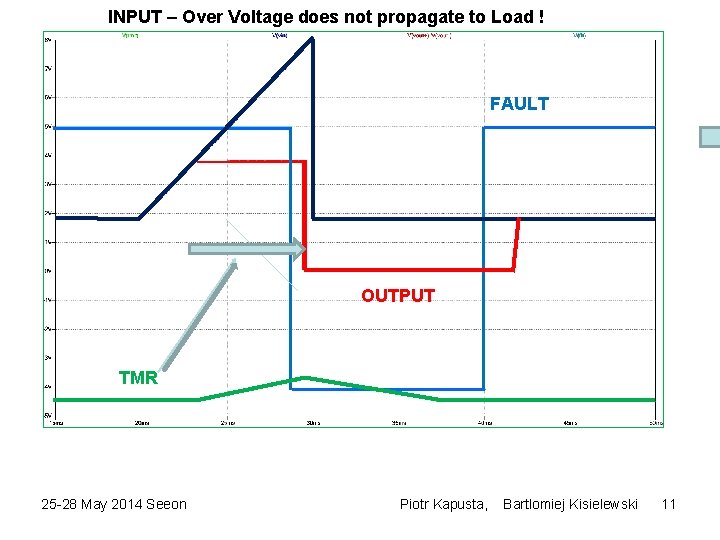

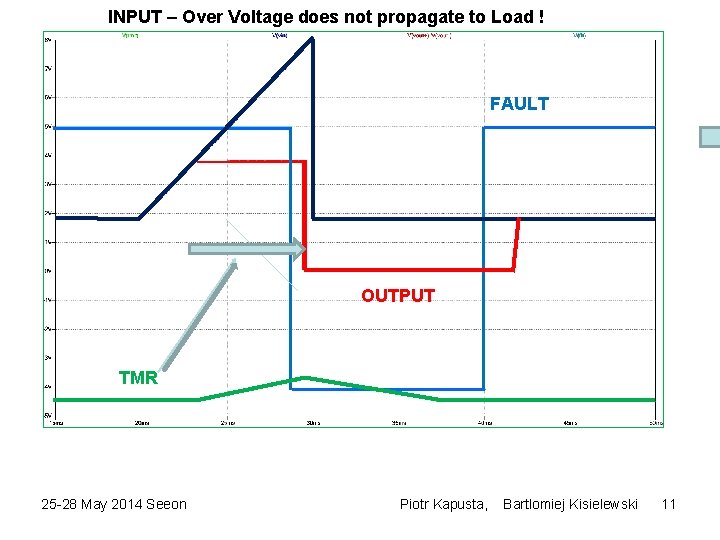

INPUT – Over Voltage does not propagate to Load ! FAULT OUTPUT TMR 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 11

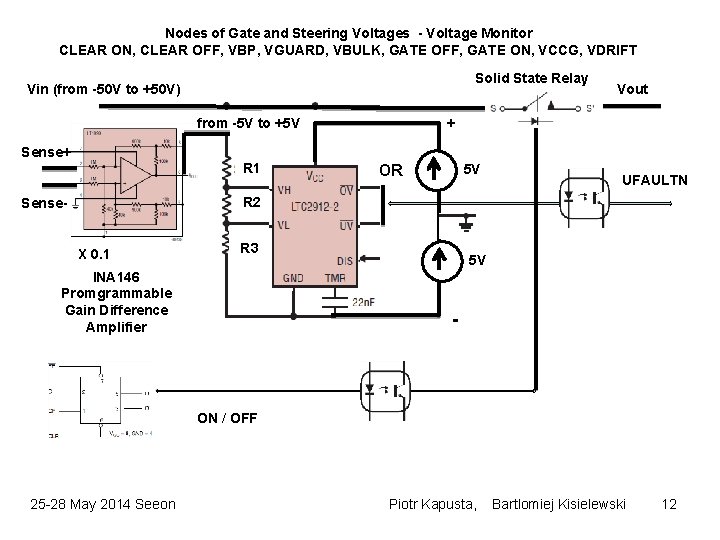

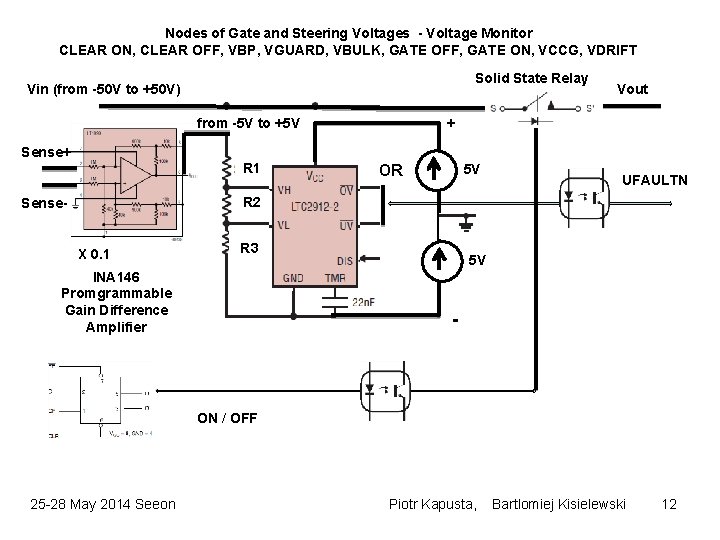

Nodes of Gate and Steering Voltages - Voltage Monitor CLEAR ON, CLEAR OFF, VBP, VGUARD, VBULK, GATE OFF, GATE ON, VCCG, VDRIFT Solid State Relay Vin (from -50 V to +50 V) from -5 V to +5 V Vout + Sense+ R 1 5 V OR UFAULTN R 2 Sense- X 0. 1 R 3 INA 146 Promgrammable Gain Difference Amplifier 5 V - ON / OFF 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 12

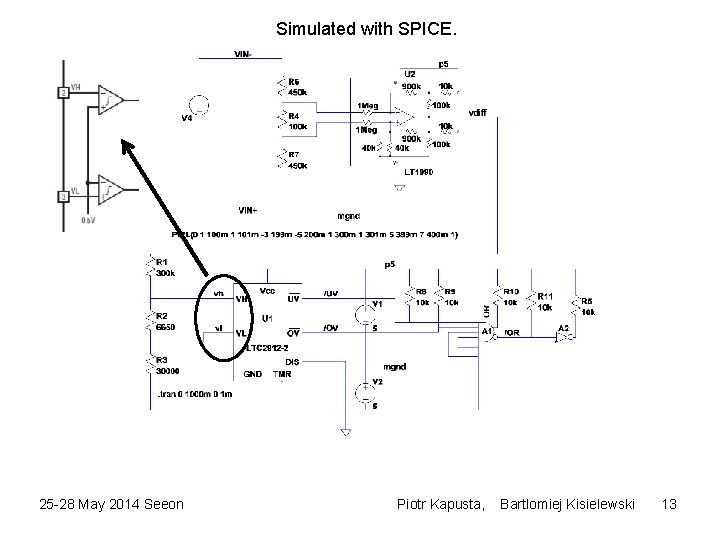

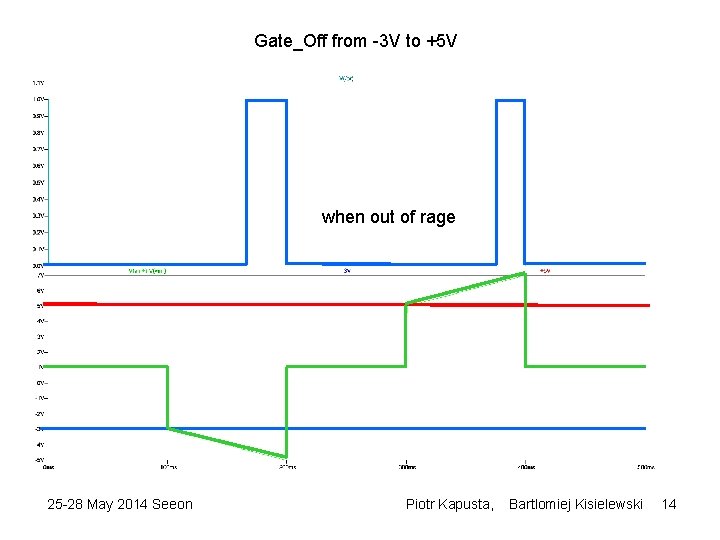

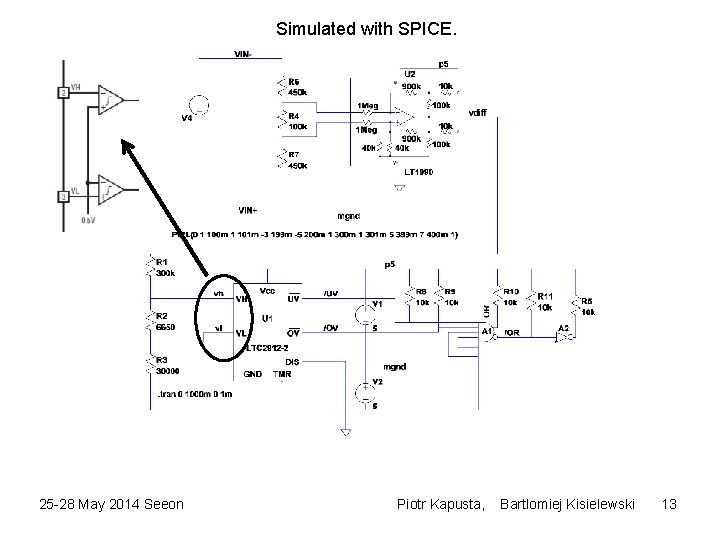

Simulated with SPICE. 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 13

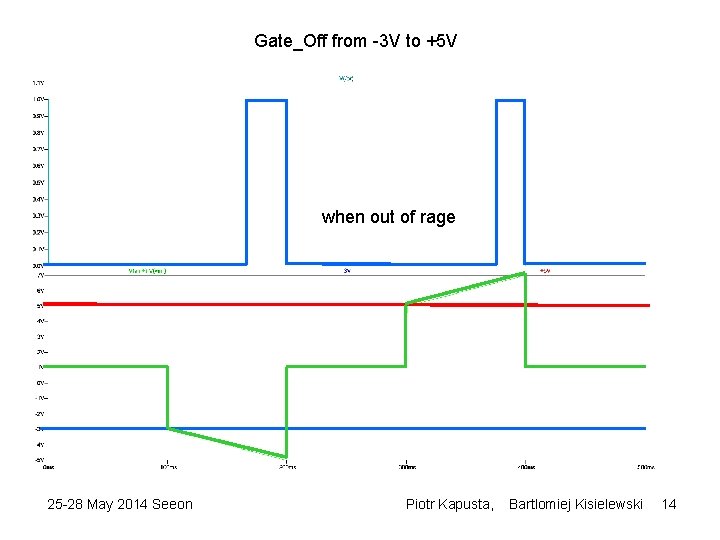

Gate_Off from -3 V to +5 V when out of rage 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 14

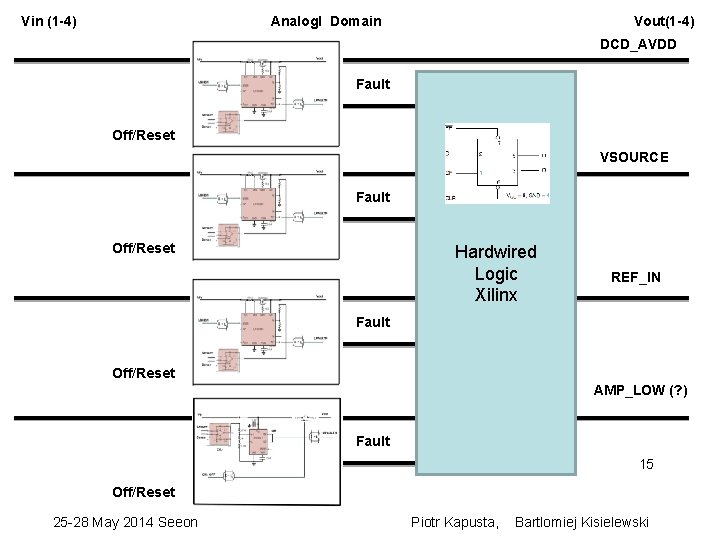

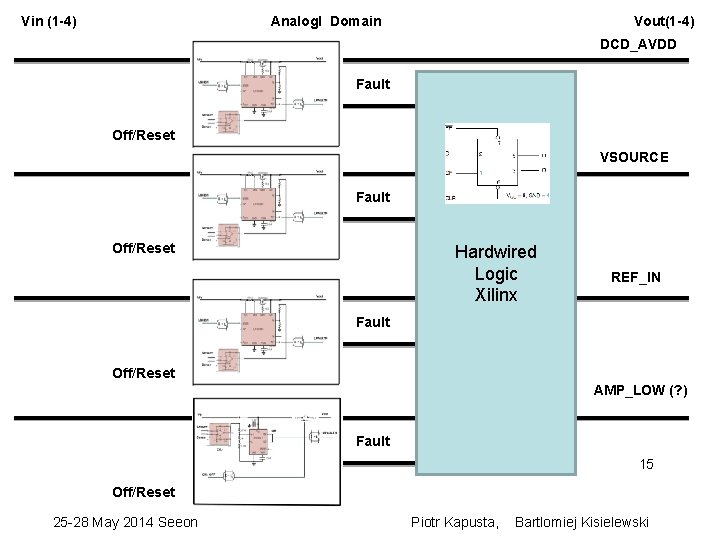

Vin (1 -4) Analogl Domain Vout(1 -4) DCD_AVDD Fault Off/Reset VSOURCE Fault Off/Reset Hardwired Logic Xilinx REF_IN Fault Off/Reset AMP_LOW (? ) Fault 15 Off/Reset 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski

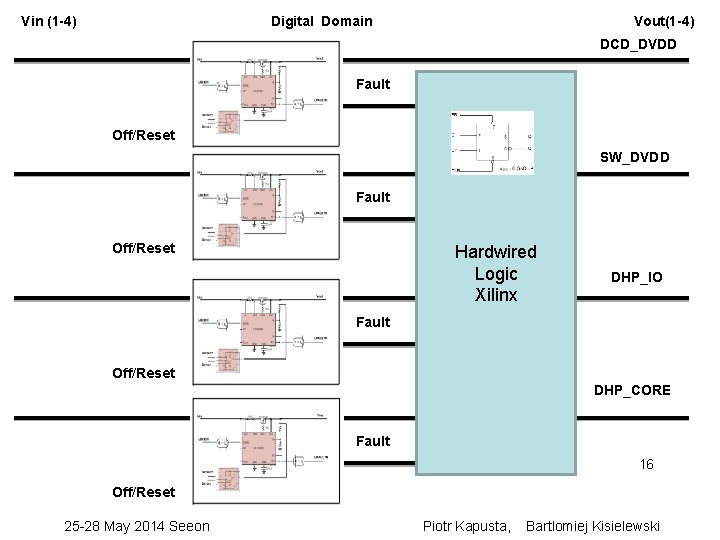

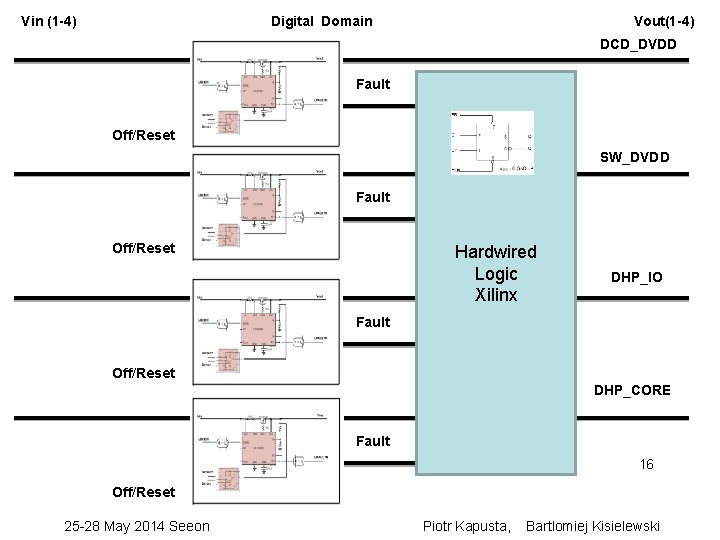

Vin (1 -4) Digital Domain Vout(1 -4) DCD_DVDD Fault Off/Reset SW_DVDD Fault Off/Reset Hardwired Logic Xilinx DHP_IO Fault Off/Reset DHP_CORE Fault 16 Off/Reset 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski

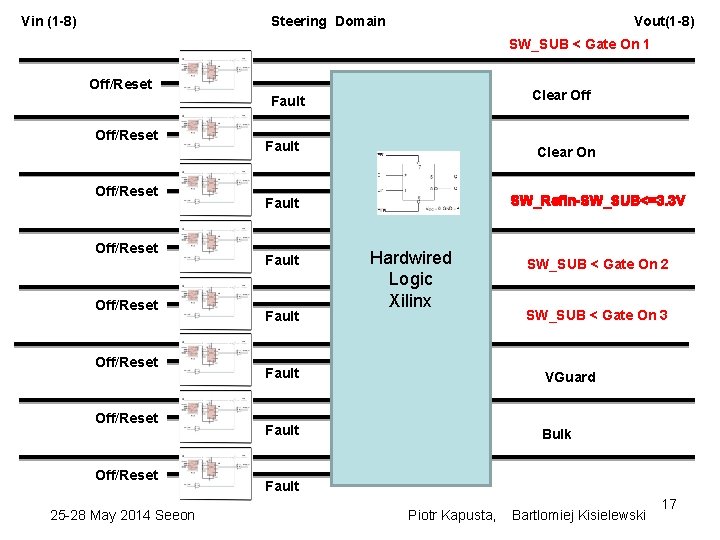

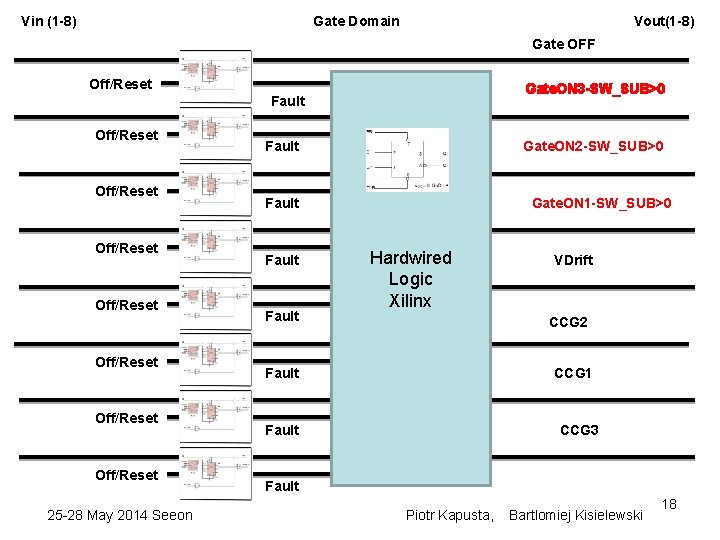

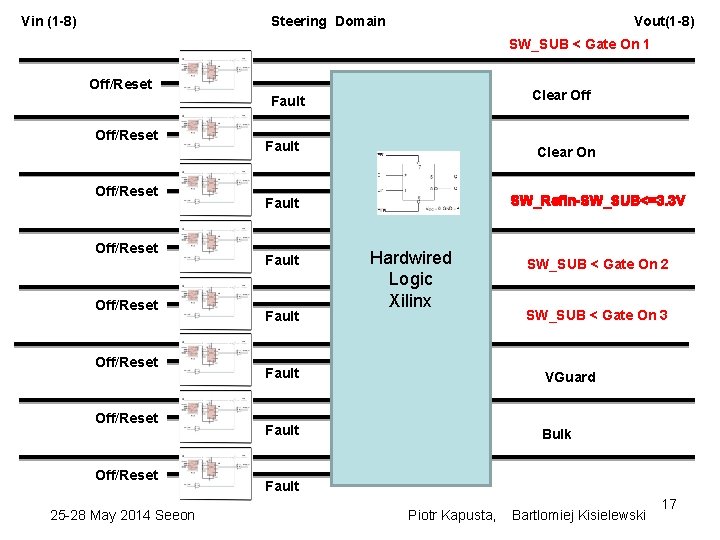

Vin (1 -8) Steering Domain Vout(1 -8) SW_SUB < Gate On 1 Off/Reset Clear Off Fault Off/Reset Off/Reset 25 -28 May 2014 Seeon Fault Clear On SW_Ref. In-SW_SUB<=3. 3 V Fault Hardwired Logic Xilinx SW_SUB < Gate On 2 SW_SUB < Gate On 3 Fault VGuard Fault Bulk Fault Piotr Kapusta, Bartlomiej Kisielewski 17

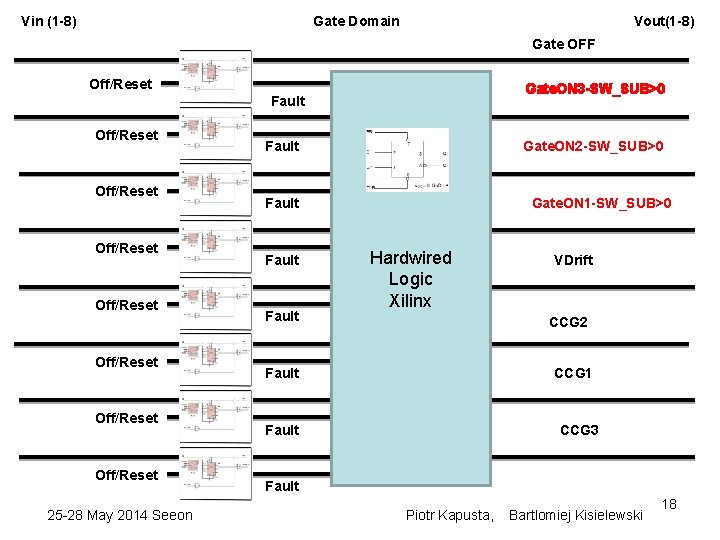

Vin (1 -8) Gate Domain Vout(1 -8) Gate OFF Off/Reset Gate. ON 3 -SW_SUB>0 Fault Off/Reset Off/Reset 25 -28 May 2014 Seeon Fault Gate. ON 2 -SW_SUB>0 Fault Gate. ON 1 -SW_SUB>0 Hardwired Logic Xilinx VDrift CCG 2 Fault CCG 1 Fault CCG 3 Fault Piotr Kapusta, Bartlomiej Kisielewski 18

Communication with Micro. Controller Unit 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 19

![Over Voltage Protection control 6 input bits of the multiplexer address A5 0 1 Over. Voltage Protection control 6 input bits of the multiplexer address A[5: 0]; 1](https://slidetodoc.com/presentation_image_h2/bc9aead4cd563736f345027b837861ed/image-20.jpg)

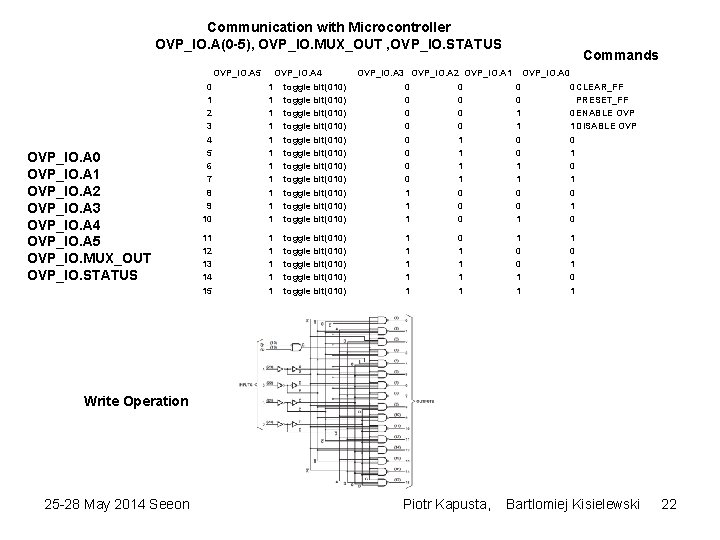

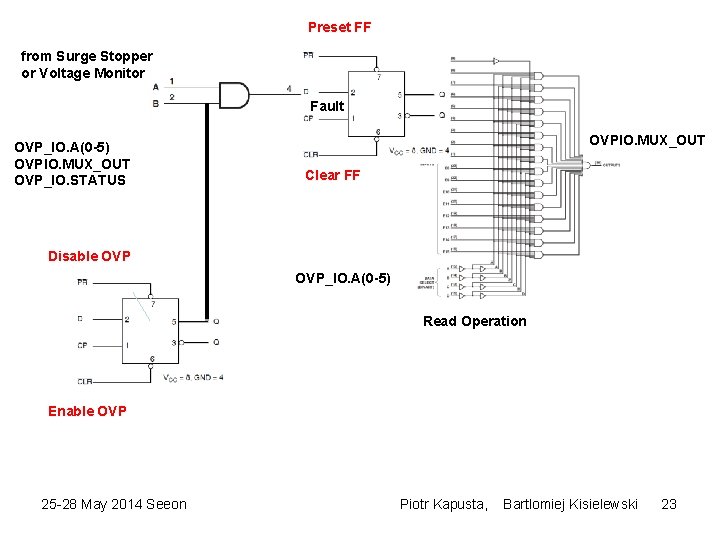

Over. Voltage Protection control 6 input bits of the multiplexer address A[5: 0]; 1 output data bit; 1 output status bit; 2 input shutdown lines SHTDN 1 , SHTDN 2; input serial clock and serial data (I 2 C). OVP logic should contain an error register (failure bits of all channels); OVP logic may contain a control register (mask bits for all channels); the mask bit should make the given channel permanently open. OVP logic should be informed about entering the “active” state , otherwise the 2912 window mode of operation would be not feasible. Simple usage report failure on the status bit (OR of all error register bits) - OVP_IO. STAUS; use A[5] as a read/write selector (0 -> read, 1 -write) - OVP_IO. A 5 ; read the error register contents with A[5]=0 and A[4: 0] used as a channel address; set the control register (masks) using serial shift-in (I 2 C lines or. . . ) with A[5]=1; use SHTDN 1 as an indication of the “active” state. use shtdwn 2 as the reset signal for all error bits. 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 20

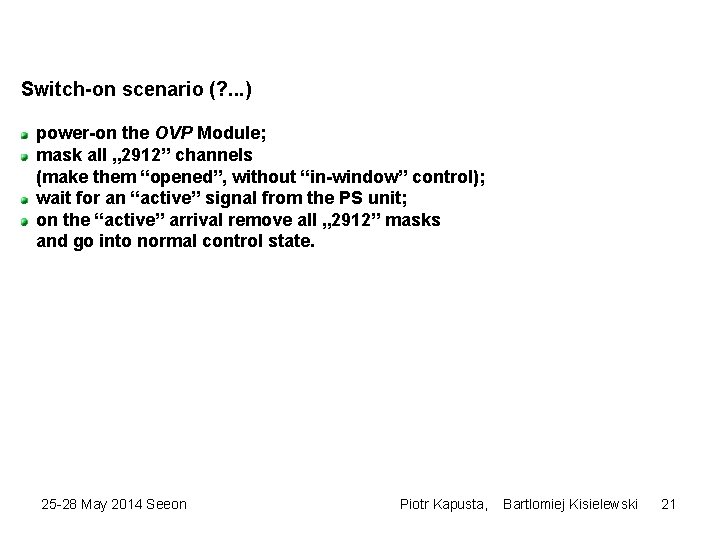

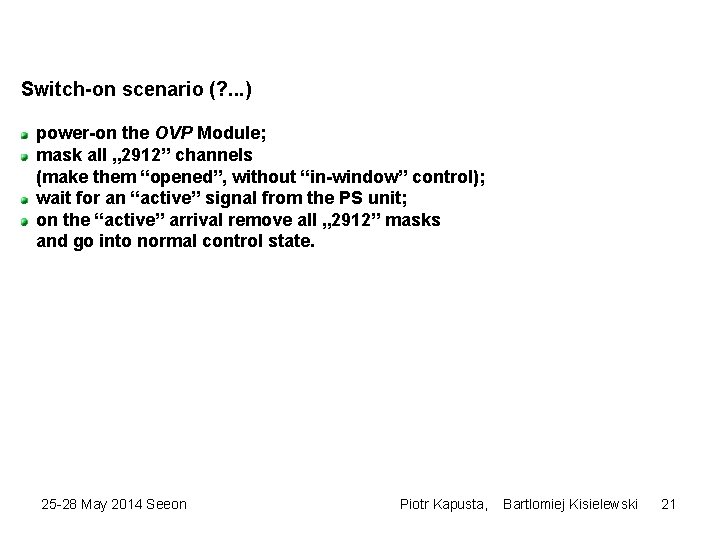

Switch-on scenario (? . . . ) power-on the OVP Module; mask all „ 2912” channels (make them “opened”, without “in-window” control); wait for an “active” signal from the PS unit; on the “active” arrival remove all „ 2912” masks and go into normal control state. 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 21

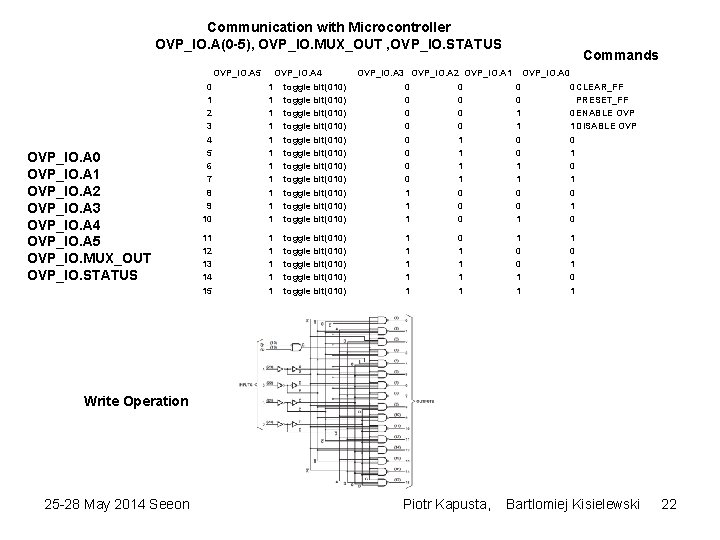

Communication with Microcontroller OVP_IO. A(0 -5), OVP_IO. MUX_OUT , OVP_IO. STATUS OVP_IO. A 5 OVP_IO. A 0 OVP_IO. A 1 OVP_IO. A 2 OVP_IO. A 3 OVP_IO. A 4 OVP_IO. A 5 OVP_IO. MUX_OUT OVP_IO. STATUS 0 1 2 3 4 5 6 7 8 9 10 1 1 1 OVP_IO. A 4 toggle bit(010) toggle bit(010) toggle bit(010) 11 12 13 14 15 1 1 1 toggle bit(010) toggle bit(010) Commands OVP_IO. A 3 OVP_IO. A 2 OVP_IO. A 1 0 0 0 0 0 1 0 1 1 1 1 OVP_IO. A 0 0 0 1 1 0 0 1 0 CLEAR_FF PRESET_FF 0 ENABLE OVP 1 DISABLE OVP 0 1 0 1 0 0 1 1 1 0 1 Write Operation 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 22

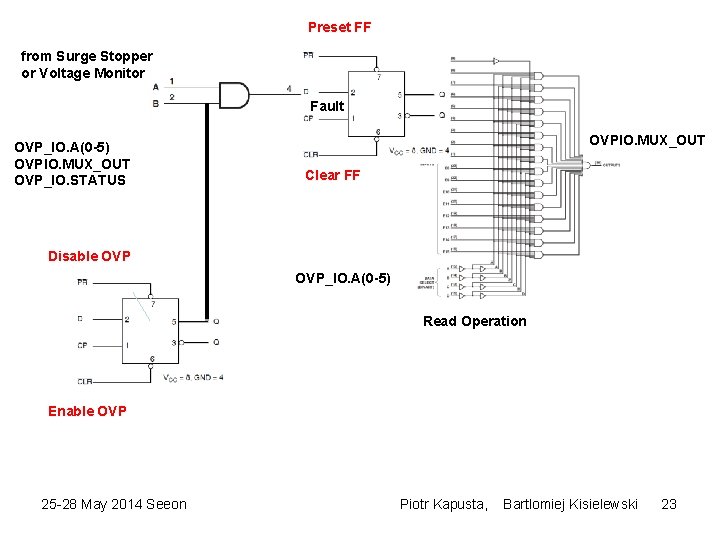

Preset FF from Surge Stopper or Voltage Monitor Fault OVP_IO. A(0 -5) OVPIO. MUX_OUT OVP_IO. STATUS OVPIO. MUX_OUT Clear FF Disable OVP_IO. A(0 -5) Read Operation Enable OVP 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 23

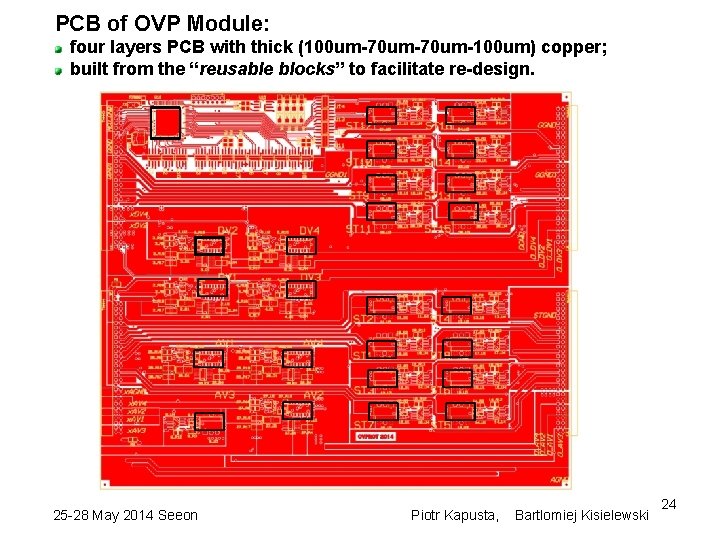

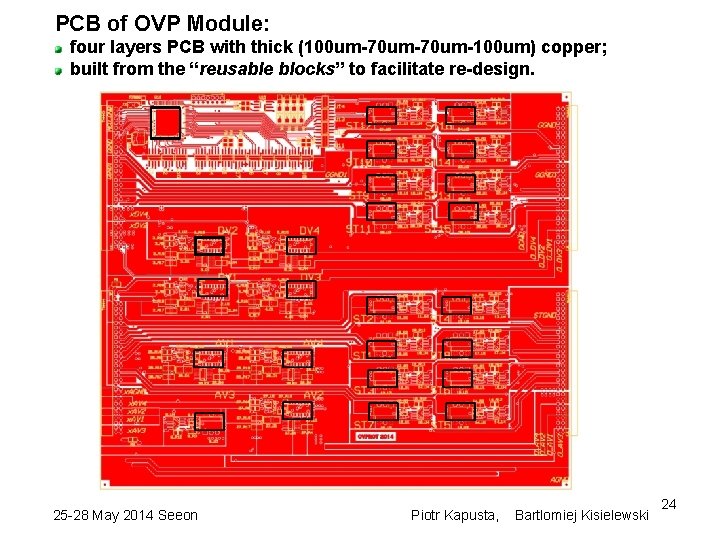

PCB of OVP Module: four layers PCB with thick (100 um-70 um-100 um) copper; built from the “reusable blocks” to facilitate re-design. 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 24

Summary: 1. 2. 3. 4. waiting for PCB – middle of June components for prototype are ordered hand made assembly of prototype and tests – in July integration with PS system – August-Semtember in Munich if OK go to 5 if NO go to 1 5. starting of mass production 12 -15 June 2013 Ringberg Castle Bartlomiej Kisielewski, Piotr Kapusta 25

Thank you ! 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 26

Backup slides 25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 27

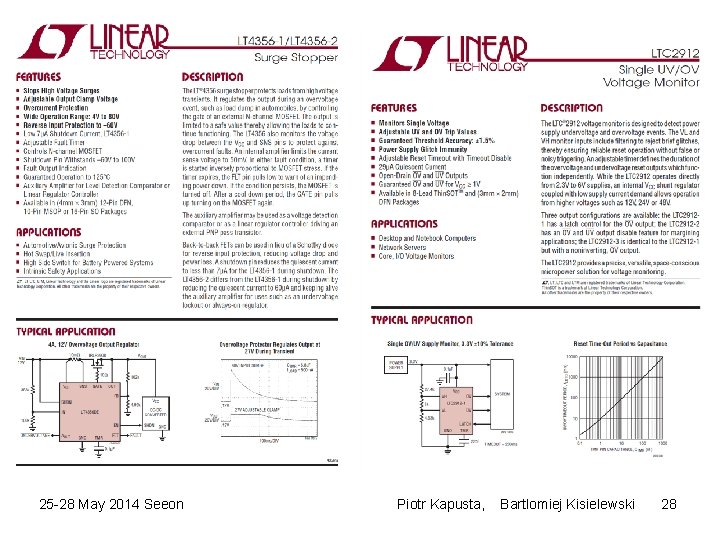

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 28

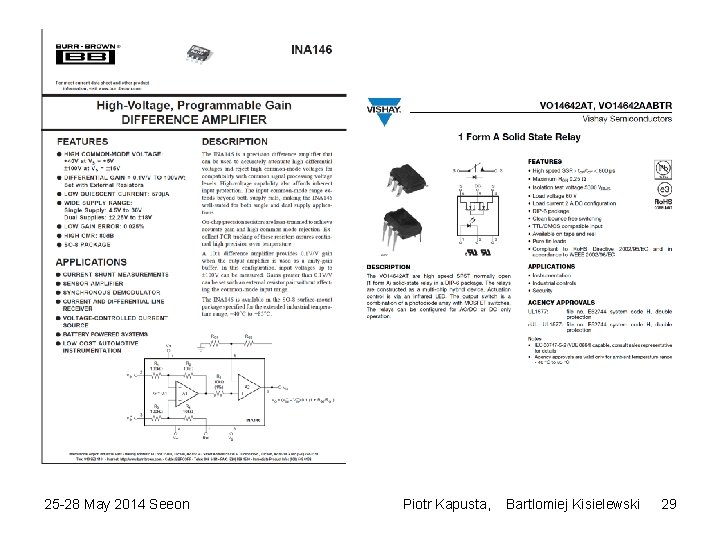

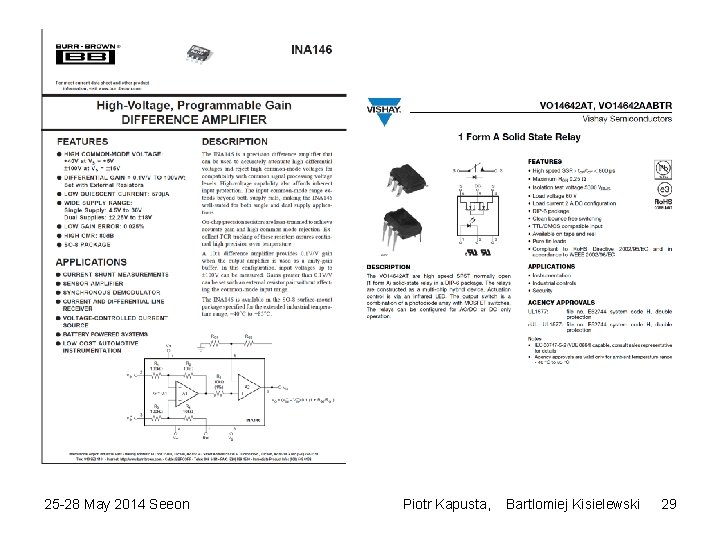

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 29

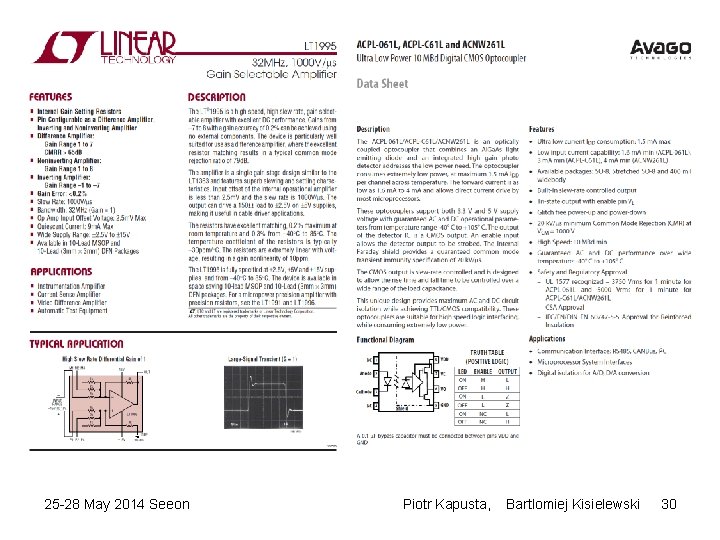

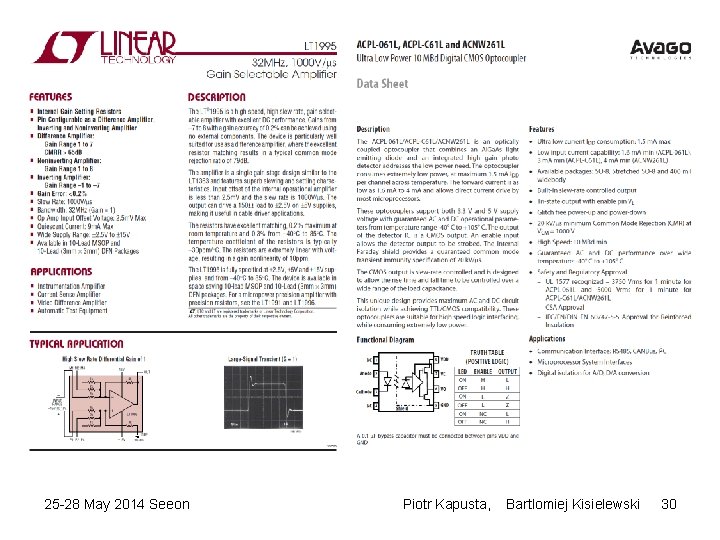

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 30

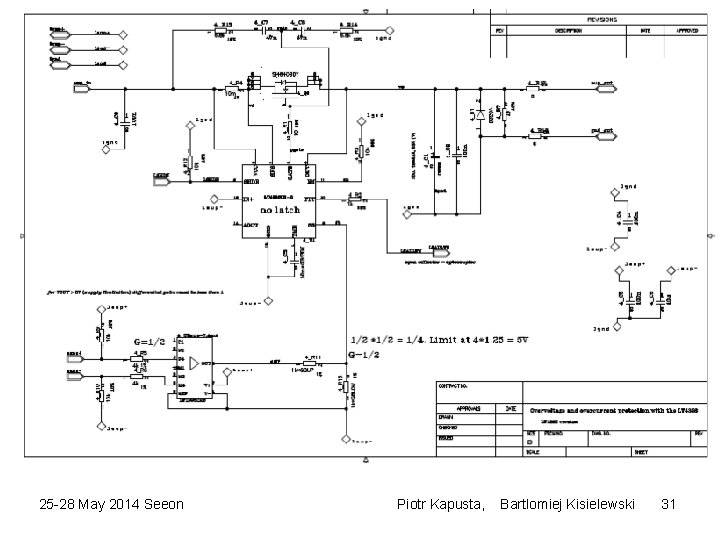

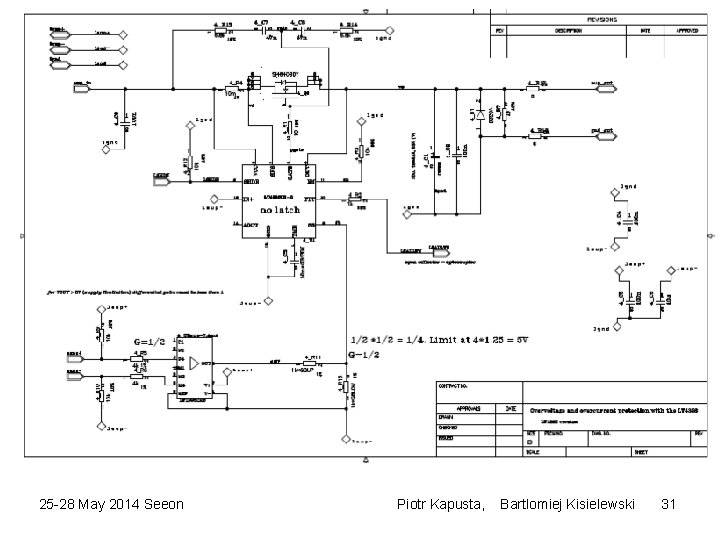

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 31

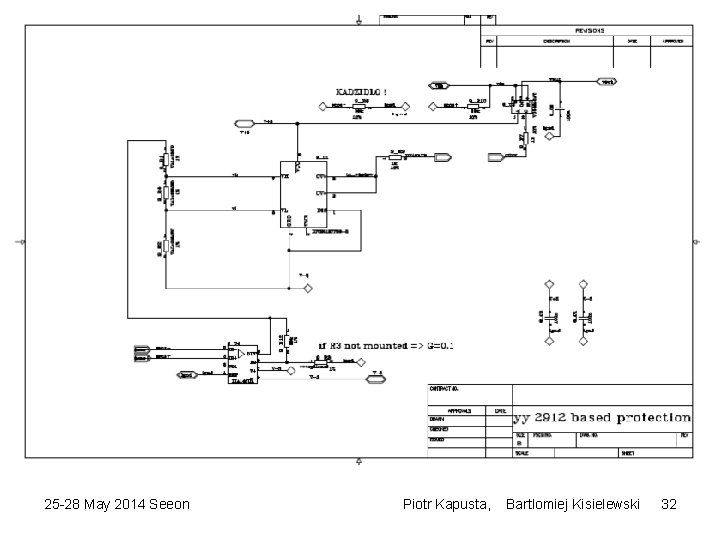

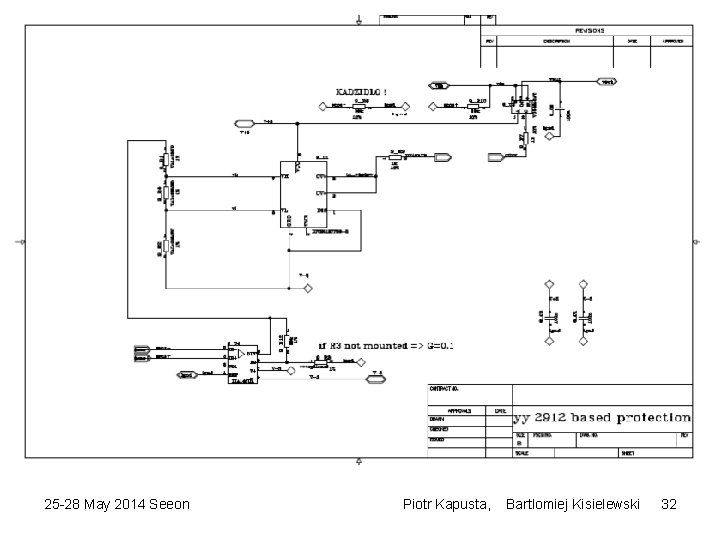

25 -28 May 2014 Seeon Piotr Kapusta, Bartlomiej Kisielewski 32