OUTLINE n n n Introduction Basics of the

OUTLINE n n n Introduction Basics of the Verilog Language Gate-level modeling Data-flow modeling Behavioral modeling Task and function

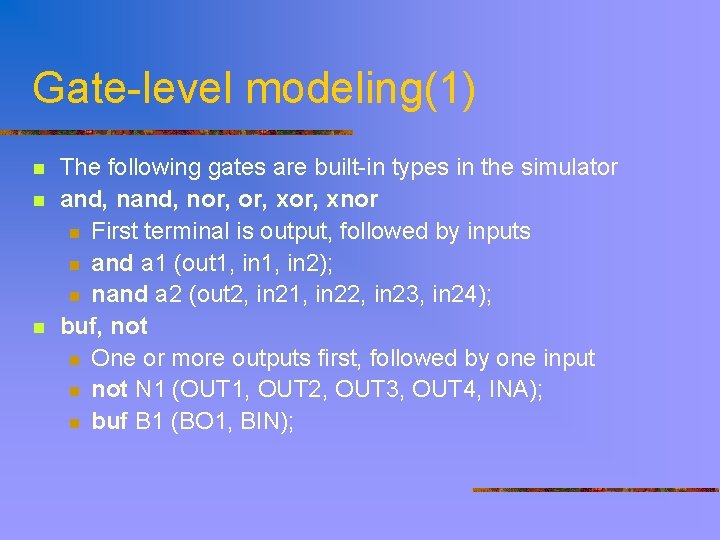

Gate-level modeling(1) n n n The following gates are built-in types in the simulator and, nor, xor, xnor n First terminal is output, followed by inputs n and a 1 (out 1, in 2); n nand a 2 (out 2, in 21, in 22, in 23, in 24); buf, not n One or more outputs first, followed by one input n not N 1 (OUT 1, OUT 2, OUT 3, OUT 4, INA); n buf B 1 (BO 1, BIN);

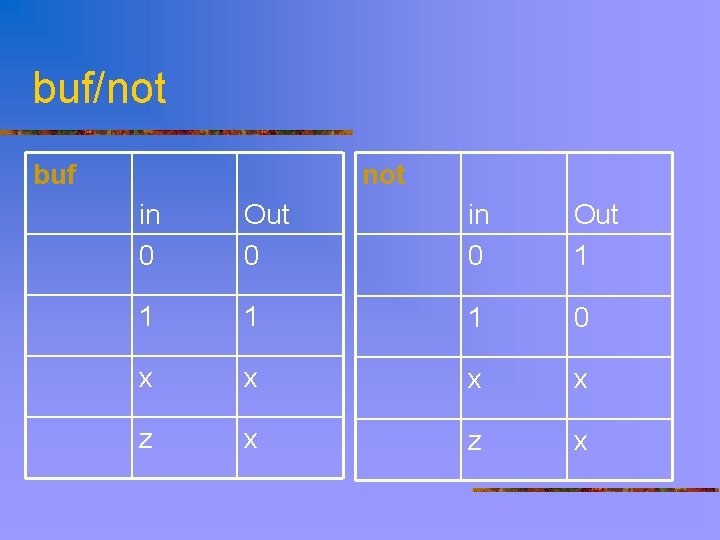

buf/not buf not in 0 Out 0 in 0 Out 1 1 0 x x z x

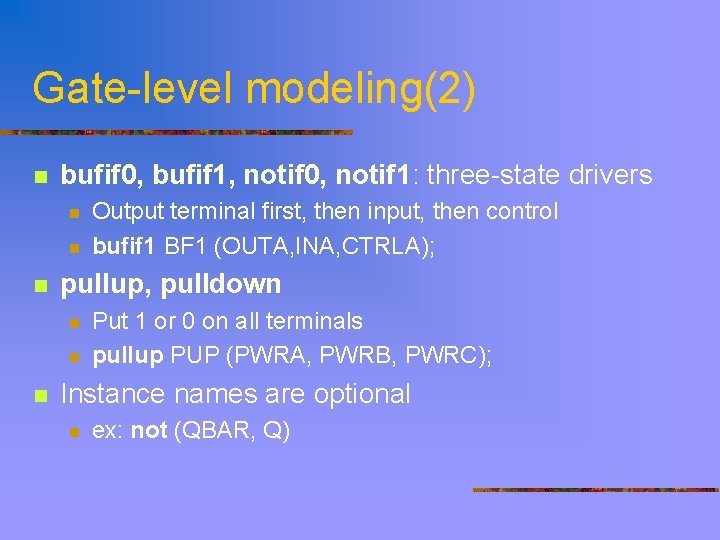

Gate-level modeling(2) n bufif 0, bufif 1, notif 0, notif 1: three-state drivers n n n pullup, pulldown n Output terminal first, then input, then control bufif 1 BF 1 (OUTA, INA, CTRLA); Put 1 or 0 on all terminals pullup PUP (PWRA, PWRB, PWRC); Instance names are optional n ex: not (QBAR, Q)

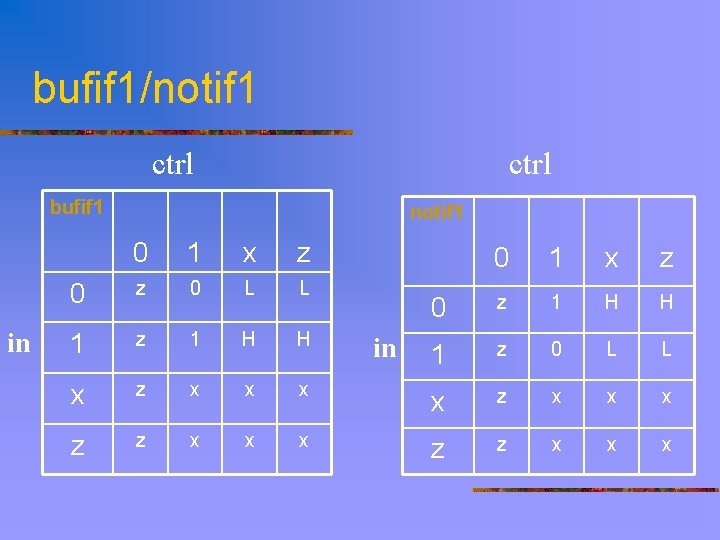

bufif 1/notif 1 ctrl bufif 1 in notif 1 0 1 x z 0 L L 1 z 1 H H x z x x z z x x 0 1 x z 0 z 1 H H 1 z 0 L L x x z z x x x in

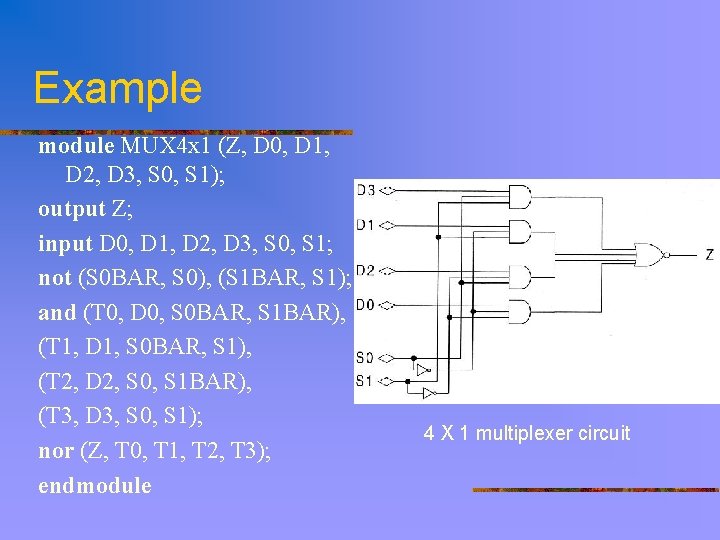

Example module MUX 4 x 1 (Z, D 0, D 1, D 2, D 3, S 0, S 1); output Z; input D 0, D 1, D 2, D 3, S 0, S 1; not (S 0 BAR, S 0), (S 1 BAR, S 1); and (T 0, D 0, S 0 BAR, S 1 BAR), (T 1, D 1, S 0 BAR, S 1), (T 2, D 2, S 0, S 1 BAR), (T 3, D 3, S 0, S 1); nor (Z, T 0, T 1, T 2, T 3); endmodule 4 X 1 multiplexer circuit

OUTLINE n n n Introduction Basics of the Verilog Language Gate-level modeling Data-flow modeling Behavioral modeling Task and function

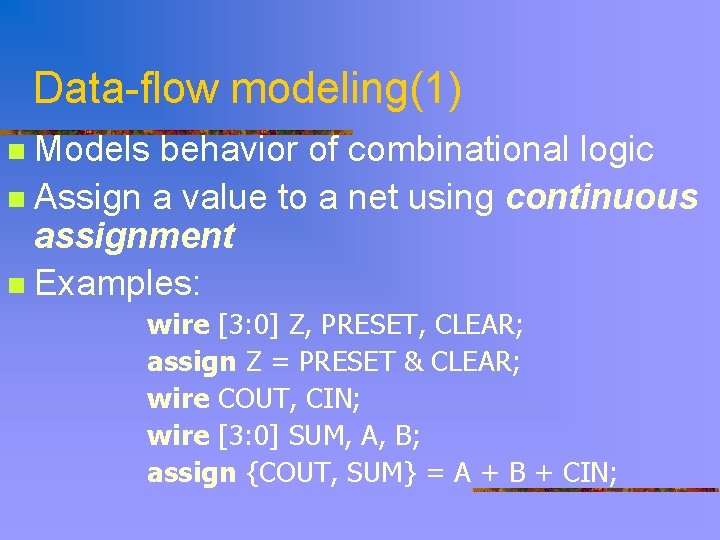

Data-flow modeling(1) Models behavior of combinational logic n Assign a value to a net using continuous assignment n Examples: n wire [3: 0] Z, PRESET, CLEAR; assign Z = PRESET & CLEAR; wire COUT, CIN; wire [3: 0] SUM, A, B; assign {COUT, SUM} = A + B + CIN;

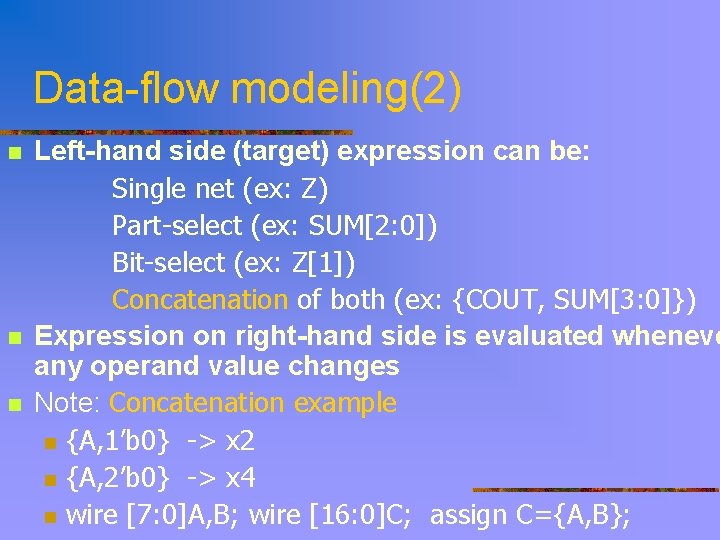

Data-flow modeling(2) n n n Left-hand side (target) expression can be: Single net (ex: Z) Part-select (ex: SUM[2: 0]) Bit-select (ex: Z[1]) Concatenation of both (ex: {COUT, SUM[3: 0]}) Expression on right-hand side is evaluated wheneve any operand value changes Note: Concatenation example n {A, 1’b 0} -> x 2 n {A, 2’b 0} -> x 4 n wire [7: 0]A, B; wire [16: 0]C; assign C={A, B};

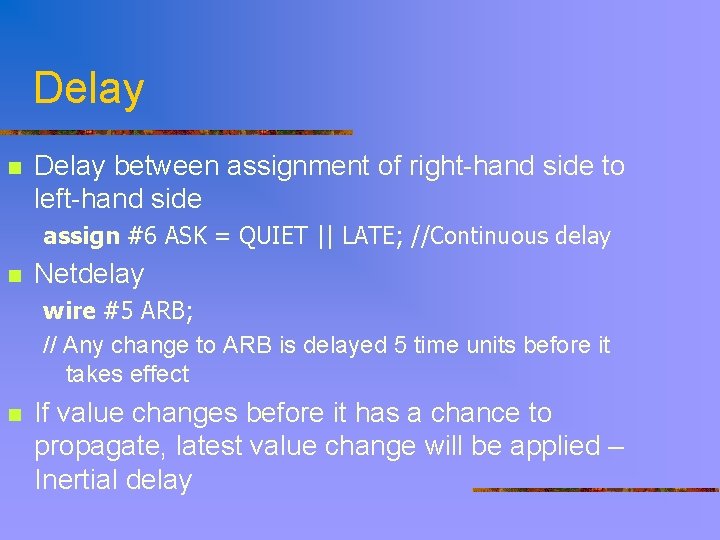

Delay n Delay between assignment of right-hand side to left-hand side assign #6 ASK = QUIET || LATE; //Continuous delay n Netdelay wire #5 ARB; // Any change to ARB is delayed 5 time units before it takes effect n If value changes before it has a chance to propagate, latest value change will be applied – Inertial delay

- Slides: 10