OTIS Review June 05 2003 Heidelberg Harald Deppe

OTIS Review June 05, 2003 Heidelberg Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 1

Content ¢ Overview ¢ Fast Control ¡ Memory and Trigger Management ¡ Data Format ¡ Debug Features ¢ Slow Control ¢ Planned Changes Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 2

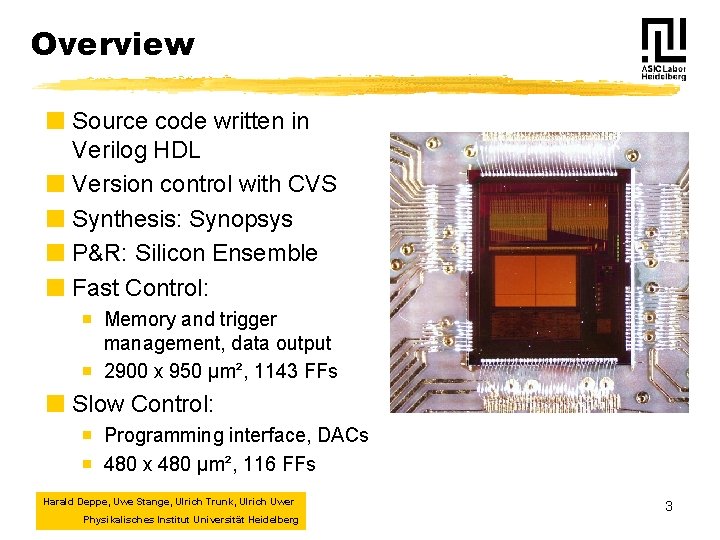

Overview ¢ Source code written in Verilog HDL ¢ Version control with CVS ¢ Synthesis: Synopsys ¢ P&R: Silicon Ensemble ¢ Fast Control: ¡ Memory and trigger management, data output ¡ 2900 x 950 µm², 1143 FFs ¢ Slow Control: ¡ Programming interface, DACs ¡ 480 x 480 µm², 116 FFs Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 3

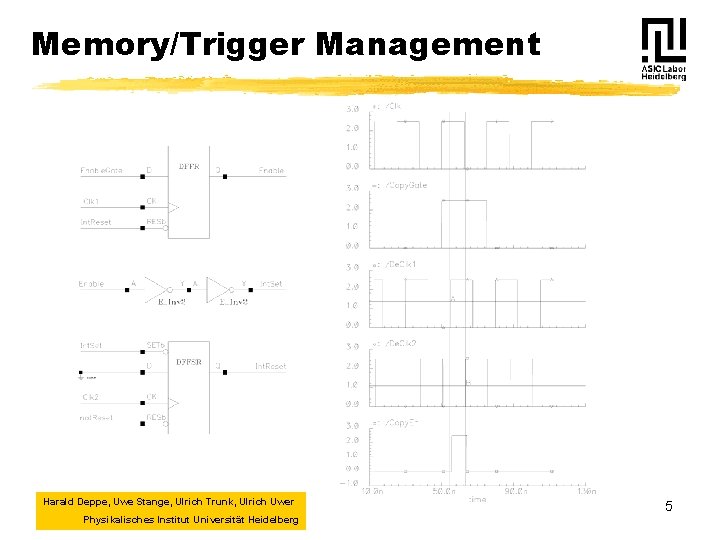

Memory/Trigger Management ¢ Control algorithm provides ¡ write/read addresses for pipeline and derandomizing buffer (clock synchronous) ¡ gate signals for memory write, copy and read events (clock synchronous) ¢ SRAM timing requirements for write, copy or read cycles are derived from the gate signals and the timer block. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 4

Memory/Trigger Management Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 5

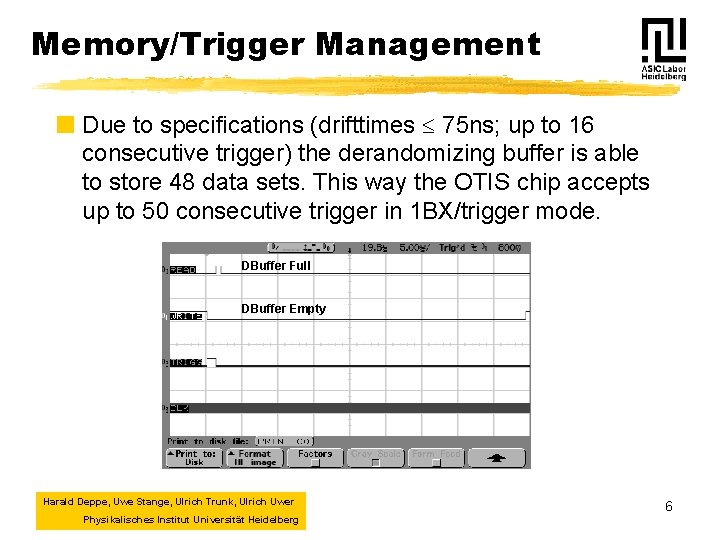

Memory/Trigger Management ¢ Due to specifications (drifttimes 75 ns; up to 16 consecutive trigger) the derandomizing buffer is able to store 48 data sets. This way the OTIS chip accepts up to 50 consecutive trigger in 1 BX/trigger mode. DBuffer Full DBuffer Empty Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 6

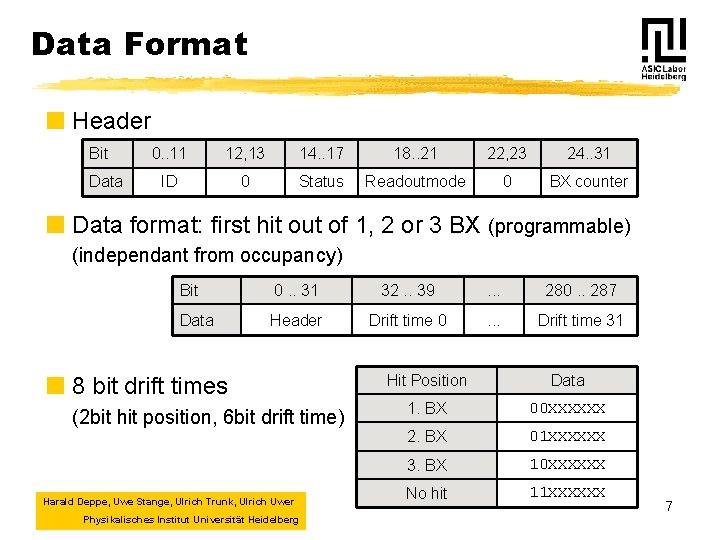

Data Format ¢ Header Bit Data 0. . 11 12, 13 14. . 17 18. . 21 22, 23 24. . 31 ID 0 Status Readoutmode 0 BX counter ¢ Data format: first hit out of 1, 2 or 3 BX (programmable) (independant from occupancy) Bit 0. . 31 32. . 39 . . . 280. . 287 Data Header Drift time 0 . . . Drift time 31 ¢ 8 bit drift times (2 bit hit position, 6 bit drift time) Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg Hit Position Data 1. BX 00 XXXXXX 2. BX 01 XXXXXX 3. BX 10 XXXXXX No hit 11 XXXXXX 7

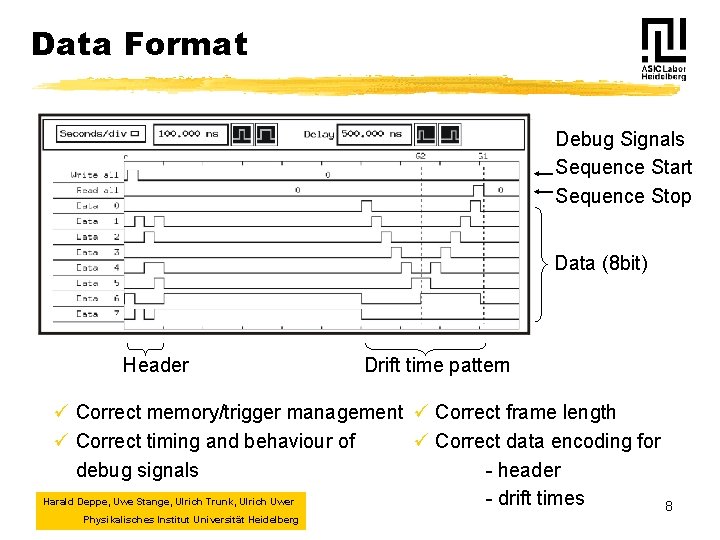

Data Format Debug Signals Sequence Start Sequence Stop Data (8 bit) Header Drift time pattern Correct memory/trigger management Correct frame length Correct timing and behaviour of Correct data encoding for debug signals - header Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer - drift times 8 Physikalisches Institut Universität Heidelberg

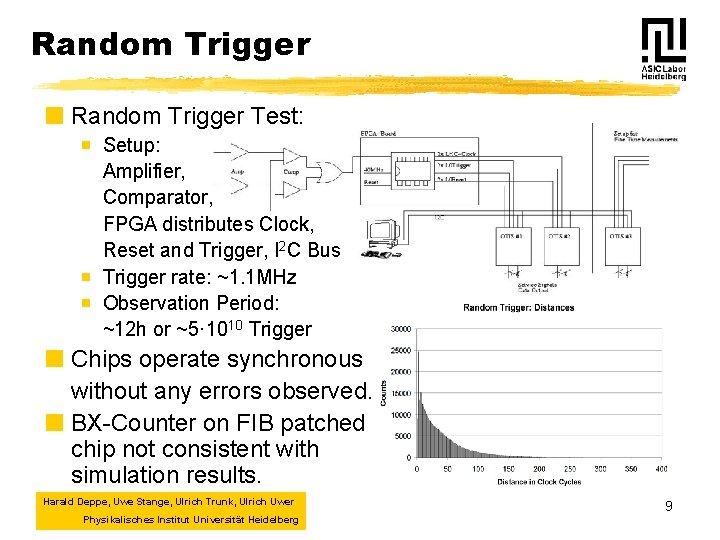

Random Trigger ¢ Random Trigger Test: ¡ Setup: Amplifier, Comparator, FPGA distributes Clock, Reset and Trigger, I 2 C Bus ¡ Trigger rate: ~1. 1 MHz ¡ Observation Period: ~12 h or ~5· 1010 Trigger ¢ Chips operate synchronous without any errors observed. ¢ BX-Counter on FIB patched chip not consistent with simulation results. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 9

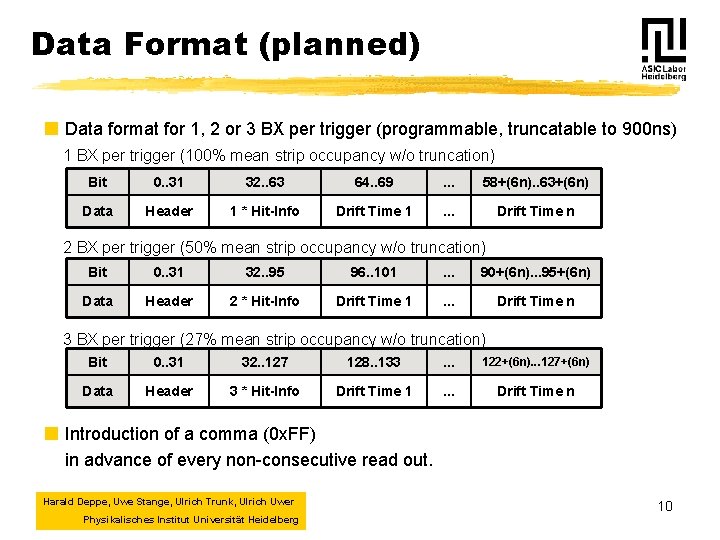

Data Format (planned) ¢ Data format for 1, 2 or 3 BX per trigger (programmable, truncatable to 900 ns) 1 BX per trigger (100% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 63 64. . 69 . . . 58+(6 n). . 63+(6 n) Data Header 1 * Hit-Info Drift Time 1 . . . Drift Time n 2 BX per trigger (50% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 95 96. . 101 . . . 90+(6 n). . . 95+(6 n) Data Header 2 * Hit-Info Drift Time 1 . . . Drift Time n 3 BX per trigger (27% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 127 128. . 133 . . . 122+(6 n). . . 127+(6 n) Data Header 3 * Hit-Info Drift Time 1 . . . Drift Time n ¢ Introduction of a comma (0 x. FF) in advance of every non-consecutive read out. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 10

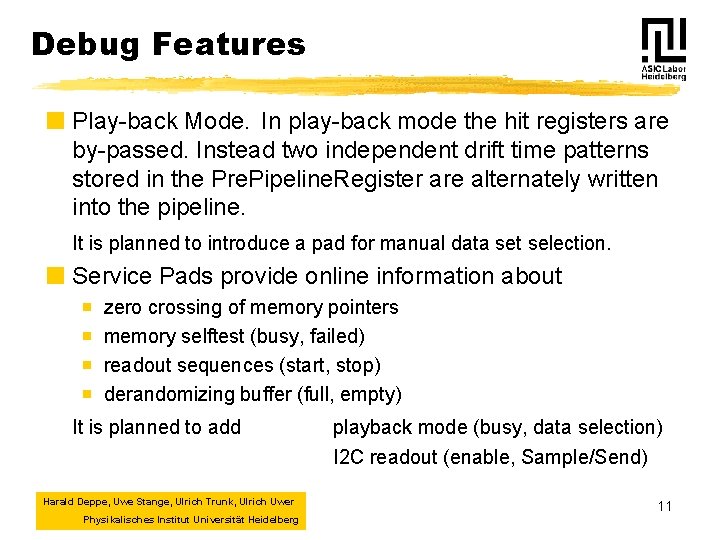

Debug Features ¢ Play-back Mode. In play-back mode the hit registers are by-passed. Instead two independent drift time patterns stored in the Pre. Pipeline. Register are alternately written into the pipeline. It is planned to introduce a pad for manual data set selection. ¢ Service Pads provide online information about ¡ ¡ zero crossing of memory pointers memory selftest (busy, failed) readout sequences (start, stop) derandomizing buffer (full, empty) It is planned to add Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg playback mode (busy, data selection) I 2 C readout (enable, Sample/Send) 11

Debug Features ¢ Memory Selftest As in play-back mode the hit registers are by-passed and a checkered pattern gets written into the pipeline and transfered to derandomizing buffer. Problems: ¡ Frequency depency ¡ Bugs in Verilog source code make every run but the first stop early (not resetted counter) and make the selftest run infinite (FSM: next state assignement gets overwritten). ¢ It is planned to provide data output via I 2 C interface. If enabled triggered data output gets stored in a FIFO accessable via I 2 C interface. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 12

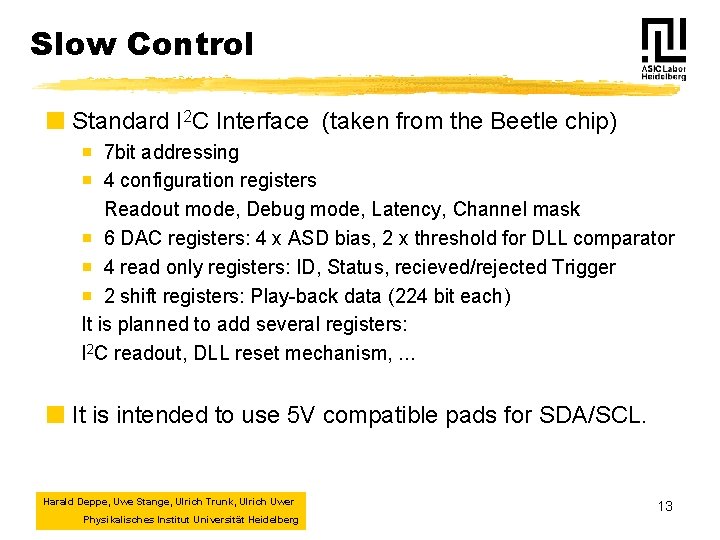

Slow Control ¢ Standard I 2 C Interface (taken from the Beetle chip) ¡ 7 bit addressing ¡ 4 configuration registers Readout mode, Debug mode, Latency, Channel mask ¡ 6 DAC registers: 4 x ASD bias, 2 x threshold for DLL comparator ¡ 4 read only registers: ID, Status, recieved/rejected Trigger ¡ 2 shift registers: Play-back data (224 bit each) It is planned to add several registers: I 2 C readout, DLL reset mechanism, . . . ¢ It is intended to use 5 V compatible pads for SDA/SCL. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 13

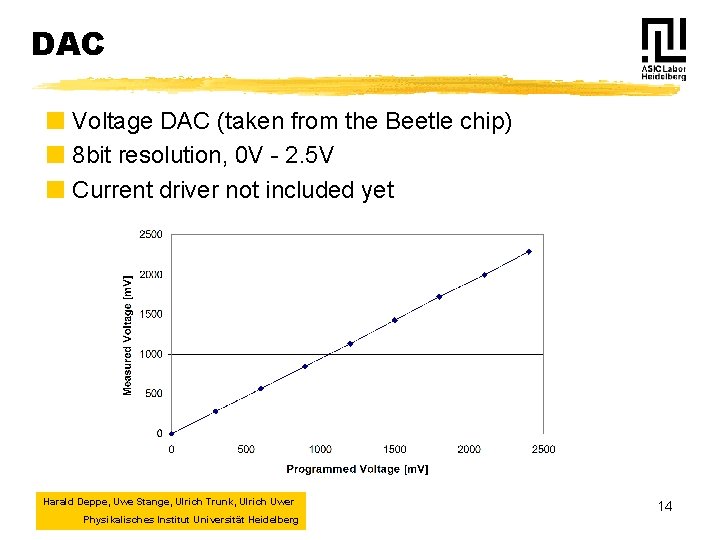

DAC ¢ Voltage DAC (taken from the Beetle chip) ¢ 8 bit resolution, 0 V - 2. 5 V ¢ Current driver not included yet Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 14

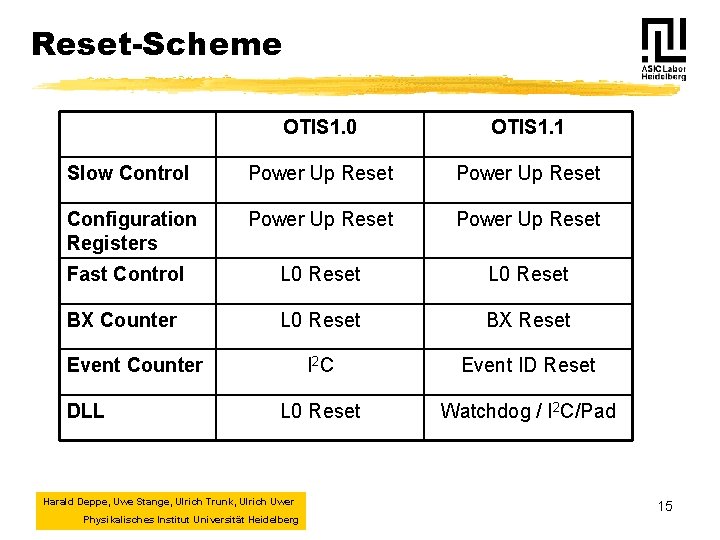

Reset-Scheme OTIS 1. 0 OTIS 1. 1 Slow Control Power Up Reset Configuration Registers Power Up Reset Fast Control L 0 Reset BX Counter L 0 Reset BX Reset I 2 C Event ID Reset L 0 Reset Watchdog / I 2 C/Pad Event Counter DLL Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 15

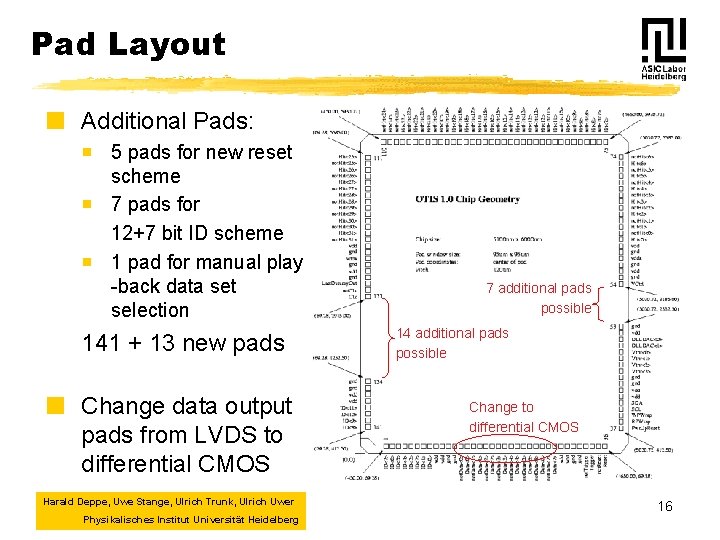

Pad Layout ¢ Additional Pads: ¡ 5 pads for new reset scheme ¡ 7 pads for 12+7 bit ID scheme ¡ 1 pad for manual play -back data set selection 141 + 13 new pads ¢ Change data output pads from LVDS to differential CMOS Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 7 additional pads possible 14 additional pads possible Change to differential CMOS 16

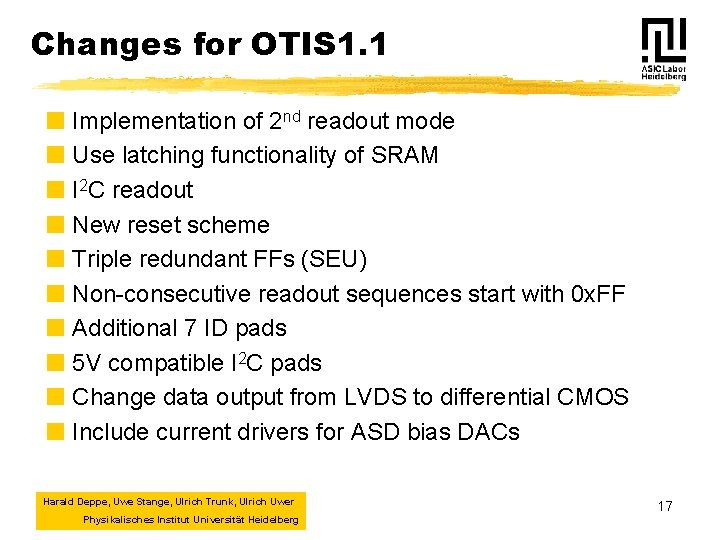

Changes for OTIS 1. 1 ¢ Implementation of 2 nd readout mode ¢ Use latching functionality of SRAM ¢ I 2 C readout ¢ New reset scheme ¢ Triple redundant FFs (SEU) ¢ Non-consecutive readout sequences start with 0 x. FF ¢ Additional 7 ID pads ¢ 5 V compatible I 2 C pads ¢ Change data output from LVDS to differential CMOS ¢ Include current drivers for ASD bias DACs Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 17

- Slides: 17